November 1999 Revised March 2005

## USB1T11A Universal Serial Bus Transceiver

### **General Description**

The USB1T11A is a one chip generic USB transceiver. It is designed to allow 5.0V or 3.3V programmable and standard logic to interface with the physical layer of the Universal Serial Bus. It is capable of transmitting and receiving serial data at both full speed (12Mbit/s) and low speed (1.5Mbit/s) data rates.

The input and output signals of the USB1T11A conform with the "Serial Interface Engine". Implementation of the Serial Interface Engine along with the USB1T11A allows the designer to make USB compatible devices with off-the-shelf logic and easily modify and update the application.

#### **Features**

- Complies with Universal Serial Bus specification 1.1

- Utilizes digital inputs and outputs to transmit and receive USB cable data

- Supports 12Mbit/s "Full Speed" and 1.5Mbit/s "Low Speed" serial data transmission

- Compatible with the VHDL "Serial Interface Engine" from USB Implementers' Forum

- Supports single-ended data interface

- Single 3.3V supply

- ESD Performance: Human Body Model > 9.5 kV on D-, D+ pins only

- > 4 kV on all other pins

- 16-lead Pb-Free MLP package saves space

## **Ordering Code:**

| Order Number                | Package<br>Number | Package Description                                                                  |

|-----------------------------|-------------------|--------------------------------------------------------------------------------------|

| USB1T11AM<br>(Note 1)       | M14A              | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow         |

| USB1T11AM_NL<br>(Note 2)    | M14A              | Pb-Free 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

| USB1T11ABQX                 | MLP16C            | Pb-Free 16-Terminal Molded Leadless Package (MLP), JEDEC MO-220, 3mm square          |

| USB1T11AMTC<br>(Note 1)     | MTC14             | 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide          |

| USB1T11AMTC_NL<br>(Note 2)  | MTC14             | Pb-Free 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide  |

| USB1T11AMTCX_NL<br>(Note 2) | MTC14             | Pb-Free 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide  |

Pb-Free package per JEDEC J-STD-020B.

Note 1: Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

Note 2: "\_NL" indicates Pb-Free package (per JEDEC J-STD-020B). Please use order number as indicated.

The USB-IF Logos are trademarks of Universal Serial Bus Implementers Forum, Inc.

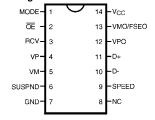

## **Connection Diagrams**

## Pin Assignments for SOIC and TSSOP

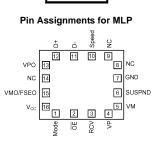

#### Pin Assignments for MLP

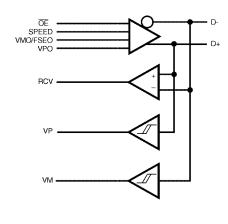

## **Logic Diagram**

## **Pin Descriptions**

| Pin Name                                            | I/O  |                                                                                                                                                                  |                                                                                                                                   | Description                                              |                                          |  |  |  |  |

|-----------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------|--|--|--|--|

| RCV                                                 | 0    | Receive data. CMOS                                                                                                                                               | Receive data. CMOS level output for USB differential input                                                                        |                                                          |                                          |  |  |  |  |

| ŌE                                                  | I    |                                                                                                                                                                  | utput Enable. Active LOW, enables the transceiver to transmit data on the bus. When not ctive the transceiver is in receive mode. |                                                          |                                          |  |  |  |  |

| MODE                                                | I    | Mode. When left unco<br>VMO/FSEO pin takes                                                                                                                       |                                                                                                                                   | oull-up transistor pulls it to EO (Force SEO).           | V <sub>CC</sub> and in this GND, the     |  |  |  |  |

| V <sub>PO</sub> , V <sub>MO</sub> /F <sub>SEO</sub> | ı    | Inputs to differential di                                                                                                                                        | river. (Outputs fron                                                                                                              | n SIE).                                                  |                                          |  |  |  |  |

|                                                     |      | MODE                                                                                                                                                             | VPO                                                                                                                               | VMO/FSEO                                                 | RESULT                                   |  |  |  |  |

|                                                     |      | 0                                                                                                                                                                | 0                                                                                                                                 | 0                                                        | Logic "0"                                |  |  |  |  |

|                                                     |      |                                                                                                                                                                  | 0                                                                                                                                 | 1                                                        | SE0                                      |  |  |  |  |

|                                                     |      |                                                                                                                                                                  | 1                                                                                                                                 | 0                                                        | Logic "1"                                |  |  |  |  |

|                                                     |      |                                                                                                                                                                  | 1                                                                                                                                 | 1                                                        | SEO                                      |  |  |  |  |

|                                                     |      | 1                                                                                                                                                                | 0                                                                                                                                 | 0                                                        | SE0                                      |  |  |  |  |

|                                                     |      |                                                                                                                                                                  | 0                                                                                                                                 | 1                                                        | Logic "0"                                |  |  |  |  |

|                                                     |      |                                                                                                                                                                  | 1                                                                                                                                 | 0                                                        | Logic "1"                                |  |  |  |  |

|                                                     |      |                                                                                                                                                                  | 1                                                                                                                                 | 1                                                        | Illegal code                             |  |  |  |  |

| $V_P, V_M$                                          | 0    | Gated version of D- and D+. Outputs are logic "0" and logic "1". Used to detect single end zero (SE0), error conditions, and interconnect speed. (Input to SIE). |                                                                                                                                   |                                                          |                                          |  |  |  |  |

|                                                     |      | VP                                                                                                                                                               | VM                                                                                                                                | RESULT                                                   |                                          |  |  |  |  |

|                                                     |      | 0                                                                                                                                                                | 0                                                                                                                                 | SE0                                                      |                                          |  |  |  |  |

|                                                     |      | 0                                                                                                                                                                | 1                                                                                                                                 | Low Speed                                                |                                          |  |  |  |  |

|                                                     |      | 1                                                                                                                                                                | 0                                                                                                                                 | Full Speed                                               |                                          |  |  |  |  |

|                                                     |      | 1                                                                                                                                                                | 1                                                                                                                                 | Error                                                    |                                          |  |  |  |  |

| D+, D-                                              | AI/O | Data+, Data Differer                                                                                                                                             | ntial data bus confo                                                                                                              | orming to the Universal Se                               | rial Bus standard.                       |  |  |  |  |

| SUSPND                                              | I    |                                                                                                                                                                  |                                                                                                                                   | ile the USB bus is inactive<br>"0" state. Both D+ and D– | e. While the suspend pin is are 3-STATE. |  |  |  |  |

| SPEED                                               | I    | Edge rate control. Log<br>Logic "0" operates edge                                                                                                                |                                                                                                                                   | edge rates for "full speed".<br>beed".                   |                                          |  |  |  |  |

| V <sub>CC</sub>                                     |      | 3.0V to 3.6V power su                                                                                                                                            | ipply                                                                                                                             |                                                          |                                          |  |  |  |  |

| GND                                                 |      | Ground reference                                                                                                                                                 |                                                                                                                                   |                                                          |                                          |  |  |  |  |

## **Functional Truth Table**

|      | Input |          |    |        | I/O |    |     | Outputs        |                |              |

|------|-------|----------|----|--------|-----|----|-----|----------------|----------------|--------------|

| Mode | VPO   | VMO/FSEO | OE | SUSPND | D+  | D- | RCV | V <sub>P</sub> | V <sub>M</sub> | Result       |

| 0    | 0     | 0        | 0  | 0      | 0   | 1  | 0   | 0              | 1              | Logic 0      |

| 0    | 0     | 1        | 0  | 0      | 0   | 0  | U   | 0              | 0              | SEO          |

| 0    | 1     | 0        | 0  | 0      | 1   | 0  | 1   | 1              | 0              | Logic 1      |

| 0    | 1     | 1        | 0  | 0      | 0   | 0  | U   | 0              | 0              | SEO          |

| 1    | 0     | 0        | 0  | 0      | 0   | 0  | U   | 0              | 0              | SEO          |

| 1    | 0     | 1        | 0  | 0      | 0   | 1  | 0   | 0              | 1              | Logic 0      |

| 1    | 1     | 0        | 0  | 0      | 1   | 0  | 1   | 1              | 0              | Logic 1      |

| 1    | 1     | 1        | 0  | 0      | 1   | 1  | U   | U              | U              | Illegal Code |

| Х    | Х     | X        | 1  | 0      | Z   | Z  | U   | U              | U              | D+/D- Hi-Z   |

| Х    | Х     | Х        | 1  | 1      | Z   | Z  | U   | U              | U              | D+/D- Hi-Z   |

X = Don't Care

Z = 3-STATE

U = Undefined State

## Absolute Maximum Ratings(Note 3)

## DC Supply Voltage (V<sub>CC</sub>) -0.5V to +7.0V

DC Input Diode Current (I<sub>IK</sub>)

$V_I < 0$  –50 mA

Input Voltage  $(V_I)$

(Note 4) -0.5V to +5.5V

Input Voltage ( $V_{I/O}$ ) -0.5V to  $V_{CC}$  + 0.5V

Output Diode Current (I<sub>OK</sub>)

$V_O > V_{CC}$  or  $V_O < 0$  ±50 mA

Output Voltage (V<sub>O</sub>)

(Note 4) -0.5V to  $V_{CC} + 0.5V$

Output Source or Sink Current (IO)

VP.VM, RCV pins

$V_O = 0 \text{ to } V_{CC}$  ±15 mA

Output Source or Sink Current (IO)

D+/D- pins

$V_O$  = 0 to  $V_{CC}$   $\pm 50$  mA

$V_{CC}$  or GND Current ( $I_{CC}$ ,  $I_{GND}$ ) ±100 mA

Storage Temperature (T<sub>STO</sub>) -60°C to + 150°C

## Recommended Operating Conditions

Supply Voltage V<sub>CC</sub> 3.0V to 3.6V

Input Voltage (V<sub>I</sub>) 0V to 5.5V

$\begin{array}{ll} \text{Input Range for AI/O (V}_{\text{AI/O}}) & \text{OV to V}_{\text{CC}} \\ \text{Output Voltage (V}_{\text{O}}) & \text{OV to V}_{\text{CC}} \\ \end{array}$

Operating Ambient Temperature

in free air ( $T_{amb}$ )  $-40^{\circ}C$  to  $+85^{\circ}C$

Note 3: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristic tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

**Note 4:** The input and output voltage ratings may be exceeded if the input and output clamp current ratings are observed.

and output damp durient ratings are

#### DC Electrical Characteristics (Digital Pins)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted).  $V_{CC} = 3.0V$  to 3.6V

|                   |                             |                                                      |                       | Limits |     |      |  |

|-------------------|-----------------------------|------------------------------------------------------|-----------------------|--------|-----|------|--|

| Symbol            | Parameter                   | Test Conditions                                      | Temp                  | Unit   |     |      |  |

|                   |                             |                                                      | Min                   | Тур    | Max |      |  |

|                   | INPUT LEVELS:               | •                                                    |                       |        |     | •    |  |

| V <sub>IL</sub>   | LOW Level Input Voltage     |                                                      |                       |        | 0.8 | V    |  |

| V <sub>IH</sub>   | HIGH Level Input Voltage    |                                                      | 2.0                   |        |     | V    |  |

|                   | OUTPUT LEVELS:              | •                                                    |                       |        |     | •    |  |

| V <sub>OL</sub>   | LOW Level Output Voltage    | I <sub>OL</sub> = 4 mA                               |                       |        | 0.4 | V    |  |

|                   |                             | $I_{OL} = 20 \mu A$                                  |                       |        | 0.1 | _ v  |  |

| V <sub>OH</sub>   | HIGH Level Output Voltage   | I <sub>OH</sub> = 4 mA                               | 2.4                   |        |     | V    |  |

|                   |                             | $I_{OH} = 20 \mu A$                                  | V <sub>CC</sub> - 0.1 |        |     | _ v  |  |

|                   | LEAKAGE CURRENT:            | •                                                    |                       |        |     | •    |  |

| IL                | Input Leakage Current       | V <sub>CC</sub> = 3.0 to 3.6                         |                       |        | ±5  | μΑ   |  |

| I <sub>CCFS</sub> | Supply Current (Full Speed) | V <sub>CC</sub> = 3.0 to 3.6                         |                       |        | 5   | mA   |  |

| I <sub>CCLS</sub> | Supply Current (Low Speed)  | V <sub>CC</sub> = 3.0 to 3.6                         |                       |        | 5   | mA   |  |

| I <sub>CCQ</sub>  | Quiescent Current           | V <sub>CC</sub> = 3.0 to 3.6                         |                       |        | 5   | mA   |  |

|                   |                             | $V_{IN} = V_{CC}$ or GND                             |                       |        | 3   | IIIA |  |

| I <sub>CCS</sub>  | Supply Current in Suspend   | V <sub>CC</sub> = 3.0 to 3.6; Mode = V <sub>CC</sub> |                       |        | 10  | μА   |  |

## DC Electrical Characteristics (D+/D- Pins)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted).  $V_{CC} = 3.0 \text{V}$  to 3.6 V

|                           |                                                |                                 |                                       | Units |      |    |

|---------------------------|------------------------------------------------|---------------------------------|---------------------------------------|-------|------|----|

| Symbol                    | Parameter                                      | Test Conditions                 | Temp                                  |       |      |    |

|                           |                                                |                                 | Min                                   | Тур   | Max  | 1  |

|                           | INPUT LEVELS:                                  |                                 |                                       |       |      |    |

| V <sub>DI</sub>           | Differential Input Sensitivity                 | (D+) - (D-)                     | 0.2                                   |       |      | V  |

| V <sub>CM</sub>           | Differential Common Mode Range                 | Includes V <sub>DI</sub> Range  | 0.8                                   |       | 2.5  | V  |

| V <sub>SE</sub>           | Single Ended Receiver Threshold                |                                 | 0.8                                   |       | 2.0  | V  |

|                           | OUTPUT LEVELS:                                 |                                 |                                       |       |      |    |

| V <sub>OL</sub>           | Static Output LOW Voltage                      | $R_L$ of 1.5 k $\Omega$ to 3.6V |                                       |       | 0.3  | V  |

| V <sub>OH</sub>           | Static Output HIGH Voltage                     | $R_L$ of 15 k $\Omega$ to GND   | 2.8                                   |       | 3.6  | V  |

| V <sub>CR</sub>           | Differential Crossover                         |                                 | 1.3                                   |       | 2.0  | V  |

|                           | LEAKAGE CURRENT:                               |                                 | •                                     | •     |      |    |

| I <sub>OZ</sub>           | High Z State Data Line Leakage Current         | 0V < V <sub>IN</sub> < 3.3V     |                                       |       | ±5   | μА |

|                           | CAPACITANCE:                                   |                                 |                                       |       |      |    |

| C <sub>IN</sub> (Note 6)  | Transceiver Capacitance                        | Pin to GND                      |                                       |       | 10   | pF |

|                           | Capacitance Match                              |                                 |                                       |       | 10   | %  |

|                           | OUTPUT RESISTANCE:                             |                                 | · · · · · · · · · · · · · · · · · · · | ı     |      |    |

| Z <sub>DRV</sub> (Note 5) | Driver Output Resistance                       | Steady State Drive              | 4                                     |       | 20   | Ω  |

|                           | Resistance Match                               |                                 |                                       |       | 10   | %  |

| Mata E. Fredric           | des suternal register. In order to comply with | HOD Oifti 4.4tli                |                                       | 40/   | D 10 |    |

Note 5: Excludes external resistor. In order to comply with USB Specification 1.1, external series resistors of 24Ω ± 1% each on D+ and D- are recommended. This specification is guaranteed by design and statistical process distribution.

Note 6: This specification is guaranteed by design and statistical process distribution.

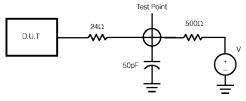

## AC Electrical Characteristics (D+/D- Pins, Full Speed)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted).  $V_{CC}=3.0V$  to 3.6V C<sub>L</sub> = 50 pF; R<sub>L</sub> = 1.5 k $\Omega$  on D+ to  $V_{CC}$

|                  |                                 |                | Limits Temp = -40°C to +85°C |       |     |    |  |

|------------------|---------------------------------|----------------|------------------------------|-------|-----|----|--|

| Symbol           | Parameter                       | Test Condition | Temp                         | Units |     |    |  |

|                  |                                 |                | Min                          | Тур   | Max | 1  |  |

|                  | DRIVER CHARACTERISTICS:         | •              | •                            |       |     | ı  |  |

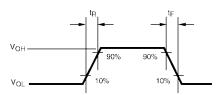

|                  |                                 | 10% and 90%    |                              |       |     | ns |  |

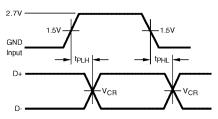

| $t_R$            | Rise Time                       | Figure 1       | 4                            |       | 20  |    |  |

| $t_{F}$          | Fall Time                       | Figure 1       | 4                            |       | 20  |    |  |

| t <sub>RFM</sub> | Rise/Fall Time Matching         | $(t_r/t_f)$    | 90                           |       | 110 | %  |  |

| V <sub>CRS</sub> | Output Signal Crossover Voltage |                | 1.3                          |       | 2.0 | V  |  |

|                  | DRIVER TIMINGS:                 |                | •                            |       |     | •  |  |

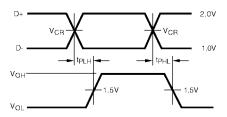

| t <sub>PLH</sub> | Driver Propagation Delay        | Figure 2       |                              |       | 18  | ns |  |

| t <sub>PLH</sub> | (VPO, VMO/FSEO to D+/D-)        | Figure 2       |                              |       | 18  | ns |  |

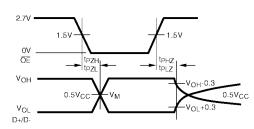

| t <sub>PHZ</sub> | Driver Disable Delay            | Figure 4       |                              |       | 13  | ns |  |

| t <sub>PLZ</sub> | (OE to D+/D-)                   | Figure 4       |                              |       | 13  | ns |  |

| t <sub>PZH</sub> | Driver Enable Delay             | Figure 4       |                              |       | 17  | ns |  |

| t <sub>PZL</sub> | (OE to D+/D-)                   | Figure 4       |                              |       | 17  | ns |  |

|                  | RECEIVER TIMINGS:               | ·              |                              |       |     |    |  |

| t <sub>PLH</sub> | Receiver Propagation Delay      | Figure 3       |                              |       | 16  | ns |  |

| t <sub>PHL</sub> | (D+, D- to RCV)                 | Figure 3       |                              |       | 19  | ns |  |

| t <sub>PLH</sub> | Single-ended Receiver Delay     | Figure 3       |                              |       | 8   | ns |  |

| t <sub>PHL</sub> | (D+, D- to VP, VM)              | Figure 3       |                              |       | 8   | ns |  |

## AC Electrical Characteristics (D+/D- Pins, Low Speed)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted).  $V_{CC}$  = 3.0V to 3.6V  $C_L$  = 200 pF to 600 pF;  $R_L$  = 1.5k $\Omega$  on D– to  $V_{CC}$

|                  |                                 |                 | Limits |      |     |    |

|------------------|---------------------------------|-----------------|--------|------|-----|----|

| Symbol           | Parameter                       | Test Conditions | Tan    | Unit |     |    |

|                  |                                 |                 | Min    | Тур  | Max |    |

|                  | DRIVER CHARACTERISTICS:         |                 | •      |      | •   |    |

|                  |                                 | 10% and 90%     |        |      |     |    |

| $t_{LR}$         | Rise Time                       | Figure 1        | 75     |      | 300 | ns |

| t <sub>LF</sub>  | Fall Time                       | Figure 1        | 75     |      | 300 |    |

| t <sub>RFM</sub> | Rise/Fall Time Matching         | $(t_r/t_f)$     | 80     |      | 120 | %  |

| V <sub>CRS</sub> | Output Signal Crossover Voltage |                 | 1.3    |      | 2.0 | V  |

|                  | DRIVER TIMINGS:                 | •               |        |      |     |    |

| t <sub>PLH</sub> | Driver Propagation Delay        | Figure 2        |        |      | 300 | ns |

| t <sub>PHL</sub> | (VPO, VMO/FSEO to D+/D-)        | Figure 2        |        |      | 300 | ns |

| t <sub>PHZ</sub> | Driver Disable Delay            | Figure 4        |        |      | 13  | ns |

| t <sub>PLZ</sub> | (OE to D+/D-)                   | Figure 4        |        |      | 13  | ns |

| t <sub>PZH</sub> | Driver Enable Delay             | Figure 4        |        |      | 205 | ns |

| t <sub>PZL</sub> | (OE to D+/D-)                   | Figure 4        |        |      | 205 | ns |

|                  | RECEIVER TIMINGS:               |                 | •      |      |     | •  |

| t <sub>PLH</sub> | Receiver Propagation Delay      | Figure 3        |        |      | 18  | ns |

| t <sub>PHL</sub> | (D+, D- to RCV)                 | Figure 3        |        |      | 18  | ns |

| t <sub>PLH</sub> | Single-ended Receiver Delay     | Figure 3        |        |      | 28  | ns |

| t <sub>PHL</sub> | (D+, D- to VP, VM)              | Figure 3        |        |      | 28  | ns |

## **AC Waveforms**

$V_{OL}$  and  $V_{OH}$  are the typical output voltage drops that occur with the output load. ( $V_{CC}$  never goes below 3.0V)

FIGURE 1. Rise and Fall Times

FIGURE 2. VPI, VMO/FSEO to D+/D-

FIGURE 3. D+/D- to RCV, VP/VM

FIGURE 4. OE to D+/D-

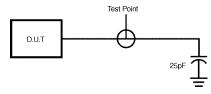

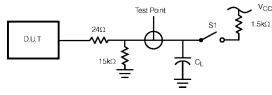

### **Test Circuits and Waveforms**

Load for VM/VP and RCV

Load for Enable and Disable Times

#### Note:

$V=0 \ for \ t_{PZH}, \ t_{PHZ}$

$V = \, V_{CC} \, for \, \, t_{PZL}, \, \, t_{PLZ}$

Load for D+/D-

$C_L$  = 50 pF, Full Speed

$C_L = 200 \text{ pF, Low Speed (Min Timing)}$

$C_L = 600 \text{ pF}$ , Low Speed (Max Timing)

1.5 k $\Omega$  on D– (Low Speed) or D+ (Full Speed) only

| Test  | S1    |

|-------|-------|

| D-/LS | Close |

| D+/LS | Open  |

| D-/FS | Open  |

| D+/FS | Close |

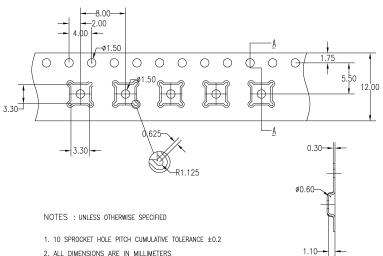

# Tape and Reel Specification Tape Format for MLP

| Tape Formation ML | F                  |           |        |            |

|-------------------|--------------------|-----------|--------|------------|

| Package           | Tape               | Number    | Cavity | Cover Tape |

| Designator        | Section            | Cavities  | Status | Status     |

|                   | Leader (Start End) | 125 (typ) | Empty  | Sealed     |

| BQX               | Carrier            | 2500      | Filled | Sealed     |

|                   | Trailer (Hub End)  | 75 (typ)  | Empty  | Sealed     |

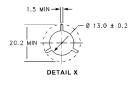

#### TAPE DIMENSIONS inches (millimeters)

- 2. ALL DIMENSIONS ARE IN MILLIMETERS

- 3. POCKET POSITION RELATIVE TO SPROCKET HOLE MEASURED AS TRUE POSITION OF POCKET, NOT POCKET HOLE

- 4. CAMBER IN COMPLIANCE WITH EIA 481

- 5. ADVANTEK PART DRAWING NUMBER ML0303-A

## <u>SECTION A - A</u>

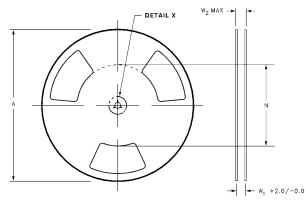

## REEL DIMENSIONS inches (millimeters)

| Tape Size | A<br>(mm) | N<br>(Typical)<br>(mm) | W1<br>(mm) | W2<br>(Max)<br>(mm) |

|-----------|-----------|------------------------|------------|---------------------|

| 12 mm     | 330       | 178                    | 12.4       | 18.4                |

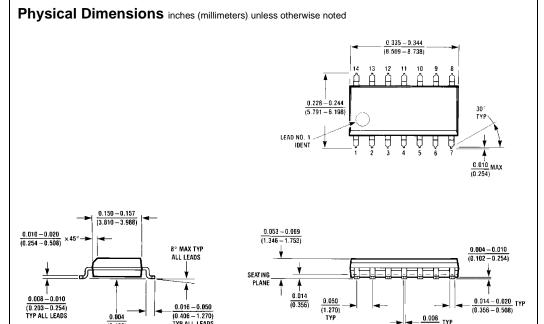

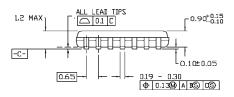

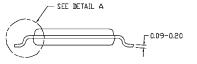

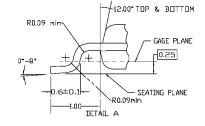

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Package Number M14A

0.016 - 0.050 (0.406 - 1.270) TYP ALL LEADS

0.004 (0.102) ALL LEAD TIPS

- (0.00B) TYP

M14A (REV H)

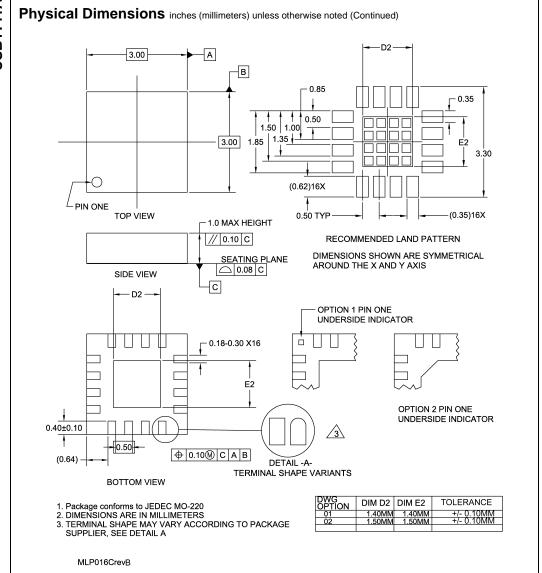

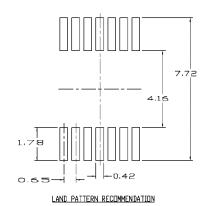

Pb-Free 16-Terminal Molded Leadless Package (MLP), JEDEC MO-220, 3mm square Package Number MLP16C

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

#### NOTES:

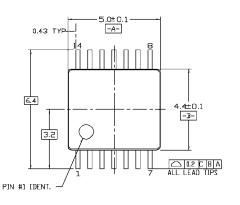

- A. CONFORMS TO JEDEC REGISTRATION MO-153, VARIATION AB., REF NOTE 6, DATED 7/93

- B. DIMENSIONS ARE IN MILLIMETERS

- C. DIMENSIONS ARE EXCLUSIVE DF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS

D. DIMENSIONING AND TOLERANCES PER ANSI Y14.5M, 1982

MTC14revD

14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC14

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com