SBOS200C - APRIL 2003 - REVISED MARCH 2004

# 8-Channel VARIABLE GAIN AMPLIFIER

### **FEATURES**

- 3V OPERATION

- LOW INPUT NOISE: 1.2nV $\sqrt{\text{Hz}}$  at  $f_{\text{IN}} = 5\text{MHz}$

- EXTREMELY LOW POWER OPERATION: 75mW/CHANNEL

- INTEGRATED LOW-PASS, 2-POLE FILTER

14MHz BANDWIDTH

- INTEGRATED INPUT CLAMP DIODES

- DIFFERENTIAL OUTPUT

- INTEGRATED INPUT LNA

- READABLE CONTROL REGISTERS

- INTEGRATED CONTINUOUS WAVE (CW) PROCESSOR

### **DESCRIPTION**

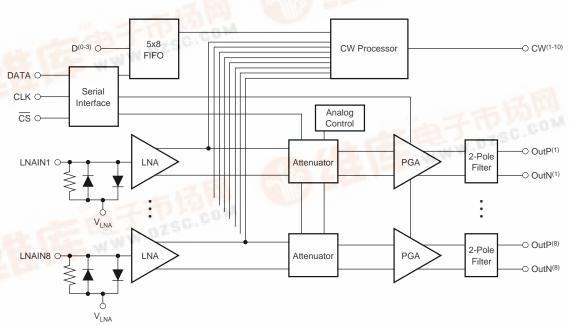

The VCA8613 is an 8-channel variable gain amplifier ideally suited to portable ultrasound applications. Excellent dynamic performance enables use in low-power, high-performance portable applications. Each channel consists of a Low-Noise pre-Amplifier (LNA) and a Variable Gain Amplifier (VGA). The differential outputs of the LNA can be switched through the 8x10 cross-point switch, which is programmable through the serial interface input port.

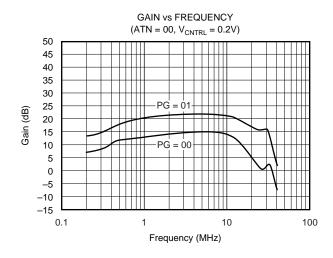

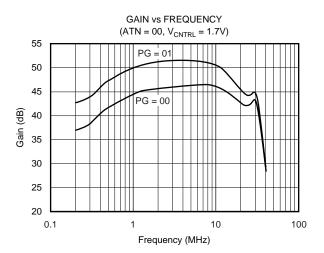

The output of the LNA is fed directly into the VGA stage. The VGA consists of two parts, a Voltage Controlled Attenuator (VCA) and a Programmable Gain Amplifier (PGA). The gain and

gain range of the PGA can be digitally configured separately. The gain of the PGA can be varied between two discrete settings of 21dB and 26dB. The VCA has four programmable maximum attenuation settings: 29dB, 33dB, 36.5dB, and 40dB. Also, the VCA can be continuously varied by a control voltage from 0dB to a maximum of 29dB, 33dB, 36.5dB, and 40dB.

The output of the PGA feeds directly into an integrated 2-pole, low-pass filter, allowing for direct connection to a differential input Analog-to-Digital Converter (ADC), such as the ADS5121 or ADS5122 from Texas Instruments. The VCA8613 is available in a TQFP-64 package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All tracemarks are the property of their respective owners.

#### ABSOLUTE MAXIMUM RATINGS(1)

| +AV <sub>DD</sub>                                        | +3.6V                       |

|----------------------------------------------------------|-----------------------------|

| Analog Input                                             | $0.3V$ to $+AV_{DD} + 0.3V$ |

| Logic Input                                              | $0.3V$ to $+AV_{DD} + 0.3V$ |

| Case Temperature                                         | +100°C                      |

| Junction Temperature                                     | +150°C                      |

| Storage Temperature                                      | +150°C                      |

| Thermal Resistance, Juction-to-Ambient $(\theta_{JA})$   | 66.6°C/W                    |

| Thermal Resistance, Junction-to-Case $(\theta_{\rm JC})$ | 4.3°C/W                     |

|                                                          |                             |

NOTE: (1) Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION(1)

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|--------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| VCA8613 | TQFP-64      | PAG                   | -40°C to +85°C                    | VCA8613Y           | VCA8613YT          | Tape and Reel, 250           |

| "       | "            | "                     | II                                | =                  | VCA8613YR          | Tape and Reel, 1500          |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet.

1/040040

## ELECTRICAL CHARACTERISTICS: $AV_{DD} = 3V$

At  $T_A = +25^{\circ}C$ , load resistance =  $500\Omega$  on each output to ground, unless otherwise noted. The input to the preamp (LNA) is single-ended, pre-amp gain is fixed at +24.5dB,  $f_{IN} = 2MHz$ , PG = 01, and the output from the VCA is differential unless otherwise noted.

|                                                                                                                                                                                                                                                                       |                                                                                        |                 | VCA8613                                               |                                     |                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                             | CONDITIONS                                                                             | MIN             | TYP                                                   | MAX                                 | UNITS                                                                    |

| PREAMPLIFIER Input Resistance Input Capacitance Input Bias Current Maximum Input Voltage <sup>(1)</sup> Input Voltage Noise (TGC) Input Voltage Noise (CW) Output Swing (Differential) Bandwidth Gain                                                                 | f <sub>IN</sub> = 5MHz<br>f <sub>IN</sub> = 5MHz                                       |                 | 4.5<br>80<br>1<br>110<br>1.2<br>1.6<br>2<br>70<br>25  |                                     | kΩ<br>pF<br>nA<br>mV <sub>pp</sub><br>nV/√Hz<br>nV/√Hz<br>V<br>MHz<br>dB |

| ACCURACY Gain Slope Gain Error Output Offset Voltage                                                                                                                                                                                                                  | 0.2V – 1.7V, VCA <sub>CNTRL</sub><br>0.2V – 1.7V, VCA <sub>CNTRL</sub><br>Differential |                 | 20<br>20                                              | 2                                   | dB/V<br>dB<br>mV                                                         |

| GAIN CONTROL INTERFACE Input Voltage (VCA <sub>CNTRL</sub> ) Range Input Resistance Response Time                                                                                                                                                                     | 40dB Gain Change, PG = 11                                                              |                 | 0 to 2.0<br>1<br>0.2                                  |                                     | V<br>MΩ<br>μs                                                            |

| POWER SUPPLY Specified Operating Range Power-Down Delay Power-Up Delay Power Dissipation (TGC Mode)                                                                                                                                                                   | Operating All Channels                                                                 | 2.85            | 3.0<br>5<br>20<br>600                                 | 3.15<br>700                         | V<br>μs<br>μs<br>mW                                                      |

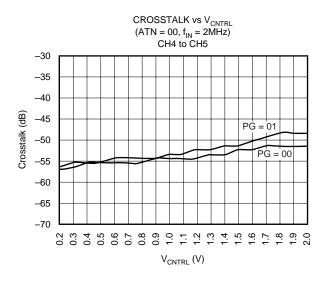

| PROGRAMMABLE VGA AND LOW-PASS FILTER  -3dB Cutoff (low-pass)  -3dB Cutoff (high-pass)  Slew Rate  Output Impedance  Crosstalk  Output Common-Mode  Output Swing (Differential) <sup>(2)</sup> 3rd-Harmonic Distortion  2nd-Harmonic Distortion  Group Delay Variation |                                                                                        |                 | 12<br>800<br>300<br>10<br>49<br>1<br>-65<br>-65<br>±3 | 2<br>-50<br>-50                     | MHz<br>kHz<br>V/μs<br>Ω<br>dB<br>V<br>V <sub>PP</sub><br>dB<br>dB        |

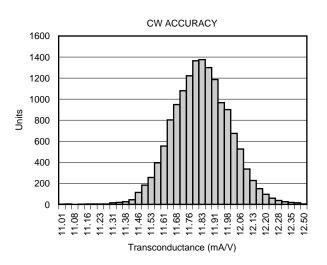

| CONTINUOUS WAVE PROCESSOR CW Output Compliance Voltage V/I Converter Transconductance Maximum CW Output Current                                                                                                                                                       |                                                                                        | 3<br>10.35      | 11.5<br>2.0                                           | 3.3<br>12.65                        | V<br>mA/V<br>mA                                                          |

| LOGIC INPUTS  V <sub>IN</sub> LOW (input low voltage)  V <sub>IN</sub> HIGH (input high voltage) Input Current Input Pin Capacitance Clock Input Frequency                                                                                                            |                                                                                        | 0<br>2.1<br>10k | 5                                                     | 0.6<br>V <sub>DD</sub><br>±1<br>25M | V<br>V<br>μA<br>pF<br>Hz                                                 |

NOTES: (1) Under conditions that input signal is within linear range of LNA. (2) Under conditions that signal is within linear range of output amplifier.

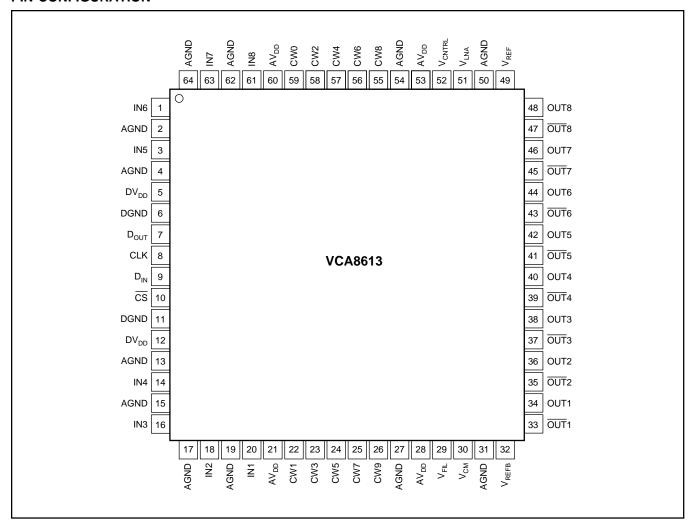

### **PIN CONFIGURATION**

### **PIN DESCRIPTIONS**

| PIN                                          | DESIGNATOR           | DESCRIPTION                                                                            |

|----------------------------------------------|----------------------|----------------------------------------------------------------------------------------|

| 5, 12                                        | DV <sub>DD</sub>     | Digital Supplies                                                                       |

| 2, 4, 13, 15, 17, 19, 27, 31, 50, 54, 62, 64 | AGND                 | Analog Ground                                                                          |

| 1, 3, 14, 16, 18, 20, 61, 63                 | IN <sup>(1-8)</sup>  | Single-Ended LNA Inputs                                                                |

| 22-26, 55-59                                 | CW <sup>(0-9)</sup>  | Continuous Wave Outputs                                                                |

| 51                                           | $V_{LNA}$            | Reference Voltage For LNA—Internally Generated; Requires External Bypass Cap           |

| 29                                           | V <sub>FIL</sub>     | Reference Voltage for Output Filter—Internally Generated; Requires External Bypass Cap |

| 30                                           | V <sub>CM</sub>      | Common-Mode Voltage—Internally Generated; Requires External Bypass Cap                 |

| 34, 36, 38, 40, 42, 44, 46, 48               | OUT <sup>(1-8)</sup> | Positive Polarity PGA Outputs                                                          |

| 33, 35, 37, 39, 41, 43, 45, 47               | OUT <sup>(1-8)</sup> | Negative Polarity PGA Outputs                                                          |

| 52                                           | V <sub>CNTRL</sub>   | Attenuator Control Input                                                               |

| 9                                            | D <sub>IN</sub>      | Serial Data Input Pin                                                                  |

| 10                                           | CS                   | Serial Data Chip Select                                                                |

| 8                                            | CLK                  | Serial Data Input Clock                                                                |

| 7                                            | D <sub>OUT</sub>     | Serial Data Output Pin                                                                 |

| 21, 28, 53, 60                               | $AV_{DD}$            | Analog Supplies                                                                        |

| 6, 11                                        | DGND                 | Digital Ground                                                                         |

| 49                                           | $V_{REF}$            | Reference Voltage for Attenuator—Internally Generated; Requires External Bypass        |

| 32                                           | $V_{REFB}$           | Bandgap Reference Voltage—Internally Generated; Requires External Bypass Cap           |

### **INPUT REGISTER BIT MAPS**

### Byte 1—Control Byte Register Map

| BIT# | NAME     | DESCRIPTION                                                                             |

|------|----------|-----------------------------------------------------------------------------------------|

| LSB  | 1        | Start Bit Always a "1"—40-bit count-down starts upon first "1" after chip select.       |

| 1    | W/R      | 1 = Write, 0 = Read—Read prevents latching of DATA only—Control register still latched. |

| 2    | $P_{WR}$ | Entire Chip. Power Control—1 = Off—Otherwise chip is on.                                |

| 3    | A0       | Attenuator Control Bit                                                                  |

| 4    | A1       | Attenuator Control Bit                                                                  |

| 5    | Mode     | 1 = TGC Mode (CW Powered Down), 0 = CW Doppler Mode (TGC Powered Down)                  |

| 6    | PG0      | LSB of PGA Gain Control                                                                 |

| MSB  | PG1      | MSB of PGA Gain Control                                                                 |

### Byte 2—First Data Byte

| BIT# | NAME     | DESCRIPTION                      |

|------|----------|----------------------------------|

| LSB  | Data 1:0 | Channel 1, LSB of Matrix Control |

| 1    | Data 1:1 | Channel 1, Matrix Control        |

| 2    | Data 1:2 | Channel 1, Matrix Control        |

| 3    | Data 1:3 | Channel 1, MSB of Matrix Control |

| 4    | Data 2:0 | Channel 2, LSB of Matrix Control |

| 5    | Data 2:1 | Channel 2, Matrix Control        |

| 6    | Data 2:2 | Channel 2, Matrix Control        |

| MSB  | Data 2:3 | Channel 2, MSB of Matrix Control |

### Byte 3—Second Data Byte

| BIT# | NAME     | DESCRIPTION                      |

|------|----------|----------------------------------|

| LSB  | Data 3:0 | Channel 3, LSB of Matrix Control |

| 1    | Data 3:1 | Channel 3, Matrix Control        |

| 2    | Data 3:2 | Channel 3, Matrix Control        |

| 3    | Data 3:3 | Channel 3, MSB of Matrix Control |

| 4    | Data 4:0 | Channel 4, Matrix Control        |

| 5    | Data 4:1 | Channel 4, Matrix Control        |

| 6    | Data 4:2 | Channel 4, Matrix Control        |

| MSB  | Data 4:3 | Channel 4, MSB of Matrix Control |

### Byte 4—Third Data Byte

| BIT # | NAME     | DESCRIPTION                      |

|-------|----------|----------------------------------|

| LSB   | Data 5:0 | Channel 5, LSB of Matrix Control |

| 1     | Data 5:1 | Channel 5, Matrix Control        |

| 2     | Data 5:2 | Channel 5, Matrix Control        |

| 3     | Data 5:3 | Channel 5, MSB of Matrix Control |

| 4     | Data 6:0 | Channel 6, Matrix Control        |

| 5     | Data 6:1 | Channel 6, Matrix Control        |

| 6     | Data 6:2 | Channel 6, Matrix Control        |

| MSB   | Data 6:3 | Channel 6, MSB of Matrix Control |

### Byte 5—Fourth Data Byte

| BIT# | NAME     | DESCRIPTION                      |

|------|----------|----------------------------------|

| LSB  | Data 7:0 | Channel 7, LSB of Matrix Control |

| 1    | Data 7:1 | Channel 7, Matrix Control        |

| 2    | Data 7:2 | Channel 7, Matrix Control        |

| 3    | Data 7:3 | Channel 7, MSB of Matrix Control |

| 4    | Data 8:0 | Channel 8, Matrix Control        |

| 5    | Data 8:1 | Channel 8, Matrix Control        |

| 6    | Data 8:2 | Channel 8, Matrix Control        |

| MSB  | Data 8:3 | Channel 8, MSB of Matrix Control |

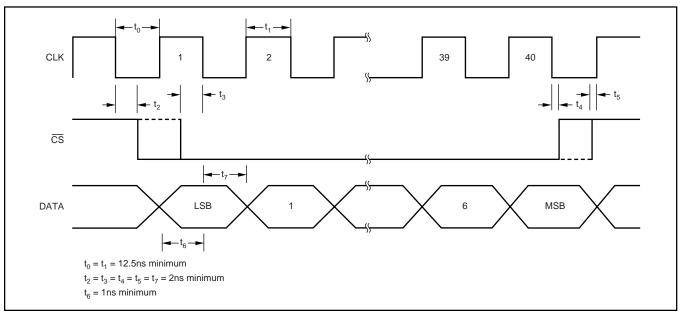

#### WRITE/READ TIMING

Generally follows SPI Timing Specification:

- All writes and reads will be 8 bytes at a time;

- · Separate write and read data lines;

- · Reads will follow the same bit stream pattern seen in the write cycle;

- · Reads will extract data from the FIFO, not the latched register;

- D<sub>OUT</sub> data is continuously available and need not be enabled with a read cycle. Selecting a read cycle in the control register *only* prevents latching of data. The control register is still latched.

### WRITE CYCLE TIMING

NOTE: It is highly recommended that the clock be turned off after the required data has been programmed into the VCA8613.

### **SERIAL PORT TIMING TABLE**

Chip Select  $(\overline{CS})$  must be held low (active LOW) during transfer.  $\overline{CS}$  can be held permanently low.

| PARAMETER      | DESCRIPTION                                | MIN | TYP | MAX | UNITS |

|----------------|--------------------------------------------|-----|-----|-----|-------|

| t <sub>1</sub> | Serial CLK Period                          | 40  |     |     | ns    |

| t <sub>2</sub> | Serial CLK HIGH Time                       | 13  |     |     | ns    |

| t <sub>3</sub> | Serial CLK LOW Time                        | 13  |     |     | ns    |

| t <sub>4</sub> | CS Falling Edge to Serial CLK Falling Edge | 10  |     |     | ns    |

| t <sub>5</sub> | Data Setup Time                            | 5   |     |     | ns    |

| t <sub>6</sub> | Data Hold Time                             | 5   |     |     | ns    |

| t <sub>7</sub> | Serial CLK Falling Edge to CS Rising Edge  | 10  |     |     | ns    |

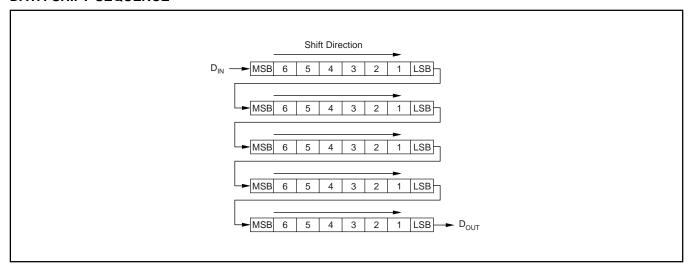

### **DATA SHIFT SEQUENCE**

| A1, A0 | MAXIMUM ATTENUATION |

|--------|---------------------|

| 0, 0   | 29dB                |

| 0, 1   | 33dB                |

| 1, 0   | 36.5dB              |

| 1, 1   | 40dB                |

| PG1, PG0 | PGA GAIN |

|----------|----------|

| 0, 0     | 21dB     |

| 0, 1     | 26dB     |

TABLE II. PGA Gain Settings.

TABLE I. Maximum Attenuation.

| CHANNEL                       | CW CODING<br>(MSB, LSB) | CHANNEL DIRECTED TO:          |  |  |

|-------------------------------|-------------------------|-------------------------------|--|--|

| 0                             | 0000                    | Output 0                      |  |  |

| 1                             | 0001                    | Output 1                      |  |  |

| 2                             | 0010                    | Output 2                      |  |  |

| 3                             | 0011                    | Output 3                      |  |  |

| 4                             | 0100                    | Output 4                      |  |  |

| 5                             | 0101                    | Output 5                      |  |  |

| 6                             | 0110                    | Output 6                      |  |  |

| 7                             | 0111                    | Output 7                      |  |  |

| 8                             | 1000                    | Output 8                      |  |  |

| 9                             | 1001                    | Output 9                      |  |  |

| 10                            | 1010                    | Channel Tied to +V (internal) |  |  |

| 11                            | 1011                    | Channel Tied to +V (internal) |  |  |

| 12                            | 1100                    | Channel Tied to +V (internal) |  |  |

| 13                            | 1101                    | Channel Tied to +V (internal) |  |  |

| 14                            | 1110                    | Channel Tied to +V (internal) |  |  |

| 15                            | 1111                    | Channel Tied to +V (internal) |  |  |

| Applies to bytes 2 through 5. |                         |                               |  |  |

TABLE III. CW Coding for Each Channel.

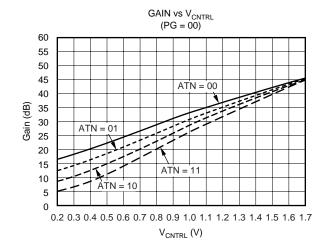

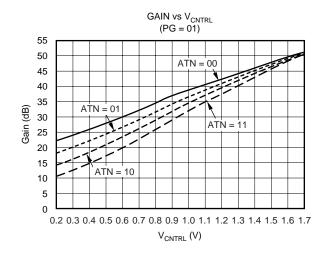

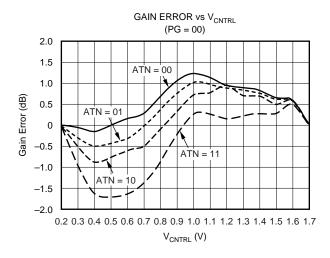

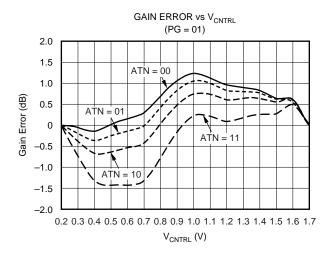

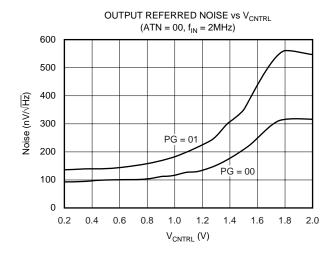

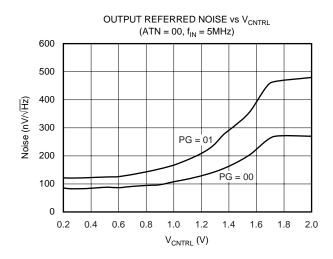

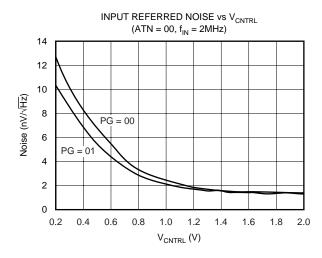

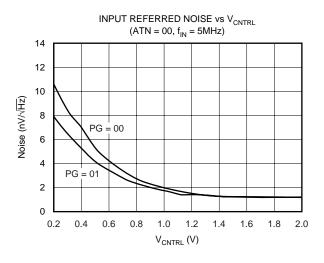

### TYPICAL CHARACTERISTICS

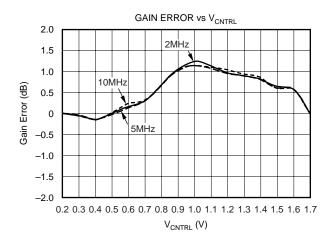

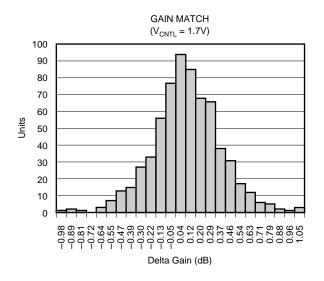

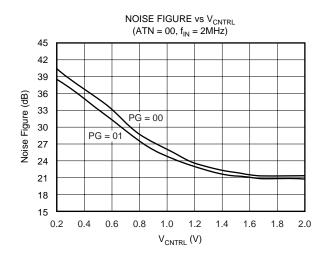

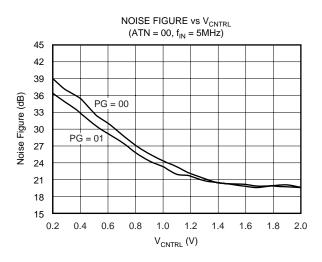

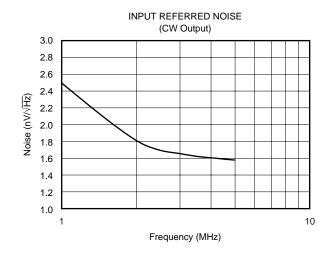

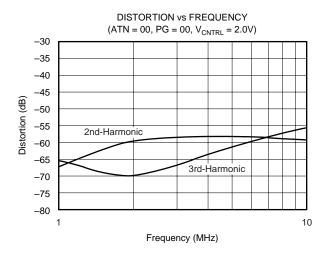

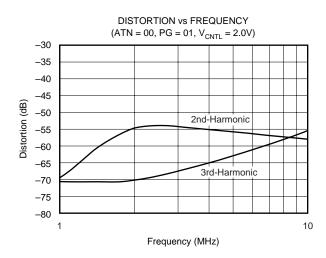

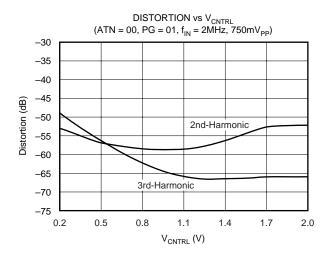

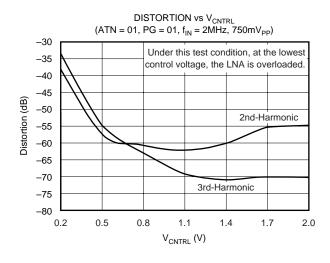

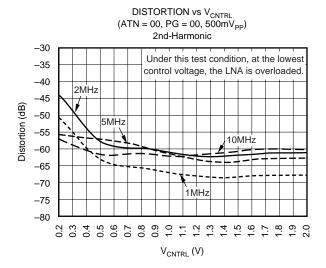

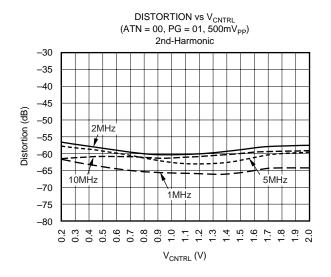

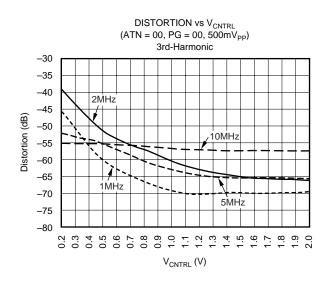

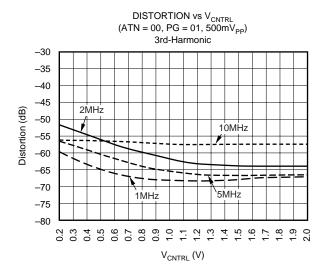

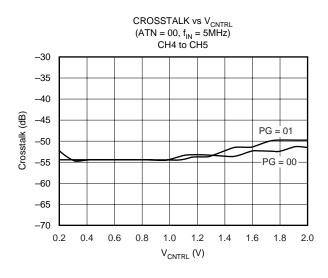

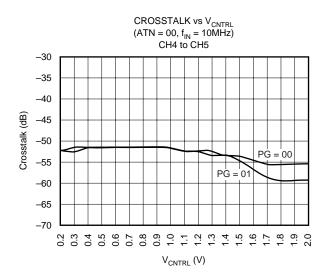

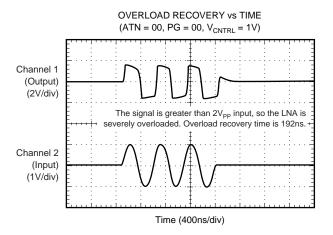

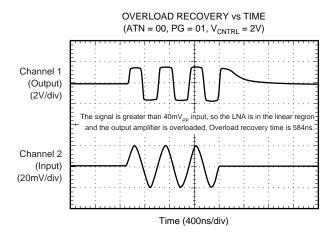

At  $T_A = +25^{\circ}C$ ,  $f_{IN} = 2MHz$ ,  $AT_N = 00$ , PG = 01,  $V_{CNTRL} = 1.7V$ , unless otherwise noted. Differential output,  $750mV_{PP}$ , and  $AV_{DD} = DV_{DD} = 3.0V$ .

.....

At  $T_A = +25^{\circ}C$ ,  $f_{IN} = 2MHz$ ,  $AT_N = 00$ , PG = 01,  $V_{CNTRL} = 1.7V$ , unless otherwise noted. Differential output,  $750mV_{PP}$ , and  $AV_{DD} = DV_{DD} = 3.0V$ .

....

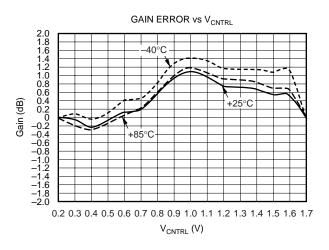

At  $T_A = +25^{\circ}C$ ,  $f_{IN} = 2MHz$ ,  $AT_N = 00$ , PG = 01,  $V_{CNTRL} = 1.7V$ , unless otherwise noted. Differential output,  $750mV_{PP}$ , and  $AV_{DD} = DV_{DD} = 3.0V$ .

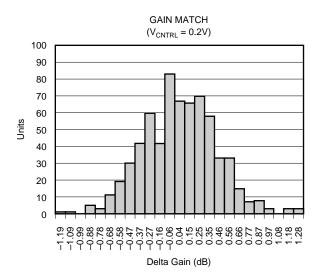

At  $T_A = +25^{\circ}C$ ,  $f_{IN} = 2MHz$ ,  $AT_N = 00$ , PG = 01,  $V_{CNTRL} = 1.7V$ , unless otherwise noted. Differential output,  $750mV_{PP}$ , and  $AV_{DD} = DV_{DD} = 3.0V$ .

.....

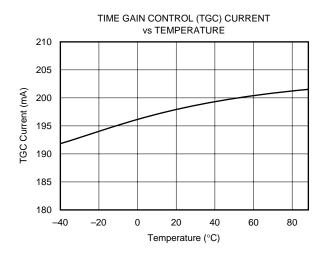

At  $T_A = +25^{\circ}C$ ,  $f_{IN} = 2MHz$ ,  $AT_N = 00$ , PG = 01,  $V_{CNTRL} = 1.7V$ , unless otherwise noted. Differential output,  $750mV_{PP}$ , and  $AV_{DD} = DV_{DD} = 3.0V$ .

At  $T_A = +25^{\circ}C$ ,  $f_{IN} = 2MHz$ ,  $AT_N = 00$ , PG = 01,  $V_{CNTRL} = 1.7V$ , unless otherwise noted. Differential output,  $750mV_{PP}$ , and  $AV_{DD} = DV_{DD} = 3.0V$ .

### APPLICATION INFORMATION

#### **INPUT CIRCUIT**

The input of the VCA8613 integrates several commonly used elements. Prior to reaching the input of the VCA, the receive signal should be coupled with a capacitor of at least 1nF, preferably more. When this AC coupling element is inserted, the LNA input bias point is held to a common-mode value of 2.4V by an integrated 4.5k $\Omega$  resistor. This common-mode value will change with temperature and may also vary from chip to chip, but for each chip, it will be held constant. In parallel with this resistor are two back-to-back clipping diodes. These diodes prevent excessive input voltages from passing through to the LNA input, preventing deep saturation effects in the LNA itself.

#### LOW-NOISE PRE-AMPLIFIER (LNA)

The VCA8613 integrates a low-noise pre-amplifier. Because of the high level of integration in the system, noise performance was traded for power consumption, resulting in an extremely low-power pre-amplifier, with 1.2nV/\dot{Hz} noise performance at 5MHz. The LNA is configured as a fixed-gain 25dB amplifier. Of this total gain, 6dB results from the single-ended to differential conversion accomplished within the LNA itself. The output of the LNA is limited to a little over 2V differential swing. This implies a maximum input voltage swing of approximately 110mV to be operating in the linear range at 5MHz. Larger input signals can be accepted by the LNA, but distortion performance will degrade with high-level input signals.

#### **CW DOPPLER PROCESSOR**

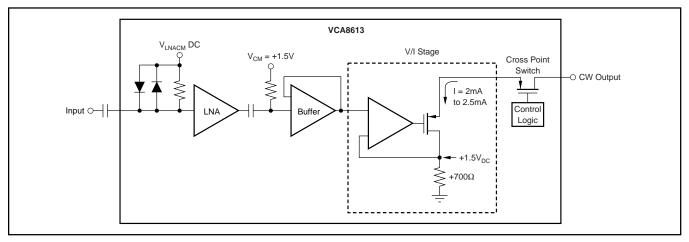

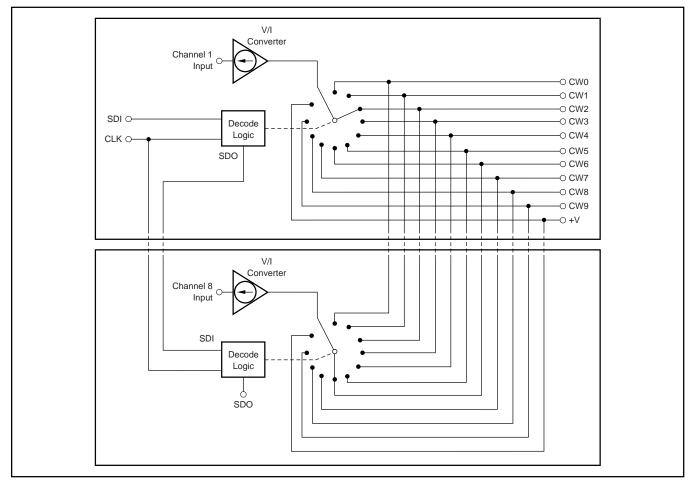

The VCA8613 integrates many of the elements necessary to allow for the implementation of a simple CW Doppler processing circuit. One circuit that was integrated was a V/I converter following the LNA (see Figure 1). The V/I converter converts the LNA voltage output to a current which is then passed through an 8x10 switch matrix (see Figure 2). Within this switch matrix, any of the eight LNA outputs can be connected to any of ten CW output pins. This is a simple current-summing circuit such that each CW output can represent the sum of any or all the channel currents. The output current for each LNA is equal to the single-ended LNA output voltage swing divided by an internally integrated  $700\Omega$  resistor. This resistor value may change  $\pm 5\%$  from chip to chip.

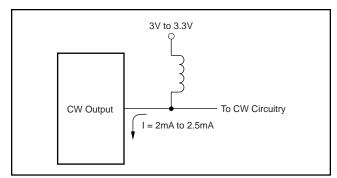

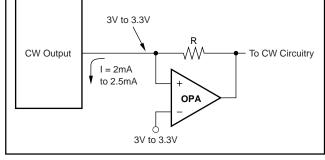

The CW output pins need a compliance voltage between 3V to 3.3V. The 3V to 3.3V can be applied through either an inductor (see Figure 3) tied to the 3V to 3.3V source or from the inverting input of an op amp circuit (see Figure 4). The architecture of the V/I converter requires a 2mA to 2.5mA current that is generated by the compliance voltage.

The CW outputs are typically routed to a passive delay line, allowing coherent summing of the signals. After summing, IQ separation and down conversion to base-band precedes a pair of high-resolution, low sample rate ADCs.

....

FIGURE 1. Basic CW Processing Block Diagram.

FIGURE 2. Basic CW Cross Point Switch Matrix for All Eight Channels.

FIGURE 3. Inductor. FIGURE 4. Op Amp.

#### **VOLTAGE-CONTROLLED ATTENUATOR (VCA)—DETAIL**

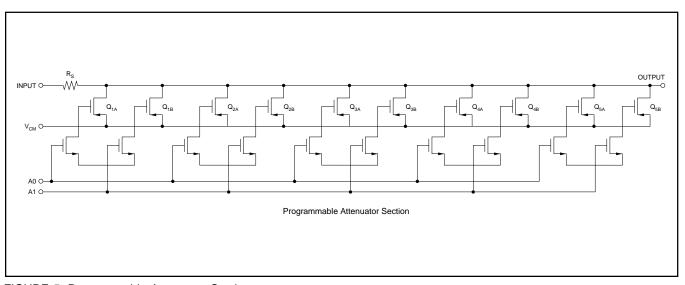

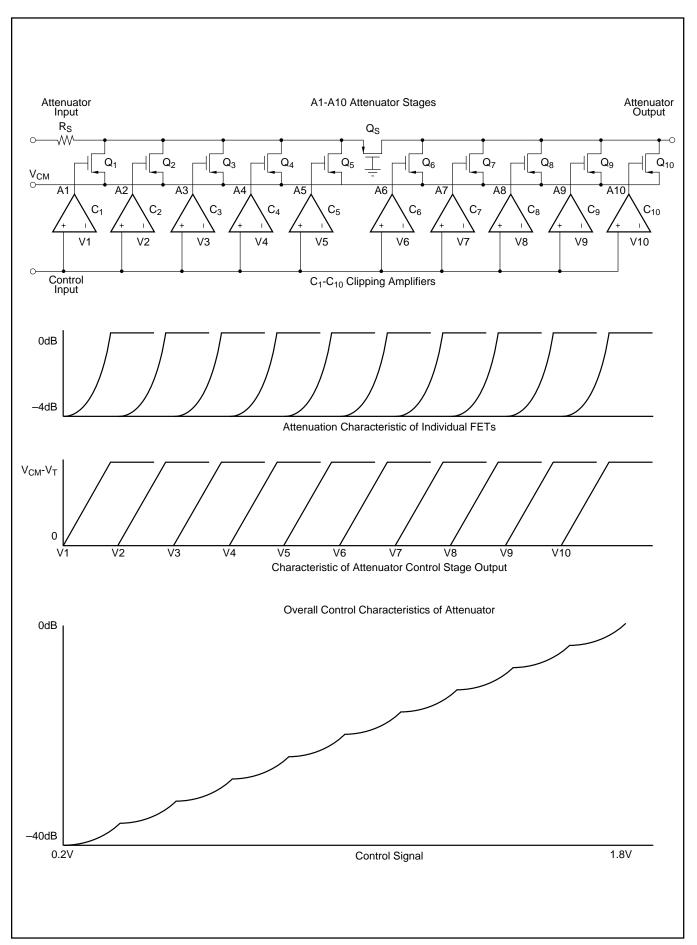

The VCA is designed to have a dB-linear attenuation characteristic; that is, the gain loss in dB is constant for each equal increment of the VCA<sub>CNTRL</sub> control voltage. Figure 5 shows a block diagram of the VCA. The attenuator is essentially a variable voltage divider consisting of one series input resistor, R<sub>S</sub>, and ten identical shunt FETs, placed in parallel and controlled by sequentially-activated clipping amplifiers. Each clipping amplifier can be thought of as a specialized voltage comparator with a soft transfer characteristic and well-controlled output limit voltages. The reference voltages V1 through V10 are equally spaced over the 0V to 1.8V control voltage range. As the control voltage rises through the input range of each clipping amplifier, the amplifier output will rise from 0V (FET completely ON) to  $V_{CM} - V_{T}$  (FET nearly OFF), where  $V_{CM}$  is the common source voltage and  $V_{T}$  is the threshold voltage of the FET. As each FET approaches its OFF state and the control voltage continues to rise, the next clipping amplifier/FET combination takes over for the next portion of the piecewise-linear attenuation characteristic. Thus, low control voltages have most of the FETs turned ON, while high control voltages have most turned OFF. Each FET acts to decrease the shunt resistance of the voltage divider formed by R<sub>S</sub> and the parallel FET network.

The attenuator is comprised of two sections, with five parallel clipping amplifier/FET combinations in each. Special reference circuitry is provided so that the  $(V_{CM}-V_T)$  limit voltage will track temperature and IC process variations, minimizing the effects on the attenuator control characteristic.

In addition to the analog VCA<sub>CNTRL</sub> gain setting input, the attenuator architecture provides digitally-programmable adjustment in eight steps, via the two attenuation bits. These adjust the maximum achievable gain (corresponding to minimum attenuation in the VCA, with VCA<sub>CNTRL</sub> = 1.8V) in 5dB increments. This function is accomplished by providing multiple FET sub-elements for each of the  $Q_1$  to  $Q_{10}$  FET shunt elements (see Figure 6). In the simplified diagram of

Figure 5, each shunt FET is shown as two sub-elements,  $Q_{NA}$  and  $Q_{NB}$ . Selector switches, driven by the MGS bits, activate either or both of the sub-element FETs to adjust the maximum  $R_{ON}$  and thus achieve the stepped attenuation options.

The VCA can be used to process either differential or singleended signals. Fully differential operation will reduce 2ndharmonic distortion by about 10dB for full-scale signals.

Input impedance of the VCA will vary with gain setting, due to the changing resistances of the programmable voltage divider structure. At large attenuation factors (that is, low gain settings), the impedance will approach the series resistor value of approximately  $120\Omega$ .

As with the LNA stage, the VCA output is AC-coupled into the PGA. This means that the attenuation-dependent DC common-mode voltage will not propagate into the PGA, and so the PGA's DC output level will remain constant.

Finally, note that the VCA<sub>CNTRL</sub> input consists of FET gate inputs. This provides very high impedance and ensures that multiple VCA8613 devices may be connected in parallel with no significant loading effects. The nominal voltage range for the VCA<sub>CNTRL</sub> input spans from 0V to 1.8V. Overdriving this input (> 3V) does not affect the performance.

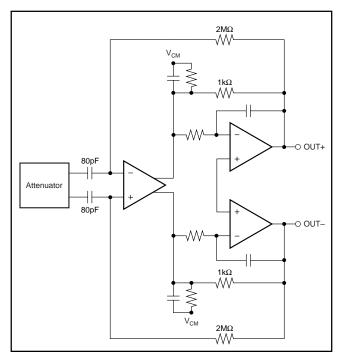

#### PGA POST-AMPLIFIER

Figure 7 shows a simplified circuit diagram of the PGA block. PGA gain is programmed through the serial port, and can be configured to 2 different gain settings of 21dB and 26dB, as shown in Table III. A patented circuit has been implemented in the PGA that allows for exceptional overload signal recovery.

| PGA | GAIN |

|-----|------|

| 00  | 21   |

| 01  | 26   |

TABLE III. PGA Gain Settings.

FIGURE 5. Programmable Attenuator Section.

FIGURE 6. Piecewise Approximation to Logarithmic Control Characteristics.

FIGURE 7. Simplified PGA and Output Filter Circuit.

#### **OUTPUT FILTER**

The VCA8613 integrates a 2-pole low-pass Butterworth filter in the output stage, as shown in Figure 7. The cutoff frequency is implemented with passive semiconductor elements and as such, the cutoff frequency will not be precise. Table IV shows the cutoff frequency for the different PGA settings.

The variation shown in Table IV reflects deviations as measured from chip to chip and over the specified temperature range.

| PGA | BANDWIDTH      |  |

|-----|----------------|--|

| 00  | 13MHz to 14MHz |  |

| 01  | 11MHz to 12MHz |  |

TABLE IV. Cutoff Frequency for PGA Settings.

#### **SERIAL INTERFACE**

The serial interface of the VCA8613 allows the user flexibility in the use of the part. The following are set from the serial control registers:

- Mode

- TGC Mode

- · CW Mode

- Attenuation Range

- PGA Gain

- Power-Down (this is the default state in which the VCA8613 powers up)

- · CW Output Selection For Each Input Channel

The serial interface uses an SPI style of interface format. The Input Register Bit Maps (see page 5) show the functionality of each control register.

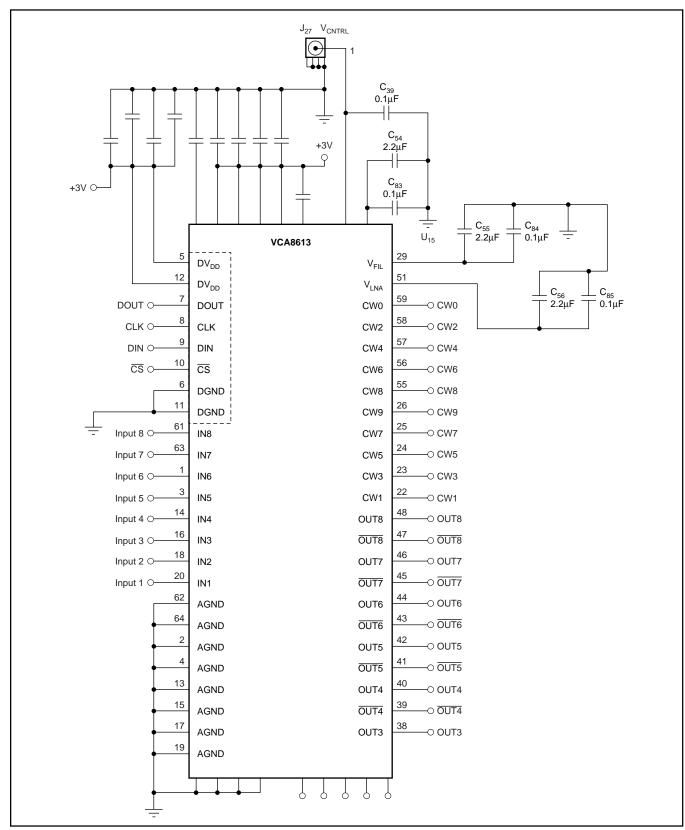

#### LAYOUT CONSIDERATIONS

The VCA8613 is a multi-channel amplifier capable of high gains that has integrated digital controls. Layout of the VCA8613 is fairly straightforward. By connecting all of the grounds (including the digital grounds) to the analog ground, noise performance will help to be maintained. The analog ground should be a solid plane.

Power-supply decoupling and decoupling of the control voltage (VCA<sub>CNTRL</sub>) pin are essential in order to ensure that the noise performance be maintained. For further help in determining basic values, please refer to Figure 8.

FIGURE 8. Basic Connection Diagram.

### **PACKAGE OPTION ADDENDUM**

30-Mar-2004

### **PACKAGING INFORMATION**

| ORDERABLE DEVICE | STATUS(1) | PACKAGE TYPE | PACKAGE DRAWING | PINS | PACKAGE QTY |

|------------------|-----------|--------------|-----------------|------|-------------|

| VCA8613YR        | ACTIVE    | TQFP         | PAG             | 64   | 1500        |

| VCA8613YT        | ACTIVE    | TQFP         | PAG             | 64   | 250         |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs. **LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

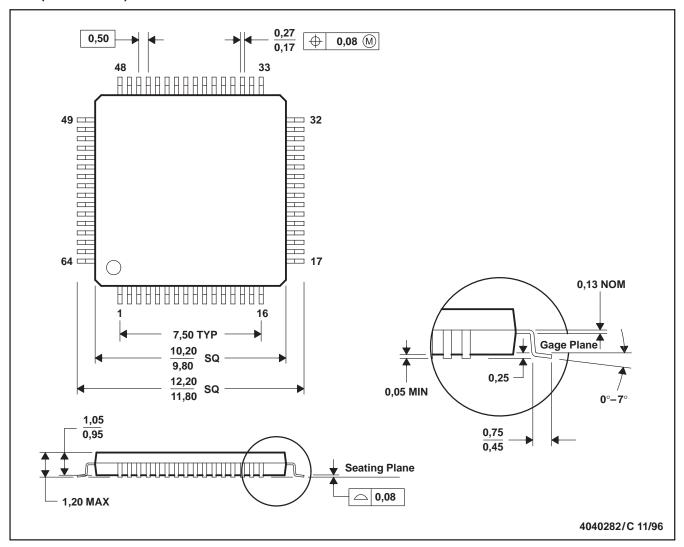

### PAG (S-PQFP-G64)

### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-026

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265