# 捷多邦,专业PCB打样工厂,24小时**SN74生**VCE161284 19-BIT IEEE 1284 TRANSLATION TRANSCEIVER WITH ERROR-FREE POWER UP

SCES541 - JANUARY 2004

- Auto-Power-Up Feature Prevents Printer

Errors When Printer Is Turned On, But No

Valid Signal Is at A9–A13 Pins

- 1.4-kΩ Pullup Resistors Integrated on All Open-Drain Outputs Eliminate the Need for Discrete Resistors

- Designed for the IEEE Std 1284-I (Level-1 Type) and IEEE Std 1284-II (Level-2 Type) Electrical Specifications

- Flow-Through Architecture Optimizes PCB Layout

- Ioff and Power-Up 3-State Support Hot

Insertion

- Latch-Up Performance Exceeds 100 mA Per JESD 78. Class II

- ESD Protection

- ±4 kV Human-Body Model

- ±8 kV IEC 61000-4-2, Contact Discharge (Connector Pins)

- ±15 kV IEC 61000-4-2, Air-Gap Discharge (Connector Pins)

- ±15 kV Human-Body Model (Connector Pins)

### description/ordering information

The SN74LVCE161284 is designed for 3-V to 3.6-V V<sub>CC</sub> operation. This device provides asynchronous two-way communication between data buses. The control-function implementation minimizes external timing requirements.

DGG OR DL PACKAGE (TOP VIEW) 48 DIR HD [ 47 Y9 A9 2 46 Y10 A10 3 A11 [ 4 45 Y11 44**∏** Y12 A12 5 A13 🛮 6 43**∏** Y13 V<sub>CC</sub> **□** 7 42 V<sub>CC</sub> CABLE A1 ∏8 41 ∏ B1 40 B2 A2 🛮 9 GND 10 39 GND 38 **∏** B3 A3 | 11 37 B4 A4 1 12 A5 [ 13 36 B5 A6 14 35 B6 34 | GND GND 15 33 B7 А7 П 16 A8 **∏** 17 32 **∏** B8 V<sub>CC</sub> 18 31 V<sub>CC</sub> CABLE PERI LOGIC IN 19 30 PERI LOGIC OUT A14 ∏20 29 ∏ C14 A15 🛮 21 28 C15 A16 **∏** 22 27 C16 A17 🛮 23 26 C17 HOST LOGIC OUT [] 24 25 HOST LOGIC IN

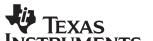

This device has eight bidirectional bits; data can flow in the A-to-B direction when the direction-control input (DIR) is high and in the B-to-A direction when DIR is low. This device also has five drivers that drive the cable side, and four receivers. The SN74LVCE161284 has one receiver dedicated to the HOST LOGIC line and a driver to drive the PERI LOGIC line.

### **ORDERING INFORMATION**

| TA          | PACKAGE <sup>†</sup> |               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|-------------|----------------------|---------------|--------------------------|---------------------|

|             | SSOP – DL            |               | SN74LVCE161284DL         | LVCE161284          |

| 0°C to 70°C | 550P - DL            | Tape and reel | SN74LVCE161284DLR        | LVCE 161264         |

|             | TSSOP - DGG          | Tape and reel | SN74LVCE161284DGGR       | LVCE161284          |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# SN74LVCE161284 19-BIT IEEE 1284 TRANSLATION TRANSCEIVER WITH ERROR-FREE POWER UP

SCES541 - JANUARY 2004

## description/ordering information (continued)

The output drive mode is determined by the high-drive (HD) control pin. When HD is high, the outputs are in a totem-pole configuration, and in an open-drain configuration when HD is low. This meets the drive requirements as specified in the IEEE Std 1284-I (level-1 type) and IEEE Std 1284-II (level-2 type) parallel peripheral-interface specifications. Except for HOST LOGIC IN and peripheral logic out (PERI LOGIC OUT), all cable-side pins have a 1.4-k $\Omega$  integrated pullup resistor. The pullup resistor is switched off if the associated output driver is in the low state or if the output voltage is above V<sub>CC</sub> CABLE. If V<sub>CC</sub> CABLE is off, PERI LOGIC OUT is set to low.

The device has two supply voltages.  $V_{CC}$  is designed for 3-V to 3.6-V operation.  $V_{CC}$  CABLE supplies the inputs and output buffers of the cable side only and is designed for 3-V to 3.6-V and for 4.7-V to 5.5-V operation. Even when  $V_{CC}$  CABLE is 3 V to 3.6 V, the cable-side I/O pins are 5-V tolerant.

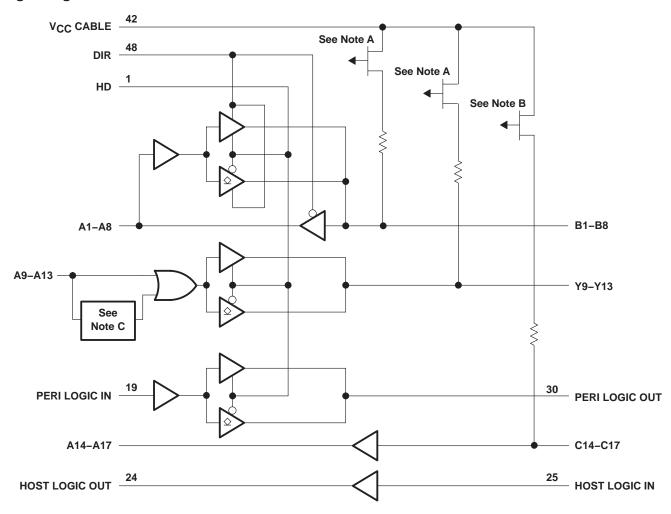

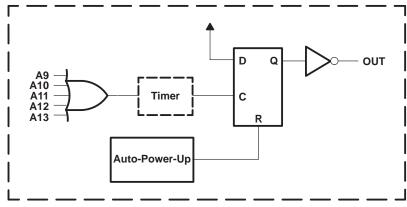

The Y outputs (Y9–Y13) stay in the high state after power on until an associated input (A9–A13) goes high. When an associated input goes high, all Y outputs are activated, and noninverting signals of the associated inputs are driven through Y outputs. This special feature prevents printer-system errors caused by deasserting the BUSY signal in the cable at power on.

#### **FUNCTION TABLE**

| INPUTS    |              |            |                                                                                           |  |  |  |

|-----------|--------------|------------|-------------------------------------------------------------------------------------------|--|--|--|

| DIR       | HD           | OUTPUT     | MODE                                                                                      |  |  |  |

|           | . Open drain |            | A9-A13 to Y9-Y13 and PERI LOGIC IN to PERI LOGIC OUT                                      |  |  |  |

| L L Toter |              | Totem pole | B1-B8 to A1-A8 and C14-C17 to A14-A17                                                     |  |  |  |

| L         | Н            | Totem pole | B1-B8 to A1-A8, A9-A13 to Y9-Y13, PERI LOGIC IN to PERI LOGIC OUT, and C14-C17 to A14-A17 |  |  |  |

|           |              | Open drain | A1-A8 to B1-B8, A9-A13 to Y9-Y13, and PERI LOGIC IN to PERI LOGIC OUT                     |  |  |  |

| Н         | L            | Totem pole | C14-C17 to A14-A17                                                                        |  |  |  |

| Н         | Н            | Totem pole | A1-A8 to B1-B8, A9-A13 to Y9-Y13, C14-C17 to A14-A17, and PERI LOGIC IN to PERI LOGIC OUT |  |  |  |

# SN74LVCE161284 19-BIT IEEE 1284 TRANSLATION TRANSCEIVER WITH ERROR-FREE POWER UP SCES541 - JANUARY 2004

## logic diagram

- NOTES: A. The PMOS transistors prevent backdriving current from the signal pins to V<sub>CC</sub> CABLE when V<sub>CC</sub> CABLE is open or at GND. The PMOS transistor is turned off when the associated driver is in the low state.

- B. The PMOS transistor prevents backdriving current from the signal pins to V<sub>CC</sub> CABLE when V<sub>CC</sub> CABLE is open or at GND.

C. Active input detection circuit forces Y9–Y13 to the high state after power-on, until one of the A9–A13 goes high (see Figure 1).

**Active Input Detection Circuit**

NOTE A: One of A9-A13 is switched as shown above, and the other four inputs are forced to low state.

Figure 1. Error-Free Circuit Timing

# SN74LVCE161284 19-BIT IEEE 1284 TRANSLATION TRANSCEIVER WITH ERROR-FREE POWER UP

SCES541 - JANUARY 2004

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| O sel selfere many V CARLE                                                                         | 0.5.1/1                                   |

|----------------------------------------------------------------------------------------------------|-------------------------------------------|

| Supply voltage range: V <sub>CC</sub> CABLE                                                        | 0.5 V to / V                              |

| V <sub>CC</sub>                                                                                    | –0.5 V to 4.6 V                           |

| Input and output voltage range, V <sub>I</sub> and V <sub>O</sub> : Cable side (see Notes 1 and 2) | –2 V to 7 V                               |

| Peripheral side (see Note 1)                                                                       | $\dots$ -0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0)                                          | –20 mA                                    |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0)                                         | –50 mA                                    |

| Continuous output current, IO: Except PERI LOGIC OUT                                               | ±50 mA                                    |

| PERI LOGIC OUT                                                                                     | ±100 mA                                   |

| Continuous current through each V <sub>CC</sub> or GND                                             | ±200 mA                                   |

| Output high sink current, I <sub>SK</sub> (V <sub>O</sub> = 5.5 V and V <sub>CC</sub> CABLE = 3 V) | 65 mA                                     |

| Package thermal impedance, θ <sub>JA</sub> (see Note 3): DGG package                               | 70°C/W                                    |

| DL package                                                                                         | 63°C/W                                    |

| Storage temperature range, T <sub>stq</sub>                                                        | –65°C to 150°C                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

- 2. The ac input-voltage pulse duration is limited to 40 ns if the amplitude is greater than -0.5 V.

- 3. The package thermal impedance is calculated in accordance with JESD 51-7.

# recommended operating conditions (see Note 4)

|                       |                                                                 |                              | MIN | MAX  | UNIT |  |

|-----------------------|-----------------------------------------------------------------|------------------------------|-----|------|------|--|

| V <sub>CC</sub> CABLE | Supply voltage for the cable side, $V_{CC}$ CABLE $\geq V_{CC}$ |                              | 3   | 5.5  | V    |  |

| VCC                   | Supply voltage                                                  |                              | 3   | 3.6  | V    |  |

|                       |                                                                 | A, B, DIR, and HD            | 2   |      |      |  |

|                       |                                                                 | C14-C17                      | 2.3 |      |      |  |

| VIH                   | High-level input voltage                                        | HOST LOGIC IN                | 2.6 |      | V    |  |

|                       |                                                                 | PERI LOGIC IN                | 2   |      |      |  |

|                       |                                                                 | A, B, DIR, and HD            |     | 0.8  |      |  |

|                       | Low-level input voltage                                         | C14-C17                      |     | 0.8  | V    |  |

| $V_{IL}$              |                                                                 | HOST LOGIC IN                |     | 1.6  |      |  |

|                       |                                                                 | PERI LOGIC IN                |     | 0.8  |      |  |

|                       | Input voltage                                                   | Peripheral side              | 0   | VCC  | V    |  |

| VI                    |                                                                 | Cable side                   | 0   | 5.5  |      |  |

| Vo                    | Open-drain output voltage                                       | HD low                       | 0   | 5.5  | V    |  |

|                       | High-level output current                                       | HD high, B and Y outputs     | -14 |      |      |  |

| <sup>I</sup> OH       |                                                                 | A outputs and HOST LOGIC OUT |     | -4   | mA   |  |

|                       |                                                                 | PERI LOGIC OUT               |     | -0.5 |      |  |

|                       | Low-level output current                                        | B and Y outputs              |     | 14   |      |  |

| lOL                   |                                                                 | A outputs and HOST LOGIC OUT |     | 4    | mA   |  |

|                       |                                                                 | PERI LOGIC OUT               |     | 84   |      |  |

| TA                    | Operating free-air temperature                                  |                              | 0   | 70   | °C   |  |

NOTE 4: All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

# SN74LVCE161284 19-BIT IEEE 1284 TRANSLATION TRANSCEIVER WITH ERROR-FREE POWER UP SCES541 – JANUARY 2004

## electrical characteristics over recommended operating free-air temperature range, (unless otherwise noted)

|                                                    | PARAMETER                                              | TEST CONDITIONS                                   | vcc                     | V <sub>CC</sub><br>CABLE | MIN TYPT MAX | UNIT |  |

|----------------------------------------------------|--------------------------------------------------------|---------------------------------------------------|-------------------------|--------------------------|--------------|------|--|

| ΔV <sub>t</sub>                                    | All inputs except the C inputs and HOST LOGIC IN       |                                                   |                         |                          | 0.4          |      |  |

| Hysteresis<br>(V <sub>T+</sub> – V <sub>T</sub> _) | HOST LOGIC IN                                          |                                                   | 3.3 V                   | 5 V                      | 0.2          | V    |  |

| (   + -     -                                      | C inputs                                               |                                                   |                         | ľ                        | 0.8          |      |  |

|                                                    | LID high D and V quitauta                              | 14 m 1                                            | 3 V                     | 3 V                      | 2.23         |      |  |

|                                                    | HD high, B and Y outputs                               | I <sub>OH</sub> = -14 mA                          | 3.3 V                   | 4.7 V                    | 2.4          |      |  |

| V                                                  | HD high, A outputs, and                                | $I_{OH} = -4 \text{ mA}$                          | 2.1/                    | 2.1/                     | 2.4          |      |  |

| VOH                                                | HOST LOGIC OUT                                         | I <sub>OH</sub> = -50 μA                          | 3 V                     | 3 V                      | 2.8          | V    |  |

|                                                    | DEDIT OCIO OLIT                                        | 1 0.5 m.A                                         | 3.15 V                  | 3.15 V                   | 3.1          |      |  |

|                                                    | PERI LOGIC OUT                                         | $I_{OH} = -0.5 \text{ mA}$                        | 3.3 V                   | 4.7 V                    | 4.5          |      |  |

|                                                    | B and Y outputs                                        | I <sub>OL</sub> = 14 mA                           |                         |                          | 0.77         |      |  |

| V                                                  | A outputs and HOST LOGIC                               | I <sub>OL</sub> = 50 μA                           | 3 V                     |                          | 0.2          | V    |  |

| V <sub>OL</sub>                                    | OUT                                                    | I <sub>OL</sub> = 4 mA                            | 3 V                     | 3 V                      | 0 4          |      |  |

|                                                    | PERI LOGIC OUT                                         | I <sub>OL</sub> = 84 mA                           | 1   †                   |                          | 0.9          |      |  |

|                                                    | C inputs                                               | $V_I = V_{CC}$                                    |                         |                          | 50           | μΑ   |  |

| lį                                                 |                                                        | V <sub>I</sub> = GND<br>(pullup resistors)        | 3.6 V                   | 3.6 V                    | -3.5         | mA   |  |

|                                                    | All inputs except B or C inputs                        | $V_I = V_{CC}$ or GND                             | 3.6 V                   | 5.5 V                    | ±1           | μΑ   |  |

|                                                    | A1-A8                                                  | $V_O = V_{CC}$ or GND                             | 3.6 V                   | 5.5 V                    | ±20          | μΑ   |  |

|                                                    |                                                        | VO = VCC CABLE                                    | 3.6 V                   | 5.5 V                    | 50           | μΑ   |  |

| loz                                                | B outputs                                              | V <sub>O</sub> = GND<br>(pullup resistors)        | 3.6 V                   | 3.6 V                    | -3.5         | mA   |  |

|                                                    | Open-drain Y outputs                                   | V <sub>O</sub> = GND<br>(pullup resistors)        | 3.6 V                   | 3.6 V                    | -3.5         | mA   |  |

|                                                    | 5 17                                                   | V <sub>O</sub> = 5.5 V                            | 0. 4514                 | 0 40 4 5 1/1             | 350          | μΑ   |  |

| lozpu                                              | B and Y outputs                                        | V <sub>O</sub> = GND                              | 0 to 1.5 V <sup>‡</sup> | 0 to 1.5 V‡              | -5           | mA   |  |

| 1                                                  | D and V autoute                                        | V <sub>O</sub> = 5.5 V                            | 01.451/                 | 01-451/1                 | 350          | μΑ   |  |

| lozpd                                              | B and Y outputs                                        | V <sub>O</sub> = GND                              | 0 to 1.5 V <sup>‡</sup> | 0 to 1.5 V <sup>‡</sup>  | -5           | mA   |  |

|                                                    | Power-down input leakage, except A1–A8 or B1–B8 inputs | $V_I$ or $V_O = 0$ to 3.6 $V$                     | _                       |                          | 100          |      |  |

| loff                                               | Power-down output leakage,<br>B1–B8 and Y9–Y13 outputs | $V_I$ or $V_O = 0$ to 5.5 $V$                     | 0                       | 0                        | 100          | μΑ   |  |

|                                                    | •                                                      | V <sub>I</sub> = GND                              | 3.6 V                   | 3.6 V                    | 45           |      |  |

| lcc                                                |                                                        | (12 × pullup)                                     | 3.6 V                   | 5.5 V                    | 70           | mA   |  |

|                                                    |                                                        | $V_I = V_{CC},$ $I_O = 0$                         | 3.6 V                   | 3.6 V                    | 0.8          | 1    |  |

| ZO                                                 | B1-B8, Y9-Y13                                          | I <sub>OH</sub> = -35 mA                          | 3.3 V                   | 3.3 V                    | 36           | Ω    |  |

| R pullup                                           | B1-B8, Y9-Y13, C14-C17                                 | V <sub>O</sub> = 0 V<br>(in high-impedance state) | 3.3 V                   | 3.3 V                    | 1.15 1.65    | kΩ   |  |

<sup>†</sup> Typical values are measured at  $T_A = 25$ °C.

<sup>‡</sup> Connect the V<sub>CC</sub> pin to the V<sub>CC</sub> CABLE pin.

# SN74LVCE161284 19-BIT IEEE 1284 TRANSLATION TRANSCEIVER WITH ERROR-FREE POWER UP SCES541 – JANUARY 2004

### electrical characteristics over recommended operating free-air temperature range, (unless otherwise noted) (continued)

|                 | PARAMETER                         | TEST CONDITIONS                         | vcc   | V <sub>CC</sub><br>CABLE | MIN TYPT MAX | UNIT |

|-----------------|-----------------------------------|-----------------------------------------|-------|--------------------------|--------------|------|

| C <sub>i</sub>  | A9-A13, DIR, HD,<br>PERI LOGIC IN | V <sub>I</sub> = V <sub>CC</sub> or GND | 3.3 V | 5 V                      | 6.5          | pF   |

| '               | HOST LOGIC IN                     |                                         |       |                          | 4            |      |

| C.              | A1-A8                             | Vo - Voo or CND                         | 3.3 V | 5 V                      | 8            | pF   |

| C <sub>io</sub> | B1-B8                             | $V_O = V_{CC}$ or GND                   | 3.3 V | 5 V                      | 13           | ρг   |

<sup>†</sup> Typical values are measured at  $T_A = 25$ °C.

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Figures 2 and 3)

| PARAMETER                         |             | FROM<br>(INPUT) | TO<br>(OUTPUT)                         | MIN  | TYP <sup>‡</sup> | MAX | UNIT |

|-----------------------------------|-------------|-----------------|----------------------------------------|------|------------------|-----|------|

| <sup>t</sup> PLH                  |             |                 | D. D.                                  | 2    |                  | 30  |      |

| <sup>t</sup> PHL                  | Totem pole  | A1–A8           | B1-B8                                  | 2    |                  | 30  | ns   |

| <sup>t</sup> PLH                  | Tatananala  | 40, 440         | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 2    |                  | 30  |      |

| <sup>t</sup> PHL                  | Totem pole  | A9–A13          | Y9–Y13                                 | 2    |                  | 30  | ns   |

| <sup>t</sup> PLH                  | Totam nole  | D4 D0           | 44.40                                  | 2    |                  | 12  |      |

| <sup>t</sup> PHL                  | Totem pole  | B1-B8           | A1–A8                                  | 2    |                  | 12  | ns   |

| <sup>t</sup> PLH                  | Totom nole  | C14 C17         | A14-A17                                | 2    |                  | 14  |      |

| <sup>t</sup> PHL                  | Totem pole  | C14-C17         | A14-A17                                | 2    |                  | 14  | ns   |

| <sup>t</sup> PLH                  | Totom nole  | PERI LOGIC IN   | PERI LOGIC OUT                         | 2    |                  | 16  | ns   |

| <sup>t</sup> PHL                  | Totem pole  | PERI LOGIC IN   |                                        | 2    |                  | 16  |      |

| <sup>t</sup> PLH                  | Totem pole  | HOST LOGIC IN   | HOST LOGIC OUT                         | 1    |                  | 18  | ns   |

| <sup>t</sup> PHL                  | rotern pole | HOST LOGIC IN   | 11031 20310 001                        | 1    |                  | 18  | 115  |

| t <sub>slew</sub>                 | Totem pole  | B1-B8 and Y9    | –Y13 outputs                           | 0.05 |                  | 0.4 | V/ns |

| <sup>t</sup> PZH                  |             | HD              | B1-B8, Y9-Y13, and                     | 2    |                  | 30  |      |

| <sup>t</sup> PHZ                  |             | но              | PERI LOGIC OUT                         | 2    |                  | 25  | ns   |

| t <sub>en</sub> -t <sub>dis</sub> |             | DIR             | A1-A8                                  | 2    |                  | 25  | ns   |

| <sup>t</sup> PHZ                  |             |                 | D4 D0                                  | 2    |                  | 25  |      |

| <sup>t</sup> PLZ                  | 7           | DIR             | B1-B8                                  | 2    |                  | 25  | ns   |

| t <sub>r</sub> , t <sub>f</sub>   | Open drain  | A1-A13          | B1-B8 or Y9-Y13                        | 1    |                  | 120 | ns   |

| t <sub>sk(o)</sub> §              |             | A1-A8 or B1-B8  | B1-B8 or A1-A8                         |      | 3                | 10  | ns   |

## **ESD** protection

| PIN                                                                  | TEST CONDITIONS                  | TYP | UNIT |

|----------------------------------------------------------------------|----------------------------------|-----|------|

| B1-B8, Y9-Y13, PERI LOGIC OUT,<br>C14-C17, HOST LOGIC IN             | НВМ                              | ±15 |      |

|                                                                      | Contact discharge, IEC 61000-4-2 | ±8  | kV   |

| 014 017,11001 20010 111                                              | Air-gap discharge, IEC 61000-4-2 | ±15 |      |

| DIR, HD, A1-A8, A9-A13,<br>PERI LOGIC IN, A14-A17,<br>HOST LOGIC OUT | НВМ                              | ±4  | kV   |

<sup>‡</sup> Typical values are measured at  $V_{CC}$  = 3.3 V,  $V_{CC}$  CABLE = 5 V, and  $T_A$  = 25°C. § Skew is measured at 1/2 ( $V_{OH}$  +  $V_{OL}$ ) for signals switching in the same direction.

# SN74LVCE161284 19-BIT IEEE 1284 TRANSLATION TRANSCEIVER WITH ERROR-FREE POWER UP SCES541 – JANUARY 2004

# operating characteristics, V<sub>CC</sub> and V<sub>CC</sub> CABLE = 3.3 V, C<sub>L</sub> = 0, f = 10 MHz, T<sub>A</sub> = 25 $^{\circ}$ C

|                 | PARAMETER                     | FROM<br>(INPUT) | TO<br>(OUTPUT) | TYP | UNIT |

|-----------------|-------------------------------|-----------------|----------------|-----|------|

|                 |                               | A               | В              | 15  |      |

|                 | Power dissipation capacitance | А               | Y              | 6   | pF   |

|                 |                               | PERI LOGIC IN   | PERI LOGIC OUT | 10  |      |

| C <sub>pd</sub> |                               | В               | А              | 33  |      |

|                 |                               | С               | A              | 29  |      |

|                 |                               | HOST LOGIC IN   | HOST LOGIC OUT | 29  |      |

# SN74LVCE161284 19-BIT IEEE 1284 TRANSLATION TRANSCEIVER WITH ERROR-FREE POWER UP

SCES541 - JANUARY 2004

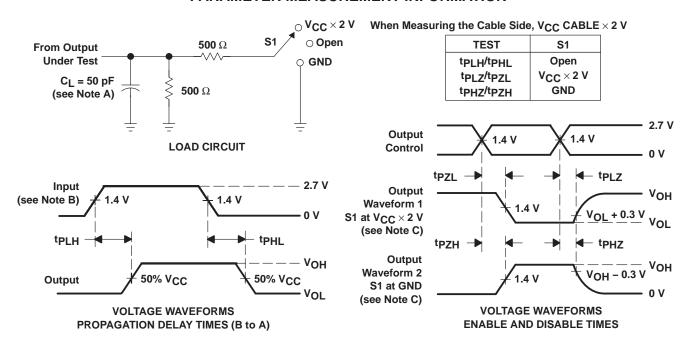

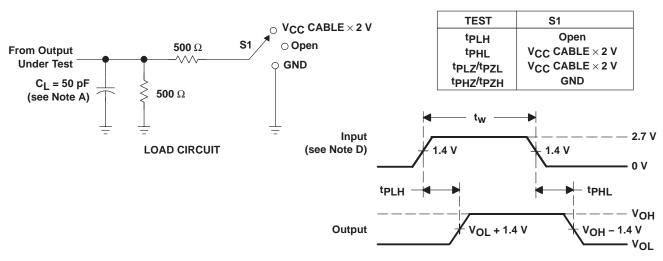

### PARAMETER MEASUREMENT INFORMATION

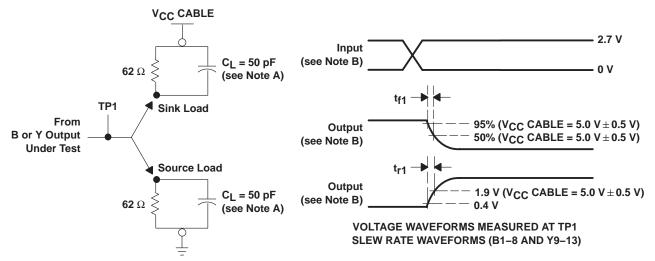

SLEW RATE A-TO-B OR A-TO-Y LOAD (TOTEM POLE) OR PERI LOGIC IN TO PERI LOGIC OUT

### A-TO-B LOAD OR A-TO-Y LOAD (OPEN DRAIN) OR PERI LOGIC IN TO PERI LOGIC OUT

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

B. When  $V_{CC}$  CABLE is 3.3 V  $\pm$  0.3 V, slew rate is measured between 0.4 V and 0.9 V for the rising edge and between 2.4 V and 1.9 V for the falling edge. When  $V_{CC}$  CABLE is 5 V  $\pm$  0.5 V, slew rate is measured between 0.4 V and 1.9 V for the rising edge and between 95%  $V_{CC}$  CABLE and 50%  $V_{CC}$  CABLE for the falling edge.

$$t_{\text{slew}} \text{fall} = V_{\text{CC}} \left( \frac{95\% - 50\%}{t_{\text{f1}}} \right)$$

$t_{\text{slew}} \text{rise} = \left( \frac{1.9 \text{ V} - 0.4 \text{ V}}{t_{\text{r1}}} \right)$

- C. Input rise  $(t_f)$  and fall  $(t_f)$  times are 3 ns. Rise and fall times (open drain) are <120 ns.

- D. The outputs are measured one at a time, with one transition per measurement.

- E. tpLz and tpHz are the same as tdis.

- F. tpZL and tpZH are the same as ten.

- G. tpLH and tpHL are the same as tpd.

Figure 2. Load Circuits and Voltage Waveforms

SCES541 - JANUARY 2004

### PARAMETER MEASUREMENT INFORMATION

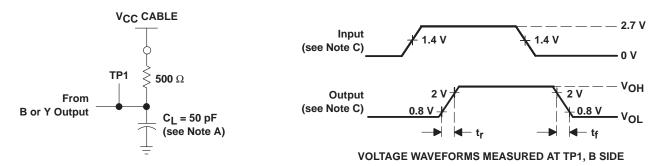

HOST LOGIC IN TO HOST LOGIC OUT OR B-TO-A LOAD (TOTEM POLE)

VOLTAGE WAVEFORMS MEASURED AT TP1

PROPAGATION DELAY TIMES (A to B)

### A-TO-B LOAD OR A-TO-Y LOAD (TOTEM POLE) OR PERI LOGIC IN TO PERI LOGIC OUT

NOTES: A. C<sub>I</sub> includes probe and jig capacitance.

- B. Input rise and fall times are 3 ns.

- C. Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.

- D. Input rise and fall times are 3 ns. Pulse duration is 150 ns <  $t_W$  < 10  $\mu$ s.

- E. The outputs are measured one at a time, with one transition per measurement.

- F.  $t_{PLZ}$  and  $t_{PHZ}$  are the same as  $t_{dis}$ .

- G. tpZL and tpZH are the same as ten.

- H. tpLH and tpHL are the same as tpd.

Figure 3. Load Circuit and Voltage Waveforms

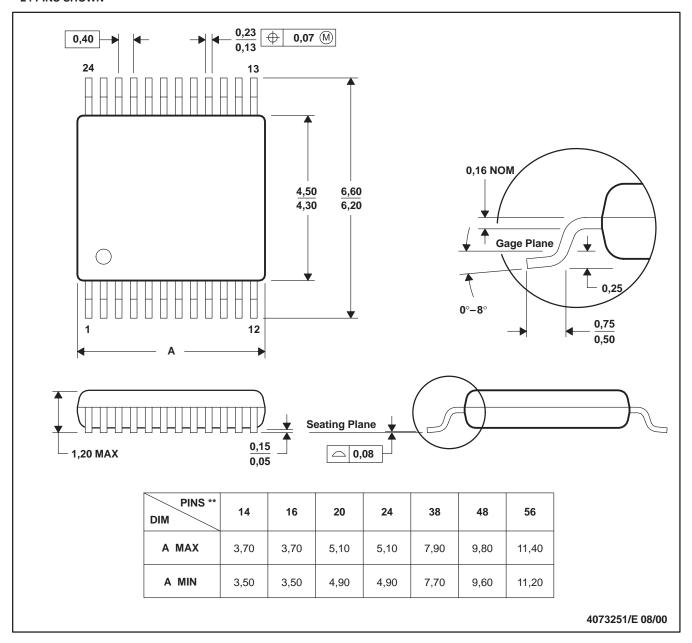

## DGV (R-PDSO-G\*\*)

### **24 PINS SHOWN**

### **PLASTIC SMALL-OUTLINE**

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0,15 per side.

- D. Falls within JEDEC: 24/48 Pins MO-153 14/16/20/56 Pins – MO-194

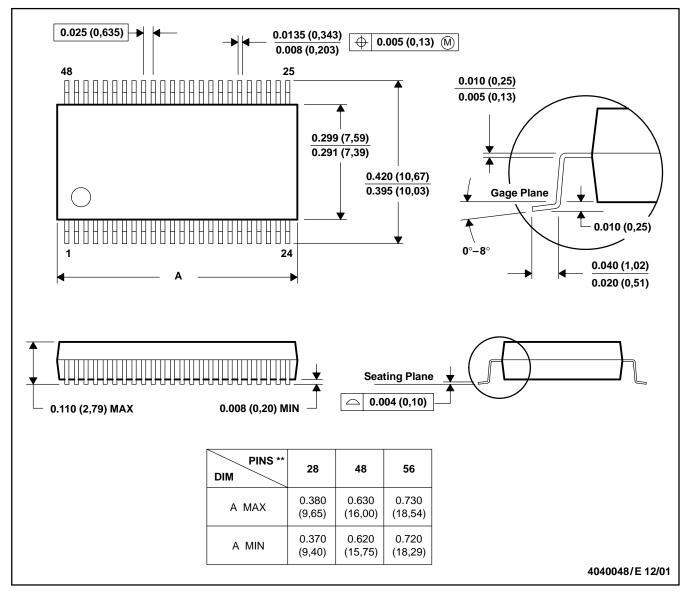

### DL (R-PDSO-G\*\*)

### **48 PINS SHOWN**

### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MO-118

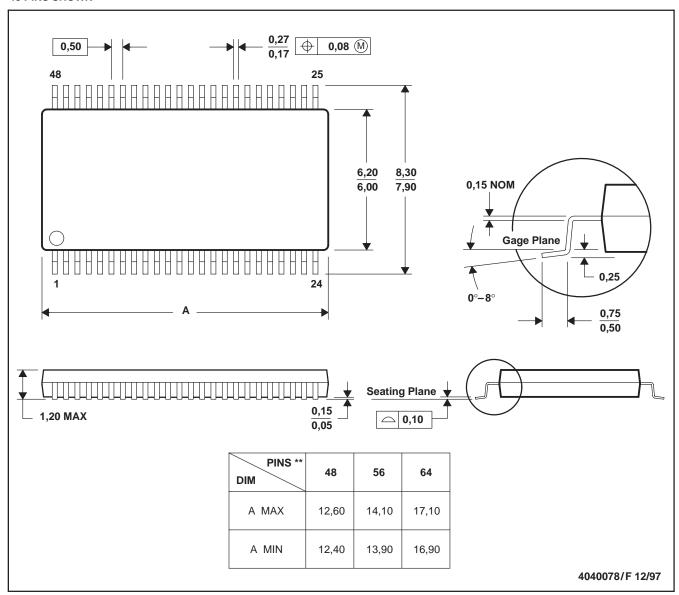

# DGG (R-PDSO-G\*\*)

### PLASTIC SMALL-OUTLINE PACKAGE

### **48 PINS SHOWN**

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold protrusion not to exceed 0,15.

- D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265