**VFC121**

# Precision Single Power Supply VOLTAGE-TO-FREQUENCY CONVERTER

## **FEATURES**

- SINGLE SUPPLY OPERATION: +4.5V to +36V

- $\bullet$  f<sub>0</sub> = 1.5MHz max

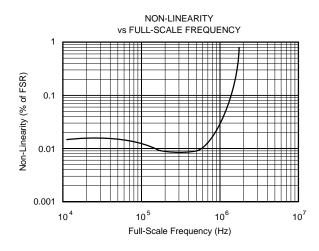

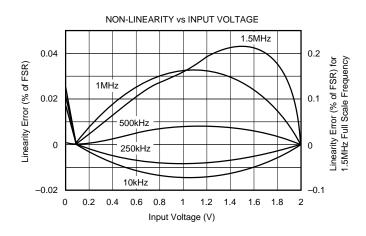

- LOW NONLINEARITY: 0.03% max at 100kHz, 0.1% max at 1MHz

- HIGH INPUT IMPEDANCE

- VOLTAGE REFERENCE OUTPUT

- THERMOMETER OUTPUT: 1mV/°K

## **APPLICATIONS**

- INTEGRATING A/D CONVERSION

- ANALOG SIGNAL TRANSMISSION

- PHASE-LOCKED LOOP VCO

- GALVANICALLY ISOLATED SYSTEMS

## DESCRIPTION

The VFC121 is a monolithic voltage-to-frequency converter consisting of an integrating amplifier, voltage reference, and one-shot charge pump circuitry. High-frequency complementary NPN/PNP circuitry is used to implement the charge-balance technique, achieving speed and accuracy far superior to previous single power supply VFCs.

The high-impedance input accepts signals from ground potential to  $V_S - 2.5V$ . Power supplies from 4.5V to

36V may be used. A 2.6V reference voltage output may be used to excite sensors or bias external circuitry. A thermometer output voltage proportional to absolute temperature (°K) may be used as a temperature sensor or for temperature compensation of applications circuits.

Frequency output is an open-collector transistor. A disable pin forces the output to the high impedance state, allowing multiple VFCs to share a common transmission path.

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706

Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

© 1989 Burr-Brown Corporation PDS-971A Printed in U.S.A. March, 1992

## **SPECIFICATIONS**

## **ELECTRICAL**

At  $T_A$  = +25°C,  $V_S$  = +5V, and  $R_{IN}$  = 8k $\Omega$ , unless otherwise noted.

|                                                                                                                                                                                 |                                                                                                                                                                  |                     | VFC121AP                                      | 1                                      |                   | VFC121BP           | )                                 |                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------|----------------------------------------|-------------------|--------------------|-----------------------------------|---------------------------------------|

| PARAMETER                                                                                                                                                                       | CONDITIONS                                                                                                                                                       | MIN                 | TYP                                           | MAX                                    | MIN               | TYP                | MAX                               | UNITS                                 |

| ACCURACY Nonlinearity: $f_{FS} = 100 \text{kHz}$ $f_{FS} = 1 \text{MHz}$ Gain Error: $f_{FS} = 100 \text{kHz}$ Gain Drift: $f_{FS} = 100 \text{kHz}$ Relative to $V_{REF}$ PSRR | $C_{OS}$ 1200pF, $C_{INT}$ = 2700pF<br>$C_{OS}$ 68pF, $C_{INT}$ = 270pF<br>$C_{OS}$ 1200pF, $C_{INT}$ = 2700pF<br>$T_{MIN}$ to $T_{MAX}$<br>$+V_S$ = +5V to +36V |                     | 0.1                                           | 0.05<br>10<br>80<br>100<br>0.025       |                   |                    | 0.03<br>0.1<br>*<br>40<br>40<br>* | %FS<br>%FS<br>%FS<br>ppm/°C<br>ppm/°C |

| INPUT Minimum Input Voltage Maximum Input Voltage Impedance IBIAS VOS VOS Drift                                                                                                 | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                             | V <sub>S</sub> -2.5 | V <sub>S</sub> - 2<br>100<br>150<br>300<br>10 | 0<br>300<br>800                        | *                 | *<br>*<br>100<br>* | *<br>400                          | V<br>V<br>MΩ<br>nA<br>μV<br>μV/°C     |

| OPEN COLLECTOR OUTPUT  V <sub>SAT</sub> I <sub>LEAKAGE</sub> Fall Time  Delay to Rise  Settling Time                                                                            | $I_{PULL\ UP} = 10\text{mA}$ $V_{PULL\ UP} = 5V$ $V_{PULL\ UP} = 36V$ $R_{PULL\ UP} = 470\Omega$ To Specified Linearity for Full Scale Input Step                | (1)                 |                                               | 0.4<br>1<br>10<br>100<br>100           |                   |                    | * * * *                           | V<br>μA<br>μA<br>ns<br>ns             |

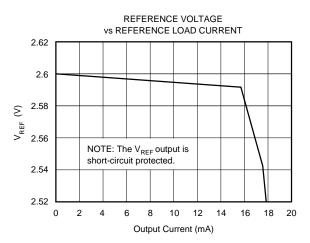

| REFERENCE VOLTAGE  Voltage  Voltage Drift  Load Regulation  PSRR  Current Limit                                                                                                 | $I_{O} = 0 \text{ to } 10\text{mA}$<br>$V_{S} = +5\text{V to } +36\text{V}$                                                                                      | 2.59                | 2.6                                           | 2.61<br>100<br>10<br>10<br>Short Circu | *<br>it Protected | *                  | *<br>50<br>*<br>*                 | V<br>ppm/°C<br>mV<br>mV               |

| INTEGRATOR AMPLIFIER OUTPUT Output Voltage Range                                                                                                                                | $R_L = 100k\Omega$                                                                                                                                               | 0.8                 |                                               | 2.9                                    | *                 |                    | *                                 | V                                     |

| COMPARATOR INPUT  I <sub>BIAS</sub> Trigger Voltage Input Voltage Range                                                                                                         |                                                                                                                                                                  | 0                   | +1<br>2.6                                     | 2.9                                    | *                 | *                  | *                                 | μA<br>V<br>V                          |

| THERMOMETER V <sub>T</sub> V <sub>T</sub> Slope                                                                                                                                 | T <sub>A</sub> = +25°C<br>T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                   |                     | 298<br>1                                      |                                        |                   | *                  |                                   | mV<br>mV/°K                           |

| DISABLE INPUT V <sub>HIGH</sub> (Disabled) V <sub>LOW</sub> I <sub>HIGH</sub> (Disabled) I <sub>LOW</sub>                                                                       | $V_{HIGH} = 2V$ $V_{LOW} = 0.8V$                                                                                                                                 | 2                   | 10<br>10                                      | 0.8                                    | *                 | *                  | *                                 | V<br>V<br>μΑ<br>μΑ                    |

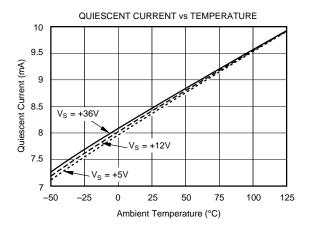

| POWER SUPPLY<br>Voltage<br>Current                                                                                                                                              |                                                                                                                                                                  | 4.5                 | 5<br>7.5                                      | 36<br>10                               | *                 | *                  | *                                 | V<br>mA                               |

| TEMPERATURE RANGE<br>Specified<br>Storage                                                                                                                                       |                                                                                                                                                                  | -25<br>-40          |                                               | +85<br>+125                            | *                 |                    | *                                 | °C<br>°C                              |

<sup>\*</sup> Same specification as VFC121AP.

NOTE: (1) One pulse of new frequency plus 1µs.

## **ORDERING INFORMATION**

|   | MODEL                | PACKAGE     | LINEARITY<br>ERROR, MAX<br>(f <sub>S</sub> = 100kHz) | TEMPERATURE<br>RANGE             |  |  |

|---|----------------------|-------------|------------------------------------------------------|----------------------------------|--|--|

| I | VFC121AP<br>VFC121BP | Plastic DIP | 0.05%<br>0.03%                                       | −25°C to +85°C<br>−25°C to +85°C |  |  |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

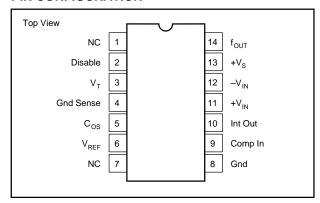

## **PIN CONFIGURATION**

## **ABSOLUTE MAXIMUM RATINGS**

| Power Supply Voltage (+V <sub>S</sub> )  f <sub>OUT</sub> Sink Current  Comparator In Voltage  Enable Input  Integrator Common-Mode Voltage  Integrator Differential Input Voltage | 20mA<br>                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| V <sub>REF</sub> Out (short-circuit)                                                                                                                                               | 40°C to +85°C<br>40°C to +125°C |

| Stresses above these ratings may permanently dar<br>sure to absolute maximum rating conditions for exte<br>device reliability.                                                     |                                 |

## **PIN CONFIGURATION**

| PIN# | NAME             | DESCRIPTION                                                                                                                                                                         |

|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | NC               | Not Connected                                                                                                                                                                       |

| 2    | Disable          | Input logic Low for normal operation. Input logic<br>High to disable the VFC121. Has internal pull-<br>down, for normal operation if not connected.                                 |

| 3    | V <sub>T</sub>   | Temperature compensation voltage proportional to absolute temperature. Typically 298mV at room temperature (298°K), with a change of 1mV per °C (°K).                               |

| 4    | Gnd Sense        | Defines ground for the internal voltage reference.                                                                                                                                  |

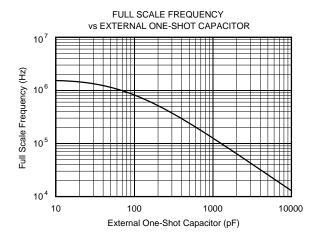

| 5    | C <sub>os</sub>  | One-shot capacitor is connected between here and ground to set full scale output frequency.                                                                                         |

| 6    | V <sub>REF</sub> | Output from the internal band-gap voltage reference, typically 2.6V. Can be used externally to set levels or excite sensors.                                                        |

| 7    | NC               | Not Connected                                                                                                                                                                       |

| 8    | Gnd              | Ground                                                                                                                                                                              |

| 9    | Comp In          | Comparator In                                                                                                                                                                       |

| 10   | Int Out          | Integrator Out                                                                                                                                                                      |

| 11   | +V <sub>IN</sub> | Non-inverting input of the integrating op amp.<br>The input signal is applied here.                                                                                                 |

| 12   | -V <sub>IN</sub> | Inverting input of the integrating op amp. $C_{\text{INT}}$ is connected between here and the integrator output (pin 10), and $R_{\text{IN}}$ is connected between here and ground. |

| 13   | +V <sub>S</sub>  | Supply voltage connected here. Range is +4.5V to +36V.                                                                                                                              |

| 14   | f <sub>оит</sub> | Frequency output pin. This is the output of an open-collector transistor, and an external pull-up circuit should be used to generate the appropriate logic levels.                  |

## **PACKAGE INFORMATION**

| MODEL    | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |  |  |

|----------|--------------------|------------------------------------------|--|--|

| VFC121AP | 14-Pin Plastic DIP | 010                                      |  |  |

| VFC121BP | 14-Pin Plastic DIP | 010                                      |  |  |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

\/504

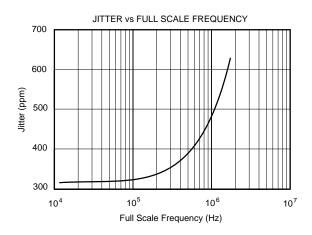

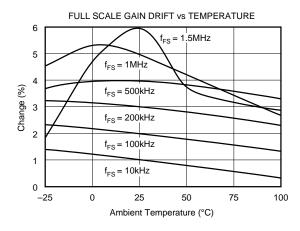

## **TYPICAL PERFORMANCE CURVES**

At  $T_A = +25^{\circ}C$ ,  $V_S = +5V$ , and  $R_{IN} = 8k\Omega$ , unless otherwise noted.

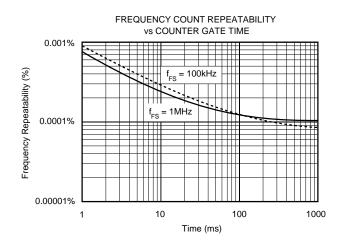

## TYPICAL PERFORMANCE CURVES (CONT)

At  $T_A = +25$ °C,  $V_S = +5V$ , and  $R_{IN} = 8k\Omega$ , unless otherwise noted.

## THEORY OF OPERATION

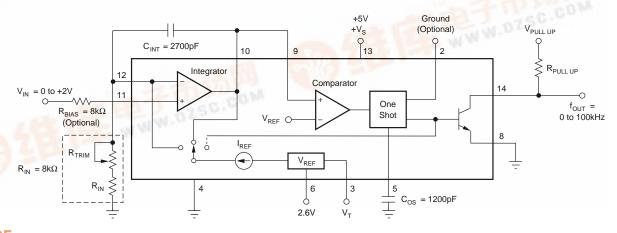

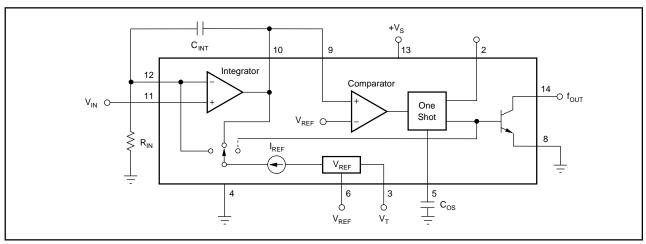

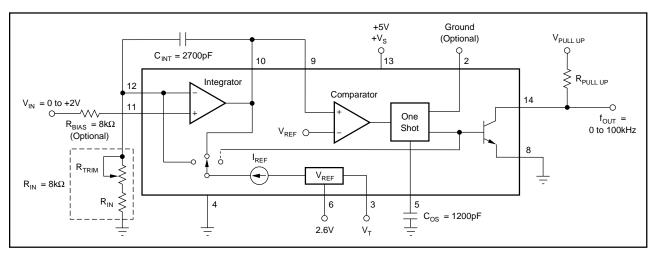

The VFC121 uses a charge-balance technique to achieve high accuracy. The basic architecture is shown in Figure 1. An analog integrator at the front end, consisting of a precision op amp and a feedback capacitor,  $C_{\rm INT}$ , provides a true integrating approach for improved noise immunity. Use of the non-inverting input of the op amp for the analog input provides a high input impedance to the user.

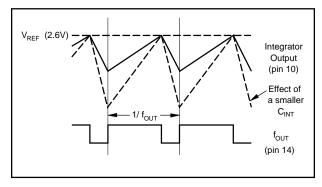

The integrator's output is proportional to the charge stored on  $C_{\rm INT}$  plus the analog input voltage. An input voltage,  $V_{\rm IN}$ , forces a current through  $R_{\rm IN}$  of  $V_{\rm IN}/R_{\rm IN}$ , which also flows through  $C_{\rm INT}$ . This current through  $C_{\rm INT}$  causes the integrator output to ramp positive. (Refer to the timing diagram in Figure 2.)

When the output of the integrator ramps to  $V_{REF}$ , the comparator trips, driving the output of the VFC121 Low, and triggering the one-shot. The tripping of the comparator also connects the reference current,  $I_{REF}$ , to the integrator input

for the duration of the one-shot period,  $T_{OS}$ . This switched current causes the output of the integrator to ramp negative.

When the one-shot times out, the output of the VFC121 is reset High, the one-shot is reset, and  $I_{REF}$  is switched to the output of the integrating op amp. (This causes the output of

FIGURE 2. Timing Diagram.

FIGURE 1. VFC121 Architecture.

FIGURE 3. 2V Full Scale Input, 100kHz Full Scale Output.

the integrating op amp to see a constant current, reducing errors that might occur if the load were unbalanced.) In this state, the output of the integrator resumes a positive ramp, restarting the cycle.

The output frequency is regulated by the balance of current (or charge) between the current  $V_{\rm IN}/R_{\rm IN}$  and the time-averaged reset current. The size of the integrating capacitor,  $C_{\rm INT}$ , determines the slew rate of the integrator, and thus how far down the integrator ramps during the one-shot period, but has no effect on the output frequency of the VFC121.

The reference voltage used internally is generated from a bandgap reference, which is actively trimmed to achieve the low drift characteristics of the VFC121. To maximize flexibility of designs using the VFC121, both the bandgap reference voltage and a thermometer voltage are available externally.

## INSTALLATION AND OPERATING INSTRUCTIONS

#### **BASIC OPERATION**

The VFC121 allows users a wide range of input voltages and supply voltages, and easy control of the full scale output frequency. The basic connections are shown in Figure 3, with components that generate a 100kHz output with a 2V full scale input.

For other input and output ranges, the full scale input voltages and full scale output frequencies can be calculated as follows:  $V_{\rm FS}$

$f_{FS} = \frac{V_{FS}}{2(R_{IN})(C_{OS} + 60)}$

The full scale input current of  $250\mu A$  was chosen to provide a 25% duty cycle in the output frequency. The VFC121 is designed to give optimum linearity under these conditions, but other current levels can be used without significantly degrading linearity. By reducing  $R_{\rm IN}$ , the integrating current is increased, increasing the positive ramp rate of the integra-

tor output. Since the one-shot period is unchanged, the duty cycle of the output increases.

Stray capacitance at the  $C_{OS}$  pin typically adds about 60pF to the capacitance of the external  $C_{OS}$ , which accounts for the adjustment in the above equation. This usually becomes negligible as the required output frequency is reduced, and  $C_{OS}$  is increased.

$R_{\rm BIAS}$  is included in the circuit in Figure 3 to compensate for the effects of bias currents at the input of the integrating op amp. It is optional in most applications, but when needed,  $R_{\rm BIAS}$  should equal  $R_{\rm IN}$ .

Table 1 indicates standard external component values for common input voltage ranges and output frequency ranges.

#### **COMPONENT SELECTION**

Selection of the external resistor and capacitor type is important. Temperature drift of the external input resistor and one-shot capacitor will affect temperature stability of the output frequency. NPO ceramic capacitors will normally produce the best results. Silver-mica types will result in slightly higher drift, but may be adequate in many applications. A low temperature coefficient film resistor should be used for R<sub>IN</sub>.

The integrator capacitor,  $C_{INT}$ , serves as a "charge bucket," where charge accumulation is induced by the input,  $V_{IN}$ , and

| FULL SCALE INPUT RANGE (V)                                                 | $R_{IN} + R_{TRIM} (k\Omega)$ |                       |  |

|----------------------------------------------------------------------------|-------------------------------|-----------------------|--|

| 2                                                                          | 8                             |                       |  |

| 5                                                                          | 20                            |                       |  |

| 10                                                                         | 4                             | 0                     |  |

| FULL SCALE OUTPUT FREQUENCY (kHz)                                          | Cos (pF)                      | C <sub>INT</sub> (pF) |  |

| 1500                                                                       | 22                            | 150                   |  |

| 1000                                                                       | 68                            | 270                   |  |

| 500                                                                        | 180                           | 470                   |  |

| 250                                                                        | 470                           | 1000                  |  |

| 125                                                                        | 1000                          | 2200                  |  |

| 25                                                                         | 4700                          | 10,000                |  |

| NOTE: Higher output frequencies can be achieved by reducing R <sub>m</sub> |                               |                       |  |

TABLE 1. Standard External Component Values

repeatedly reduced during the one-shot period. The size of the bucket (the capacitor value) is not critical, since it primarily determines how far below  $V_{REF}$  the output of the integrator ramps during the one-shot period. At the same time, the capacitor used must not leak since capacitor leakage or dielectric absorption can affect the linearity and offset of the transfer function. High-quality ceramic capacitors can be used for values less than  $0.01\mu F$ , but caution should be used with higher value ceramic capacitors. High-k ceramic capacitors may have voltage non-linearities which can degrade overall linearity. Polystyrene, polycarbonate, or mylar film capacitors are superior for higher capacitance values.

During the one-shot period, the output of the integrator is ramping down. To prevent the integrating op amp from being saturated at its minimum output of 0.8V,  $C_{INT}$  should be kept at least  $1.7 \times C_{OS}$ .

## **OUTPUT FREQUENCY ADJUSTMENT**

The full scale output frequency of the VFC121 can be adjusted using a trim-pot,  $R_{TRIM}$  in Figure 3, in series with  $R_{\rm IN}$ . For optimum drift vs temperature, a low temperature coefficient fixed resistor of approximately 90% of the calculated  $R_{\rm IN}$  requirement should be used in series with a trimpot approximately 20% of the size of the calculated  $R_{\rm IN}$ . The low-drift fixed resistor contributes most of the final  $R_{\rm IN}$  resistance, so that the effect of higher drift from the trim-pot is attenuated in the total  $R_{\rm IN}$ .

#### **PULL-UP RESISTOR**

The VFC121's frequency output is an open-collector transistor. A pull-up resistor should be connected from  $f_{OUT}$  to the logic supply,  $+V_L$ . The output transistor is On during the one-shot period, causing the output to be logic Low. The current flowing in this resistor should be limited to 10mA to assure a 0.4V maximum logic Low. The value chosen for the pull-up resistor may depend on the full-scale frequency and capacitance on the output line. Excessive capacitance on  $f_{OUT}$  will cause a slow, rounded rising edge at the end of an output pulse. This effect can be minimized by using a pull-up resistor which sets the output current to its maximum of 10mA. The logic power supply can be any positive voltage up to +36V.

#### **ENABLE PIN**

If left unconnected, the Enable input will assume a logic Low level, enabling the output stage, Alternatively, the Enable input may be connected directly to ground. This pin can also be driven by standard TTL or CMOS logic.

A logic High at the Enable input causes output pulses to cease. This is accomplished by interrupting the signal path through the one-shot circuitry. While disabled, all circuitry remains active and quiescent current is unchanged. Since no reset current pulses can occur while disabled, any positive input voltage will cause the integrator op amp to ramp positive and saturate at its most positive output swing of approximately  $V_{\rm REF} + 0.7 V. \label{eq:logical_path}$

When the Enable input receives a logic Low (less than 0.8V), a reset current cycle is initiated, (causing  $f_{OUT}$  to go Low). The integrator ramps negatively and normal operation is established. The time required for the output frequency to stabilize is equal to approximately one cycle of the final output frequency plus  $1\mu s$ .

Using the Enable input, the outputs from several VFCs can be connected to a single line. All disabled VFCs will have a high output impedance; one active VFC can then transmit on the line. Since disabled VFCs are not oscillating, they cannot interfere or "lock" with the operating VFC. Locking can occur when one VFC operates at nearly the same frequency, or a multiple, as a nearby VFC. Coupling between the two may cause them to lock to the same frequency or an exact multiple. It then takes a small incremental input voltage change on one of the VFCs to unlock them. Locking cannot occur when unneeded VFCs are disabled.

## APPLICATION INFORMATION

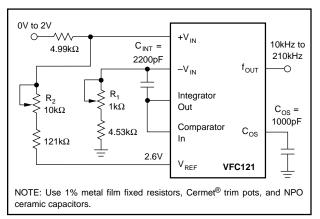

#### **OPERATION FROM 10kHz TO 210kHz**

The VFC121 is designed to provide an output frequency starting at 0Hz for a 0V input and increasing linearly to the full scale output frequency,  $f_{\rm FS}$ , at the full scale input voltage,  $V_{\rm FS}$ . For applications where low level inputs, near 0V, are critical, it may be inconvenient to have an output frequency approaching 0Hz. Figure 4 shows a circuit which transforms a 0V to 2V input level into output frequencies from 10kHz to 210kHz, by placing a resistor divider network between the input source and the  $V_{\rm REF}$  output of the VFC121. This produces a positive voltage at  $+V_{\rm IN}$  when the input to the circuit is grounded. This circuit makes use of the high input impedance at  $+V_{\rm IN}$ .

The transfer function of this circuit is:

$$V_{IN} = \frac{f_{OUT} - 10kHz}{100kHz} V$$

To trim the circuit, first apply 2V to the analog input, and adjust  $R_1$  to give a full scale output frequency of 210kHz. Then apply 0V to the analog input, and adjust  $R_2$  until the output frequency is 10kHz. For absolute precision, it may be necessary to make several iterations trimming  $R_1$  and  $R_2$ . In most cases, one iteration will be enough, since the effect of  $R_2$  on

FIGURE 4. Offsetting the Output Frequency.

full scale output frequency is attenuated by the divider network, which sees only a 0.6V total delta at full scale (2.6V at  $V_{REF}$  minus 2V full scale input) as compared with a 2.6V delta at a 0V input level.

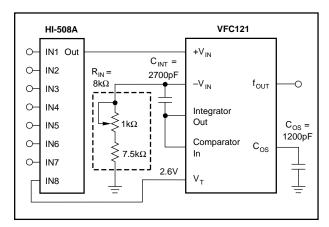

#### **USING THE VFC121 THERMOMETER VOLTAGE**

Because of the high input impedance of the VFC121 (which results from using the non-inverting input to the integrating op amp), it is relatively simple to use a standard multiplexer in front of the VFC121. One of the possible reason to multiplex the input to the VFC121 is to use it to track temperature changes in the operating environment of the electronics in a system, in addition to using the VFC121 in its normal mode to measure an analog signal.

Figure 5 shows a way to do this. In this circuit, the normal analog input signals to be multiplexed through the VFC121 have a full scale voltage of 2V, and generate a full scale output frequency of 100kHz. To measure the electronics system temperature, the user selects the multiplexer channel connected to the thermometer voltage on pin 3. A measured output frequency from the VFC121, with the multiplexer on channel 8, now corresponds to the temperature of the electronics as follows:

Temp (°C) =

$$\frac{\text{Output Frequency} - 13,650}{50}$$

FIGURE 5. Measuring System Temperature.