## **VSP2264**

**CCD Signal Processor With Timing Generator for Digital Cameras**

# Data Manual

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

## **Contents**

| Se | ction    |                                                | Page |

|----|----------|------------------------------------------------|------|

| 1  | Introdu  | uction                                         | 1    |

|    | 1.1      | Description                                    |      |

|    | 1.2      | Features                                       | 1    |

|    | 1.3      | Block Diagram                                  | 2    |

|    | 1.4      | Terminal Assignments                           | 3    |

|    | 1.5      | Package/Ordering Information                   | 3    |

|    | 1.6      | Terminal Functions                             | 4    |

| 2  | Theory   | y of Operation                                 | 7    |

|    | 2.1      | Introduction                                   |      |

|    | 2.2      | Timing Generator (TG)                          | 7    |

|    | 2.3      | Analog Front End                               |      |

|    | 2.4      | Correlated Double Sampler (CDS)                |      |

|    | 2.5      | Input Clamp                                    |      |

|    | 2.6      | 14-Bit A/D Converter                           |      |

|    | 2.7      | Digital Programmable-Gain Amplifier (DPGA)     |      |

|    | 2.8      | AFE Operating Timing                           |      |

|    | 2.9      | Black-Level Clamp Loop and 10-Bit DAC          |      |

|    | 2.10     | Preblanking and Data Latency                   |      |

|    | 2.10     | Power-Save Mode                                |      |

|    | 2.11     | Additional Output Delay Control                |      |

|    | 2.12     |                                                |      |

|    |          | Voltage Reference                              |      |

|    | 2.14     | Operating Modes                                |      |

|    | 2.15     | Functions                                      |      |

|    | 2.16     | TG Vertical-Rate Operation                     |      |

|    |          | 2.16.1 Frame Mode Operation                    |      |

|    |          | 2.16.2 Monitor Mode Operation (5A CCD)         |      |

|    | 2.17     | Still Function                                 |      |

|    |          | 2.17.1 Operation Outline                       |      |

|    |          | 2.17.2 Operation Sequence                      |      |

|    | 2.18     | Readout Function                               |      |

|    |          | 2.18.1 Operation Outline                       |      |

|    |          | 2.18.2 Operation Sequence                      |      |

|    | 2.19     | Power-Save-1 Function Explanation              | 19   |

|    |          | 2.19.1 Operation Outline                       | 19   |

|    |          | 2.19.2 Operation Sequence                      | 19   |

|    | 2.20     | Power-Save-2 Function Explanation              | 19   |

|    |          | 2.20.1 Operation Outline                       | 19   |

|    |          | 2.20.2 Operation Sequence                      | 19   |

|    | 2.21     | TG Pixel-Rate Operation                        | 20   |

|    |          | 2.21.1 High-Speed Pulse Adjustment             | 20   |

|    |          | 2.21.2 Default Timing Value                    |      |

|    | 2.22     | High-Speed Clock Timing Adjustable Range       |      |

|    |          | 2.22.1 ADCCK Clock                             |      |

|    |          | 2.22.2 SHP, SHD, PBLK, CLPOB, and CLPDM Clocks |      |

|    |          | 2.22.3 H1, HL, H2, and R Clocks                |      |

| 3  | Serial I | Interface Timing Specification                 |      |

| •  | Our lui  |                                                | 20   |

#### Contents

|   | 3.1        | Serial Data Format                                                                                                                     | 2 |

|---|------------|----------------------------------------------------------------------------------------------------------------------------------------|---|

|   | 3.1        | Register Default Values                                                                                                                |   |

|   | 5.2        | 3.2.1 Configuration Register                                                                                                           |   |

|   |            | 3.2.2 PGA Gain Register                                                                                                                |   |

|   |            | 3.2.3 AFE Standby Register                                                                                                             |   |

|   |            | 3.2.4 Operation Mode Register                                                                                                          |   |

|   |            | 3.2.5 Function Register                                                                                                                |   |

|   |            | 3.2.6 E-Shutter Register                                                                                                               |   |

|   |            | 3.2.7 VDHD Polarity Register                                                                                                           |   |

|   |            | 3.2.8 SUBSW Register                                                                                                                   |   |

|   |            | 3.2.9 V-Transfer Register                                                                                                              |   |

|   |            | 3.2.10 H1 Register                                                                                                                     |   |

|   |            |                                                                                                                                        |   |

|   |            | 3.2.11       H2 Register       32         3.2.12       R Register       32                                                             |   |

|   |            | <u> </u>                                                                                                                               |   |

|   |            | 3.2.13       SHP Register       33         3.2.14       SHD Register       33                                                          |   |

|   |            | ŭ                                                                                                                                      |   |

|   |            | 3.2.15 ADCCK Register                                                                                                                  |   |

|   |            |                                                                                                                                        |   |

|   | T::        | 3.2.17 Test AFE Register                                                                                                               |   |

| 4 | _          | Specification                                                                                                                          |   |

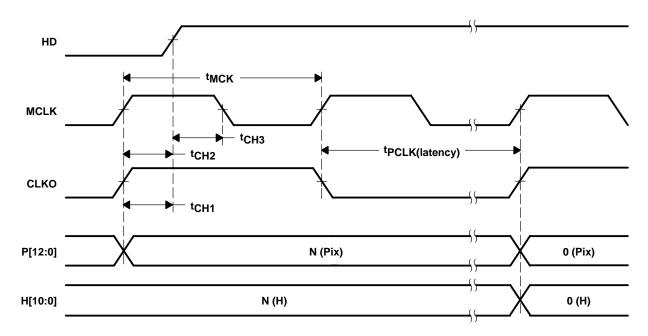

|   | 4.1<br>4.2 | HD-MCLK Relation                                                                                                                       |   |

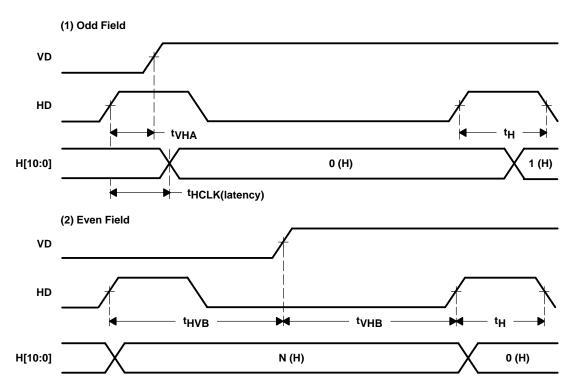

|   |            | VD-HD Relation                                                                                                                         |   |

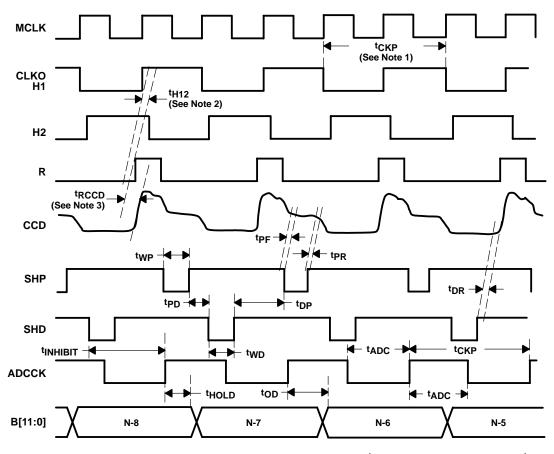

|   | 4.3        | High-Speed Timing Specifications                                                                                                       |   |

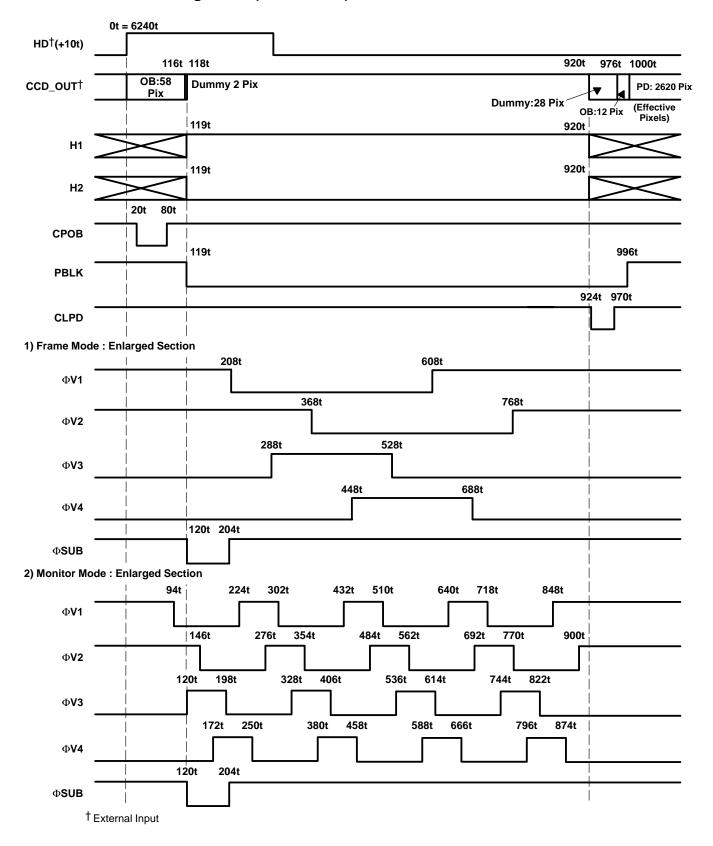

|   | 4.4        | Horizontal Timing Chart (for 5A CCD)                                                                                                   |   |

|   | 4.5        | Vertical Timing Chart (for 5A CCD)                                                                                                     |   |

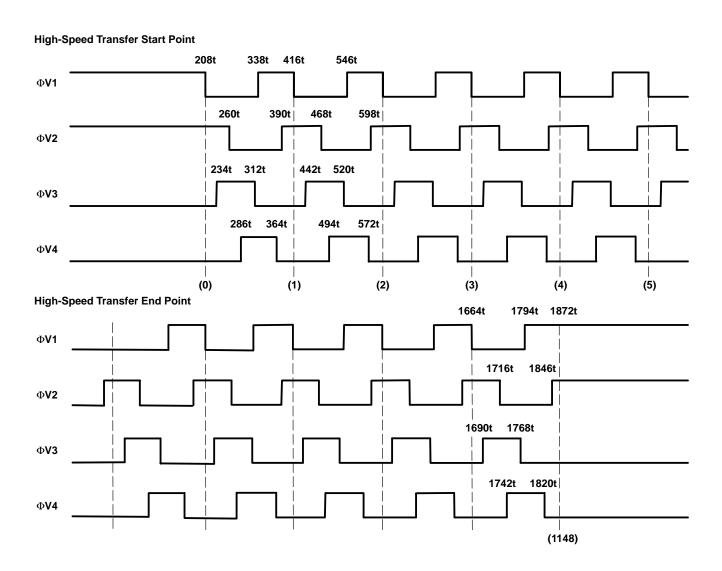

|   | 4.6        | Vertical High-Speed Transfer Timing Chart (for 5A CCD)                                                                                 |   |

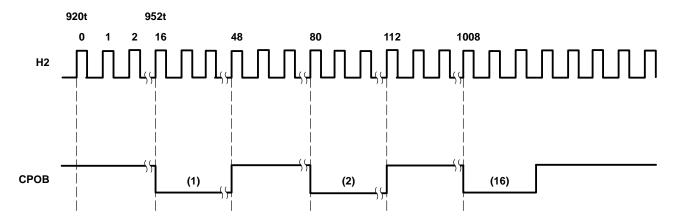

|   | 4.7        | Vertical Rate CPOB Timing Chart (for 5A CCD)                                                                                           |   |

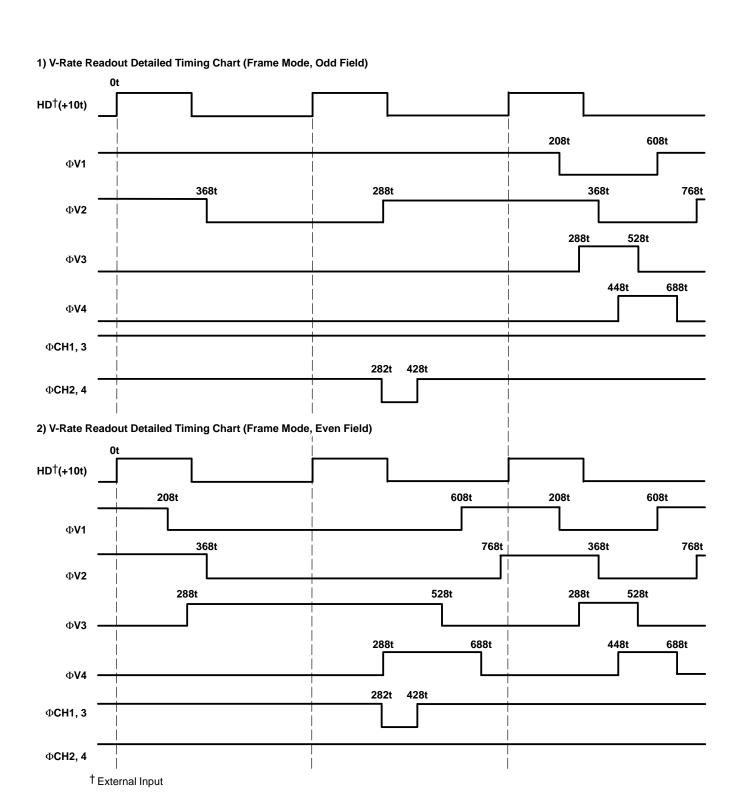

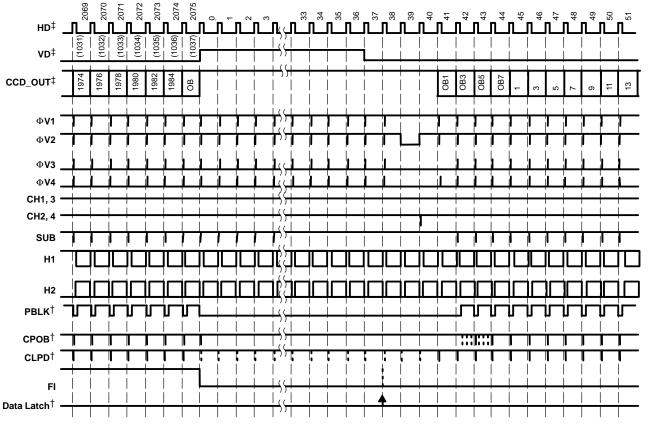

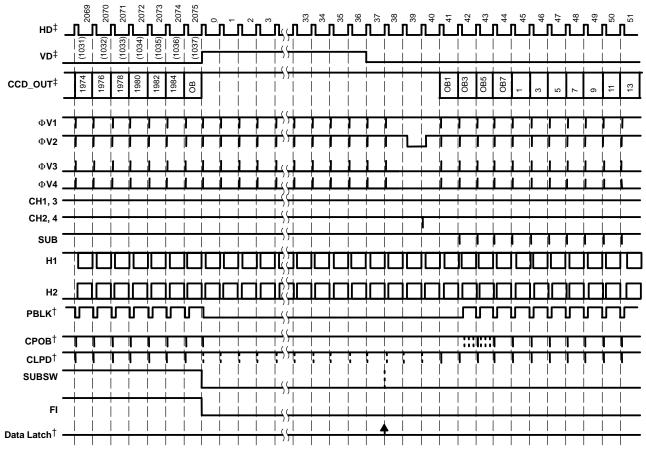

|   | 4.8        | Vertical Rate Timing (for 5A CCD) [frame mode—odd field]                                                                               |   |

|   | 4.9        | Vertical Rate Timing (for 5A CCD) [frame mode—even field]                                                                              |   |

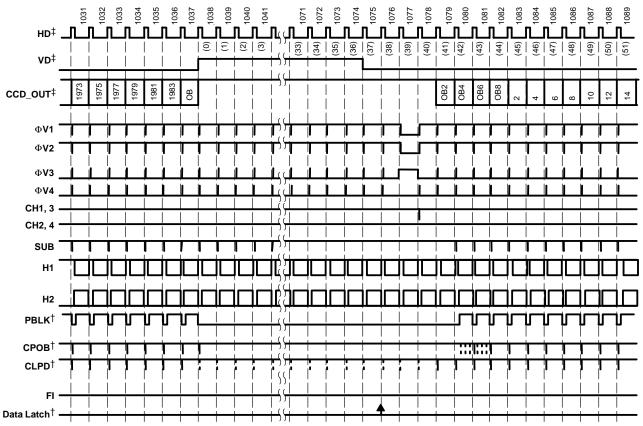

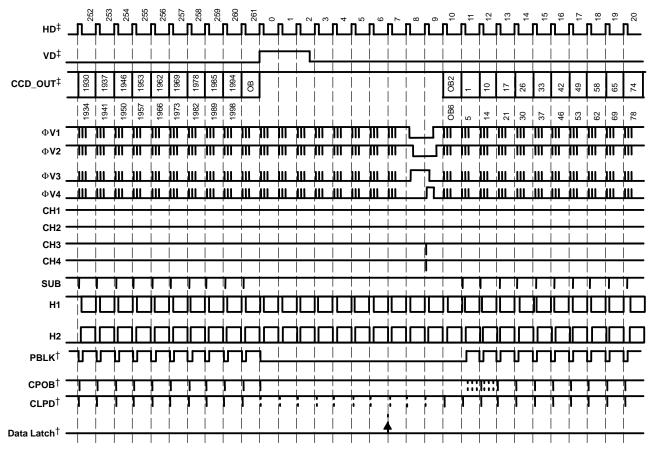

|   | 4.10       | Vertical Rate Timing (for 5A CCD) [frame mode—still function—odd field]                                                                |   |

|   | 4.11       | Vertical Rate Timing (for 5A CCD) [frame mode—still function—even field]                                                               |   |

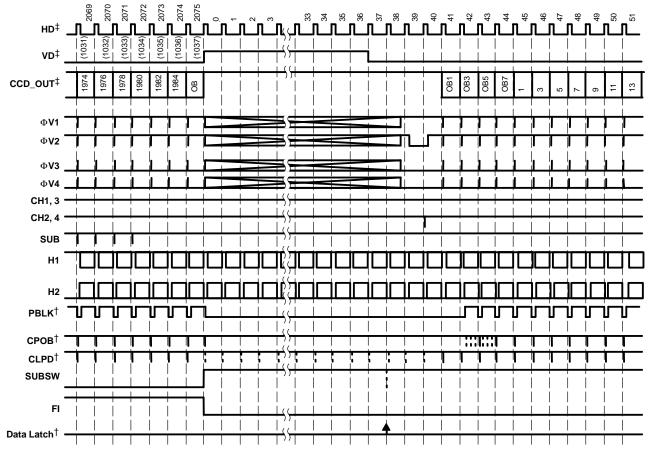

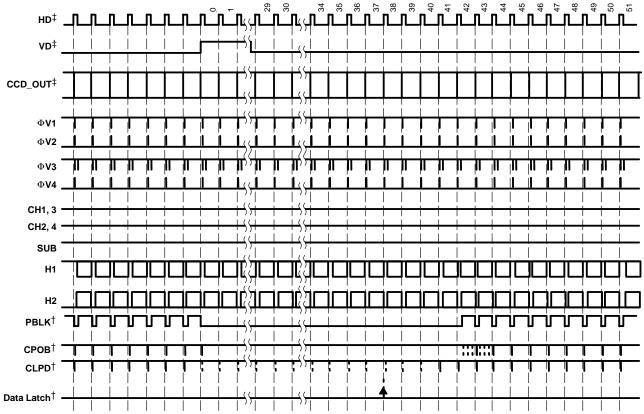

|   | 4.12       | Vertical Rate Timing (for 5A CCD) [frame mode—still function turnoff]                                                                  |   |

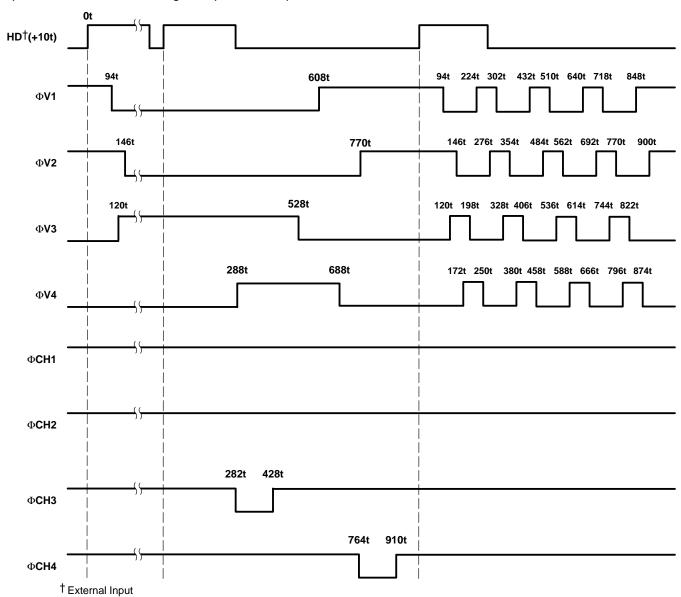

|   | 4.13       | Vertical Rate Timing (for 5A CCD) [monitor mode]                                                                                       |   |

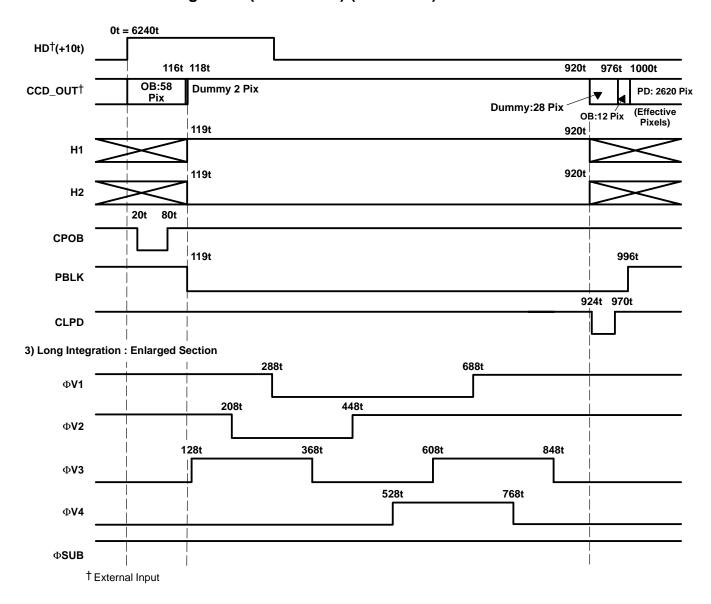

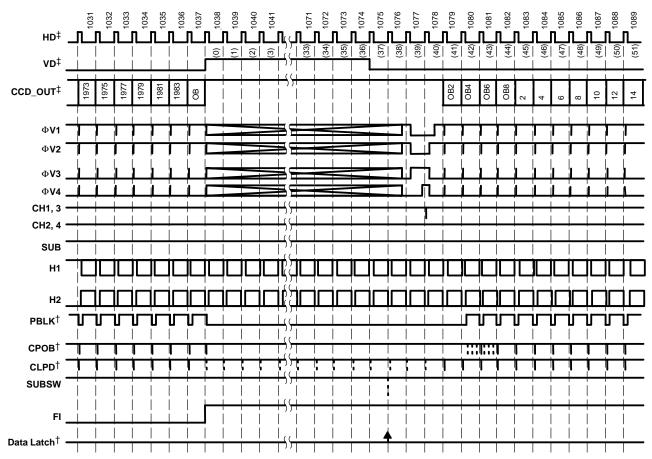

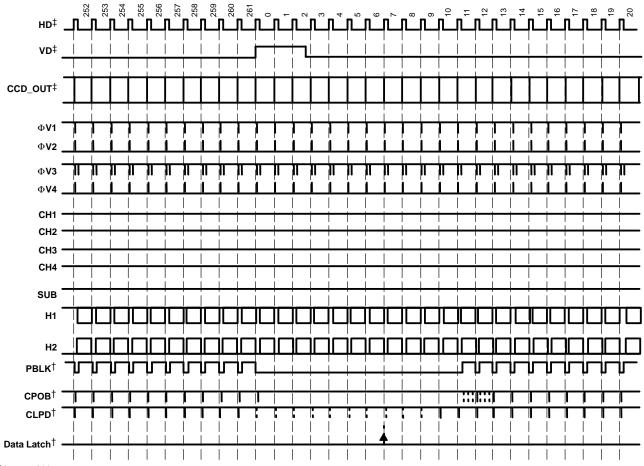

|   | 4.14       | Vertical Rate Timing (for 5A CCD) [frame mode—long integration function]                                                               |   |

| _ | 4.15       | Vertical Rate Timing (for 5A CCD) [monitor mode—long integration function]                                                             |   |

| 5 |            | al Characteristics                                                                                                                     |   |

|   | 5.1        | Absolute Maximum Ratings Over Operating Free-Air Temperature Range                                                                     | 1 |

|   | 5.2        | Electrical Characteristics, All Specifications at T <sub>A</sub> = 25°C, All Power Supply Voltages = 3 V, and Conversion Rate = 20 MHz | 1 |

| 6 | Mocho      | ical Data55                                                                                                                            |   |

| U | MICCIIA    | iidai Data                                                                                                                             | J |

CLECOEO V

## **List of Illustrations**

| Figure                         | Title                       | Page |

|--------------------------------|-----------------------------|------|

| 2-1 VSP2264 High-Speed Clock   | k Block Diagram             |      |

| 2-2 VSP2264 Line and Pixel Co  |                             |      |

| 2-3 VSP2264 Vertical-Rate Tim  | ing Block Diagram           |      |

| 2-4 VSP2264 AFE Simplified BI  | lock Diagram                |      |

| 2-5 CDS and Input Clamp Block  | k Diagram                   |      |

| 2-6 PGA Gain Characteristics . |                             |      |

| 2–7 Digital PGA and Black-Leve | el Clamp Loop Block Diagram | 13   |

|                                | List of Tables              |      |

| Table                          | Title                       | Page |

| 2–1 Function Table             |                             |      |

#### 1 Introduction

#### 1.1 Description

The VSP2264 is a complete mixed-signal IC for CCD signal processing with a CCD timing generator and A/D converter. The system synchronizes the master clock, HD, and VD. The VSP2264 supports all signal terminals that the CCD and the vertical driver require. The R driver and H driver synchronize the A/D converter clock phase to realize ideal performance. The CCD channel has correlated double sampling (CDS) to extract image information from the CCD output signal. The digital control gain curve is linear in dB, ranging from –6 dB to 42 dB. A black-level clamping circuit ensures black reference level accuracy and speeds black-level recovery after a gain change. Input signal clamping with a CDS offset adjustment function is available.

#### 1.2 Features

The VSP2264 supports the following features:

- CCD Signal Processing:

- Correlated Double Sampling (CDS)

- Programmable Black-Level Clamping

- Timing Generator With R and H Drivers

- Programmable Phase Control:

- Fine Step: 0.6 ns

- Wide Step: 8 ns

- Programmable Gain Amplifier (PGA): –6 dB to 42 dB Gain Range

- 12-Bit Digital Data Output:

- Up to 25-MHz Conversion Rate

- No Missing Codes

- Signal-to-Noise Ratio: 79 dB

- Portable Operation:

- Low Voltage: 3.0 V to 3.6 V

- Low Power: 130 mW at 3.0 V and 20 MHzStandby Plus Power Save-Mode: 39 mW

- MCLK-Off Mode: 6 mW

- Recommended CCD: MN39594 (Panasonic)

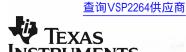

#### 1.3 Block Diagram

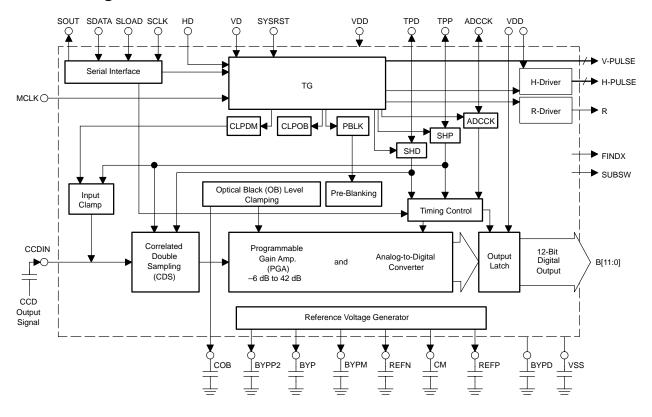

#### 1.4 Terminal Assignments

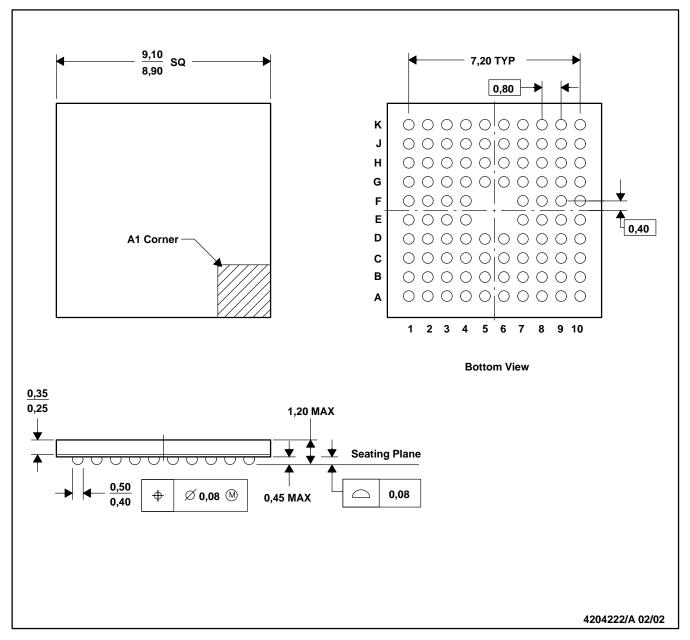

## 1.5 Package/Ordering Information

| PRODUCT    | PACKAGE | PACKAGE<br>CODE | OPERATION<br>TEMPERA-<br>TURE RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT MEDIA |

|------------|---------|-----------------|-------------------------------------|--------------------|--------------------|-----------------|

| V0D0004004 | 04001   |                 | VSP2264GSJ                          | 168-piece tray     |                    |                 |

| VSP2264GSJ | BGA 96  | GSJ             | –25°C to 85°C                       | VSP2264            | VSP2264GSJR        | Tape and reel   |

#### 1.6 Terminal Functions

|       | TERMINAL                                                                                            | TVDE  | DECORPTIONS                                            |

|-------|-----------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------|

| NAME  | NO.                                                                                                 | TYPE† | DESCRIPTIONS                                           |

| ADCCK | J2                                                                                                  | DO    | Clock for digital output buffer                        |

| AVDD  | A5, B4, C2, E1                                                                                      | Р     | Analog power supply                                    |

| AVSS  | B5, C3, C5, E2, E3                                                                                  | Р     | Analog ground                                          |

| В0    | J6                                                                                                  | DO    | A/D converter output, bit 0                            |

| B1    | J5                                                                                                  | DO    | A/D converter output, bit 1                            |

| B2    | K5                                                                                                  | DO    | A/D converter output, bit 2                            |

| В3    | H5                                                                                                  | DO    | A/D converter output, bit 3                            |

| B4    | K4                                                                                                  | DO    | A/D converter output, bit 4                            |

| B5    | J4                                                                                                  | DO    | A/D converter output, bit 5                            |

| B6    | H4                                                                                                  | DO    | A/D converter output, bit 6                            |

| B7    | K3                                                                                                  | DO    | A/D converter output, bit 7                            |

| B8    | J3                                                                                                  | DO    | A/D converter output, bit 8                            |

| В9    | H3                                                                                                  | DO    | A/D converter output, bit 9                            |

| B10   | K2                                                                                                  | DO    | A/D converter output, bit 10                           |

| B11   | K1                                                                                                  | DO    | A/D converter output, bit 11                           |

| BYP   | A2                                                                                                  | AO    | Internal reference C (bypass to ground)¶               |

| BYP2  | A1                                                                                                  | AO    | Internal reference P (bypass to ground)§               |

| BYPD  | C7                                                                                                  | AO    | Bypass                                                 |

| BYPM  | B1                                                                                                  | AO    | Internal reference N (bypass to ground)‡               |

| CCDIN | A4                                                                                                  | Al    | CCD signal input                                       |

| CH1   | J9                                                                                                  | DO    | Readout pulse 1                                        |

| CH2   | K10                                                                                                 | DO    | Readout pulse 2                                        |

| CH3   | J10                                                                                                 | DO    | Readout pulse 3                                        |

| CH4   | H9                                                                                                  | DO    | Readout pulse 4                                        |

| СМ    | C1                                                                                                  | AO    | A/D converter common-mode voltage (bypass to ground)¶  |

| СОВ   | B2                                                                                                  | AO    | Optical black clamp loop reference (bypass to ground)‡ |

| DVDD  | B6, B7, B8, C9, C10,<br>E10, G1, J8, K7                                                             | Р     | Digital power supply                                   |

| DVSS  | A6, A7, A8, B9, D9,<br>D10, F3, J7, K9                                                              | Р     | Digital ground                                         |

| FINDX | H6                                                                                                  | DO    | Field index                                            |

| H1    | B10                                                                                                 | DO    | CCD horizontal driver 1                                |

| H2    | D8                                                                                                  | DO    | CCD horizontal driver 2                                |

| HD    | H7                                                                                                  | DI    | HD input                                               |

| HL    | E9                                                                                                  | DO    | H1 last pulse                                          |

| MCLK  | C6                                                                                                  | DI    | Master clock input                                     |

| NC    | A3, A9, A10, B3, C4,<br>D3, D4, D5, D6, D7,<br>E4, E7, F4, F7, F8,<br>G2, G4, G5, G6, G7,<br>H8, K6 | _     | No connection                                          |

| R     | E8                                                                                                  | DO    | CCD reset driver                                       |

<sup>†</sup> Designators in TYPE column: P-Power supply and ground, DI-Digital input, DO-Digital output, AI-Analog input, AO-Analog output

<sup>‡</sup> Should be connected to ground with a bypass capacitor. A value of 0.1 μF to 0.22 μF is recommended; however, it depends on the application environment. See the *Black Level Clamp Loop and 10-Bit DAC* (Section 2.9) for details.

<sup>§</sup> Should be connected to ground with a bypass capacitor. A value of 400 pF to 1000 pF is recommended; however, it depends on the application environment. See *Voltage Reference* (Section 2.13) for details.

<sup>¶</sup> Should be connected to ground with a bypass capacitor (0.1 μF). See *Voltage Reference* (Section 2.13) for details.

|        | TERMINAL |       |                                                    |

|--------|----------|-------|----------------------------------------------------|

| NAME   | NO.      | TYPE† | DESCRIPTIONS                                       |

| REFN   | D2       | AO    | A/D converter negative voltage (bypass to ground)¶ |

| REFP   | D1       | AO    | A/D converter positive voltage (bypass to ground)¶ |

| SCLK   | H2       | DI    | Clock for serial-data shift                        |

| SDATA  | H1       | DI    | Serial-data input                                  |

| SLOAD  | G3       | DI    | Serial-data latch signal                           |

| SOUT   | J1       | DO    | Serial-data monitor out                            |

| SUB    | F10      | DO    | CCD substrate pulse                                |

| SUBSW  | F9       | DO    | CCD substrate bias control                         |

| SYSRST | C8       | DI    | System reset                                       |

| TPD    | F1       | DI/O  | SHD, CLPD                                          |

| TPP    | F2       | DI/O  | SHP, CPOB, PBLK                                    |

| V1     | H10      | DO    | V1 pulse                                           |

| V2     | G8       | DO    | V2 pulse                                           |

| V3     | G9       | DO    | V3 pulse                                           |

| V4     | G10      | DO    | V4 pulse                                           |

| VD     | K8       | DI    | VD input                                           |

<sup>†</sup> Designators in TYPE column: P–Power supply and ground, DI–Digital input, DO–Digital output, AI–Analog input, AO–Analog output ¶ Should be connected to ground with a bypass capacitor (0.1 µF). See *Voltage Reference* (Section 2.13) for details.

| Introduction |  |

|--------------|--|

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

|              |  |

## 2 Theory of Operation

#### 2.1 Introduction

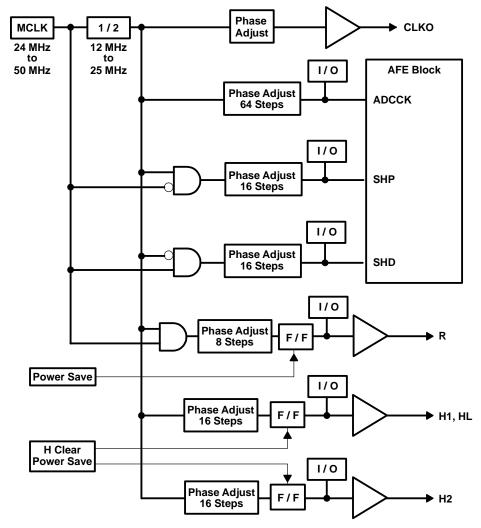

The VSP2264 is a high-resolution mixed-signal IC that contains key features associated with the processing of the CCD signal in a digital still camera (DSC). The VSP2264 integrates the analog front end (AFE) and CCD timing generator (TG) with the H and R drivers.

The AFE block includes a correlated double sampler (CDS), 14-bit analog-to-digital converter (ADC), digital gain amplifier, black-level clamp loop, input clamp, CDS timing generator, and voltage reference. The built-in TG generates not only horizontal (H-rate) timing, but also vertical (V-rate) timing for the specified CCD model. Optimized timing is generated by selecting the CCD model and operating mode through the serial interface.

#### 2.2 Timing Generator (TG)

The TG generates both H-rate timing and V-rate timing.

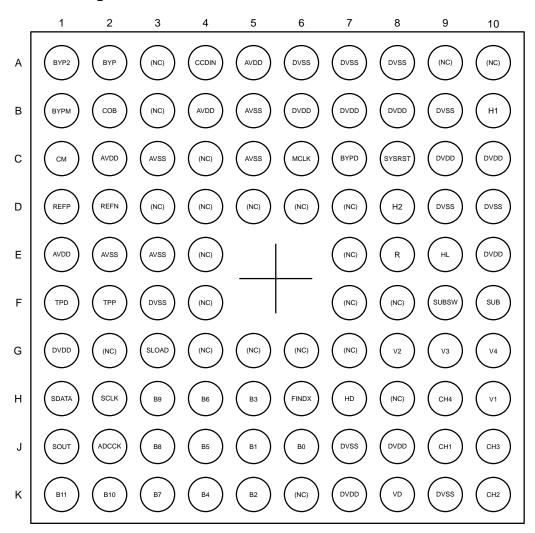

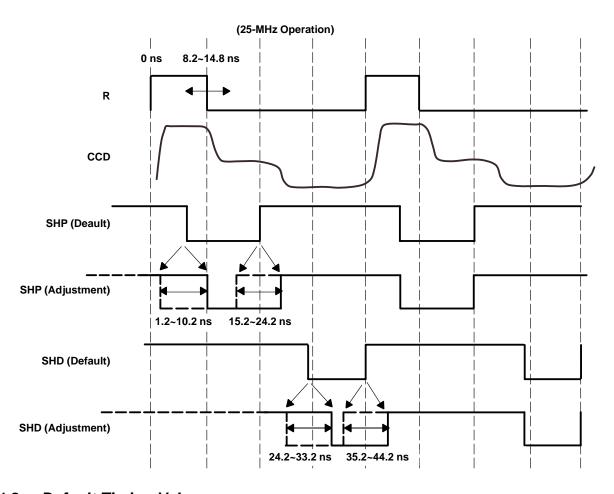

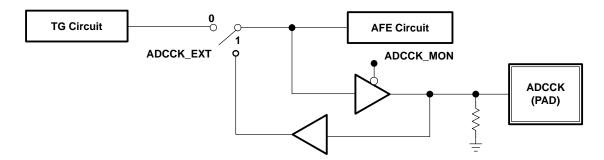

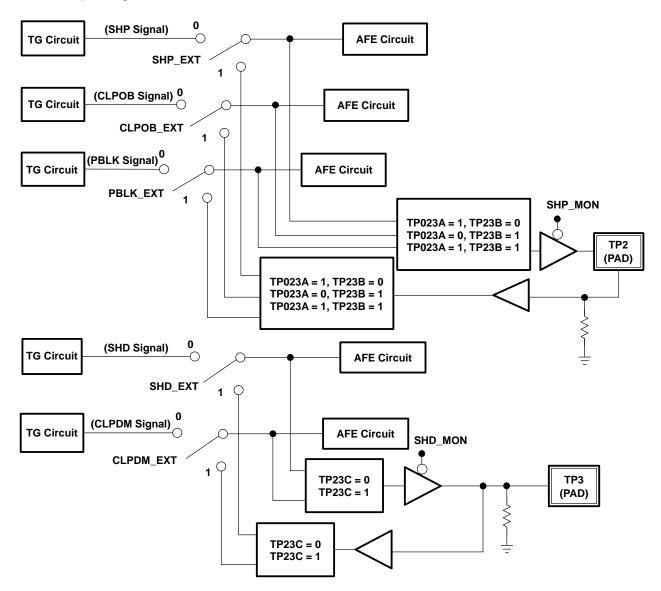

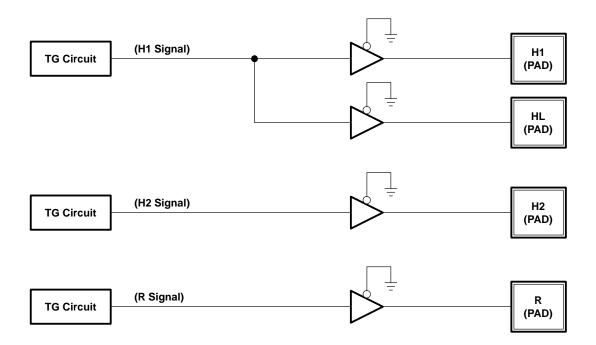

Figure 2–1 shows a high-speed timing block of the TG. This part generates six high-speed pulses for H-rate timing such as R, H1 and HL/H2, SHP/SHD, and ADCCK. These high-speed pulses are generated from the master clock, which has a speed of twice the pixel rate. The serial interface sets the amount of phase adjustment for these high-speed pulses in 16 steps (8 steps for R) with a minimum 0.6-ns pitch (four steps of 0.6 ns and four steps of 1.2 ns for R). The power mode controls the output driver enable/disable. An on-chip decoder calculates H clear according to the CCD model and operating mode. H1, HL, H2, and R can drive the CCD directly. The ADCCK, SHP, and SHD, signals support both the internal generation mode and the external supply mode.

Figure 2–1. VSP2264 High-Speed Clock Block Diagram

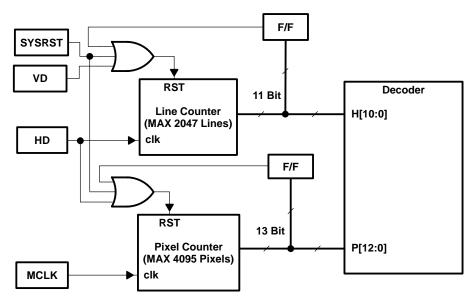

An on-chip V-rate timing generator creates all the signals that are required for specific CCD image sensors. The TG contains the line and pixel counters used to generate V-rate timing. Figure 2–2 is the block diagram of the line and pixel counter circuit. A maximum 2047 lines and 4095 pixels per line are supported in time scale.

Figure 2-2. VSP2264 Line and Pixel Counter Block Diagram

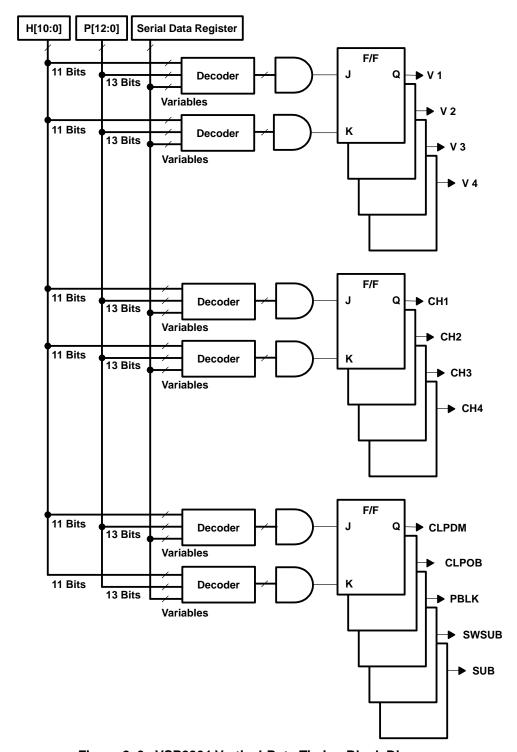

Figure 2–3 shows a V-rate timing generator block diagram. By one H (horizontal line) before CCD readout, serial data transfer must be completed by the user, and data must be loaded in the registers containing CCD model, operation mode, integration time, and electronic zoom area information. Just before CCD readout, information in the registers is supplied automatically to the decoder, which generates the V-rate signal using line counter and pixel counter data. Not only the signals used for the CCD, but also the strobe light control signal is supported. The CPOB, CLPD, and PBLK signals support both the internal generation mode and the external supply mode.

Figure 2–3. VSP2264 Vertical-Rate Timing Block Diagram

#### 2.3 Analog Front End

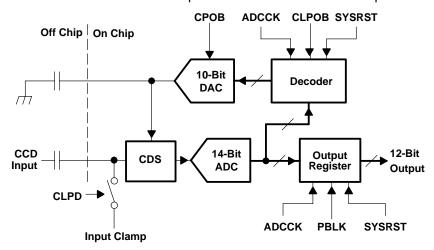

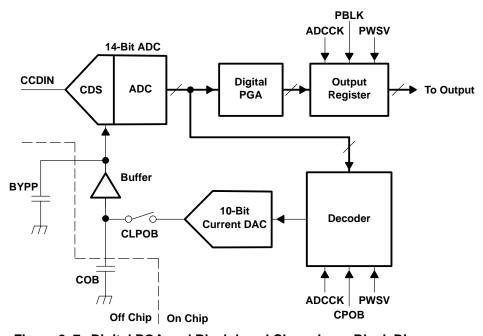

Figure 2–4 shows a simplified AFE block diagram of the VSP2264. The AFE circuit includes the correlated double sampler (CDS), a 14-bit analog-to-digital converter (ADC), digital gain amplifier, black-level clamp loop, input clamp, CDS timing generator, and voltage reference. An off-chip emitter-follower buffer or preamplifier is needed between the CCD output and the VSP2264 CCDIN input.

Figure 2-4. VSP2264 AFE Simplified Block Diagram

#### 2.4 Correlated Double Sampler (CDS)

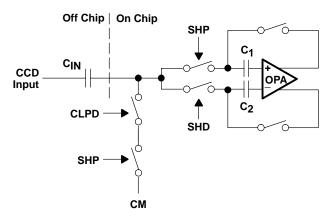

The output signal of a CCD image sensor is sampled twice during one pixel period, once during the reference interval and again during the data interval. Subtracting these two samples extracts the video information of the pixel and removes noise which is low frequency—the kTC and CCD reset noise. Figure 2–5 is a block diagram of the CDS.

The CDS is driven through an off-chip coupling capacitor  $C_{IN.}$  (A 0.1- $\mu$ F capacitor is recommended for  $C_{IN}$ ). AC coupling is highly recommended because the dc level of the CCD output signal is usually too high (several volts) for the CDS to work properly. The appropriate common-mode voltage for the CDS is around 0.5 V–1.5 V. The reference-level sampling is performed while SHP is active, and the voltage level is held on sampling capacitor  $C_1$  at the trailing edge of SHP. The data-level sampling is performed while SHD is active, and the voltage level is held on sampling capacitor  $C_2$  at the trailing edge of SHD. Then the subtraction of the two levels is performed by the switched-capacitor amplifier. The off-chip emitter follower or equivalent buffer must be able to drive more than 10 pF because the 10-pF sampling capacitor is seen at the input terminal. (Usually additional stray capacitance of a few pF is present.) The analog input signal range of the VSP2264 is about 1 Vp-p.

Figure 2-5. CDS and Input Clamp Block Diagram

#### 2.5 Input Clamp

The buffered CCD output is capacitively coupled to the VSP2264. The input clamp restores the dc component of the input signal which was lost with the ac-coupling and establishes the desired dc bias point for the CDS. Figure 2–5 also shows the block diagram of the input clamp. The input level is clamped to the internal reference voltage CM (1.5 V) during the dummy pixel interval. More specifically, the clamping function becomes active when both CLPD and SHP are active.

#### 2.6 14-Bit A/D Converter

The ADC uses a fully differential pipelined architecture of 1.5 bits per stage, which is well-suited for low-power, low-voltage, and high-speed applications. The ADC provides 14-bit resolution for the entire scale. The 1.5-bit-per-stage structure of the ADC is advantageous in realizing better linearity for a smaller signal level. Improved linearity occurs because large linearity errors tend to occur at specific points in the full scale, and the linearity improves for a signal level below any such specific point.

#### 2.7 Digital Programmable-Gain Amplifier (DPGA)

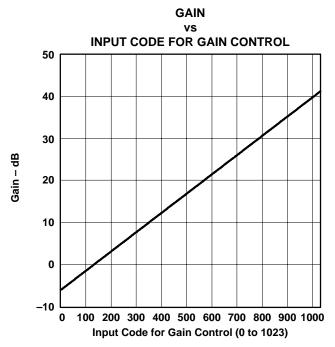

Figure 2–6 shows the characteristics of the DPGA gain. The DPGA provides a gain range of –6 dB to 42 dB, which is linear in dB. The gain, controlled by a digital code with 10-bit resolution, can be set through the serial interface; see the *Serial Interface Timing Specification* (Section 3) for details. The default value of the gain control code is 128 (PGA gain = 0 dB).

After powering on, the gain control value is undetermined. For this reason, it must be set to an appropriate value by using the serial interface or reset to the default value by strobing the SYSRST terminal.

Figure 2-6. PGA Gain Characteristics

Figure 2-7. Digital PGA and Black-Level Clamp Loop Block Diagram

#### 2.8 AFE Operating Timing

The CDS and the ADC are operated by SHP, SHD, and their derivative timing clocks are generated by the internal on-chip timing generator. The DPGA output register and decoder are operated by ADCCK. The digital output data is synchronized with ADCCK. The timing relationship between the CCD signal, SHP, SHD, ADCCK, and the output data is shown in the VSP2264 timing specification. CPOB activates the black-level clamp loop during the OB pixel interval and CLPD activates input clamping during the dummy pixel interval.

#### 2.9 Black-Level Clamp Loop and 10-Bit DAC

To extract the video information correctly, the CCD signal must be referenced to a well-established black level. The VSP2264 has an auto-zero loop (calibration loop) to establish the black level using the CCD optical black (OB) pixels. Figure 2–7 shows the block diagram of this loop. The input signal level from the OB pixels is identified as the real black level, and the loop is closed during this period (actually during the period while CPOB is active). While the auto-zero loop is closed, the difference between the ADC output code is evaluated and applied to the decoder, which then controls the 10-bit current DAC. The current DAC can charge or discharge the external capacitor at COB, depending on the sign of the code difference. The loop adjusts the voltage at COB, which sets the offset of the CDS to make the code difference zero. Thus the ADC output code converges to black level while CPOB is active and maintains the black level derived from the OB pixels after the loop has converged. CPOB performs the OB clamping of both channels simultaneously.

To determine the loop time constant, an off-chip capacitor is required and should be connected to the COB terminal. The time constant T is calculated using the following equation:

$$T = \frac{C}{(16384 \times I_{MIN})} \tag{1}$$

where C is the capacitor value connected to COB,  $I_{MIN}$  is the minimum current (0.15  $\mu$ A) of the control DAC in the OB level clamp loop, and 0.15  $\mu$ A is equivalent to 1 LSB of the DAC output current. When C is 0.1  $\mu$ F, then the time constant T is 40.7  $\mu$ S for ADC output codes from 0 LSB to 1543 LSB (the convergence curve becomes exponential).

For output codes above 1543 LSB, the current DAC injects constant (maximum) current into the capacitor and the convergence curve becomes linear. The slew rate SR is calculated using the following equation.

$$SR = \frac{I_{MAX}}{C}$$

(2)

where C is the capacitor value connected to COB.  $I_{MAX}$  is the maximum current (153  $\mu$ A) of the control DAC in the OB level clamp loop, and 153  $\mu$ A is equivalent to 1023 LSB of the DAC output current.

Generally, OB level clamping at high speed causes clamping noise. However, the noise can be reduced by making C large. On the other hand, a large C requires a much longer time to restore from the power-save mode or right after the power goes ON. Therefore, 0.1  $\mu$ F to 0.22  $\mu$ F is considered a reasonable value for C. If the application environment requires a value outside this range, making careful adjustments by trial and error is recommended.

The OB clamp level (the pedestal level) is programmable through the serial interface; see the *Serial Interface Timing Specification* (Section 3) for details. Also see the *Serial Interface Timing Specification* section for the relationship between input code and the OB clamp level.

The black-level clamp loop not only eliminates the CCD black-level offset, but also eliminates the offsets of the VSP2264 CDS and ADC themselves.

#### 2.10 Preblanking and Data Latency

The VSP2264 has a preblanking function. When PBLK = LOW, the digital outputs all become zero at the ninth rising edge of ADCCK, counting from the time when PBLK becomes LOW, to accommodate the clock latency of the VSP2264.

Data latency of this device is seven clock cycles. The digital output data come out on the rising edge of ADCCK with a delay of seven clock cycles.

Some CCDs have a large transient output signal during blanking intervals. If the input voltage is higher than the supply rail or lower than the ground rail by 0.3 V, then protection diodes are turned on, limiting the input voltage. Such a high-swing signal can cause device damage to the VSP2264 and should be avoided.

#### 2.11 Power-Save Mode

For the purpose of power savings, the VSP2264 can be put into the power-save plus standby mode by serial interface command. In this mode, all the function blocks are disabled, the A/D outputs all go to zero and the TG output goes to high or low status as determined by the configuration of the serial interface command. The power consumption drops to 39 mW. Because all the bypass capacitors discharge during this mode, a substantial time (usually on the order of 200–300 ms) is required to restore from the power-save plus standby mode.

#### 2.12 Additional Output Delay Control

The VSP2264 can control the delay time of output data by setting registers through the serial interface. In some cases, the transition of output data affects analog performance. Generally, this is avoided by adjusting the timing of ADCCK. In case the ADCCK timing cannot be adjusted, the additional output delay control is effective for reducing the influence of transient noise. Refer to the *Serial Interface Timing Specification* (Section 3) for details.

#### 2.13 Voltage Reference

All the reference voltages and bias currents used on the device are created from internal band-gap circuitry.

The CDS and the ADC mainly use three reference voltages, REFP (1.75 V), REFN (1.25 V) and CM (1.5 V). REFP and REFN are buffered on-chip. CM is derived as the midvoltage of the resistor chain connecting REFP and REFN internally. The ADC full-scale range is determined by twice the voltage difference between REFP and REFN.

REFP, REFN, and CM should be heavily decoupled with appropriate capacitors.

OPERATION MODE

5A CCD†

FRAME

MONITOR

LONG INTEGRATION (CHDEL)

√

√

POWER SAVE (PWSV)

√

√

STILL (STIL)

√

√

E-SHUTTER

√

√

Table 2-1. Function Table

#### 2.14 Operating Modes

- Frame mode enables each pixel output with interlace.

- Monitor mode enables the output of four from every 16 lines.

#### 2.15 Functions

- The long integration function stops CCD readout (CH1, CH2, CH3, CH4 pulse) at the end of one frame, as defined by the serial data instruction.

- The power save function stops all clocks and preserves high or low levels according to the serial data instruction.

- The e-shutter function enables electronic shutter operation by the serial data instruction.

<sup>†</sup> Recommended CCD MN39594 (Panasonic)

#### 2.16 TG Vertical-Rate Operation

#### 2.16.1 Frame Mode Operation

#### 2.16.1.1 Operation Outline

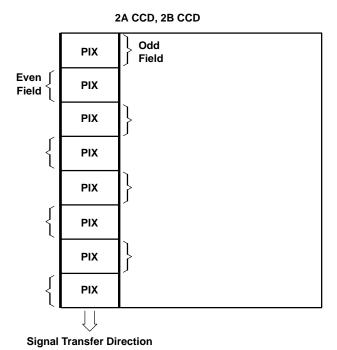

Horizontal output of the CCD is generated by reading out individual pixels vertically at 2-pixel intervals, and successively repeating the readout for each pixel column. Either the odd field or the even field is selectable.

#### 2.16.1.2 Operation Sequence

- 1. Set serial data address 000100 bits 6-5 = 01.

- 2. Define odd/even by the relation of VD and HD or by serial address 000100 bits 8-7.

#### 2.16.2 Monitor Mode Operation (5A CCD)

#### 2.16.2.1 Operation Outline

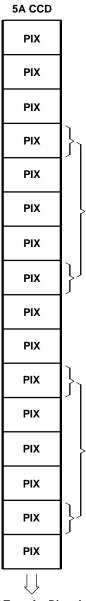

Horizontal output of the CCD is generated by summing pixels vertically in groups of two, and successively repeating the readout for each pixel column. The second and sixth of every 16 consecutive vertical pixels are selected for summing together, as are the ninth and 13th.

#### 2.16.2.2 Operation Sequence

- 1. Set serial data address 000100 bits 6-5 = 11.

- 2. Operation proceeds without regard for odd-/even-field considerations.

**Signal Transfer Direction**

#### 2.17 Still Function

#### 2.17.1 Operation Outline

Smear dump operation is available.

SUB output is controlled by using the serial data instruction.

The SUBSW level follows the still mode condition. SUBSW can be used for the SUB bias control circuit when using a mechanical shutter. It is recommended to set the toggling position of SUBSW after the mechanical shutter has closed.

#### 2.17.2 Operation Sequence

- Set the serial data address 000101.

Input bit 2 = H, and set to the still mode.

The SUB output is defined by the serial data instruction. Integration time is defined by ES 000111, and can be performed after step 2, following.

- 2. Input a pulse to SLOAD and send the serial data. Upon going to the still mode, during the horizontal scan time preceding a readout operation, a SUB output is made for every H and charge is drained. After the end of the SUB pulse, the SUB output goes high and charge integration starts.

- 3. Set the serial data address 001010. Input the STVV data in bits 0–5 for SUBSW rise time definition.

- 4. Input a pulse to SLOAD and send the serial data.

- 5. Input a VD rising edge. SUBSW goes high at the position defined by the serial data. Positioning uses the next HD input pulse as 1. A vertical high-speed pulse, which corresponds to more than the number of one field to V-CCD, is applied.

- 6. After one field of signal has been read out, input a VD pulse again and read out the signal, which was not read out during step 5. Input serial data for address 000101 and bit 2 = L to exit from the still mode.

- 7. Input a VD pulse after one field of CCD output signal has completed. SUBSW goes low at the next HD rising edge.

#### NOTES:

- 1. Do not use the electronic shutter in the still mode, when SUBSW is high.

- 2. For the VD-to-VD interval, more than 90 counts of the HD-to-HD interval are required.

#### 2.18 Readout Function

#### 2.18.1 Operation Outline

This mode can control a pair of pixels, which are mixed in the vertical transfer CCD. Control is not accomplished by the HD-VD phase, but by the serial data instruction.

#### 2.18.2 Operation Sequence

- 1. Set serial data address 000100. At the same time, input data bit 7 = H and set the serial data control mode. In this case, readout timing is defined by the value of bit 8. When bit 8 = L, the odd field is read out; when bit 8 = H, the even field is read out.

- 2. Input a pulse to SLOAD and transfer the serial data.

NOTE:

If bit 7 = L, odd/even readout recognition is made by the HD–VD phase difference.

#### 2.19 Power-Save-1 Function Explanation

#### 2.19.1 Operation Outline

Power save by stopping H1, HL, R, V3, V4, CH1, CH2, CH3, CH4, SUB = Fixed high H2, SHP, SHD, ADCCK, V1, V2 = Fixed low

#### 2.19.2 Operation Sequence

- 1. Set serial data 000100. Set data bit PWSV1 = H to enter the power-save mode.

- 2. Input a pulse for SLOAD and transfer the serial data.

- 3. Transfer data into the TG.

NOTES:

- 1. After release from this mode, signal performance is not assured during 1 V.

- 2. Do not use both power-save modes 1 and 2 at the same time.

#### 2.20 Power-Save-2 Function Explanation

#### 2.20.1 Operation Outline

Power save by stopping H1, HL, H2, R, SHP, SHD, ADCCK, V1-V4, CH1-CH4, SUB.

#### 2.20.2 Operation Sequence

(same as power-save mode 1)

NOTES:

(same as power-save mode 1)

#### 2.21 TG Pixel-Rate Operation

#### 2.21.1 High-Speed Pulse Adjustment

For a high-speed pulse, the CCD signal sampling time is adjustable (see serial data addresses from 001100 to 010111). The default value is set as follows.

#### 2.21.2 Default Timing Value

- R: Standard reset duration is 25% of cycle.

- SHP: Standard rise point is 50% of cycle, based on a 3-ns CCD signal delay. Actual delay depends on the system.

- SHD: Standard rise point is 100% of cycle, based on a 3-ns CCD signal delay. Actual delay depends on the system.

- H1: Standard duration is 50% of cycle.

- H1 and H2 are complementary. The crossover point of the H1 rising edge and H2 falling edge should be higher than VDD/2.

- H2: Standard duration is 50% of cycle.

- ADCCK: Standard rise and fall points are 25% and 75% of cycle, respectively, based on a 3-ns CCD signal delay.

## 2.22 High-Speed Clock Timing Adjustable Range

The timing reference for the values in the following table is the R pulse rising edge.

|            |         | 25-MF | lz OPER | TION | 20-MI | lz OPERA | ATION | 12-1 | MHz OPERAT | ION  | NOTE  |

|------------|---------|-------|---------|------|-------|----------|-------|------|------------|------|-------|

| TERMINAL   | EDGE    | MIN   | STD     | MAX  | MIN   | STD      | MAX   | MIN  | STD        | MAX  | NOTE  |

|            | Rising  | 0     | 0       | 0    | 0     | 0        | 0     | 0    | 0          | 0    | 0%    |

| R          | Falling | 8.2   | 10      | 14.8 | 10.7  | 12.5     | 17.3  | 19.0 | 20.8       | 25.6 | 25%   |

| OUD        | Rising  | 15.2  | 20      | 24.2 | 20.2  | 25       | 29.2  | 36.9 | 41.7       | 45.9 | 50%   |

| SHP        | Falling | 1.2   | 6       | 10.2 | 6.2   | 11       | 15.2  | 22.9 | 27.7       | 31.9 | 14 ns |

| OLID.      | Rising  | 35.2  | 40      | 44.2 | 45.2  | 50       | 54.2  | 78.5 | 83.3       | 87.5 | 100%  |

| SHD        | Falling | 24.2  | 29      | 33.2 | 34.2  | 39       | 43.2  | 67.5 | 72.3       | 76.5 | 11 ns |

|            | Rising  | -4.2  | 0       | 4.8  | -4.2  | 0        | 4.8   | -4.2 | 0          | 4.8  | 0%    |

| H1, HL     | Falling | 15.8  | 20      | 24.8 | 20.8  | 25       | 29.8  | 37.5 | 41.7       | 46.5 | 50%   |

|            | Rising  | 15.8  | 20      | 24.8 | 20.8  | 25       | 29.8  | 37.5 | 41.7       | 46.5 | 50%   |

| H2         | Falling | -4.2  | 0       | 4.8  | -4.2  | 0        | 4.8   | -4.2 | 0          | 4.8  | 0%    |

| ADCCK      | Rising  | 3.6   | 6       | 12.6 | 7.1   | 9.5      | 16.1  | 15.1 | 17.5       | 24.1 | 25%   |

| (phase 00) | Falling | 23.6  | 26      | 32.6 | 32.1  | 34.5     | 41.1  | 56.7 | 59.1       | 65.7 | 75%   |

#### 2.22.1 ADCCK Clock

The signal can be monitored on the ADCCK I/O terminal. External input is available via the serial data instruction.

#### 2.22.2 SHP, SHD, PBLK, CLPOB, and CLPDM Clocks

Signal monitoring and signal input for SHP, SHD, PBLK, CLPOB, and CLPDM are available using the corresponding I/O terminal.

## 2.22.3 H1, HL, H2, and R Clocks

High-speed signals for the CCD (H1, HL, H2, R) are available using the corresponding I/O terminals.

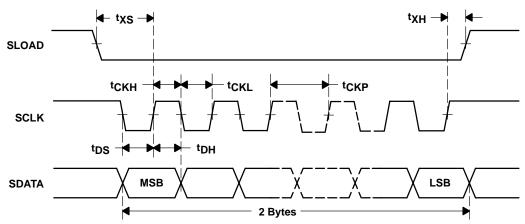

## 3 Serial Interface Timing Specification

|                  | PARAMETER                 | MIN | TYP | MAX | UNIT |

|------------------|---------------------------|-----|-----|-----|------|

| <sup>t</sup> CKP | Clock period              | 100 |     |     | ns   |

| <sup>t</sup> CKH | Clock high-pulse duration | 40  |     |     | ns   |

| <sup>t</sup> CKL | Clock low-pulse duration  | 40  |     |     | ns   |

| tDS              | Data setup time           | 30  |     |     | ns   |

| <sup>t</sup> DH  | Data hold time            | 30  |     |     | ns   |

| txs              | SLOAD to SCLK setup time  | 30  |     |     | ns   |

| <sup>t</sup> XH  | SCLK to SLOAD hold time   | 30  |     |     | ns   |

A data shift operation should decode at the rising edge of SCLK while SLOAD is LOW. At the rising edge of SLOAD, 2 bytes of input data are loaded into the parallel latch in the VSP2264.

When the input serial data is longer than 2 bytes (16 bits), the last 2 bytes become effective and the previous bits are lost.

| SD15<br>MSB | SD14                       | SD13 | SD12 | SD11 | SD10<br>LSB | SD9 | SD8                           | SD7 | SD6 | SD5 | SD4 | SD3 | SD2 | SD1 | SD0 |

|-------------|----------------------------|------|------|------|-------------|-----|-------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| A5          | A4                         | А3   | A2   | A1   | A0          | D9  | D8                            | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|             | Register address (default) |      |      |      |             |     | Register data (default value) |     |     |     |     |     |     |     |     |

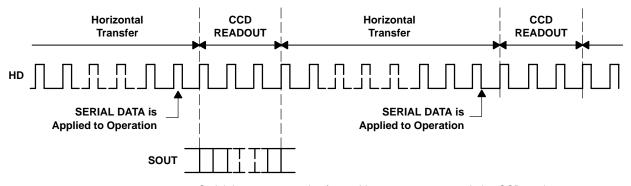

Serial data for the AFE is applied to the operation at every ADCCK edge (addresses 000000 to 000011).

Serial data input for the TG should be made when the CCD operation is changed.

Serial data for the TG is applied to the operation 1 H before every readout. (CCD) starting point (addresses 000100 to 011000).

Serial data output, starting from address 000000, occurs during CCD readout.

## 3.1 Serial Data Format

| Register<br>Name   | A5 | A4 | А3 | A2 | A1 | Α0 | D9<br>MSB     | D8           | D7          | D6     | D5           | D4          | D3              | D2       | D1           | D0<br>LSB       |

|--------------------|----|----|----|----|----|----|---------------|--------------|-------------|--------|--------------|-------------|-----------------|----------|--------------|-----------------|

| Configura<br>-tion | 0  | 0  | 0  | 0  | 0  | 0  | 0             | O3           | O2          | O1     | 00           | P2          | P1              | P0       | J1           | J0              |

| PGA gain           | 0  | 0  | 0  | 0  | 0  | 1  | G9            | G8           | G7          | G6     | G5           | G4          | G3              | G2       | G1           | G0              |

| Reserved           | 0  | 0  | 0  | 0  | 1  | 0  | _             | _            | _           | _      | _            | _           | _               | _        | _            | _               |

| AFE<br>standby     | 0  | 0  | 0  | 0  | 1  | 1  | 0             | 0            | 0           | 0      | 0            | C0          | 0               | 0        | 0            | 0               |

| Operation mode     | 0  | 0  | 0  | 1  | 0  | 0  | ES10<br>MSB   | CHMOD2       | CHMOD1      | DRV2   | DRV1         | 1           | 0               | 1        | PWSV2        | PWSV1           |

| Function           | 0  | 0  | 0  | 1  | 0  | 1  | 0             | 0            | 0           | 0      | 0            | 1           | 0               | STILL    | 0            | CHDEL           |

| Reserved           | 0  | 0  | 0  | 1  | 1  | 0  | _             | _            | _           | _      | _            | _           | _               | _        | _            | _               |

| E-shutter          | 0  | 0  | 0  | 1  | 1  | 1  | ES9           | ES8          | ES7         | ES6    | ES5          | ES4         | ES3             | ES2      | ES1          | ES0<br>LSB      |

| VDHD<br>polarity   | 0  | 0  | 1  | 0  | 0  | 0  | OBSEL2        | CLPDSEL      | POLHV       | 0      | 0            | 0           | 1               | FINDX    | 0            | 0               |

| SUBSW              | 0  | 0  | 1  | 0  | 0  | 1  | SUBSW9<br>MSB | SUBSW8       | SUBSW7      | SUBSW6 | SUBSW5       | SUBSW4      | SUBSW3          | SUBSW2   | SUBSW1       | SUBSW0<br>LSB   |

| V-transfer         | 0  | 0  | 1  | 0  | 1  | 0  | 0             | 0            | 0           | 0      | STVV5<br>MSB | STVV4       | STVV3           | STVV2    | STVV1        | STVV0<br>LSB    |

| Reserved           | 0  | 0  | 1  | 0  | 1  | 1  | _             | _            | _           | _      | _            | _           | _               | _        | _            | _               |

| H1                 | 0  | 0  | 1  | 1  | 0  | 0  | 0             | 0            | 0           | 0      | 0            | 0           | H1fa3<br>MSB    | H1fa2    | H1fa1        | H1fa0<br>LSB    |

| Reserved           | 0  | 0  | 1  | 1  | 0  | 1  | _             | _            | _           | _      | _            | _           | _               | _        | _            | _               |

| Reserved           | 0  | 0  | 1  | 1  | 1  | 0  | _             | _            | _           | _      | _            | _           | _               | _        | _            | _               |

| H2                 | 0  | 0  | 1  | 1  | 1  | 1  | 0             | 0            | 0           | 0      | 0            | 0           | H2ri3<br>MSB    | H2ri2    | H2ri1        | H2ri0<br>LSB    |

| Reserved           | 0  | 1  | 0  | 0  | 0  | 0  | _             | _            | _           | _      | _            | _           | _               | _        | _            | _               |

| R                  | 0  | 1  | 0  | 0  | 0  | 1  | 0             | 0            | 0           | 0      | 0            | Rfa4<br>MSB | Rfa3            | Rfa2     | Rfa1         | Rfa0<br>LSB     |

| SHP                | 0  | 1  | 0  | 0  | 1  | 0  | SHP<br>ext    | SHP<br>mon   | 0           | 0      | 0            | 0           | SHPfa3<br>MSB   | SHPfa2   | SHPfa1       | SHPfa0<br>LSB   |

| Reserved           | 0  | 1  | 0  | 0  | 1  | 1  | _             | _            | _           | _      | _            | _           | _               | _        | _            | _               |

| SHD                | 0  | 1  | 0  | 1  | 0  | 0  | SHD<br>ext    | SHD<br>mon   | 0           | 0      | 0            | 0           | SHDfa3<br>MSB   | SHDfa2   | SHDfa1       | SHPfa0<br>LSB   |

| Reserved           | 0  | 1  | 0  | 1  | 0  | 1  | _             | _            | _           | _      | _            | _           | _               | _        | _            | _               |

| ADCCK              | 0  | 1  | 0  | 1  | 1  | 0  | ADCCK ext     | ADCCK<br>mon | 0           | 0      | 0            | 0           | ADCCKri3<br>MSB | ADCCKri2 | ADCCKri1     | ADCCKri0<br>LSB |

| ADCCK2             | 0  | 1  | 0  | 1  | 1  | 1  | ADCKQ1        | ADCKQ2       | 0           | 0      | 0            | 0           | 0               | 0        | 0            | 0               |

| Test AFE           | 0  | 1  | 1  | 0  | 0  | 0  | TP23<br>MSB   | TP23         | TP23<br>LSB | 0      | CLPDM<br>ext | 0           | PBLK<br>ext     | 0        | CLPOB<br>ext | 0               |

Do not input values into reserved registers.

## 3.2 Register Default Values

| DECISION NAME  |    |    | 40 | 40 |    | 140 | DEFAULT VALUE |

|----------------|----|----|----|----|----|-----|---------------|

| REGISTER NAME  | A5 | A4 | А3 | A2 | A1 | A0  | DEFAULT VALUE |

| Configuration  | 0  | 0  | 0  | 0  | 0  | 0   | 01 0000 0000  |

| PGA gain       | 0  | 0  | 0  | 0  | 0  | 1   | 00 1000 0000  |

| Reserved       | 0  | 0  | 0  | 0  | 1  | 0   | 00 0000 0000  |

| AFE standby    | 0  | 0  | 0  | 0  | 1  | 1   | 00 0000 0000  |

| Operation mode | 0  | 0  | 0  | 1  | 0  | 0   | 00 0111 0100  |

| Function       | 0  | 0  | 0  | 1  | 0  | 1   | 00 0001 0000  |

| Reserved       | 0  | 0  | 0  | 1  | 1  | 0   | 00 0000 0000  |

| E-shutter      | 0  | 0  | 0  | 1  | 1  | 1   | 01 1101 1001  |

| VDHD polarity  | 0  | 0  | 1  | 0  | 0  | 0   | 00 0000 1100  |

| SUBSW          | 0  | 0  | 1  | 0  | 0  | 1   | 00 0000 0000  |

| V-transfer     | 0  | 0  | 1  | 0  | 1  | 0   | 00 0000 0000  |

| Reserved       | 0  | 0  | 1  | 0  | 1  | 1   | 00 0000 0000  |

| H1             | 0  | 0  | 1  | 1  | 0  | 0   | 00 0000 0111  |

| Reserved       | 0  | 0  | 1  | 1  | 0  | 1   | 00 0000 0000  |

| Reserved       | 0  | 0  | 1  | 1  | 1  | 0   | 00 0000 0000  |

| H2             | 0  | 0  | 1  | 1  | 1  | 1   | 00 0000 0111  |

| Reserved       | 0  | 1  | 0  | 0  | 0  | 0   | 00 0000 0000  |

| R              | 0  | 1  | 0  | 0  | 0  | 1   | 00 0000 0000  |

| SHP            | 0  | 1  | 0  | 0  | 1  | 0   | 01 0000 1000  |

| Reserved       | 0  | 1  | 0  | 0  | 1  | 1   | 00 0000 0000  |

| SHD            | 0  | 1  | 0  | 1  | 0  | 0   | 01 0000 1000  |

| Reserved       | 0  | 1  | 0  | 1  | 0  | 1   | 00 0000 0000  |

| ADCCK          | 0  | 1  | 0  | 1  | 1  | 0   | 01 0000 0100  |

| ADCCK2         | 0  | 1  | 0  | 1  | 1  | 1   | 01 0000 0000  |

| Test AFE       | 0  | 1  | 1  | 0  | 0  | 0   | 00 0000 0000  |

## 3.2.1 Configuration Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9 | SD8 | SD7 | SD6 | SD5 | SD4 | SD3 | SD2 | SD1 | SD0 |

|------|---------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0       | 0    | 0    | 0    | 0    | 0   | О3  | O2  | O1  | 00  | P2  | P1  | P0  | J1  | J0  |

|      | default |      |      |      |      | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| BIT     | NAME   | DEFAULT VALUE | DESCRIPTION                                                                                                                                                                                                                                                   |

|---------|--------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD8-SD5 | O[3:0] | 1000          | Programmable OB clamp level  0000 = 2 LSB  0001 = 18 LSB  0010 = 34 LSB  0011 = 50 LSB  0100 = 66 LSB  0101 = 82 LSB  0110 = 98 LSB  0111 = 114 LSB  1000 = 130 LSB (default)  1001 = 146 LSB  1010 = 162 LSB  1011 = 178 LSB  1110 = 291 LSB  1111 = 242 LSB |

| SD4     | P2     | 0             | SHP/SHD clock polarity 0 = Polarity of SHP/SHD is active low. 1 = Polarity of SHP/SHD is active high.                                                                                                                                                         |

| SD3     | P1     | 0             | CLPOB clock polarity  0 = Polarity of CLPOB is active low.  1 = Polarity of CLPOB is active high.                                                                                                                                                             |

| SD2     | P0     | 0             | CLPDM clock polarity  0 = Polarity of CLPDM is active low.  1 = Polarity of CLPDM is active high.                                                                                                                                                             |

| SD1-SD0 | J[1:0] | 00            | Additional output delay  00 = Additional delay is 0 ns.  01 = Additional delay is 5 ns (typical).  10 = Additional delay is 10 ns (typical).  11 = Additional delay is 13 ns (typical).                                                                       |

## 3.2.2 PGA Gain Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9 | SD8 | SD7 | SD6 | SD5 | SD4 | SD3 | SD2 | SD1 | SD0 |

|------|---------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0       | 0    | 0    | 0    | 1    | G9  | G8  | G7  | G6  | G5  | G4  | F3  | G2  | G1  | G0  |

|      | default |      |      |      |      |     | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| BIT     | NAME   | DEFAULT VALUE | DESCRIPTION                                                                                                                                                                                                                                   |

|---------|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD9-SD0 | G[9:0] | 00 1000 0000  | PGA gain characteristics<br>00 0000 0000 = -6 dB<br>00 0011 0101 = -3 dB<br>00 1000 0000 = 0 dB<br>00 1011 0101 = 3 dB<br>00 1111 1111 = 6 dB<br>01 0111 1111 = 12 dB<br>10 0010 0000 = 20 dB<br>11 0100 1000 = 34 dB<br>11 1111 1111 = 42 dB |

## 3.2.3 AFE Standby Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9 | SD8 | SD7 | SD6 | SD5 | SD4 | SD3 | SD2 | SD1 | SD0 |

|------|---------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0    | 0       | 0    | 0    | 1    | 1    | 0   | 0   | 0   | 0   | 0   | C0  | 0   | 0   | 0   | 0   |

|      | default |      |      |      |      |     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| BIT | NAME | DEFAULT VALUE | DESCRIPTION                                                                              |

|-----|------|---------------|------------------------------------------------------------------------------------------|

| SD4 | C0   | 0             | AFE operation mode (normal/standby)  0 = AFE normal operation mode  1 = AFE standby mode |

## 3.2.4 Operation Mode Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9         | SD8    | SD7    | SD6  | SD5  | SD4 | SD3 | SD2 | SD1   | SD0   |

|------|---------|------|------|------|------|-------------|--------|--------|------|------|-----|-----|-----|-------|-------|

| 0    | 0       | 0    | 1    | 0    | 0    | ES10<br>MSB | CHMOD2 | CHMOD1 | DRV2 | DRV1 | 1   | 0   | 1   | PWSV2 | PWSV1 |

|      | default |      |      |      |      | 0           | 0      | 0      | 1    | 1    | 1   | 0   | 1   | 0     | 0     |

| BIT     | NAME               | DEFAULT<br>VALUE | DESCRIPTION                                                                                                                                                                  |

|---------|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD9     | ES10               | 0                | SUB (SUB pin) pulse number instruction. MSB of the 11 bits ES[10:0]. The 10 bits ES[9:0] are located in SD9 through SD0 at address 000111.                                   |

| SD8-SD7 | CHMOD[2:1]         | 00               | Operation mode:  X0 = HD-VD phase (default)  01 = Odd field  11 = Even field                                                                                                 |

| SD6-SD5 | DRV [2:1]          | 11               | Operation mode: 00 = Reserved 01 = Frame mode 10 = Reserved 11 = Monitor mode (default)                                                                                      |

| SD4-SD2 | _                  | 101              | Reserved; input required                                                                                                                                                     |

| SD1     | PWSV2†             | 0                | Output pin state: 0 = normal operation 1 = (H1, R, V3, V4, CH1, CH2, CH3, CH4, SUB, SHP, SHD, CPOB, CLPDM, PBLK, H2, ADCCK, V1, V2= Fixed low)                               |

| SD0     | PWSV1 <sup>†</sup> | 0                | Output pin state:  0 = normal operation <sup>‡</sup> 1 = (H1, R, V3, V4, CH1, CH2, CH3, CH4, SUB, SHP, SHD, CPOB, CLPDM, PBLK = Fixed high)  (H2, ADCCK, V1, V2 = Fixed low) |

<sup>†</sup> When PWSV1 = PWSV2 = 1, automatically set to PWSV1 = 1, PWSV2 = 0.

## 3.2.5 Function Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9 | SD8 | SD7 | SD6 | SD5 | SD4 | SD3 | SD2   | SD1 | SD0   |

|------|---------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-------|-----|-------|

| 0    | 0       | 0    | 1    | 0    | 1    | 0   | 0   | 0   | 0   | 0   | 1   | 0   | STILL | 0   | CHDEL |

|      | default |      |      |      |      | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0     | 0   | 0     |

| ВІТ | NAME  | DEFAULT<br>VALUE | DESCRIPTION                                                                                              |

|-----|-------|------------------|----------------------------------------------------------------------------------------------------------|

| SD4 |       | 1                | Reserved; input required                                                                                 |

| SD3 |       | 0                | Reserved; input required                                                                                 |

| SD2 | STILL | 0                | Function: 0 = normal operation 1 = Still function (see <i>Still Function</i> , Section 2.17)             |

| SD1 | _     | 0                | Reserved; input required                                                                                 |

| SD0 | CHDEL | 0                | Output pin: 0 = normal operation 1 = CH1, CH2, CH3, CH4 terminals are fixed high for longer integration. |

## 3.2.6 E-Shutter Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9 | SD8 | SD7 | SD6 | SD5 | SD4 | SD3 | SD2 | SD1 | SD0        |

|------|---------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------------|

| 0    | 0       | 0    | 1    | 1    | 1    | ES9 | ES8 | ES7 | ES6 | ES5 | ES4 | ES3 | ES2 | ES1 | ES0<br>LSB |

|      | default |      |      |      |      | 0   | 1   | 1   | 1   | 0   | 1   | 1   | 0   | 0   | 1          |

| BIT     | NAME    | DEFAULT VALUE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |

|---------|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD9-SD0 | ES[9:0] | 01 1101 1001  | SUB (SUB terminal) pulse number instruction SUB pulse number is defined using a binary code from $0 \le n \le A-3$ . Note that A is an HD number between two successive VD pulses. When $n=0$ , SUB pulse is zero. SUB pulse starts 2 H after readout (CH1 to CH4). Integration time is defined by $(A-n-1)$ H. Initial: 70.3 ms integration at 50 MHz (MCLK) in frame mode |

#### 3.2.7 VDHD Polarity Register

| SD15 | SD14 | SD13 | SD12 | SD11 | SD10 | SD9    | SD8     | SD7   | SD6 | SD5 | SD4 | SD3 | SD2   | SD1 | SD0 |

|------|------|------|------|------|------|--------|---------|-------|-----|-----|-----|-----|-------|-----|-----|

| 0    | 0    | 1    | 0    | 0    | 0    | OBSEL2 | CLPDSEL | POLHV | 0   | 0   | 0   | 1   | FINDX | 0   | 0   |

|      |      | def  | ault |      |      | 0      | 0       | 0     | 0   | 0   | 0   | 1   | 1     | 0   | 0   |

| BIT     | NAME    | DEFAULT VALUE | DESCRIPTION                                                                                                                                                                                                               |

|---------|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD9     | OBSEL2  | 0             | V-rate OB selection: 0 = Vertical-rate CPOB timing 1 = negative                                                                                                                                                           |

| SD8     | CLPDSEL | 0             | V-blank CLPD selection: 0 = V-blank 1 = Continuous CLPD                                                                                                                                                                   |

| SD7     | POLHV   | 0             | VD, HD polarity selection: 0 = positive 1 = negative                                                                                                                                                                      |

| SD6-SD4 | _       | 0             | Reserved; input required                                                                                                                                                                                                  |

| SD3     |         | 1             | Reserved; input required                                                                                                                                                                                                  |

| SD2     | FINDX   | 1             | Field indes selection:  0 = Active  If CHMOD[1:0] = 00, FINDX follows the VD-HD phase.  If CHMOD[1:0] = 01, FINDX = 0.  If CHMOD[1:0] = 10, FINDX follows the VD-HD phase.  If CHMOD[1:0] = 11, FINDX = 1.  1 = Fixed low |

#### 3.2.8 SUBSW Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9           | SD8    | SD7    | SD6    | SD5    | SD4    | SD3    | SD2    | SD1    | SD0           |

|------|---------|------|------|------|------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| 0    | 0       | 1    | 0    | 0    | 1    | SUBSW9<br>MSB | SUBSW8 | SUBSW7 | SUBSW6 | SUBSW5 | SUBSW4 | SUBSW3 | SUBSW2 | SUBSW1 | SUBSW0<br>LSB |

|      | default |      |      | 0    | 0    | 0             | 0      | 0      | 0      | 0      | 0      | 0      | 0      |        |               |

| BIT     | NAME       | DEFAULT VALUE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |

|---------|------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD9-SD0 | SUBSW[9:0] | 00 0000 0000  | SUBSW signal output position when in the still function. SUBSW signal output position is defined by 1 H step using a binary code from $0 \le \text{SUBSW} \le \text{A} - \text{STW} - 40$ . Note that A is an HD number between two successive VD pulses. When $10 = 0$ , SUBSW must be kept 0. Count as 1 the first HD after VD or after a trigger pulse. |

#### 3.2.9 V-Transfer Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9 | SD8 | SD7 | SD6 | SD5          | SD4   | SD3   | SD2   | SD1   | SD0          |

|------|---------|------|------|------|------|-----|-----|-----|-----|--------------|-------|-------|-------|-------|--------------|

| 0    | 0       | 1    | 0    | 1    | 0    | 0   | 0   | 0   | 0   | STVV5<br>MSB | STVV4 | STVV3 | STVV2 | STVV1 | STVV0<br>LSB |

|      | default |      |      |      |      | 0   | 0   | 0   | 0   | 0            | 0     | 0     | 0     | 0     | 0            |

| BIT     | NAME      | DEFAULT VALUE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |

|---------|-----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD9-SD8 |           | 00            | Reserved; input required                                                                                                                                                                                                                                                                                                                            |

| SD6     |           | 0             | Reserved; input required                                                                                                                                                                                                                                                                                                                            |

| SD5-SD0 | STVV[5:0] | 00 0000       | Vertical high speed transfer position control when in the still function. Position is controlled by 1-H steps, counting in binary code from $0 \le STW \le 63$ , where $STW \le A - SUBSW - 40$ . Note that A is an HD number between two successive VD pulses. When $n0 = 0$ , vertical high speed transfer synchronizes to the SUBSW rising edge. |

#### 3.2.10 H1 Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9 | SD8 | SD7 | SD6 | SD5 | SD4 | SD3          | SD2   | SD1   | SD0          |

|------|---------|------|------|------|------|-----|-----|-----|-----|-----|-----|--------------|-------|-------|--------------|

| 0    | 0       | 1    | 1    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | H1fa3<br>MSB | H1fa2 | H1fa1 | H1fa0<br>LSB |

|      | default |      |      |      |      |     | 0   | 0   | 0   | 0   | 0   | 0            | 1     | 1     | 1            |

| BIT     | NAME      | DEFAULT VALUE | DESCRIPTION                                                                                                                     |

|---------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------|

| SD3-SD0 | H1fa[3:0] | 0111          | H1 delay definition using 4 bits:  1111 = H1 delay, maximum  :  0111 = H1 delay, typical (default)  :  0000 = H1 delay, minimum |

### 3.2.11 H2 Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9 | SD8 | SD7 | SD6 | SD5 | SD4 | SD3          | SD2   | SD1   | SD0          |

|------|---------|------|------|------|------|-----|-----|-----|-----|-----|-----|--------------|-------|-------|--------------|

| 0    | 0       | 1    | 1    | 1    | 1    | 0   | 0   | 0   | 0   | 0   | 0   | H2ri3<br>MSB | H2ri2 | H2ri1 | H2ri0<br>LSB |

|      | default |      |      |      |      | 0   | 0   | 0   | 0   | 0   | 0   | 0            | 1     | 1     | 1            |

| BIT     | NAME      | DEFAULT VALUE | DESCRIPTION                                                                                                                         |

|---------|-----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------|

| SD3-SD0 | H2ri[3:0] | 0111          | H2 delay edge definition using 4 bits  1111 = H2 delay, maximum  :  0111 = H2 delay, typical (default)  :  0000 = H2 delay, minimum |

#### 3.2.12 R Register

| SD15 | SD14    | SD13 | SD12 | SD11 | SD10 | SD9 | SD8 | SD7 | SD6 | SD5 | SD4         | SD3  | SD2  | SD1  | SD0         |

|------|---------|------|------|------|------|-----|-----|-----|-----|-----|-------------|------|------|------|-------------|

| 0    | 1       | 0    | 0    | 0    | 1    | 0   | 0   | 0   | 0   | 0   | Rfa4<br>MSB | Rfa3 | Rfa2 | Rfa1 | Rfa0<br>LSB |

|      | default |      |      |      |      |     | 0   | 0   | 0   | 0   | 0           | 0    | 0    | 0    | 0           |

| BIT     | NAME     | DEFAULT VALUE | DESCRIPTION                                                                          |

|---------|----------|---------------|--------------------------------------------------------------------------------------|

| SD4_SD0 | Rfa[4:0] | 0 0000        | R falling edge definition using 5 bits R duration, maximum = 111XX 110XX 101XX 100XX |

|         |          |               | R duration, typical = 0XX00<br>0XX01<br>0XX10<br>R duration, minimum = 0XX11         |

#### 3.2.13 SHP Register