# VT6305 PCI 1394 Host Controller

1394.A OHCI Link Layer Controller for the PCI Bus

**Revision 0.2 March 10, 2000**

VIA TECHNOLOGIES, INC.

# **Copyright Notice:**

Copyright © 1998 VIA Technologies Incorporated. Printed in the United States. All RIGHTS RESERVED.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of VIA Technologies Incorporated.

VT6305 may only be used to identify a product of VIA Technologies, Inc.

is a registered trademark of VIA Technologies, Incorporated.

Windows 95<sup>™</sup>, Windows 98<sup>™</sup>, Windows NT<sup>™</sup>, and Plug and Play<sup>™</sup> are registered trademarks of Microsoft Corp.

PCI<sup>™</sup> is a registered trademark of the PCI Special Interest Group.

All trademarks are the properties of their respective owners.

## **Disclaimer Notice:**

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. The information provided by this document is believed to be accurate and reliable to the publication date of this document. However, VIA Technologies assumes no responsibility for any errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

# Offices:

USA Office: 1045 Mission Court Fremont, CA 94539 USA

Tel: (510) 683-3300 Fax: (510) 683-3301 Taipei Office:

8<sup>th</sup> Floor, No. 533 Chung-Cheng Road, Hsin-Tien

Taipei, Taiwan ROC Tel: (886-2) 218-5452 Fax: (886-2) 218-5453

# **Online Services:**

Web Page: <a href="http://www.via.com.tw">http://www.via.com.tw</a> -or- <a href="http://www.viatech.com">http://www.viatech.com</a>

FTP Server: <u>ftp://ftp.via.com.tw</u>

BBS: <u>886-2-2185208</u>

# **REVISION HISTORY**

| Document Release | Date    | Revision                                                            |    |

|------------------|---------|---------------------------------------------------------------------|----|

|                  |         |                                                                     | S  |

| Revision 0.1     | 5/19/98 | Initial release as VT83C574                                         | DH |

| Revision 0.2     | 7/31/98 | Changed part # to VT6305 Revised pinouts and added pin descriptions | DH |

# TABLE OF CONTENTS

| REVISION HISTORY                                          |     |

|-----------------------------------------------------------|-----|

| TABLE OF CONTENTS                                         | I   |

| LIST OF FIGURES                                           | III |

| LIST OF TABLES                                            | III |

| OVERVIEW                                                  |     |

| PINOUTS                                                   |     |

| PIN DIAGRAM                                               | 3   |

| PIN LIST                                                  | 4   |

| PIN DESCRIPTIONS                                          | 5   |

| REGISTERS                                                 | 8   |

| REGISTER OVERVIEW                                         | 8   |

| REGISTER DESCRIPTIONS                                     | 11  |

| 1394 Host Controller Configuration Registers (Function 0) |     |

| Configuration Space Header                                |     |

| Controller-Specific Configuration Registers               |     |

| 1394 Host Controller Memory-Space Registers               | 14  |

| Autonomous CSR Resources                                  |     |

| Bus Management CSR Registers                              |     |

| HC Control Registers                                      |     |

| Self-ID Control Registers                                 |     |

| Channel Mask Registers                                    |     |

| Interrupt Registers                                       |     |

| Link Control Registers                                    |     |

| PHY Control Registers                                     |     |

| Filter Registers                                          |     |

| Asynchronous Transmit & Receive Context Registers         | 24  |

| Isochronous Transmit Context Registers                    |     |

| Isochronous Receive Context Registers                     |     |

| ELECTRICAL SPECIFICATIONS                                 | 29  |

| ABSOLUTE MAXIMUM RATINGS                                  |     |

| DC CHARACTERISTICS                                        |     |

| PACKAGE MECHANICAL SPECIFICATIONS                         | 30  |

# **LIST OF FIGURES**

| FIGURE 1. VT6305 CHIP BLOCK DIAGRAM                        | 2 |

|------------------------------------------------------------|---|

| FIGURE 2. VT6305 PIN DIAGRAM (TOP VIEW)                    |   |

| FIGURE 3. VT6305 PIN LIST (ALPHABETICAL ORDER)             | 4 |

| FIGURE 4. MECHANICAL SPECIFICATIONS – 128 PIN PQFP PACKAGE |   |

|                                                            |   |

|                                                            |   |

|                                                            |   |

|                                                            |   |

|                                                            |   |

|                                                            |   |

|                                                            |   |

|                                                            |   |

| LIST OF TABLES                                             |   |

|                                                            |   |

|                                                            |   |

# VT6305 PCI 1394 HOST CONTROLLER

# 1394.A OHCI LINK LAYER CONTROLLER FOR THE PCI BUS

- Single Chip PCI Host Controller for IEEE P1394.A

- Data Transfers of 100 / 200 / 400 MHz

- Embedded IEEE 1394.A Link Core

- 32 bit CRC generator and checker for receive and transmit data

- Built-in isochronous and asynchronous receive and transmit FIFOs for packets

- 2 / 4 / 8 bit data interface to external discrete PHY

- Compliant with IEEE 1394.A Specification Release 1.0

- OHCI Compliant Programming Interface

- Descriptor based isochronous and asynchronous DMA channels for receive / transmit packets

- Compliant with 1394 Open HCI Specification v0.94

- 32-Bit Power-Managed PCI Bus Interface

- High-performance bus mastering support

- Byte alignment to run in both little-endian (x86/PCI) and byte-swapped big-endian (PowerMac/PCI) environments

- Compliant with PCI Bus Power Management Specification v1.0

- 3.3V Power Supply with 5V Tolerant Inputs

- 0.35um, Low Power CMOS Process

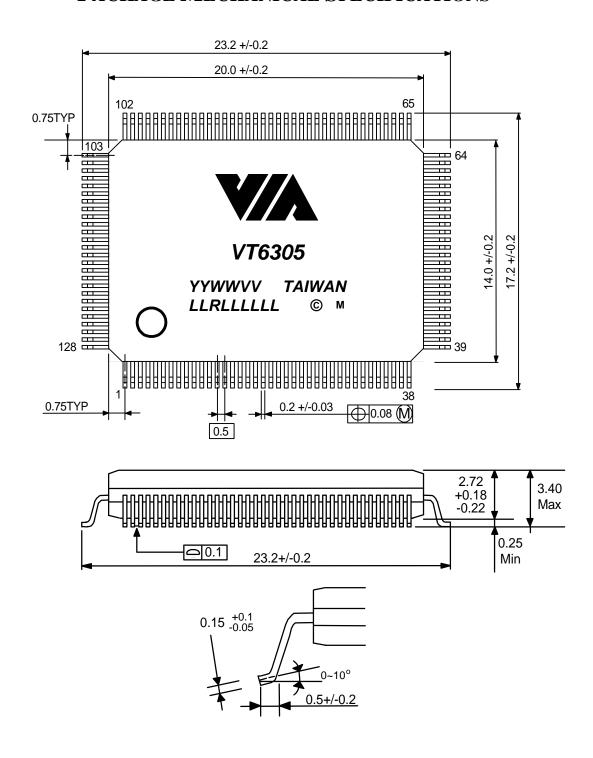

- 128-Pin PQFP Package

- PCB Reference Designs & Schematics Available

... 00 1/ 1 10 2000

## **OVERVIEW**

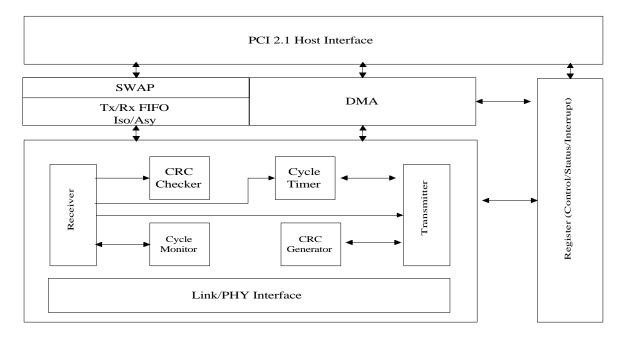

The VT6305 IEEE 1394 Open HCI Link Controller provides high performance serial connectivity. It implements the Link layer for IEEE 1394.A release v1.0 and is compliant with Open HCI with DMA engine support for high performance data transfer. It has a PCI host bus interface.

The VT6305 supports 100, 200 and 400 Mbits/sec transmission. Depending on transmission speed, the Link / PHY connection is provided through a 2- / 4- / 8-bit interface operating at 50 MHz. The VT6305 services two types of data packets: asynchronous and isochronous (real time). The 1394 link core performs arbitration requesting, packet generation and checking, and bus cycle master operations. It also has root node capability and performs cycle and retry operations.

The VT6305 is ready to provide industry-standard IEEE 1394 peripheral connections for desktop and mobile PC platforms. Support for the VT6305 will be built into Microsoft Windows 98 (Memphis) and Windows NT 5.0.

Figure 1. VT6305 Chip Block Diagram

2 . . . 0.2 M . I 10 2000

#### **PINOUTS**

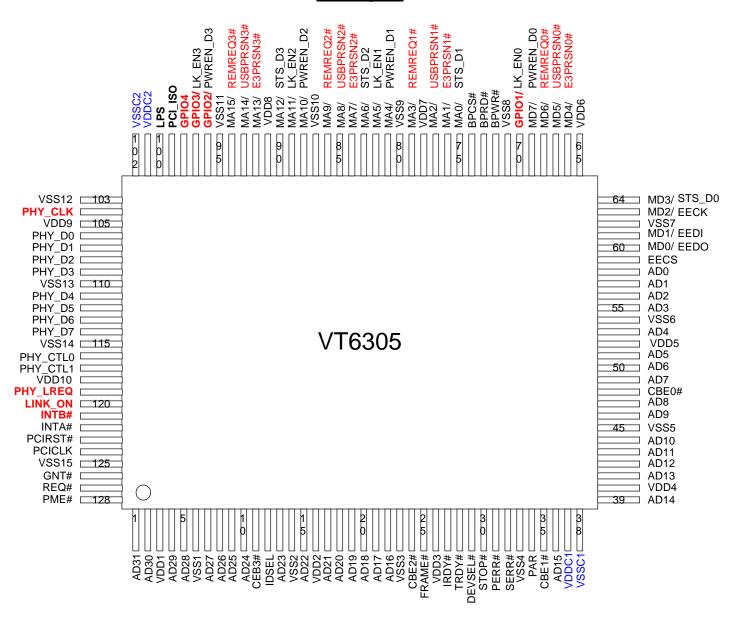

#### Pin Diagram

Figure 2. VT6305 Pin Diagram (Top View)

# Pin List

Figure 3. VT6305 Pin List (Alphabetical Order)

| Pin |    | Pin Name | Pin |        | Pin Name       | Pin |     | Pin Name        | Pin       |    | Pin Name |

|-----|----|----------|-----|--------|----------------|-----|-----|-----------------|-----------|----|----------|

| 58  | IO | AD00     | 48  | IO     | CBE0#          | 75  | O/I | MA00 / DB1SLK   | 104       | I  | PHYCLK   |

| 57  | IO | AD01     | 35  | IO     | CBE1#          | 76  | O/I | MA01 / DB11394# | 116       | IO | PHYCTL0  |

| 56  | IO | AD02     | 24  | IO     | CBE2#          | 77  | O/I | MA02 / DB1USB#  | 117       | IO | PHYCTL1  |

| 55  | IO | AD03     | 11  | IO     | CBE3#          | 79  | O/I | MA03 / DB1RRQ#  | 106       | IO | PHYD0    |

| 53  | IO | AD04     | 29  | IO     | DEVSEL#        | 81  | O/O | MA04 / DB1PEN   | 107       | IO | PHYD1    |

| 51  | IO | AD05     | 59  | О      | EECS#          | 82  | O/O | MA05 / DB1LEN   | 108       | IO | PHYD2    |

| 50  | IO | AD06     | 25  | IO     | FRAME#         | 83  | O/I | MA06 / DB2SLK   | 109       | IO | PHYD3    |

| 49  | IO | AD07     | 6   | P      | GND            | 84  | O/I | MA07 / DB21394# | 111       | IO | PHYD4    |

| 47  | IO | AD08     | 14  | P      | GND            | 85  | O/I | MA08 / DB2USB#  | 112       | IO | PHYD5    |

| 46  | IO | AD09     | 23  | P      | GND            | 86  | O/I | MA09 / DB2RRQ#  | 113       | IO | PHYD6    |

| 44  | IO | AD10     | 33  | P      | GND            | 88  |     | MA10 / DB2PEN   | 114       | IO | PHYD7    |

| 43  | IO | AD11     | 38  | P      | GND            | 89  | O/O | MA11 / DB2LEN   | 120       | I  | PHYLON   |

| 42  | IO | AD12     | 45  | P      | GND            | 90  |     | MA12 / DB3SLK   | 100       | I  | PHYLPS   |

| 41  | IO | AD13     | 54  | P      | GND            | 92  | O/I | MA13 / DB31394# | 119       | 0  | PHYLREQ  |

| 39  | IO | AD14     | 62  | P      | GND            | 93  | O/I | MA14 / DB3USB#  | 128       | O  | PME#     |

| 36  | IO | AD15     | 71  | P      | GND            | 94  | O/I | MA15 / DB3RRQ#  | 127       | O  | PREQ#    |

| 22  | IO | AD16     | 80  | P      | GND            | 74  | О   | MCS#            | 123       | I  | RESET#   |

| 21  | IO | AD17     | 87  | P      | GND            | 60  |     | MD0 / EEDO      | 32        | O  | SERR#    |

| 20  | IO | AD18     | 95  | P      | GND            | 61  |     | MD1 / EEDI      | 30        | IO | STOP#    |

| 19  | IO | AD19     | 102 | P      | GND            | 63  |     | MD2 / EECK      | 28        | IO | TRDY#    |

| 18  | IO | AD20     | 103 | P      | GND            | 64  |     | MD3 / DB0SLK    | 3         | P  | VCC      |

| 17  | IO | AD21     | 110 | P      | GND            | 66  |     | MD4 / DB01394#  | 16        | P  | VCC      |

| 15  | IO | AD22     | 115 | P      | GND            | 67  |     | MD5 / DB0USB#   | 26        | P  | VCC      |

| 13  | IO | AD23     | 125 | P      | GND            | 68  |     | MD6 / DB0RRQ#   | 37        | P  | VCC      |

| 10  | IO | AD24     | 70  |        | GPIO1 / DB0LEN | 69  |     | MD7 / DB0PEN    | 40        | P  | VCC      |

| 9   | IO | AD25     | 96  |        | GPIO2 / DB3PEN | 73  | О   | MRD#            | 52        | P  | VCC      |

| 8   | IO | AD26     | 97  | IO / O | GPIO3 / DB3LEN | 72  | О   | MWR#            | 65        | P  | VCC      |

| 7   | IO | AD27     | 98  | IO     | GPIO4          | 34  | IO  | PAR             | <b>78</b> | P  | VCC      |

| 5   | IO | AD28     | 12  | О      | IDSEL          | 99  | IO  | PCIISO          | 91        | P  | VCC      |

| 4   | IO | AD29     | 122 | О      | INTA#          | 124 | I   | PCLK            | 101       | P  | VCC      |

| 2   | IO | AD30     | 121 | О      | INTB#          | 31  | О   | PERR#           | 105       | P  | VCC      |

| 1   | IO | AD31     | 27  | IO     | IRDY#          | 126 | I   | PGNT#           | 118       | P  | VCC      |

... 0.2 1/4 1 10 2000

# **Pin Descriptions**

Table 1. VT6305 Pin Descriptions

| PCI Bus Interface |                                                                                   |     |                                                                                                                                                                                                                                                                                          |  |  |  |

|-------------------|-----------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Signal Name       | Pin No.                                                                           | I/O | Signal Description                                                                                                                                                                                                                                                                       |  |  |  |

| AD[31:0]          | 1, 2, 4, 5, 7-10,<br>13, 15, 17-22, 36,<br>39, 41-44, 46, 47,<br>49-51, 53, 55-58 | IO  | Address / Data Bus. The standard PCI address and data lines. The address is driven with FRAME# assertion and data is driven or received in following cycles.                                                                                                                             |  |  |  |

| CBE[3:0]#         | 11, 24, 35, 48                                                                    | IO  | <b>Command / Byte Enable.</b> The command is driven with FRAME# assertion. Byte enables corresponding to supplied or requested data are driven on following clocks.                                                                                                                      |  |  |  |

| FRAME#            | 25                                                                                | IO  | <b>Frame.</b> Assertion indicates the address phase of a PCI transfer. Negation indicates that one more data transfer is desired by the cycle initiator.                                                                                                                                 |  |  |  |

| DEVSEL#           | 29                                                                                | Ю   | <b>Device Select.</b> As an output, this signal is asserted to claim PCI transactions hrough positive or subtractive decoding. As an input, DEVSEL# indicates the esponse to a VT6305-initiated transaction and is also sampled when decoding whether to subtractively decode the cycle. |  |  |  |

| TRDY#             | 28                                                                                | IO  | <b>Target Ready.</b> Asserted when the target is ready for data transfer.                                                                                                                                                                                                                |  |  |  |

| IRDY#             | 27                                                                                | IO  | <b>nitiator Ready.</b> Asserted when the initiator is ready for data transfer.                                                                                                                                                                                                           |  |  |  |

| PREQ#             | 127                                                                               | О   | <b>PCI Bus Request.</b> Asserted by the bus master to indicate to the bus arbiter that it wants to use the bus.                                                                                                                                                                          |  |  |  |

| PGNT#             | 126                                                                               | I   | PCI Bus Grant. Asserted to indicate that access to the bus is granted.                                                                                                                                                                                                                   |  |  |  |

| IDSEL             | 12                                                                                | О   | Initialization Device Select. IDSEL is used as a chip select during configuration read and write cycles.                                                                                                                                                                                 |  |  |  |

| INTA#             | 122                                                                               | О   | <b>Interrupt A.</b> An asynchronous signal used to request an interrupt.                                                                                                                                                                                                                 |  |  |  |

| INTB#             | 121                                                                               | О   | <b>Interrupt B.</b> An asynchronous signal used to request an interrupt.                                                                                                                                                                                                                 |  |  |  |

| PCLK              | 124                                                                               | I   | PCI Clock. Timing reference for all transactions on the PCI Bus.                                                                                                                                                                                                                         |  |  |  |

| RESET#            | 123                                                                               | Ι   | <b>Reset.</b> When detected low, an internal hardware reset is performed. PCIRST# assertion or deassertion may be asynchronous to PCLK, however, it is recommended that deassertion be synchronous to guarantee a clean and bounce free edge.                                            |  |  |  |

| PAR               | 34                                                                                | IO  | <b>Parity.</b> A single parity bit is provided over AD[31:0] and C/BE[3:0]#.                                                                                                                                                                                                             |  |  |  |

| PERR#             | 31                                                                                | О   | Parity Error. Parity error is asserted when a data parity error is detected.                                                                                                                                                                                                             |  |  |  |

| SERR#             | 32                                                                                | О   | System Error. SERR# is pulsed active to indicate a system error condition.                                                                                                                                                                                                               |  |  |  |

| STOP#             | 30                                                                                | IO  | <b>Stop.</b> Asserted by the target to request the master to stop the current transaction.                                                                                                                                                                                               |  |  |  |

| 1394 PHY Interface |                                           |     |                    |  |  |  |  |  |

|--------------------|-------------------------------------------|-----|--------------------|--|--|--|--|--|

| Signal Name        | Pin No.                                   | I/O | Signal Description |  |  |  |  |  |

| PHYD[7:0]          | 114, 113, 112, 111,<br>109, 108, 107, 106 | Ю   | PHY Data.          |  |  |  |  |  |

| PHYCTL1            | 117                                       | IO  | PHY Control 1.     |  |  |  |  |  |

| PHYCTL0            | 116                                       | IO  | PHY Control 0.     |  |  |  |  |  |

| PHYCLK             | 104                                       | I   | PHY Clock.         |  |  |  |  |  |

| PHYLREQ            | 119                                       | О   | PHY Link Request.  |  |  |  |  |  |

| PHYLON             | 120                                       | I   | PHY Link On.       |  |  |  |  |  |

| PHYLPS             | 100                                       | I   | PHY Link           |  |  |  |  |  |

| Serial Configuration Memory Interface      |    |       |                                                                                                                                                                  |  |  |  |  |

|--------------------------------------------|----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Signal Name Pin No. I/O Signal Description |    |       |                                                                                                                                                                  |  |  |  |  |

| EECS#                                      | 59 | О     | <b>EEPROM Chip Select.</b> Chip select for external serial EEPROM when used to provide configuration data. A high-value pull-up resistor is provided internally. |  |  |  |  |

| EEDO / MD0                                 | 60 | O / I | EEPROM Data Out.                                                                                                                                                 |  |  |  |  |

| EEDI / MD1                                 | 61 | I/I   | EEPROM Data In.                                                                                                                                                  |  |  |  |  |

| EECK / MD2                                 | 63 | O / I | EEPROM Clock.                                                                                                                                                    |  |  |  |  |

| Local Memory Interface |         |     |                                                                                     |  |  |  |  |

|------------------------|---------|-----|-------------------------------------------------------------------------------------|--|--|--|--|

| Signal Name            | Pin No. | I/O | Signal Description                                                                  |  |  |  |  |

| MD[7:0]                |         | IO  | Memory Data. Pins optionally used for device bay if local memory not used           |  |  |  |  |

| MA[15:0]               |         | О   | <b>Memory Address.</b> Pins optionally used for device bay if local memory not used |  |  |  |  |

| MCS#                   | 74      | О   | Memory Chip Select.                                                                 |  |  |  |  |

| MRD#                   | 73      | О   | Memory Read Enable.                                                                 |  |  |  |  |

| MWR#                   | 72      | О   | Memory Write Enable.                                                                |  |  |  |  |

| Miscellaneous  |         |        |                         |  |  |  |  |  |

|----------------|---------|--------|-------------------------|--|--|--|--|--|

| Signal Name    | Pin No. | I/O    | Signal Description      |  |  |  |  |  |

| PME#           | 128     | О      | Power Management Event. |  |  |  |  |  |

| PCIISO         | 99      | IO     | General Purpose I/O.    |  |  |  |  |  |

| GPIO1 / DB0LEN | 70      | IO / O | General Purpose I/O.    |  |  |  |  |  |

| GPIO2 / DB3PEN | 96      | IO / O | General Purpose I/O.    |  |  |  |  |  |

| GPIO3 / DB3LEN | 97      | IO/O   | General Purpose I/O.    |  |  |  |  |  |

| GPIO4          | 98      | IO     | General Purpose I/O.    |  |  |  |  |  |

|             | Power and Ground |     |                    |  |  |  |  |  |  |

|-------------|------------------|-----|--------------------|--|--|--|--|--|--|

| Signal Name | Pin No.          | I/O | Signal Description |  |  |  |  |  |  |

| VCC | 3, 16, 26, 37, 40,<br>52, 65, 78, 91,<br>101, 105, 118                          | P | Power.  |

|-----|---------------------------------------------------------------------------------|---|---------|

| GND | 6, 14, 23, 33, 38,<br>45, 54, 62, 71, 80,<br>87, 95, 102, 103,<br>110, 115, 125 | Р | Ground. |

D. . . . 0.2 M. 1.10.2000

# **REGISTERS**

#### **Register Overview**

The following tables summarize the configuration and I/O registers of the VT6305. These tables also document the power-on default value ("Default") and access type ("Acc") for each register. Access type definitions used are RW (Read/Write), RO (Read/Only), "—" for reserved / used (essentially the same as RO), and RWC (or just WC) (Read / Write 1's to Clear individual bits). Registers indicated as RW may have some read/only bits that always read back a fixed value (usually 0 if unused); registers designated as RWC or WC may have some read-only or read write bits (see individual register descriptions for details).

Detailed register descriptions are provided in the following section of this document. All offset and default values are shown in hexadecimal unless otherwise indicated

#### Table 2. Registers

#### PCI Function 0 Registers - Controller Configuration

#### **Configuration Space Header Registers**

| Offset | PCI Configuration Space Header      | Default   | Acc                    |

|--------|-------------------------------------|-----------|------------------------|

| 1-0    | Vendor ID                           | 1106      | RO                     |

| 3-2    | Device ID                           | 0130      | RO                     |

| 5-4    | Command                             | 0000      | $\mathbf{RW}$          |

| 7-6    | Status                              | 0280      | WC                     |

| 8      | Revision ID                         | nn        | RO                     |

| 9      | Programming Interface               | 10        | RO                     |

| A      | Sub Class Code                      | 00        | RO                     |

| В      | Base Class Code                     | 0C        | RO                     |

| C      | -reserved- (cache line size)        | 00        |                        |

| D      | Latency Timer                       | 00        | $\mathbf{R}\mathbf{W}$ |

| E      | Header Type                         | 00        | RO                     |

| F      | -reserved- (Built In Self Test)     | 00        | _                      |

| 13-10  | Base Address Register               | 0000 0000 | $\mathbf{R}\mathbf{W}$ |

| 14-27  | -reserved- (base address registers) | 00        |                        |

| 28-2B  | -reserved- (unassigned)             | 00        |                        |

| 2C-2F  | -reserved- (subsystem ID read)      | 00        |                        |

| 30-33  | -reserved- (expan. ROM base addr)   | 00        |                        |

| 34-3B  | -reserved- (unassigned)             | 00        |                        |

| 3C     | Interrupt Line                      | 00        | $\mathbf{R}\mathbf{W}$ |

| 3D     | Interrupt Pin                       | 01        | RO                     |

| 3E     | -reserved- (min gnt)                | 00        |                        |

| 3F     | -reserved- (max lat)                | 00        | _                      |

#### **Controller-Specific Configuration Registers**

| <b>Offset</b> | Heading                | <b>Default</b> | Acc |

|---------------|------------------------|----------------|-----|

| 43-40         | PCI HCI Control        | 0000 0000      | RO  |

| 44            | Miscellaneous Control  | 00             | RW  |

| 45            | -reserved-             | 00             |     |

| 46            | PHY Control 00         |                | RW  |

| 47-F3         | -reserved-             | 00             | _   |

| F4            | Hide Function Register | 00             | RW  |

| F5-F7         | -reserved-             | 00             | _   |

| FB-F8         | Manufacturer ID        | TBD            | RO  |

| FC-FF         | -reserved-             | 00             | _   |

# 1394 Memory-Space Registers

| Offset         | Heading Default                     |           | Acc |

|----------------|-------------------------------------|-----------|-----|

| 0              |                                     |           | RO  |

| 4              | -reserved- (GUID ROM) 0000 0000     |           | _   |

| 8              | ` '                                 |           | RW  |

| С              | CSR Data                            | 0000 0000 | RW  |

| 10             | CSR Compare Data                    | 0000 0000 | RW  |

| 14             | CSR Control                         | 8000 0000 | RW  |

| 18             | Configuration ROM Header            | 0000 0000 | RW  |

| 1C             | 1394 Bus ID                         | 3133 3934 | RO  |

| 20             | 1394 Bus Options                    | F000 0002 | RW  |

| 24             | Global Unique ID High               | 0000 0000 | RW  |

| 28             | Global Unique ID Low                | 0000 0000 | RW  |

| 2C-33          | -reserved-                          | 00        |     |

| 34             | Configuration ROM Map               | 0000 0000 | RW  |

| 38             | Posted Write Address Low            | 0000 0000 |     |

| 3C             | Posted Write Address High           | 0000 0000 | RO  |

| 40             | Vendor ID                           | 0000 0000 | RO  |

| 44-4F          | -reserved-                          | 00        | _   |

| 50             | HC Control Set                      | 0000 0000 | RW  |

| 54             | HC Control Clear                    | 0000 0000 | RW  |

| 58-5F          | -reserved-                          | 00        | _   |

| 60-63          | -reserved-                          | 00        |     |

| 64             | Self-ID Buffer Pointer              | 0000 0000 | RW  |

| 68             | Self-ID Count                       | 0000 0000 | RO  |

| 6C-6F          | -reserved-                          | 00        | _   |

| 70             | Isoch Rcv Channel Mask High Set     | 0000 0000 | RW  |

| 74             | Isoch Rcv Channel Mask High Clr     | 0000 0000 | RW  |

| 78             | Isoch Rcv Channel Mask Low Set      | 0000 0000 | RW  |

| 7C             | Isoch Rcv Channel Mask Low Clr      | 0000 0000 | RW  |

| 80             | Interrupt Event Set                 |           | RW  |

| 84             | Interrupt Event Clear               | 0000 0000 | RW  |

| 88             | Interrupt Mask Set                  |           | RW  |

| 8C             | Interrupt Mask Clear                | 0000 0000 |     |

| 90             | Isoch Xmit Interrupt Event Set      | 0000 0000 |     |

| 94             | Isoch Xmit Interrupt Event Clear    | 0000 0000 | RW  |

| 98             | Isoch Xmit Interrupt Mask Set       | 0000 0000 |     |

| 9C             | Isoch Xmit Interrupt Mask Clear     | 0000 0000 |     |

| A0             | Isoch Rcv Interrupt Event Set       | 0000 0000 |     |

| A4             | Isoch Rcv Interrupt Event Clear     | 0000 0000 |     |

| A8             | Isoch Rcv Interrupt Mask Set        | 0000 0000 | RW  |

| AC             | Isoch Rcv Interrupt Mask Clear      | 0000 0000 | RW  |

| B0-DB          | -reserved-                          | 00        | _   |

| DC             | Fairness Control                    | 0000 0000 | RW  |

| E0             | Link Control Set                    | 0000 0000 |     |

| E4             |                                     | 0000 0000 |     |

|                |                                     |           |     |

| E8             | Node ID 0000 0000                   |           |     |

| E8<br>EC       |                                     |           |     |

| E8<br>EC<br>F0 | PHY Control Isochronous Cycle Timer | 0000 0000 |     |

| 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100     | Async Request Filter High Set          | 0000 0000                | RW |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------|--------------------------|----|

| 10C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 104     | Async Request Filter High Clear        | 0000 0000                | RW |

| 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 108     | Async Request Filter Low Set           | 0000 0000                | RW |

| 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10C     | Async Request Filter Low Clear         | 0000 0000                | RW |

| 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 110     | Physical Request Filter High Set       | 0000 0000                | RW |

| 11C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 114     | Physical Request Filter High Clear     | 0000 0000                | RW |

| 120-17F         -reserved-         00         —           180         Async Request Xmit Context Set         0000 0000 RW         RW           184         Async Request Xmit Context Clr         0000 0000 RW           18C         Async Response Xmit Context Set         0000 0000 RW           1A0         Async Response Xmit Context Set         0000 0000 RW           1A4         Async Response Xmit Context Clr         0000 0000 RW           1AC         Async Response Xmit Context Set         0000 0000 RW           1C0         Async Request Rcv Context Set         0000 0000 RW           1C1         Async Request Rcv Context Set         0000 0000 RW           1E0         Async Response Rcv Context Set         0000 0000 RW           1E1         Async Response Rcv Context Clr         0000 0000 RW           1E2         Async Response Rcv Context Clr         0000 0000 RW           1E2         Async Response Rcv Command         0000 0000 RW           1E2         Async Response Rcv Context Olr         0000 0000 RW           1E2         Async Response Rcv Context Olr         0000 0000 RW           200         Isoch Xmit Context Olr         0000 0000 RW           201         Isoch Xmit Context Olr         0000 0000 RW           210         I                                                                                                      | 118     | Physical Request Filter Low Set        | 0000 0000                | RW |

| 180         Async Request Xmit Context Set         0000 0000 RW           184         Async Request Xmit Context Clr         0000 0000 RW           18C         Async Request Xmit Context Clr         0000 0000 RW           1A0         Async Response Xmit Context Set         0000 0000 RW           1A4         Async Response Xmit Context Clr         0000 0000 RW           1AC         Async Response Xmit Cmd Ptr         0000 0000 RW           1C0         Async Request Rcv Context Set         0000 0000 RW           1C1         Async Request Rcv Context Clr         0000 0000 RW           1C2         Async Request Rcv Command Ptr         0000 0000 RW           1E0         Async Response Rcv Context Set         0000 0000 RW           1E1         Async Response Rcv Context Clr         0000 0000 RW           1E2         Async Response Rcv Command         0000 0000 RW           1E2         Async Response Rcv Command         0000 0000 RW           1E4         Async Response Rcv Command         0000 0000 RW           1E5         Async Response Rcv Command         0000 0000 RW           200         Isoch Xmit Context 0 Set         0000 0000 RW           201         Isoch Xmit Context 1 Set         0000 0000 RW           210         Isoch Xmit Context 1 Clr <td>11C</td> <td>Physical Request Filter Low Clear</td> <td>0000 0000</td> <td>RW</td> | 11C     | Physical Request Filter Low Clear      | 0000 0000                | RW |

| 184         Async Request Xmit Context Clr         0000 0000 RW           18C         Async Request Xmit Command Ptr         0000 0000 RW           1A0         Async Response Xmit Context Set         0000 0000 RW           1A4         Async Response Xmit Context Clr         0000 0000 RW           1AC         Async Request Rcv Context Set         0000 0000 RW           1C0         Async Request Rcv Context Set         0000 0000 RW           1C2         Async Request Rcv Context Clr         0000 0000 RW           1C0         Async Response Rcv Context Set         0000 0000 RW           1C1         Async Response Rcv Context Clr         0000 0000 RW           1E0         Async Response Rcv Context Set         0000 0000 RW           1E1         Async Response Rcv Context Clr         0000 0000 RW           1E2         Async Response Rcv Command         0000 0000 RW           1E1         Async Response Rcv Command         0000 0000 RW           1E2         Async Response Rcv Command         0000 0000 RW           1E2         Async Response Rcv Command         0000 0000 RW           1E2         Async Response Rcv Command         0000 0000 RW           200         Isoch Xmit Context 0 Set         0000 0000 RW           201         Isoch Xmit Context 1 Cl                                                                                    | 120-17F | -reserved-                             | 00                       | _  |

| 18C         Async Response Xmit Command Ptr         0000 0000 RW           1A0         Async Response Xmit Context Set         0000 0000 RW           1A4         Async Response Xmit Context Clr         0000 0000 RW           1AC         Async Response Xmit Cmd Ptr         0000 0000 RW           1C0         Async Request Rcv Context Set         0000 0000 RW           1C4         Async Request Rcv Context Clr         0000 0000 RW           1C0         Async Response Rcv Context Clr         0000 0000 RW           1C1         Async Response Rcv Context Set         0000 0000 RW           1E0         Async Response Rcv Context Set         0000 0000 RW           1E1         Async Response Rcv Context Clr         0000 0000 RW           1EC         Async Response Rcv Context Clr         0000 0000 RW           1EC         Async Response Rcv Command Ptr         0000 0000 RW           200         Isoch Xmit Context 0 Set         0000 0000 RW           201         Isoch Xmit Context 1 Set         0000 0000 RW           202         Isoch Xmit Context 1 Set         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           210         Isoch Xmit Context 1 Clr <td>180</td> <td>Async Request Xmit Context Set</td> <td>0000 0000</td> <td>RW</td>    | 180     | Async Request Xmit Context Set         | 0000 0000                | RW |

| 1A0         Async Response Xmit Context Set         0000 0000 RW           1A4         Async Response Xmit Context Clr         0000 0000 RW           1AC         Async Response Xmit Cmd Ptr         0000 0000 RW           1C0         Async Request Rcv Context Set         0000 0000 RW           1C4         Async Request Rcv Context Clr         0000 0000 RW           1C0         Async Request Rcv Command Ptr         0000 0000 RW           1C1         Async Response Rcv Command Ptr         0000 0000 RW           1E0         Async Response Rcv Context Set         0000 0000 RW           1E1         Async Response Rcv Context Clr         0000 0000 RW           1E2         Async Response Rcv Command Ptr         0000 0000 RW           1E1         Async Response Rcv Command Ptr         0000 0000 RW           1E2         Async Response Rcv Command Ptr         0000 0000 RW           200         Isoch Xmit Context 0 Set         0000 0000 RW           201         Isoch Xmit Context 1 Set         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           211         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Set         0000 0000 RW           221         Isoch Xmit Context 1 Clr                                                                                          | 184     | Async Request Xmit Context Clr         | 0000 0000                | RW |

| 1A4         Async Response Xmit Context Clr         0000 0000 RW           1AC         Async Response Xmit Cmd Ptr         0000 0000 RW           1C0         Async Request Rcv Context Set         0000 0000 RW           1C4         Async Request Rcv Context Clr         0000 0000 RW           1CC         Async Response Rcv Context Clr         0000 0000 RW           1E0         Async Response Rcv Context Set         0000 0000 RW           1E4         Async Response Rcv Context Clr         0000 0000 RW           1EC         Async Response Rcv Command Ptr         0000 0000 RW           200         Isoch Xmit Context 0 Set         0000 0000 RW           204         Isoch Xmit Context 0 Clr         0000 0000 RW           200         Isoch Xmit Context 1 Set         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           211         Isoch Xmit Context 1 Clr         0000 0000 RW           212         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW                                                                                             | 18C     | Async Request Xmit Command Ptr         | 0000 0000                | RW |

| 1AC         Async Response Xmit Cmd Ptr         0000 0000 RW           1C0         Async Request Rcv Context Set         0000 0000 RW           1C2         Async Request Rcv Context Clr         0000 0000 RW           1C2         Async Response Rcv Context Clr         0000 0000 RW           1E0         Async Response Rcv Context Set         0000 0000 RW           1E4         Async Response Rcv Context Clr         0000 0000 RW           1EC         Async Response Rcv Command Ptr         0000 0000 RW           200         Isoch Xmit Context 0 Set         0000 0000 RW           204         Isoch Xmit Context 0 Clr         0000 0000 RW           200         Isoch Xmit Context 1 Set         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           211         Isoch Xmit Context 1 Clr         0000 0000 RW           212         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Clr         0000 0000 RW           221         Isoch Xmit Context 1 Clr         0000 0000 RW           222         Isoch Xmit Context 2 Clr         0000 0000 RW           230         Isoch Xmit Context 2 Clr         0000 0000 RW           231         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW <td>1A0</td> <td>Async Response Xmit Context Set</td> <td>0000 0000</td> <td>RW</td>           | 1A0     | Async Response Xmit Context Set        | 0000 0000                | RW |

| 1C0         Async Request Rcv Context Set         0000 0000 RW           1C2         Async Request Rcv Context Clr         0000 0000 RW           1E0         Async Response Rcv Context Set         0000 0000 RW           1E4         Async Response Rcv Context Clr         0000 0000 RW           1EC         Async Response Rcv Context Clr         0000 0000 RW           1EC         Async Response Rcv Command Ptr         0000 0000 RW           204         Isoch Xmit Context 0 Set         0000 0000 RW           204         Isoch Xmit Context 0 Cmd Ptr         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           211         Isoch Xmit Context 1 Clr         0000 0000 RW           212         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Clr         0000 0000 RW           224         Isoch Xmit Context 1 Clr         0000 0000 RW           225         Isoch Xmit Context 2 Set         0000 0000 RW           230         Isoch Xmit Context 2 Clr         0000 0000 RW           231         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           232         Isoch Xmit Context 0 Set         0000 0000 RW </td <td>1A4</td> <td>Async Response Xmit Context Clr</td> <td>0000 0000</td> <td>RW</td>     | 1A4     | Async Response Xmit Context Clr        | 0000 0000                | RW |

| 1C4         Async Request Rcv Context Clr         0000 0000 RW           1CC         Async Request Rcv Command Ptr         0000 0000 RW           1E0         Async Response Rcv Context Set         0000 0000 RW           1E4         Async Response Rcv Context Clr         0000 0000 RW           1EC         Async Response Rcv Command Ptr         0000 0000 RW           200         Isoch Xmit Context 0 Set         0000 0000 RW           204         Isoch Xmit Context 0 Clr         0000 0000 RW           200         Isoch Xmit Context 1 Set         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           211         Isoch Xmit Context 1 Set         0000 0000 RW           212         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 2 Clr         0000 0000 RW           230         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW </td <td>1AC</td> <td>Async Response Xmit Cmd Ptr</td> <td>0000 0000</td> <td>RW</td>                   | 1AC     | Async Response Xmit Cmd Ptr            | 0000 0000                | RW |

| 1CC         Async Response Rcv Context Set         0000 0000 RW           1E0         Async Response Rcv Context Set         0000 0000 RW           1E4         Async Response Rcv Context Clr         0000 0000 RW           1EC         Async Response Rcv Command Ptr         0000 0000 RW           200         Isoch Xmit Context 0 Set         0000 0000 RW           204         Isoch Xmit Context 0 Clr         0000 0000 RW           205         Isoch Xmit Context 1 Set         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           214         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           210         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Clr         0000 0000 RW           221         Isoch Xmit Context 2 Clr         0000 0000 RW           230         Isoch Xmit Context 2 Clr         0000 0000 RW           231         Isoch Xmit Context 2 Clr         0000 0000 RW           232         Isoch Rcv Context 0 Set         0000 0000 RW <td>1C0</td> <td>Async Request Rcv Context Set</td> <td>0000 0000</td> <td>RW</td>                       | 1C0     | Async Request Rcv Context Set          | 0000 0000                | RW |

| 1E0         Async Response Rcv Context Set         0000 0000 RW           1E4         Async Response Rcv Context Clr         0000 0000 RW           1EC         Async Response Rcv Command Ptr         0000 0000 RW           200         Isoch Xmit Context 0 Set         0000 0000 RW           204         Isoch Xmit Context 0 Clr         0000 0000 RW           200         Isoch Xmit Context 0 Cmd Ptr         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           214         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           210         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           211         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Set         0000 0000 RW           220         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 2 Clr         0000 0000 RW           230         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Clr         0000 0000 RW           231         Isoch Rcv Context 2 Cmd Ptr         0000 0000 RW           232         Isoch Rcv Context 0 Set         0000 0000 RW                                                                                                     | 1C4     | •                                      | 0000 0000                | RW |

| 1E4         Async Response Rcv Context Clr         0000 0000 RW           1EC         Async Response Rcv Command Ptr         0000 0000 RW           200         Isoch Xmit Context 0 Set         0000 0000 RW           204         Isoch Xmit Context 0 Clr         0000 0000 RW           20C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           214         Isoch Xmit Context 1 Clr         0000 0000 RW           210         Isoch Xmit Context 1 Clr         0000 0000 RW           211         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Set         0000 0000 RW           220         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Clr         0000 0000 RW           230         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Clr         0000 0000 RW           231         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           232         Isoch Rcv Context 0 Set         0000 0000 RW           230         Isoch Rcv Context 0 Set         0000 0000 RW           240         Isoch Rcv Context 0 Set         0000 0000 RW <tr< td=""><td>1CC</td><td>Async Request Rcv Command Ptr</td><td>0000 0000</td><td>RW</td></tr<>                   | 1CC     | Async Request Rcv Command Ptr          | 0000 0000                | RW |

| 1E4         Async Response Rcv Context Clr         0000 0000         RW           1EC         Async Response Rcv Command Ptr         0000 0000         RW           200         Isoch Xmit Context 0 Set         0000 0000         RW           204         Isoch Xmit Context 0 Clr         0000 0000         RW           20C         Isoch Xmit Context 0 Cmd Ptr         0000 0000         RW           210         Isoch Xmit Context 1 Set         0000 0000         RW           214         Isoch Xmit Context 1 Clr         0000 0000         RW           210         Isoch Xmit Context 1 Cmd Ptr         0000 0000         RW           210         Isoch Xmit Context 1 Cmd Ptr         0000 0000         RW           210         Isoch Xmit Context 1 Set         0000 0000         RW           210         Isoch Xmit Context 1 Clr         0000 0000         RW           220         Isoch Xmit Context 1 Clr         0000 0000         RW           221         Isoch Xmit Context 2 Set         0000 0000         RW           230         Isoch Xmit Context 2 Set         0000 0000         RW           231         Isoch Xmit Context 2 Cmd Ptr         0000 0000         RW           232         Isoch Rcv Context 0 Set <t< td=""><td>1E0</td><td>Async Response Rcv Context Set</td><td>0000 0000</td><td>RW</td></t<>                                                   | 1E0     | Async Response Rcv Context Set         | 0000 0000                | RW |

| Dec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1E4     | •                                      | 0000 0000                | RW |

| 200         Isoch Xmit Context 0 Set         0000 0000 RW           204         Isoch Xmit Context 0 Clr         0000 0000 RW           20C         Isoch Xmit Context 0 Cmd Ptr         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           214         Isoch Xmit Context 1 Clr         0000 0000 RW           21C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           220         Isoch Xmit Context 1 Set         0000 0000 RW           224         Isoch Xmit Context 1 Clr         0000 0000 RW           230         Isoch Xmit Context 2 Set         0000 0000 RW           231         Isoch Xmit Context 2 Clr         0000 0000 RW           232         Isoch Xmit Context 2 Clr         0000 0000 RW           234         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           231         Isoch Rcv Context 0 Set         0000 0000 RW           230         Isoch Rcv Context 0 Set         0000 0000 RW           240         Isoch Rcv Context 0 Set         0000 0000 RW           250-3FF -reserved-         00         0000 0000 RW           400         Isoch Rcv Context 0 Set         0000 0000 RW           40                                                                                                                       | 1EC     | Async Response Rcv Command             | 0000 0000                | RW |

| 204         Isoch Xmit Context 0 Clr         0000 0000 RW           20C         Isoch Xmit Context 0 Cmd Ptr         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           214         Isoch Xmit Context 1 Clr         0000 0000 RW           21C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           220         Isoch Xmit Context 1 Set         0000 0000 RW           224         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Set         0000 0000 RW           231         Isoch Xmit Context 2 Clr         0000 0000 RW           232         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           230         Isoch Rcv Context 2 Cmd Ptr         0000 0000 RW           230         Isoch Rcv Context 0 Set         0000 0000 RW           240         Isoch Rcv Context 0 Set         0000 0000 RW           400         Isoch Rcv Context 0 Clr         0000 0000 RW           400         Isoch Rcv Context 0 Clr         0000 0000 RW           410         Isoch Rcv Context 1 Set         0000 0000 RW           420         Isoch Rcv Context 1 Clr         0000 0000 RW                                                                                                                            |         | Ptr                                    |                          |    |

| 20C         Isoch Xmit Context 0 Cmd Ptr         0000 0000 RW           210         Isoch Xmit Context 1 Set         0000 0000 RW           214         Isoch Xmit Context 1 Clr         0000 0000 RW           21C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           220         Isoch Xmit Context 1 Set         0000 0000 RW           224         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Set         0000 0000 RW           231         Isoch Xmit Context 2 Clr         0000 0000 RW           232         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           230         Isoch Rcv Context 2 Cmd Ptr         0000 0000 RW           231         Isoch Rcv Context 0 Set         0000 0000 RW           232         Isoch Rcv Context 0 Set         0000 0000 RW           2404         Isoch Rcv Context 0 Set         0000 0000 RW           405         Isoch Rcv Context 0 Clr         0000 0000 RW           406         Isoch Rcv Context 1 Set         0000 0000 RW           420         Isoch Rcv Context 1 Set         0000 0000 RW           420         Isoch Rcv Context 1 Clr         0000 0000 RW                                                                                                                            | 200     | Isoch Xmit Context 0 Set               | 0000 0000                | RW |

| 210         Isoch Xmit Context 1 Set         0000 0000 RW           214         Isoch Xmit Context 1 Clr         0000 0000 RW           21C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           220         Isoch Xmit Context 1 Set         0000 0000 RW           224         Isoch Xmit Context 1 Clr         0000 0000 RW           220         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Set         0000 0000 RW           234         Isoch Xmit Context 2 Clr         0000 0000 RW           23C         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           250-3FF -reserved-         00         —           400         Isoch Rcv Context 0 Set         0000 0000 RW           404         Isoch Rcv Context 0 Clr         0000 0000 RW           40C         Isoch Rcv Context 0 Command Ptr         0000 0000 RW           410         Isoch Rcv Context 1 Set         0000 0000 RW           420         Isoch Rcv Context 1 Set         0000 0000 RW           421         Isoch Rcv Context 1 Clr         0000 0000 RW           422         Isoch Rcv Context 1 Clr         0000 0000 RW           423         Isoch Rcv Context 1 Clr         0000 0000 RW                                                                                                                                               | 204     | Isoch Xmit Context 0 Clr               | 0000 0000                | RW |

| 214         Isoch Xmit Context 1 Clr         0000 0000 RW           21C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           220         Isoch Xmit Context 1 Set         0000 0000 RW           224         Isoch Xmit Context 1 Clr         0000 0000 RW           22C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Set         0000 0000 RW           234         Isoch Xmit Context 2 Clr         0000 0000 RW           23C         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           250-3FF -reserved-         00         —           400         Isoch Rcv Context 0 Set         0000 0000 RW           404         Isoch Rcv Context 0 Clr         0000 0000 RW           40C         Isoch Rcv Context 0 Command Ptr         0000 0000 RW           410         Isoch Rcv Context 1 Set         0000 0000 RW           420         Isoch Rcv Context 1 Set         0000 0000 RW           424         Isoch Rcv Context 1 Clr         0000 0000 RW           426         Isoch Rcv Context 1 Clr         0000 0000 RW           427         Isoch Rcv Context 1 Clr         0000 0000 RW           428         Isoch Rcv Context 1 Clr         0000 0000 RW                                                                                                                                                | 20C     | Isoch Xmit Context 0 Cmd Ptr           | 0000 0000                | RW |

| 21C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           220         Isoch Xmit Context 1 Set         0000 0000 RW           224         Isoch Xmit Context 1 Clr         0000 0000 RW           22C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Set         0000 0000 RW           234         Isoch Xmit Context 2 Clr         0000 0000 RW           23C         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           250-3FF -reserved-         00            400         Isoch Rcv Context 0 Set         0000 0000 RW           404         Isoch Rcv Context 0 Clr         0000 0000 RW           40C         Isoch Rcv Context 0 Command Ptr         0000 0000 RW           410         Isoch Rcv Context 1 Set         0000 0000 RW           420         Isoch Rcv Context 1 Set         0000 0000 RW           421         Isoch Rcv Context 1 Clr         0000 0000 RW           422         Isoch Rcv Context 1 Clr         0000 0000 RW           423         Isoch Rcv Context 1 Clr         0000 0000 RW           420         Isoch Rcv Context 1 Clr         0000 0000 RW                                                                                                                                                                                                                             | 210     | Isoch Xmit Context 1 Set               | 0000 0000                | RW |

| 220         Isoch Xmit Context 1 Set         0000 0000 RW           224         Isoch Xmit Context 1 Clr         0000 0000 RW           22C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Set         0000 0000 RW           234         Isoch Xmit Context 2 Clr         0000 0000 RW           23C         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           250-3FF -reserved-         00         —           400         Isoch Rcv Context 0 Set         0000 0000 RW           404         Isoch Rcv Context 0 Clr         0000 0000 RW           40C         Isoch Rcv Context 0 Command Ptr         0000 0000 RW           410         Isoch Rcv Context 1 Set         0000 0000 RW           420         Isoch Rcv Context 1 Set         0000 0000 RW           421         Isoch Rcv Context 1 Clr         0000 0000 RW           422         Isoch Rcv Context 1 Clr         0000 0000 RW           423         Isoch Rcv Context 1 Command Ptr         0000 0000 RW           430         Isoch Rcv Context 1 Match         0000 0000 RW                                                                                                                                                                                                                                                                                  | 214     | Isoch Xmit Context 1 Clr 0000 0000     |                          | RW |

| 224         Isoch Xmit Context 1 Clr         0000 0000 RW           22C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Set         0000 0000 RW           234         Isoch Xmit Context 2 Clr         0000 0000 RW           23C         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           250-3FF -reserved-         00         —           400         Isoch Rcv Context 0 Set         0000 0000 RW           404         Isoch Rcv Context 0 Clr         0000 0000 RW           40C         Isoch Rcv Context 0 Command Ptr         0000 0000 RW           410         Isoch Rcv Context 1 Set         0000 0000 RW           420         Isoch Rcv Context 1 Set         0000 0000 RW           424         Isoch Rcv Context 1 Clr         0000 0000 RW           42C         Isoch Rcv Context 1 Clr         0000 0000 RW           430         Isoch Rcv Context 1 Match         0000 0000 RW                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21C     | Isoch Xmit Context 1 Cmd Ptr 0000 0000 |                          | RW |

| 22C         Isoch Xmit Context 1 Cmd Ptr         0000 0000 RW           230         Isoch Xmit Context 2 Set         0000 0000 RW           234         Isoch Xmit Context 2 Clr         0000 0000 RW           23C         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           250-3FF -reserved-         00         —           400         Isoch Rcv Context 0 Set         0000 0000 RW           404         Isoch Rcv Context 0 Clr         0000 0000 RW           40C         Isoch Rcv Context 0 Command Ptr         0000 0000 RW           410         Isoch Rcv Context 0 Match         0000 0000 RW           420         Isoch Rcv Context 1 Set         0000 0000 RW           424         Isoch Rcv Context 1 Clr         0000 0000 RW           42C         Isoch Rcv Context 1 Command Ptr         0000 0000 RW           430         Isoch Rcv Context 1 Match         0000 0000 RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 220     |                                        |                          | RW |

| 230         Isoch Xmit Context 2 Set         0000 0000 RW           234         Isoch Xmit Context 2 Clr         0000 0000 RW           23C         Isoch Xmit Context 2 Cmd Ptr         0000 0000 RW           250-3FF -reserved-         00         —           400         Isoch Rcv Context 0 Set         0000 0000 RW           404         Isoch Rcv Context 0 Clr         0000 0000 RW           40C         Isoch Rcv Context 0 Command Ptr         0000 0000 RW           410         Isoch Rcv Context 0 Match         0000 0000 RW           420         Isoch Rcv Context 1 Set         0000 0000 RW           424         Isoch Rcv Context 1 Clr         0000 0000 RW           42C         Isoch Rcv Context 1 Command Ptr         0000 0000 RW           430         Isoch Rcv Context 1 Match         0000 0000 RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 224     | Isoch Xmit Context 1 Clr 0000 0000     |                          | RW |