# VT6516

# 16/12-PORT 10/100BASE-T/TX ETHERNET SWITCH CONTROLLER

**REVISION 'E' DATASHEET** (Preliminary)

**ISSUE 1: July 31, 1999**

VIA Technologies, Inc.

#### PRELIMINARY RELEASE

Please contact VIA Technologies for the latest documentation.

# **Copyright Notice:**

Copyright © 1995, VIA Technologies Incorporated. Printed in Taiwan. ALL RIGHTS RESERVED.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of VIA Technologies Incorporated.

The VT86C100P may only be used to identify products of VIA Technologies. All trademarks are the properties of their respective owners.

# **Disclaimer Notice:**

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. The information provided by this document is believed to be accurate and reliable to the publication date of this document. However, VIA Technologies assumes no responsibility for any errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

# **Offices:**

1045 Mission Court 8<sup>th</sup> Floor, No. 533 Fremont, CA 94539 Chung-Cheng Rd., Hsin-Tien

USA Taipei, Taiwan ROC

Tel: (510) 683-3300 Tel: (886-2) 2218-5452 Fax: (510) 683-3301 Fax: (886-2) 2218-5453

# **Online Services:**

BBS: 886-2-2186408 FTP: <u>FTP.VIA.COM.TW</u>

HTTP: WWW.VIA.COM.TW -or- WWW.VIATECH.COM

# TABLE OF CONTENTS

| TABLE OF CONTENTS                                                |       |       |       |       |       |       | 3    |

|------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|------|

| FIGURES AND TABLES                                               |       |       |       |       |       |       | 4    |

| REVERSION HISTORY                                                |       |       |       |       |       |       | 5    |

| FEATURES                                                         |       |       |       |       |       |       | 6    |

| BLOCK DIAGRAM                                                    |       |       |       |       |       |       | 9    |

| BALL OUT DIAGRAM                                                 |       |       |       |       |       |       | . 11 |

| RMII-mode Ball out Diagram                                       |       |       |       |       |       |       | . 11 |

| MII-mode Ballout Diagram                                         |       |       |       |       |       |       |      |

| LOGIC SYMBOL                                                     |       |       |       |       |       |       |      |

| PIN DESCRIPTIONS                                                 |       |       |       |       |       |       |      |

| JUMPER STRAPPING.                                                |       |       |       |       |       |       |      |

| SECTION I FUNCTIONAL DESCRIPTIONS                                |       |       |       |       |       |       |      |

|                                                                  |       |       |       |       |       |       |      |

| 1. GENERAL DESCRIPTION                                           |       |       |       |       |       |       |      |

| 2. THE VIA ETHER SWITCH ARCHITECTURE                             |       |       |       |       |       |       |      |

| 2.1 Switch initialization procedures                             |       |       |       |       |       |       |      |

| 2.2 Packet receiving and forwarding follow                       |       |       |       |       |       |       |      |

| 3. Interface Descriptions                                        |       |       |       |       |       |       |      |

| 3.1 Buffer Memory (SDRAM) Interface and Table (SRAM) interface 2 |       |       |       |       |       |       |      |

| 4. FUNCTIONAL DESCRIPTION                                        |       |       |       |       |       |       |      |

| 4.1 Packet Reception and Address recognition                     |       |       |       |       |       |       |      |

| 4.2 Packet Forwarding and VLAN                                   |       |       |       |       |       |       | . 33 |

| 4.3 Network Management Features                                  |       |       |       |       |       |       | . 34 |

| SECTION II REGISTER MAP                                          | ••••• | ••••• | ••••• | ••••• | ••••• | ••••• | . 36 |

| 1. Register Tables                                               |       |       |       |       |       |       | . 36 |

| 2 CPU Interface Registers Map.                                   |       |       |       |       |       |       |      |

| 3 SWITCH INTERNAL REGISTERS MAP                                  |       |       |       |       |       |       |      |

| 4. DETAIL OF SWITCH REGISTER.                                    |       |       |       |       |       |       |      |

| 4.1 Registers of SDRAM Control Module                            |       |       |       |       |       |       |      |

| 4.2 Registers of SRAM Control Module                             |       |       |       |       |       |       |      |

| 4.4 Registers of Buffer Control Module                           |       |       |       |       |       |       |      |

| 4.5 Registers of Forwarding Control Module                       |       |       |       |       |       |       |      |

| 4.6 Registers of PHY Control Module                              |       |       |       |       |       |       |      |

| 4.7 Registers of EEPROM Control Module                           |       |       |       |       |       |       |      |

| 4.8 Registers of CPU Interface Module                            |       |       |       |       |       |       |      |

| 4.9 Registers of MAC/IO Control Module                           |       |       |       |       |       |       |      |

| 4.10 Registers of CPU IO Control Module                          |       |       |       |       |       |       |      |

| SECTION III ELECTRICAL SPECIFICATIONS                            |       |       |       |       |       |       |      |

| ABSOLUTE MAXIMUM RATINGS                                         |       |       |       |       |       |       |      |

| DC CHARACTERISTICS                                               |       |       |       |       |       |       |      |

| AC CHARACTERISTICS                                               |       |       |       |       |       |       |      |

| PACKAGE MECHANICAL SPECIFICATIONS                                |       |       |       |       |       |       |      |

| I ACKAGE MIECHANICAL DECIFICATIONS                               |       |       |       |       |       |       | . 13 |

# FIGURES AND TABLES

| Figure 1: Block Diagram                                    |    |

|------------------------------------------------------------|----|

| Figure 3-3                                                 | 22 |

| Figure 3-6: Algorithm of Initialization of Free Link Lists | 22 |

| Figure 3-1 SRAM                                            | 26 |

| Figure 3-2 Free buffer link structure                      | 27 |

| Table 1-0 Free buffer link structure                       | 27 |

| Figure 3-5 The Address table entries structure +           | 27 |

| Table 1-1 Address table structure                          | 28 |

| Table 3-1 RMII interface signals                           | 30 |

| Figure 3-1 RMII timing diagram                             | 30 |

| Table 3-2 MII interface signals                            | 31 |

| Figure 3-2 MII timing diagram                              | 31 |

|                                                            |    |

# **REVERSION HISTORY**

| Reversion | Date      | Reason for change                                               | By           |

|-----------|-----------|-----------------------------------------------------------------|--------------|

| V0.90     | 2/18/1999 | First release version                                           | JeffreyChang |

| V0.91     | 6/2/1999  | Add D version silicon features modification                     | JeffreyChang |

| V0.92     | 8/23/1999 | Add E version silicon features modification                     | MurphyChen   |

| V0.93     | 9/9/1999  | Revision according to Weipin's,<br>Kevin's, and Ruth's comments | MurphyChen   |

#### **FEATURES**

- Single chip 16/12 ports 10/100M Ethernet switch controller

- Highly integrated single chip shared memory switch engine

- With option for 16 RMII (Reduced Media Independent Interface) ports or 12 MII (Media Independent Interface) ports

- Non-blocking layer 2 switch, 148,810 packets/sec on each 100Mbps Ethernet port

- Media Access Control (MAC)

- Dual 192-bytes FIFO's of receive and transmit for each port

- CRC generator for outgoing packets from CPU port

- IEEE 802.3X compliant flow control for full duplex ports

- Backpressure for half duplex ports

- Two switching mechanisms

- Supports 'store and forward' switching without forwarding CRC-bad packets

- Supports 'cut through' switching subject to long packets of length over 290 bytes for 100Mbps ports or of length over 98 bytes for 10Mbps ports

- Packet buffering

- Glueless 64-bit interface to SDRAM as a packet buffer pool with size from 2M bytes (SGRAM) to 512 M bytes

- 1536 bytes for each packet buffer

- External 32 bits SSRAM interface for forwarding table and memory link table

- Link list structure initialized by software

- 2K up to 32K unicast/multicast addresses table entries with VLAN information

- Supports static entries for upper-layer multicast protocols, e.g. IGMP

- Advanced address recognition

- Layer 2 MAC address recognition engine to enable wire-speed forwarding rate

- Self learning mechanism

- Supports multiple MAC address per-port from 2K up to 32K unicast/multicast addresses

- Switch management support

- Supports port mirroring (Sniffer feature)

- Supports spanning tree algorithm

- Supports CPU direct access to SDRAM and SSRAM

- Supports five statistical counters in each port

- Supports I<sup>2</sup>C EEPROM interface for customized configuration

- Support port-grouping VLAN

- Configurable server ports belonging to multiple VLAN groups

- Support port-based trunking

- Three types of trunk grouping: one trunk group with 2 or 4 ports, two trunk groups each with 2 ports

- Load balance according to MAC address and port number

- CPU interface VIA 8/16 bits ISA-like interface

- Chip initialization, auto-aging and spanning tree algorithm support by firmware

- Auto-sensing 10/100M media speed, duplex mode, and flow-control capability by firmware

- 50MHz internal reference clock rate

- 50~100MHz SDRAM clock rate, typically 83MHz

- 50~100MHz SSRAM clock rate, typically 83MHz

- Single +3.3V supply, 0.3µm standard CMOS technology

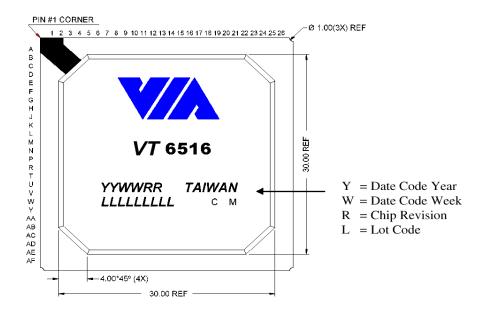

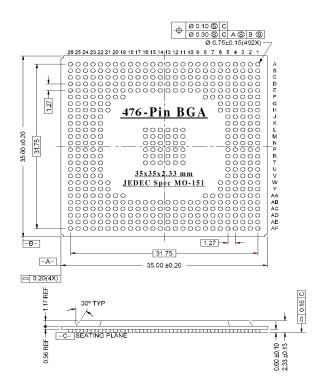

- 476 ball BGA package

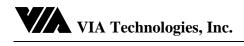

# **BLOCK DIAGRAM**

Figure 1: Block Diagram

99/12/09

# BALL OUT DIAGRAM

RMII-mode Ball out Diagram

|    | 1           | 2           | 3           | 4          | 5          | 6      | 7    | 8    | 9    | 10   | 11   | 12   | 13   | 14   | 15   | 16  | 17  | 18    | 19    | 20     | 21     | 22     | 23 |

|----|-------------|-------------|-------------|------------|------------|--------|------|------|------|------|------|------|------|------|------|-----|-----|-------|-------|--------|--------|--------|----|

| A  |             |             | RXD1.1      | TXEN1      | TXD1.0     | RXD0.0 | MD1  | MD3  | MD5  | MD7  | MD9  | MD11 | MD45 | MD47 | RAS0 | MA3 | MA7 | MA11  | DCS2  | DWE0   | MD49   | MD20   | MI |

|    |             | V1          |             |            |            |        |      |      |      |      |      |      |      |      |      |     |     |       |       |        |        |        |    |

| В  |             |             |             |            | CSDV0      |        |      | MD34 | MD36 | MD38 | MD40 | MD42 | MD14 | CAS1 | MA0  | MA4 | MA8 | BA0   | DCS1  |        | MD18   | MD52   |    |

| C  |             |             |             |            | TXEN0      |        |      | MD2  | MD4  | MD6  | MD8  | MD10 | MD46 | CAS0 | MA1  | MA5 | MA9 | BA1   | DCS0  | MD16   | MD50   | MD21   | MI |

| D  |             | CSDV3       |             |            |            | NC     | MD33 | GND  | MD37 | MD39 | MD41 | MD43 | MD13 | MD15 | RAS1 | MA2 | MA6 | MA10  | DCS3  | MD48   | MD19   | MD53   | MI |

| E  |             | TXD0.3      |             |            |            | GNDI   | GND  | MD35 | VDD  | VDD  | VDD  | MD12 | MD44 | GND  | GND  | GND | VDD | VDD   | VDD   | MD17   | MD51   | GNDI   | DC |

| F  | RXD1.4      | TXD0.4      | RXD0.4      | TXEN4      | RCLK5<br>0 | VDDI   | GND  | NC   |      |      |      |      |      |      |      |     |     |       | NC    | GND    | GNDI   | VDDI   | MI |

| G  | RXD0.5      | CSDV4       | TXD1.4      | TXEN5      | VDD        | GND    |      |      |      |      |      |      |      |      |      |     |     |       |       |        | GND    | SCLK   | SD |

| H  | TXD1.5      | RXD1.5      | TXD0.5      | NC         | VDD        | VDD    |      |      |      |      |      |      |      |      |      |     |     |       |       |        | NC     | SD23   | SD |

| J  | TXD0.6      | RXD0.6      | CSDV5       | NC         | VDD        |        |      |      |      |      |      |      |      |      |      |     |     |       |       |        |        | VDD    | SD |

| K  | CSDV6       | TXD1.6      | RXD1.6      | TXEN6      | NC         |        |      |      |      |      |      |      |      |      |      |     |     |       |       |        |        | VDD    | SA |

| L  | RXD1.7      | TXD0.7      | RXD0.7      | NC         | GND        |        |      |      |      |      | GND  | GND  | GND  | GND  | GND  | GND |     |       |       |        |        | VDD    | SA |

| M  | CSRV7       | TXD1.7      | TXEN7       | NC         | GND        |        |      |      |      |      | GND  | GND  | GND  | GND  | GND  | GND |     |       |       |        |        | SA10   | SA |

| N  | RXD1.8      | TXD1.8      | CSDV8       | TXEN8      | NC         |        |      |      |      |      | GND  | GND  | GND  | GND  | GND  | GND |     |       |       |        |        | SA15   | SA |

| P  | TXD0.8      | RXD0.8      | CSDV9       | TXEN9      | NC         |        |      |      |      |      | GND  | GND  | GND  | GND  | GND  | GND |     |       |       |        |        | GND    | SD |

| R  | TXD1.9      | RXD1.9      | TXD0.9      | NC         | VDD        |        |      |      |      |      | GND  | GND  | GND  | GND  | GND  | GND |     |       |       |        |        | GND    | SD |

| T  | RXD0.9      | RXD0.1<br>0 | TXD0.1<br>0 | TXEN1<br>0 | VDD        |        |      |      |      |      | GND  | GND  | GND  | GND  | GND  | GND |     |       |       |        |        | SD11   | SD |

| U  | RXD1.1<br>0 | TXD1.1<br>0 | CSDV1       | NC         | VDD        |        |      |      |      |      |      |      |      |      |      |     |     |       |       |        |        | VPP    | SA |

| v  | RXD0.1      | TXD0.1      | RXD1.1      | TXEN1      | VDD        |        |      |      |      |      |      |      |      |      |      |     |     |       |       |        |        | VPP    | so |

| w  | TXD1.1      | CSDV1       | RXD0.1      | TXEN1      | NC         | GND    |      |      |      |      |      |      |      |      |      |     |     |       |       |        | GND    | SCS3#  | SC |

| Y  | TXD0.1      | RXD1.1      | TXD1.1<br>2 | NC         | GND        | GNDI   |      |      |      |      |      |      |      |      |      |     |     |       |       |        | GNDI   | HCLK   | HD |

| AA | CSDV1       | RXD0.1      | TXD0.1<br>3 | NC         | GNDI       | VDDI   | VDD  | VDD  |      |      |      |      |      |      |      |     |     |       | GND   | GND    | GND    | GNDI   | HE |

| AB | RXD1.1<br>3 | TXEN1<br>3  | TXD1.1<br>3 | NC         | VDDI       | VDD    | VDD  | NC   | VPP  | VPP  | NC   | NC   | GND  | GND  | NC   | NC  | VPP | VPP   | VPP   | TEST12 | VDDI   | GND    | HE |

| AC | CSDV1       | CSDV1<br>4  | TXD1.1<br>4 | NC         | EEC        | NC     | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC  | NC  | NC    | TEST7 | TEST11 | TEST16 | TEST17 | HE |

| AD | RXD1.1      | TXD0.1<br>4 | RXD1.1<br>5 | TXEN1<br>5 | EEIO       | NC     | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC  | NC  | TEST3 | TEST6 | TEST10 | TEST15 | TEST20 | TE |

| AE | RXD0.1      | CSDV1       | TXD0.1<br>5 | MDC        | NC         | NC     | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC  | NC  | TEST2 | TEST5 | TEST9  | TEST14 | TEST19 | TE |

| AF | TXEN1<br>4  | TXD1.1<br>5 | RXD0.1<br>5 | MDIO       | NC         | NC     | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC   | NC  | NC  | TEST1 | TEST4 | TEST8  | TEST13 | TEST18 | TE |

99/12/09

**MII-mode Ballout Diagram**

|    | -1110C | 2          | 2          | 4     | 15    |       | 7     | e     | 0     | 10    | 11    | 12                | 13          | 14                | 15                | 16          | 17                | 18    | 19    | 20     | 21     | 22     | 722  |

|----|--------|------------|------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|-------------|-------------------|-------------------|-------------|-------------------|-------|-------|--------|--------|--------|------|

| A  | CRS1   | RXD3_      | COL0       | TXD1_ | RXD0_ |       | MD32  | MD34  | MD36  | MD38  | MD40  | MD42              | MD14        | CAS1#             | MA0               | MA4         | MA8               | BA0   |       | DWE1#  |        | MD20   | MI   |

| В  | RXD1_  | 0<br>RXDV0 | TXD3_      | RXD2_ | CRS0  | TXD0_ | MD0   | MD2   | MD4   | MD6   | MD8   | MD10              | MD46        | CAS0#             | MA1               | MA5         | MA9               | BA1   | DCS0# | MD16   | MD50   | MD52   | MI   |

| C  | TXEN1  | TXD1_      | TXD0_      | TXD2_ | TXEN0 | RXD1_ | MD33  | MD35  | MD37  | MD39  | MD41  | MD43              | MD13        | MD15              | RAS1#             | MA2         | MA6               | MA10  | DCS3# | MD48   | MD19   | MD21   | MI   |

| D  | TXD3_  | RXD0_      | COL1       | NC    | NC    | NC    | MD3   | VSS   | MD7   | MD9   | MD11  | MD12              | MD44        | RAS0#             | MA3               | MA7         | MA11              | DCS2# | DWE0# | MD17   | MD51   | MD53   | MI   |

| E  | RXD2_  | RXDV1      | RXD3_      | NC    | VDD   | GND   | VSS   | MD5   | VCC   | VCC   | VCC   | MD45              | MD47        | VSS               | VSS               | VSS         | VCC               | VCC   | VCC   | MD49   | NC     | GND    | DC   |

| F  | RXD1_  | TXD2_      | RXD0_      | TXEN2 | RCLK5 | VDD   | VSS   | NC    |       |       |       |                   |             |                   |                   |             |                   |       | NC    | VSS    | GND    | VDD    | MI   |

| G  | RXD2_  | TXD0_      | TXD1_      | COL2  | VCC   | VSS   |       |       |       |       |       |                   |             |                   |                   |             |                   |       |       |        | VSS    | SCLK   | SD   |

| Н  | TXD3_  | CRS2       | TXD2_      | RCLK2 | VCC   | VCC   |       |       |       |       |       |                   |             |                   |                   |             |                   |       |       |        | NC     | SD23   | SD   |

| J  | TXD0_  | RXD3_      | 2<br>RXDV2 | TCLK2 | VCC   |       |       |       |       |       |       |                   |             |                   |                   |             |                   |       |       |        |        | VCC    | SD   |

| K  | RXD0_  | CRS3       | TXD1_      | RXD1_ | TXEN3 |       |       |       |       |       |       |                   |             |                   |                   |             |                   |       |       |        |        | VCC    | SA   |

| L  | RXD3_  | TXD2_      | RXD2_      | RCLK3 | VSS   |       |       |       |       |       | VSS   | VSS               | VSS         | VSS               | VSS               | VSS         |                   |       |       |        |        | VCC    | SA   |

| M  | RXDV3  | TXD3_      | COL3       | TCLK3 | VSS   |       |       |       |       |       | VSS   | VSS               | VSS         | VSS               | VSS               | VSS         |                   |       |       |        |        | SA10   | SA   |

| N  | TXD0_  | RXD1_      | TXD1_      | CRS4  | TXEN4 |       |       |       |       |       | VSS   | VSS               | VSS         | VSS               | VSS               | VSS         |                   |       |       |        |        | SA15   | SA   |

| P  | TXD3_  | RXD0_      | RXDV4      | COL4  | RCLK4 |       |       |       |       |       | VSS   | VSS               | VSS         | VSS               | VSS               | VSS         |                   |       |       |        |        | VSS    | SD   |

| R  | RXD2_  | RXD3_      | TXD2_      | TCLK4 | VCC   |       |       |       |       |       | VSS   | VSS               | VSS         | VSS               | VSS               | VSS         |                   |       |       |        |        | VSS    | SD   |

| T  | RXD1_  | RXD0_      | TXD0_      | TXEN5 | VCC   |       |       |       |       |       | VSS   | VSS               | VSS         | VSS               | VSS               | VSS         |                   |       |       |        |        | SD11   | SD   |

| U  | RXD2_  | TXD1_      | CRS5       | TCLK5 | VCC   |       |       |       |       |       |       |                   |             |                   |                   |             |                   |       |       |        |        | VCC    | SA   |

| v  | TXD3_  | TXD2_      | RXD3_      | COL5  | VCC   |       |       |       |       |       |       |                   |             |                   |                   |             |                   |       |       |        |        | VCC    | so   |

| W  | TXD0_  | RXDV5      | RXD0_      | TXEN6 | RCLK5 | VSS   |       |       |       |       |       |                   |             |                   |                   |             |                   |       |       |        | VSS    | SCS3#  | SC   |

| Y  | CRS6   | RXD1_      | TXD1_      | TCLK6 | VSS   | GND   |       |       |       |       |       |                   |             |                   |                   |             |                   |       |       |        | GND    | HCLK   | HD   |

| AA | RXD3_  | RXD2_      | TXD2_      | RCLK6 | GND   | VDD   | VCC   | VCC   |       |       |       |                   |             |                   |                   |             |                   |       | VSS   | VSS    | VSS    | GND    | НΩ   |

| AB | RXDV6  | COL6       | TXD3_      | TCLK7 | VDD   | VCC   | VCC   | NC    | VCC   | VCC   | TCLK9 | RXD3_<br>10       | VSS         | VSS               | CRS10             | RCLK1       | VCC               | VCC   | VCC   | TEST12 | VDD    | VSS    | HD   |

| AC | RXD1_  | CRS7       | TXD1_      | RCLK7 | EEC   | RCLK8 | TCLK8 | RXD3_ | RXD2_ | RCLK9 | TXD2_ |                   | RCLK1       | TCLK1             | RXD3_<br>11       | RXDV1       | TCLK1             | CRS11 | TEST7 | TEST11 | TEST16 | TEST17 | HE   |

| AD | RXD0_  | TXD0_      | RXD3_      | COL7  | EEIO  | RXD0_ | TXD0_ | TXD3_ | RXD1_ | TXEN9 | TXD3_ | RXD1_             | TXEN1       | TXD2_             | RXD2_             | TXEN1       |                   | TEST3 | TEST6 | TEST10 | TEST15 | TEST20 | ) TE |

| AE | TXEN7  | RXDV7      | TXD2_      | MDC   | RXD2_ | RXDV8 | TXD1_ | COL8  | RXD0_ | TXD0_ | COL9  | 10<br>RXD0_<br>10 | TXD0_<br>10 | 10<br>TXD3_<br>10 | 11<br>RXD1_<br>11 | TXD0_<br>11 | 11<br>TXD3_<br>11 | TEST2 | TEST5 | TEST9  | TEST14 | TEST19 | TE   |

| AF | TXD3_  | RXD2_      | MDIO       | RXD3_ | RXD1_ | TXEN8 | TXD2_ | CRS8  | RXDV9 | TXD1_ | CRS9  | RXDV1             | TXD1_       | COL10             | RXD0_             | TXD1_       | COL11             | TEST1 | TEST4 | TEST8  | TEST13 | TEST18 | TE   |

|    | 1      | /          | L          | 0     | 0     |       | 0     |       | L     | 7     | L     | 0                 | 10          | l                 | 11                | 11          |                   | L     |       | L      |        |        | 4    |

99/12/09

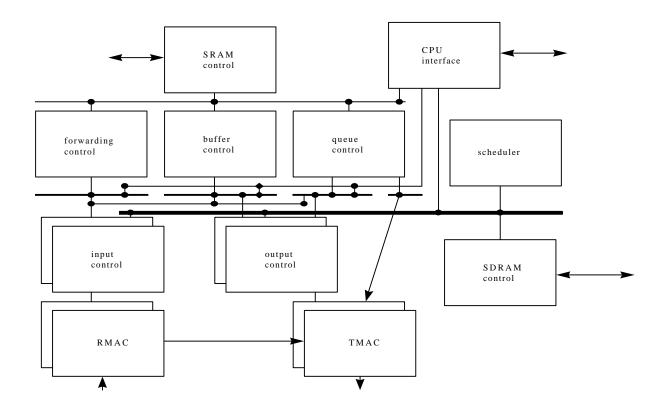

#### LOGIC SYMBOL

# PIN DESCRIPTIONS

| No.               | Name      | Type | Description                                                                                                                    |  |  |  |  |  |  |  |

|-------------------|-----------|------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                   | T         |      | SDRAM Interface                                                                                                                |  |  |  |  |  |  |  |

| See Ball<br>Table | MD[63:0]  | I/O  | SDRAM Data: 64-bit SDRAM data bus. These signals connect directly to the data input/output pins of the SDRAM devices.          |  |  |  |  |  |  |  |

| See Ball<br>Table | MA[11:0]  | О    | SDRAM Address Bus: 12-bit SDRAM data bus. These signals connect directly to the address input of the SDRAM devices.            |  |  |  |  |  |  |  |

| See Ball<br>Table | BA[1:0]   | О    | Bank Identifier for Bank 0 and 1:                                                                                              |  |  |  |  |  |  |  |

| See Ball<br>Table | RAS [1:0] | О    | Row Address Strobes for Bank 0 and 1:  DRAM row address strobes. RAS [0] is used for Bank 0. RAS [1] is used for Bank 1.       |  |  |  |  |  |  |  |

| See Ball<br>Table | CAS[1:0]  | О    | Column Address Strobes for Bank 0 and 1:  DRAM column address strobes. CAS [0] is used for Bank 0. CAS [1] is used for Bank 1. |  |  |  |  |  |  |  |

| See Ball<br>Table | DWE[1:0]  | О    | DRAM Write Enable for Bank 0 and 1:                                                                                            |  |  |  |  |  |  |  |

| See Ball<br>Table | DCS[3:0]  | О    | DRAM Chip Select: VT-3061A supports at most 4 SDRAM DIMM modules.                                                              |  |  |  |  |  |  |  |

|                   |           | •    | SRAM Interface                                                                                                                 |  |  |  |  |  |  |  |

| See Ball<br>Table | SD[31:0]  | I/O  | SRAM Data:  32-bit SRAM data bus. These signals connect directly to the data input/output pins of the SRAM devices.            |  |  |  |  |  |  |  |

| See Ball<br>Table | SA[17:0]  | 0    | SRAM Address Bus:  18-bit SDRAM data bus. These signals connect directly to the address input of the SDRAM devices.            |  |  |  |  |  |  |  |

| See Ball<br>Table | SCS [4:0] | 0    | SRAM Chip Select:         SRAM Type       Chip Select Pins       Address Pins                                                  |  |  |  |  |  |  |  |

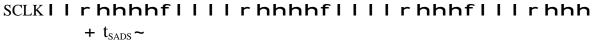

| See Ball<br>Table | SADS[1:0] | О    | Synchronous Processor Address Status                                                                                           |  |  |  |  |  |  |  |

| See Ball<br>Table | SOE [1:0] | О    | Output Enable                                                                                                                  |  |  |  |  |  |  |  |

| See Ball<br>Table | SWE [1:0] | О    | SRAM Write Enable:                                                                                                             |  |  |  |  |  |  |  |

|                   |           | 1    | Miscellaneous Interface                                                                                                        |  |  |  |  |  |  |  |

| 0 7 11            |             |     |                                                                                                        |

|-------------------|-------------|-----|--------------------------------------------------------------------------------------------------------|

| See Ball<br>Table | EEC         | O   | Serial EEPROM Interface Clock Output:                                                                  |

| Table             |             |     | EEPROM Device Addressing in the demo board:                                                            |

|                   |             |     | PAGE 0 (EEPROM): Device Address = 1010 000 XXXXXXXX                                                    |

|                   |             |     | PAGE 1 (EEPROM): Device Address = 1010 001 XXXXXXXX                                                    |

|                   |             |     | PAGE 2 (EEPROM): Device Address = 1010 010 XXXXXXXX                                                    |

|                   |             |     | PAGE 3 (EEPROM): Device Address = 1010 011 XXXXXXXX                                                    |

|                   |             |     | PAGE 4 (SDRAM BANK-0): Device Address = 1010 100 XXXXXXXX                                              |

|                   |             |     | PAGE 5 (SDRAM BANK-1): Device Address = 1010 101 XXXXXXXX                                              |

| See Ball<br>Table | EEIO        | I/O | Serial EEPROM Interface Data I/O                                                                       |

| See Ball<br>Table | MDC         | О   | Management Interface (MI) Clock Output                                                                 |

| See Ball<br>Table | MDIO        | I/O | Management Interface (MI) Data I/O                                                                     |

| See Ball<br>Table | RCLK50      | I   | Main Reference Clock:                                                                                  |

| See Ball<br>Table | DCLK        | I   | SDRAM Reference Clock:                                                                                 |

| See Ball<br>Table | SCLK        | I   | SRAM Reference Clock                                                                                   |

| See Ball          | HCLK        | О   | HOST Reference Clock                                                                                   |

| Table             |             |     | HCLK is determined by the strapping pins in SYSLED[3:1], i.e. the jump selection of J1[5-6, 3-4, 1-2]: |

|                   |             |     | J1[OFF,OFF,OFF] => 8MHz                                                                                |

|                   |             |     | J1[ OFF,OFF, ON] => 16MHz                                                                              |

|                   |             |     | J1[OFF, ON, OFF] => 25MHz                                                                              |

|                   |             |     | J1[OFF, ON, ON] => 4MHz                                                                                |

|                   |             |     | J1[ ON,OFF,OFF] => 33MHz                                                                               |

| See Ball<br>Table | RESET       | I   | SYSTEM RESET                                                                                           |

| See Ball          | SYSLED[26:0 | О   | SYSTEM Output Pins for LED:                                                                            |

| Table             | ]           |     | SYSLED[8:0] are connected to pull-up IO PADs for strapping.                                            |

|                   |             |     | SYSLED[25:9] are connected to IO PADs without pull up/down.                                            |

|                   |             |     | All SYSLED[25:0] are                                                                                   |

|                   |             |     |                                                                                                        |

# **HOST Interface**

1.4

| See Ball |          | _   |                                                                                                                                                                           |

|----------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table    | HA[2:0]  | I   | HOST IDE-Interface Address Bus:                                                                                                                                           |

| Table    |          |     | 3'b000: command the switch that the whole 16-bit data in the HOST data bus HD[15:0] is valid for packet-data read/write.                                                  |

|          |          |     | 3'b001: command the switch that only the 8-bit data in the HOST data bus HD[15:0] is valid for internal registers read/write.                                             |

|          |          |     | 3'b010: command the switch to write the low byte in the HOST data bus HD[15:0] into the low byte of the 16-bit switch address register for internal registers reference.  |

|          |          |     | 3'b011: command the switch to write the low byte in the HOST data bus HD[15:0] into the high byte of the 16-bit switch address register for internal registers reference. |

|          |          |     | 3'b1xx: bus-idle command. Keep this address bus to be 3'b111 as the HOST has no access to VT-3061A.                                                                       |

| See Ball | HD[15:0] | I/O | HOST IDE-Interface Data Bus:                                                                                                                                              |

| Table    |          |     | The whole 16-bit data bus is valid for packet data read/write. However, only the 8-bit data bus is valid for internal registers read/write.                               |

| See Ball | HCS      | I   | HOST Chip Select:                                                                                                                                                         |

| Table    |          |     | Active LOW. HCS must be asserted during the access of HOST IDE interface.                                                                                                 |

| See Ball | ĪŌR      | I   | IO READ:                                                                                                                                                                  |

| Table    |          |     | High-to-Low Edge Trigger. IOR must be asserted from high to low to begin the read cycle of HOST IDE interface.                                                            |

| See Ball | ĪŌW      | I   | IO READ:                                                                                                                                                                  |

| Table    |          |     | High-to-Low Edge Trigger. IOW must be asserted from high to low to begin the write cycle of HOST IDE interface.                                                           |

| See Ball | INTRQ    | О   | Interrupt Request:                                                                                                                                                        |

| Table    |          |     | Connected to the HOST external interrupt pin. It is asserted as the following four interrupt events happen:                                                               |

|          |          |     | (1) MII Management Registers read/write command done                                                                                                                      |

|          |          |     | (2) EEPROM read/write command done                                                                                                                                        |

|          |          |     | (3) Receiving a packet destined to HOST                                                                                                                                   |

|          |          |     | (4) Finishing transmission of a packet issued by HOST                                                                                                                     |

|          |          |     | The interrupt cause is recorded in register IRQSTS[3:0] in address 2000H. To clear the individual interrupt, The corresponding register has to be written:                |

|          |          |     | (1) register CLR_PHY_INT in 1806H for PHY interrupt.                                                                                                                      |

|          |          |     | (2) register CLR_EE_INT in 1C04H for EEPROM interrupt.                                                                                                                    |

|          |          |     | (3) register CLR_RCV_INT in 6403H for packet-receiving interrupt.                                                                                                         |

|          |          |     | • register CLR_SENT_INT in 6411H for packet-sent interrupt.                                                                                                               |

| MII Interfa | ace        |   |                                                                                                                                                                                                                                                                                                   |

|-------------|------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| See Ball    | TCLK[11:0] | I | Transmit Clock for Port 0-11:                                                                                                                                                                                                                                                                     |

| Table       |            |   | TCLK is driven by the PHY device. TCLK is a continuous clock that provides the timing reference for the transfer of the TXEN and TXD signals to the PHY. A PHY operating at 100Mbps must provide a TCLK frequency of 25MHz and a PHY operating at 10Mbps must provide a TCLK frequency of 2.5MHz. |

1.0

| See Ball | TXD<3:0>[11: | О | Transmit Data for Port 0-11:                                                                                                                                                                                                                                                                                                                           |

|----------|--------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table    | 0]           |   | TXD is a bundle of 4 data signals (TXD<3:0>) that shall transition to the TCLK. For each TCLK period in which TXEN is asserted, TXD<3:0> are accepted for transmission by the PHY. TXD<0> is the least significant bit. While TXEN is de-asserted, TXD<3:0> shall have no effect upon the PHY, and the value of TXD<3:0> is unspecified.               |

| See Ball | TXEN[11:0]   | O | Transmit Enable for Port 0-11:                                                                                                                                                                                                                                                                                                                         |

| Table    |              |   | TXEN shall transition synchronous to the TCLK. TXEN indicates the nibbles presenting on the MII for transmission. It shall be asserted synchronously with the first nibble of the preamble and shall remain asserted while all nibbles to be transmitted are presented to the MII.                                                                     |

| See Ball | COL[11:0]    | I | Collision Detected for Port 0-11:                                                                                                                                                                                                                                                                                                                      |

| Table    |              |   | COL shall be asserted by the PHY asynchronously upon detection of a collision on the medium, and shall remain asserted while the collision condition persists.                                                                                                                                                                                         |

| See Ball | CRS[11:0]    | I | Carrier Sense for Port 0-11:                                                                                                                                                                                                                                                                                                                           |

| Table    |              |   | CRS shall be asserted by the PHY asynchronously upon detection of a non-idle medium or while TX_EN is asserted. CRS shall be de-asserted by the PHY asynchronously upon detection of idle conditions on both transmit and receive media. The PHY shall ensure that CRS remains asserted throughout the duration of a collision condition.              |

| See Ball | RXD<3:0>[11  | I | Receive Data for Port 0-11:                                                                                                                                                                                                                                                                                                                            |

| Table    | :0]          |   | RXD is a bundle of 4 data signals (RXD<3:0>) that shall transition to the RCLK. For each RCLK period in which RXDV is asserted, RXD<3:0> from the PHY are accepted by the switch's MAC. RXD<0> is the least significant bit. While RXDV is de-asserted, RXD<3:0> shall have no effect upon the switch's MAC, and the value of RXD<3:0> is unspecified. |

| See Ball | RCLK[11:0]   | I | Receive Clock for Port 0-11:                                                                                                                                                                                                                                                                                                                           |

| Table    |              |   | RCLK is sourced from the PHY. RCLK is a continuous clock that provides the timing reference for the transfer of the RXDV and RXD signals from the PHY. A PHY operating at 100Mbps must provide a RCLK frequency of 25MHz and a PHY operating at 10Mbps must provide a RCLK frequency of 2.5MHz.                                                        |

| See Ball | RXDV[11:0]   | I | Receive Data Valid for Port 0-11:                                                                                                                                                                                                                                                                                                                      |

| Table    |              |   | RXDV is driven by the PHY to indicate the nibbles presenting on the MII for receiving. RXDV shall transition synchronous to the RCLK. It shall be asserted synchronously with the first nibble of the preamble and shall remain asserted while all nibbles to be received are presented to the MII.                                                    |

Note: Some flat MII input pin when the VT6516 under the RMII application, please use 22 ohm resister pull down, refer to Table XXXX

17

| RMII inter | face        |   |                                                      |

|------------|-------------|---|------------------------------------------------------|

| See Ball   | CRS_DV[15:0 | I | Carries sense and data valid from port 15 to port 0: |

| Table      | ]           |   |                                                      |

| See Ball   | RXD0[15:0]  | I | Receive data zero from port 15 to port 0:            |

| Table      |             |   |                                                      |

| See Ball   | RXD1[15:0]  | I | Receive data one from port 15 to port 0:             |

| Table      |             |   |                                                      |

| See Ball   | TXEN[15:0]  | О | Transmit enable from port 15 to port 0:              |

| Table      |             |   |                                                      |

| See Ball   | TXD0[15:0]  | О | Transmit data zero from port 15 to port 0:           |

| Table      |             |   |                                                      |

| See Ball   | TXD1[15:0]  | О | Transmit data one from port 15 to port 0:            |

| Table      |             |   |                                                      |

| Power Sup | ply & Ground |   |                                                                           |

|-----------|--------------|---|---------------------------------------------------------------------------|

| See Ball  | VDD, VDDA    | P | Positive 3.3V Supply: Supply power to Internal digital logic, Digital I/O |

| Table     |              |   | pads, and TD, TX pads. Double bonding may be required.                    |

| See Ball  | VSS, VSSA    | G | Negative Supply: digital ground. Multiple bonding pads are required to    |

| Table     |              |   | separate core and I/O pads ground.                                        |

# JUMPER STRAPPING

| Jumper               | Pin       | Description                                       |

|----------------------|-----------|---------------------------------------------------|

| HOST Clock           |           |                                                   |

| J1 [5-6], [3-4], [1- | SYSLED[3: | HOST Clock (HCLK) Rate Selection:                 |

| 2]                   | 1]        | J1[OFF,OFF,OFF] (SYSLED[3:1]==3'b111) => 8MHz     |

|                      |           | J1[ OFF,OFF, ON] (SYSLED[3:1]==3'b110) => 16MHz   |

|                      |           | J1[OFF, ON, OFF] (SYSLED[3:1]==3'b101) => 25MHz   |

|                      |           | J1[OFF, ON, ON] (SYSLED[3:1]==3'b100) => 4MHz     |

|                      |           | J1[ ON,OFF,OFF] (SYSLED[3:1]==3'b011) => 33MHz    |

| PHY Mode             |           |                                                   |

| J1 [7-8]             | SYSLED[4] | PHY Device Selection:                             |

|                      |           | J1[OFF] (SYSLED[4]==1'b1) => RMII PHY             |

|                      |           | J1[ ON] (SYSLED[3:1]==1'b0) => MII PHY            |

| SRAM Type            |           |                                                   |

| J1 [11-12,9-10]      | SYSLED[6: | SRAM Device Type Selection:                       |

|                      | 5]        | J1[OFF,OFF] (SYSLED[6:5]==2'b11) => 64K x 32 SRAM |

|                      |           | J1[OFF,ON] (SYSLED[6:5]==2'b10) => 128K x 32 SRAM |

|                      |           | J1[ON,OFF] (SYSLED[6:5]==2'b01) => 32K x 32 SRAM  |

#### SECTION I FUNCTIONAL DESCRIPTIONS

#### 1. GENERAL DESCRIPTION

The VT6516 is a switch engine chip implementation of a 16 ports 10/100M Ethernet switch system for IEEE 802.3 and IEEE 802.3u network. Each of individual port can be either auto-sensing or manually selected to run at 10Mbps or 100Mbps speed rate and under full or half duplex mode.

There are sixteen independent MACs within the VT6516 chip. The MAC controller controls the receiving, transmitting, and deferring of each individual port, and the MAC controller also provides framing, FCS checking, error handling, status indication and flow control function.

The VT6516 10/100M N-way switch port IC is wire-speed performance and low-cost packet switch; it can forward up to 148,810 packets/sec on each Ethernet port. The VT6516 support 12 ports MII or 16 ports RMII (reduce MII) interface for network interface,

The VT6516 used the simple 8/16 bits ISA-like interface to support initiation, expansion and management. The system CPU can access various registers inside VT6516 through a simple ISA-like CPU interface. The CPU can configure the switch by writing into the appropriate registers, or retrieve the status of the switch by reading the corresponding registers. The CPU can also access the register of external transceiver (PHY) device through the CPU interface.

The VT6516 supports new features including port based VLAN, 802.3X flow control, and the VT6516 also support the sniffer function to monitor network traffic in special ports.

#### 2. THE VIA ETHER SWITCH ARCHITECTURE

The VT6516 switch engine uses the shared memory architecture. In order to improve the packet latency, VT6516 provides two methods for packet switching, one is cut-through, another is store-and-forwarding. A typical packet flow for Ethernet switch is described as follows in 4.5.

#### 2.1 Switch initialization procedures

- 1. Test all of the on board components except the switch chip or access VIA the switch chip, including UART, LED, etc.

- 2. Switch SDRAM test --- switch chip SDRAM control hardware initialization, configuration, SDRAM size determination (VIA embedded EEPROM in SDRAM module) and read write test.

- 3. Switch SRAM test --- switch chip SDRAM control hardware initialization and read write test. Note that the SRAM size determination is VIA strapping.

- 4. Switch IO registers read write test.

- 5. Ethernet PHY registers read write test ---- the CPU read/write to PHY devices will go through PHY control in switch chip. Although they are outside components, but we test them as part of the switch chip.

- 6. Determine link table size; reset free buffer list pointers of bank 0 and 1; initialize free memory block counter. Note that permanent buffer management is controlled by allocating bit mask. They will be cleared automatically in the hardware reset or software reset.

#### 2.2 Packet Switching Flow

1. After the switch microprocessor activates a port during initialization, the input control of that port preallocates one packet buffer from buffer pool. In the beginning, the buffer allocated will be from private buffer pool, but subsequent buffers may come from either private or public buffer pools.

- 2. When receive MAC (RMAC) receives a packet data from the network interface either through MII or reduced MII (RMII) it packs the data into 16-bit word then passes it to input control. If RMAC detects any error, it also notifies input control to stop forwarding process.

- 3. Input control extracts the destination MAC address from incoming data, passes it along to forwarding table control for forwarding decision. In the mean while, it packs 16-bit words into 64-bit quad-words, and saves it to an input FIFO before storing the packet data to SDRAM.

- 4. If the switch is configured to "store and forward" mode, input control queues the packet to the output queue of the destination port after input control is informed by RMAC that this is a good packet and it stores all packet data to SDRAM. If the switch is configured to "cut-through" mode, the input control queues the packet to the output queue of the destination port after enough amount of packet is stored in SDRAM to prevent output FIFO under-run.

- 5. After the whole packet is received and FCS is correct, input control pass the source MAC address of the packet to forwarding table control for address learning.

- 6. Output control of the outbound port de-queue the packet from output queue, and fetch packet data from SDRAM and save it into output FIFO. Then it notifies the transmit MAC (TMAC) of the new packet to transmit.

- 7. TMAC grabs 16-bit at a time from output control, adds preamble and SFD to the beginning of the packet, then send them out. Proper deferring is done if necessary to conform to 802.3 standard.

- 8. After the packet is successfully transmitted, TMAC notifies output control of the successful transmission. Output control then returns the packet to buffer pool.

#### 3. Interface Descriptions

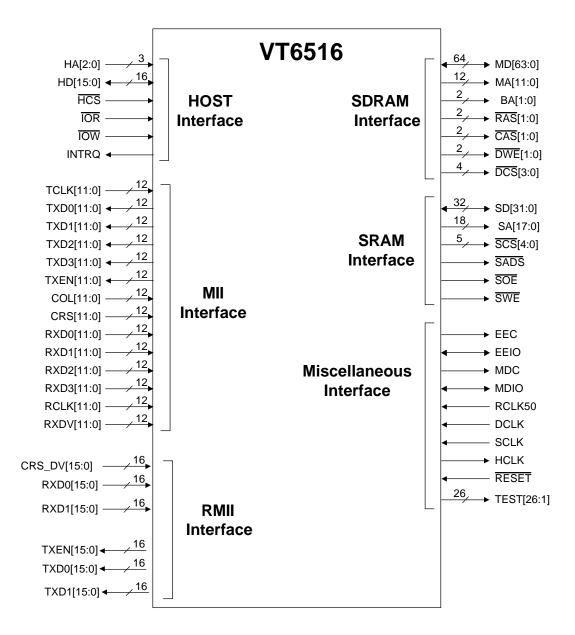

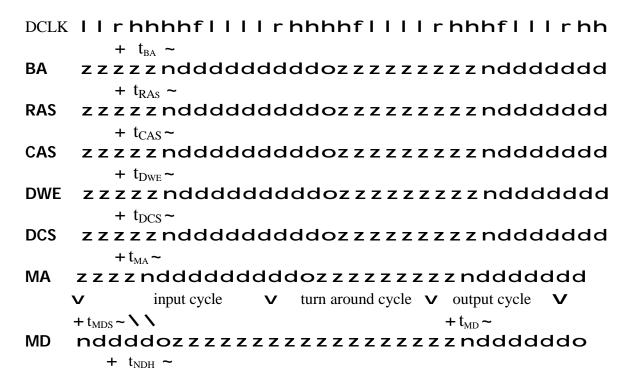

#### BUFFER MEMORY (SDRAM) INTERFACE AND TABLE (SSRAM) INTERFACE

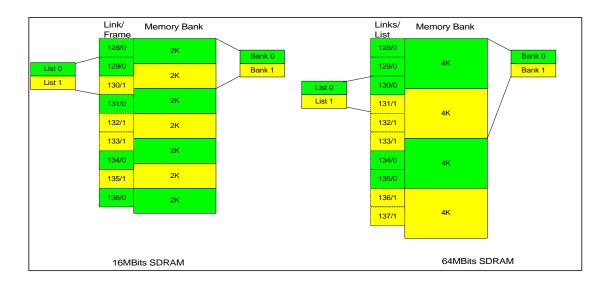

VT6516 provides a 64-bit SDRAM/SGRAM interface for packet buffering and a 32-bit synchronous SRAM (SSRAM) interface for maintaining address table and various link lists. VT6516 uses SDRAM as packet buffers. Each packet buffer is a 1536-byte contiguous memory block in SDRAM, and corresponds to a 12-byte link node data structure in SSRAM. Except the first 128 link nodes, each link node can be part of an output queue, a free buffer link list, or held in input or output control. The first 128 link nodes are divided into 16 groups, each pre-assigned to a specific input control, and bit-mapped inside buffer control for faster allocate/free operation and reduce SSRAM usage.

Initially, each input port control would request one packet buffer from its private buffer pool. Each time when a packet buffer is consumed by an incoming packet, the input port control will request another packet buffer to prepare for next packet. The common shared packet memory will be allocated only when there's no free permanent packet memory for that port. See Figure 3-4.

20

Figure 3-3

Following as the listing and figure 3-6 is the algorithm of initialization procedures for 2 bank free list of SDRAM.

For 16 Mbit SDRAM as following,

- -- Bank0 free link list:

- 128, 129, 131, 134, 136, 137, 139, 142, 144, 145, 147, 150, 152, 153, 155, 158, 160,...

- -- Bank1 free link list:

- 130, 132, 133, 135, 138, 140, 141, 143, 146, 148, 149, 151, 154, 156, 157, 159, 162, 164, ...

#### For 64 Mbit SDRAM as following,

- -- Bank0 free link list:

- 128, 129, 130, 134, 135, 139, 140, 141, 144, 145, 146, 150, 151, 155, 156, 157, 160, ...

- --Bank1 free link list:

- 131, 132, 133, 136, 137, 138, 142, 143, 147, 148, 149, 152, 153, 154, 158, 159, 163, ...

Figure 3-6: Algorithm of Initialization of Free Link Lists.

```

#define SRAM_ADDR_REG0 0x2001

#define SRAM ADDR REG1 0x2002

#define SRAM_ADDR_REG2 0x2003

#define SRAM_DATA_REG0 0x2004

#define SRAM_DATA_REG1 0x2005

#define SRAM_DATA_REG2 0x2006

#define SRAM_DATA_REG3 0x2007

#define SRAM_CMD_REG 0x2008

#define SRAM STATUS REG 0x2009

#define SRAM_ACCESS_IDLE 0x01

#define NULL_PTR

0x7FFFF

void writeLinkEntry(int entryID, int nextID)

reg_byte_write (SRAM_ADDR_REG0, entryID*3 & 0x0FF);

reg_byte_cont_write (((entryID*3) >> 8) & 0x0FF);

reg_byte_cont_write (((entryID*3) >> 16) & 0x0FF);

```

```

reg_byte_cont_write (nextID & 0x0FF); // data bits [7:0] reg_byte_cont_write ((nextID >> 8) & 0x0FF); // data bits [15:8]

reg_byte_cont_write ((nextID >> 16) & 0x0FF); // data bits [23:16]

reg_byte_cont_write (0); // data bits [31:24]

reg_byte_cont_write (0x02); // SRAM-write command

while (reg_byte_read(SRAM_STATUS_REG) != SRAM_ACCESS_IDLE) {}

void initFreeList16Mb(int maxLinkEntryNo)

{ // note: for 16Mb SDRAM,

Bank0 free list head pointer = 128

Bank1 free list head pointer = 130

int k; // k: current free entry id

int b0, b1; // b0, b1: bank0/1 free list head entry id

for(b0=b1= NULL_PTR, k= maxLinkEntryNo; k <=128; k--)

if (((k * 3) % 8) < 4)

{ writeLinkEntry(b0,k); b0=k;}

else { writeLinkEntry(b1,k); b1=k;}

void initFreeList64Mb(int maxLinkEntryNo)

{ // note: for 64Mb SDRAM,

Bank0 free list head pointer = 128

Bank1 free list head pointer = 131

int k; // k: current free entry id

int b0, b1; // b0, b1: bank0/1 free list head entry id

for(b0=b1= NULL_PTR, k= maxLinkEntryNo; k <=128; k--)

if (((k * 3) % 16) < 8)

{ writeLinkEntry(b0,k); b0=k;}

else { writeLinkEntry(b1,k); b1=k;}

```

#### 3.1.1 SDRAM interface

All frames received by the VT6516 will be stored into a common frame buffer memory, SDRAM. The SDRAM contains the packet buffers, each buffer is a 1536 (1.5K) bytes memory block. Each block is associated to an entry in link table in SRAM. The link entry includes a field (19 bits to support 512 MB) to point to next link entry. The figure 3-2 is buffer link list structure.

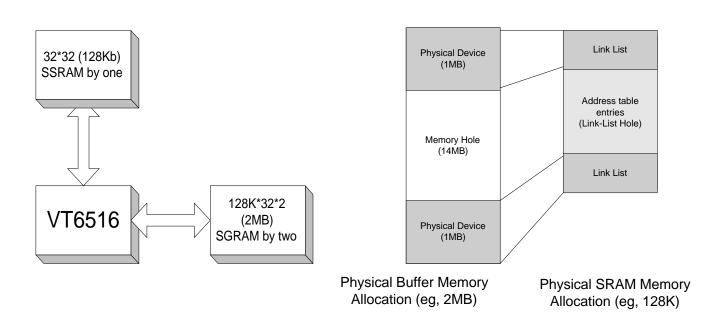

In order to provide the cost effective DRAM buffers, user can connect the 32 bits data SGRAM with VT6516 switch, there are two external buffer device using two double bank 128Kbits by 32 required. The following figure shows the minimum configuration of buffer memory and link/address memory. Note that the SGRAM physical memory hole is to accommodate the forwarding table into the SRAM link list hole.

The detail initial step of VT6516 as following,

- 1. Forwarding table base = 683 \* 3

- 2. SDRAM type equal to 16M bit

- 3. END0-3 = 2 (16MB)

- 4. Free list of SRAM have to be constructed by release public node in the sequence of buffers with blocks number

10922, 10911, ...10240, 681, 680, 128

Note: The buffers numbered 682 to 10239 are located in the buffer memory hole, those buffers will be not put into the free list.

5. Free Memory count equal to 1364

Otherwise like this minimum configuration, the entries support for difference SRAM size using normal Address table followed by free-list, the following table show the address entries support

| Buffers | 32*32 SSRAM | 64*32  | 64*64  |

|---------|-------------|--------|--------|

| 2MB     | 8K entries  | 8K~16K | 8K~64K |

| 4MB     | 8K entries  | 8K~16K | 8K~64K |

#### 3.1.2 SRAM interface

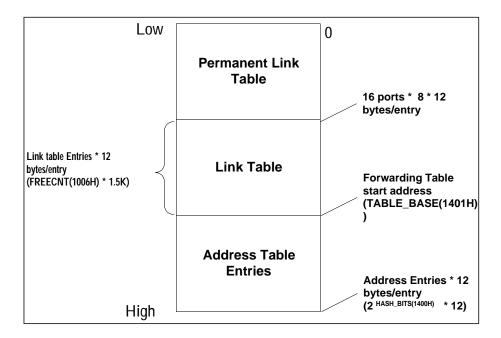

The feature 3-1 is SSRAM structure map, the SSRAM contains the forwarding address entries, SDRAM buffers link list and permanent buffers table.

Figure 3-1 SRAM

| 95   | 65                                                                                                     | 64 | 59 | 58 | 57 | 55 | 54 | 52  | 51 | 50 | 47 | 46 | 36 | 35 | 19 | 18 | 0 |

|------|--------------------------------------------------------------------------------------------------------|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|---|

| rese | reserved VLAN ID VLAN frame tag type priority frame type source packet byte port pointer to next entry |    |    |    |    |    |    | l l |    |    |    |    |    |    |    |    |   |

|      | 16 ports<br>+1 cpu                                                                                     |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |   |

Figure 3-2 Free buffer link structure

Table 1-0 Free buffer link structure

| bit 18-0  | Next entry pointer                                             |  |  |  |  |

|-----------|----------------------------------------------------------------|--|--|--|--|

| bit 35-19 | port mask (bit[16]: CPU port + bit[15:0]: Ethernet ports 0~15) |  |  |  |  |

| bit 46-36 | Packet byte count                                              |  |  |  |  |

| bit 50-47 | Source port ID                                                 |  |  |  |  |

| bit 51    | Frame type Reserved (zero)                                     |  |  |  |  |

| Bit 54-52 | Priority                                                       |  |  |  |  |

| Bit 57-55 | Frame tag type Reserved (zero)                                 |  |  |  |  |

| bit 58    | VLAN tag flag Reserved (zero)                                  |  |  |  |  |

| bit 64-59 | VLAN ID                                                        |  |  |  |  |

| bit 95-65 | reserved for future                                            |  |  |  |  |

| 95       | 64 | 63 58   | 57                | 56                     | 55 5         | 453 37             | 736 0                              |

|----------|----|---------|-------------------|------------------------|--------------|--------------------|------------------------------------|

| reserved |    | VLAN ID | VLAN<br>tage flag | static/dynamic<br>flag | age<br>count | port<br>mask       | bit-47:11<br>MAC address           |

|          |    |         |                   |                        |              | 16 ports<br>+1 cpu | fixed, even for key length = 11~15 |

Figure 3-5 The Address table entries structure +

The address table structure as figure 3-5, The address table entries contains the MAC address information from bit 11 to bit 47, others bits  $0\sim10$  or bits  $0\sim14$  ( $2K\sim32K$ ) as the address entries hashing index, the total address entries of device assigned by the HASH\_BITS(1400H).

Initialization procedures include to set forwarding address table control in normal mode and to invalidate all forwarding table entries by setting the age-count field as 0. Configure port mask register (USER\_PM) for broadcast MAC address. Configure port mask and MAC address pairs that allow any static MAC to port mask mapping.

Forwarding table entry has 96 bits, defined as follows:

| Table 1-1 Address table structur | Table ' | 1.1 | Addres | s table | structure |

|----------------------------------|---------|-----|--------|---------|-----------|

|----------------------------------|---------|-----|--------|---------|-----------|

| bit 36-0  | High bits (bit 47-11) of MAC address                                    |

|-----------|-------------------------------------------------------------------------|

| bit 53-37 | port mask (bit[16]: CPU port + bit[15:0]: Ethernet ports 0~15)          |

| bit 55-54 | age count                                                               |

| bit 56    | Static flag (0: dynamic entry, 1: static entry that can not be updated) |

| bit 57    | <del>VLAN tag flag</del> Reserved (zero)                                |

| bit 63-58 | VLAN ID                                                                 |

| bit 95-64 | Reserved for future                                                     |

And following is the algorithm for the initial the address entries;

```

#define SRAM_ADDR_REG0 0x2001

#define SRAM_ADDR_REG1 0x2002

#define SRAM_ADDR_REG2 0x2003

#define SRAM_DATA_REG0 0x2004

#define SRAM DATA REG1 0x2005

#define SRAM_DATA_REG2 0x2006

#define SRAM_DATA_REG3 0x2007

#define SRAM_CMD_REG 0x2008

#define SRAM_STATUS_REG 0x2009

#define SRAM_ACCESS_IDLE 0x01

void invalidateForwardEntry(int entryID)

{ // the entryID is starting from maxLinkEntryID with width of 96 bits

reg_byte_write (SRAM_ADDR_REG0, (entryID*3+1) & 0x0FF);

reg_byte_cont_write (((entryID*3+1) >> 8) & 0x0FF);

reg_byte_cont_write (((entryID*3+1) >> 16) & 0x0FF);

reg_byte_cont_write (nextID & 0x0FF); entry bits [32]

reg_byte_cont_write ((nextID >> 8) & 0x0FF);

reg_byte_cont_write ((nextID >> 16) & 0x0FF);

reg_byte_cont_write ((nextID >> 16) & 0x0FF);

reg_byte_cont_write (0x02); // SRAM-write command

while (reg_byte_read(SRAM_STATUS_REG) != SRAM_ACCESS_IDLE) {}

```

#### 3.1.3 CPU interface

The VT6516 support one ISA-like CPU interface, this CPU interface can cooperate with one simple microprocessor like 8031 or 8051. The CPU will access the switch control and status register to perform initialization and configurations. By the CPU interface, the frames of CPU port can be read/written from/into the buffer. The CPU interface can also be used to access the internal registers. The CPU interface also used to access the external PHY devices through the PHY control module.

The CPU firmware will perform following tasks,

- Read the configuration from switch register or from the EEPROM contains

- Initialize the switch followed by the configuration, those task including

- \* DRAM initialization

- \* SRAM initialization and link list construction

- \* Program for each network ports for users manual setting or read the auto-negotiation result

- start switch to receive frames and forward frames

- decrease the learning address aging count

- polling the network port change event and change the switch MAC negotiation mode.

- Receiving the STP defined BPDU packets

- Blocking or re-start port due to STP

- Access the network management counter of each port

For a management switch the CPU also perform the management function like receiving and transmitting the SNMP frame.

#### 3.1.4 Network interface

The VT6516 directly connect to 16 port RMII PHY or 12 port MII PHY device which compliant with IEEE standard (Please see IEEE 802.3u Fast Ethernet standard). Each Fast Ethernet port has following characteristics:

- Capable of supporting both 10MBps and 100MBps data rates in half and full duplex modes.

- Provide a simple management interface (SMI) for port status

- Perform all functions of the IEEE 802.3 protocol such as frame formatting, frame stripping, collision handling, deferred, etc.

- Adjustable preamble ,SFD and inter frame gap (IFG).

- IEEE 802.3X flow control supported

- IEEE 802.1D spanning tree protocol support, and all port state of listen and block configurable

#### 3.1.4.1 RMII interface

The VT6516 communicates with the external 10/100M Ethernet transceiver through the reduced MII (RMII) interface. The signals of RMII interface are described in Table-3-1

| Name     | Type | Description                                   |

|----------|------|-----------------------------------------------|

| CRSDV    | I    | Carrier sense and Data valid                  |

| RXD[0-1] | I    | Receive data bit 0 to 1, data rate with 50MHz |

| TXEN     | O    | Transmit Enable                               |

| TXD[0-1] | О    | Transmit Data bit 0 to 1                      |

Table 3-1 RMII interface signals

Figure 3-1 RMII timing diagram

(omitted)

#### 3.1.4.2 MII interface

The VT6516 communicates with the external 10/100M Ethernet transceiver through standard MII interface, in this mode the VT6516 became 12 ports MII port due to the MII signal multiplexed with RMII signal. But the ports number of internal remained as 16 ports. The signals of MII interface are described in Table-3-2:

Name Description Type TCLK Transmit Clock I TXD[3:0] O Transmit Data for. **TXEN** O Transmit COL I **Collision Detected** Ι CRS Carrier Sense I RXD[3:0] **Receive Data RCLK** Ι Receive Clock **RXDV** I Receive Data

Table 3-2 MII interface signals

Figure 3-2 MII timing diagram

(omitted)

#### **3.1.4.3 Flow control**

Under full-duplex mode operation, if the buffer utilization of whole switch has exceeded the upper threshold and the permanent buffer has been used up, a pause frame with a pause time interval will be send to the sending port to stop it from sending new frame. If register- FMFCT not enable at this switch, the public buffer will used until no more buffers. Then further incoming frames will be dropped. The unit in pause time field of the flow control frame is slot time (512 bits).

The max possible waiting time should be the max packet memory size divided by lowest port speed, for example if 512MB is the max packet buffer size and 10Mb is the lowest speed, the 512M \* 8 bits \* 100ns = 409.6 seconds (8M slot time) is the max possible waiting time. The congestion factor is the max possible waiting time at current link load. The pause timer value is half of the max possible waiting time. If it is greater than the feasible max pause time, use all 1's in pause time value.

If the utilization of the public buffer of the switch drops below the lower threshold, a pause-frame with minimum frame interval of 0 will be sent to the linking ports the enable new frame transmission.

Under half duplex operation, if the buffer utilization of whole switch has exceeded the upper threshold and the permanent buffer has been used up, the port will perform back-pressure based flow control by sending a jam pattern on each incoming frame. If backpressure flow control of the port is not enable, the frame will be dropped. The flow control pause time is calculated by maintained the configuration of port speed of each port and the buffer size. With input of the free memory block count and congestion factor, it determines flow control on or off on an output port. If flow control is on, any new queue request from a input port to this output port will trigger a flow control frame sent to that request port by the output MAC that is notified by the packet flow control unit.

21

The flow control activity is triggered when the buffer utilization exceeds certain thresholds specified by the dedicated register FMFCT, Register- FMFCT is used to specify the upper and lower thresholds of reserved buffer slot for whole switch.

#### 3.1.4.4 SMI interface

The VT6516 communicates with the external 10/100M PHY and access the PHY register through MDC, MDIO

#### 3.1.4.5 Auto negotiation

The VT6516 communicates with the external 10/100M PHY and access the PHY register through MDC, MDIO

#### 3.1.5 Serial EEPROM interface

20

#### 4. FUNCTIONAL DESCRIPTION

#### 4.1 Packet Reception and Address recognition

When VT6516 received frames from network, the input control module will receive packet from input MAC module, then get the output port mask from forwarding table control module, request packet buffer from buffer control, write packet from input FIFO to packet buffer scheduled by scheduler module, queue packet to the output queue through queue control module. And update the forwarding table by the source address of the received good packet.

Usually the source MAC address will be learned and stored to forwarding table. If VLAN is configured by user, the frame tag type and VLAN ID will also be learned. The source MAC address bit 47~11 and VLAN ID will be record in the forwarding table entry indexed by source MAC address bit 10~0 or 14~0.

The on chip multicast forwarding configuration registers mainly are for well-known addresses which are listened by CPU. External multicast addresses are for dynamically assigned. Also some static Mac addresses/port mask registers can be configured by CPU, these addresses will also be checked before look up the forward table.

#### 4.2 Packet Forwarding and VLAN

The VT6516's queue control maintains all head and tail pointers for all output ports. Accept the request to queue and dequeue packets from input and output control.

Both queue and dequeue operations take only 1 SRAM access (3 words = 96 bits), because the tail node is stored in the internal register of the queue control

Usually, queue and dequeue operations to a specific output queue can be performed simultaneously. However, mutual exclusion is applied while only one node in this queue

Each port will maintain a packet counter, it increments when packet gets queued through the tail pointer, it decrements when packet de-queued through head pointer. The congestion factor is the queued packet count divided by port media speed. The congestion factor will be used for flow control and multicast, congestion factor should be roughly equal to the time it takes to transmit all the queued packets.

For multicast packet, based on congestion factor, the least congested output port will be queued first. The output control will queue the packet to next least congested output port when it is transmitted, the CPU port will always be last port to be transmitted if the corresponding CPU bit is set in the port mask.

The port speed will be used for cut through forwarding decision. If the packet length is 7ff, it implies the input control try to cut through, queue control will accept or reject by looking whether the input port speed is equal to the output port speed and the output don't have queued packets and any pending transmission. The faster output port (than input port speed) and CPU port is not able to cut through

Broadcast packet, multicast and look up miss packet will forward(multicast) to those ports which is configured by software, but default(dump switching hub) will be all ports(or all ports in that VLAN if VLAN is implemented) except CPU port. Broadcast, multicast packet will check the on chip broadcast forwarding configuration registers and multicast forwarding configuration registers first, if multicast address not match any of the multicast forwarding configuration registers then it will look up the external SRAM forwarding table.

When request transfer to or from SDRAM through scheduler, the input control need to derive each burst starting address to bank0 or bank1 information for scheduler to utilize SDRAM bandwidth efficiently. When input FIFO is filled to 12x64 or page boundary or end of frame, the input port control will request DRAM access to write packet. Input FIFO size is 64 bits by 24.

After receiving the grant of queueing (cut-through or store-and-forward), even the bad packet has to be forwarded.

While cut-through, the input control will request the grant of cut-through counter bus for passing the cut through packet count from input port to output port as the whole packet has received.

#### 4.2.1 Cross VLAN Server Port support

The VT6516 support Cross VLAN server port configuration, the following illation show the sample of server ports configuration by set the register of server port mask(14A0H~14A1H), and server ports only enable after the VLAN enabled. The multicast or broadcast frames received from one VLAN group will forward to any server ports and only forward to the ports with same VID.

#### 4.3 Network Management Features

#### Flow control

The flow control activity is triggered when the buffer utilization exceeds certain thresholds specified by the dedicated register XXXX, Register-XXXX is used to specify the upper and lower thresholds of reserved buffer slot for whole switch.

Under full-duplex mode operation, if the buffer utilization of whole switch has exceeded the upper threshold and the permanent buffer has been used up, a flow control with a predefined pause time value will be sent to the source port to stop the input traffic. If flow control mechanism is not enabled, the public buffer will exhausted so that the further incoming frames will be dropped.

Under half duplex operation, if the buffer utilization of whole switch has exceeded the upper threshold and the permanent buffer has been used up, the port will perform back-pressure based flow control by sending a jam pattern on each incoming frame. If backpressure flow control of the port is not enable, the frame will be dropped.

#### Sniffer port

The VT6516 support sniffer function for user to monitor the network traffic. The Sniffer port enable can be set for any individual port of sixteen ports. And each sniffer port can set to monitor the traffic coming from any others fifteen port(monitor port). Any packets sent to the monitor ports or transmitted out of monitor port will be forwarded to sniffer port.

#### Spanning tree support