# VT83C469

# PCMCIA Socket Controller

# DATA SHEET (Preliminary)

**DATE:** March 13, 1995

VIA TECHNOLOGIES, INC.

#### VIA VT83C469 PCMCIA SOCKET CONTROLLER

**DATE: MARCH 13, 1995**

#### **OVERVIEW**

The VIA VT83C469 is a highly integrated PC Card socket controller chip that implements the PCMCIA 2.0/JEIDA 4.1 specifications. The chip is register compatible with the INTEL 82365SL and supports two PC card sockets with a fully buffered PCMCIA interface. No external buffer is required between the ISA bus and PCMCIA bus. For systems requiring more than two sockets, the VT83C469 can be cascaded to support up to eight sockets without external logic. Under EEPROM IO resource data, the VT83C469 can support unlimited sockets under ISA Plug and Play mode

In addition, the VT83C469 offers a jumperless configuration mechanism which allows the system manufacturer to set up a configuration (CONFIG.SYS) driver for PC card setup.

#### **FEATURES**

- Single chip PCMCIA controller between ISA bus and PCMCIA bus

- Full ExCA implementation of two PCMCIA 2.0/JEIDA 4.1 PC Card sockets

- Register-compatible with INTEL 82365SL

- Supports memory cards, I/O cards and DMA cards

- Supports PCMCIA-ATA disk interface

- 8 or 16-bit CPU interface

- 8 or 16-bit PCMCIA interface support

- High integration without any external logic or buffers

- Five mappable memory windows and two I/O windows for each socket

- Pin to Pin compatibility with Vadem VG-468

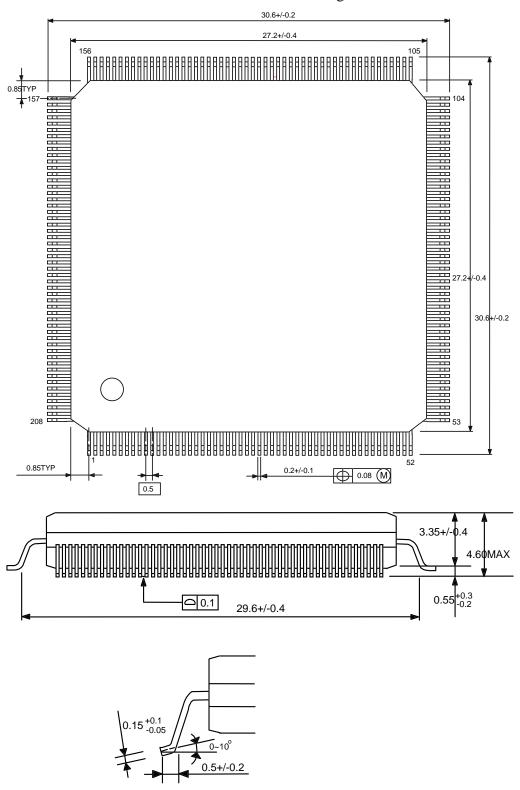

- 208 PQFP/Two sockets support

- Plug and Play ISA specifications version 1.0 with EEPROM

- Supports dynamic relocation of address space to avoid conflicts with system resources.

- Supports multiple PCMCIA controllers

- Features easy interface and design for docking stations

- Mixed voltage operation

- Support 3.3v or 5v PCMCIA socket interface

- Support PC card DMA operation

- Dual configuration for drive bay: socket controller can be located either on motherboard/ISA plug-in board or in the drive bay housing

- Support up to 8 sockets without external decoding

#### **ARCHITECTURAL OVERVIEW**

The VT83C469 functional blocks include the PCMCIA/JEIDA PC Card socket interface, ISA interface, memory and I/O window mapping, socket power management, interrupt steering, configuration registers and ATA mode operation.

#### PCMCIA/JEIDA PC Card Socket Interface

The PCMCIA/JEIDA interface consists of 60 signals and 8 power connections that interfaces to PC Cards through a 68 pin socket. A single VT83C469 can be configured to support either one or two sockets. Up to eight PC Card sockets may be supported by cascading VT83C469 chips. This chip supports memory, I/O and ATA card interchangeably.

#### **ISA Interface**

The VT83C469 interfaces directly to the ISA bus. No external buffers or transceivers are needed. For systems based on the 386SL, this chip provides the special signals INTR, RIO#, PWRGOOD, HDREQ, HDACK#, HTC, DREQ#, DACK, TC#, HBUFDIR, LBUFDIR, D7BUFDIR, A\_5VDECT AND B\_5VDECT.

#### Memory and I/O Window Mapping

Multiple PC cards in a system could conflict if they try to utilize the same system memory and I/O space. The VT83C469 allows the drivers to map a memory card into up to five separate windows and an I/O card into two separate windows, thus avoiding system configuration conflicts.

The VT83C469 provides memory paging, memory address mapping for PC card attribute and common memory, and I/O address mapping. The VT83C469 includes registers which provide access to the card information structure and card configuration registers within PC card's attribute memory (as described by the PCMCIA/JEIDA PC Card Standard).

#### Power Management for Socket Side and Core

At power on, if there is no card plugged into any socket, power to the socket is turned off. When a card is inserted, one of two events occur. If the chip has been set for automatic power on, then the VT83C469 automatically enables the power to socket. If the VT83C469 has been configured to cause management interrupts for card detection events, a management interrupt is generated to inform driver of the fact that a card was installed. Software driver can then initialize the card, or in the case of manual power detection, power the socket up manually and then initialize it. When a card is removed from a socket, and if the VT83C469 has been configured for automatic power on, the VT83C469 automatically disables VCC and VPP supplies to the socket.

#### **Interrupt Steering**

The VT83C469 steers the interrupt from the PC card to one of ten system interrupts. Multiple PC cards in a system can conflict if they try to utilize the same interrupt level. The VT83C469 can be programmed to eliminate this conflict by steering each PC card interrupt request to a different system interrupt.

#### **Configuration Registers**

The VT83C469 provides a register containing interface identity and version information for each socket.

#### **ATA Mode Operation**

The VT83C469 supports direct connection to AT attached interface hard drives. ATA drives use an interface that is very similar to the IDE interface found on many popular portable computers. In this mode, the address and data conflict with the floppy drive is handled automatically.

#### **Chip Mode Selection and Power-On Strapping**

The VT83C469 can be set to four different modes: PCMCIA B Socket bus mode, ISA bus mode, normal mode and Plug and Play mode. In the normal mode (under VG-468 pin definition), no advanced features of the VT83C469 such as Plug and Play, DMA and 3.3/5V sockets power supports are available. The ISA bus mode and the PCMCIA B socket mode allows for add-on applications to control the data buffer's (ie. 74245) direction control. The Plug and Play mode changes these pins to EEPROM for Plug and Play resource data support.

#### **Mode Configuration**

| HDACK# (PIN 67) | HTC (PIN 68) | Mode                   |  |

|-----------------|--------------|------------------------|--|

| Pull up         | Pull up      | normal mode            |  |

| Pull up         | Pull down    | ISA bus buffer mode    |  |

| Pull down       | Pull up      | PCMCIA bus buffer mode |  |

| Pull down       | Pull down    | PnP mode               |  |

#### Buffered bus direction support and PnP mode

| PINS | PCMCIA B        | ISA BUS MODE | NORMAL MODE   | PnP   |

|------|-----------------|--------------|---------------|-------|

|      | SOCKET BUS MODE |              | (VG-468 MODE) | MODE  |

| 136  | SHBUFDIR        | HHBUFDIR     | IRQ15         | E2CS  |

| 152  | SLBUFDIR        | HLBUFDIR     | INTR#         | E2SK  |

| 153  |                 | D7BUFDIR     | SPKROUT       | E2DIO |

Note:

SHBUFDIR Socket Data high byte direction SLBUFDIR Socket Data low byte direction HHBUFDIR ISA Data high byte direction HLBUFDIR ISA Data high byte direction

#### PC Card interface I/O Register Addressing

The VT83C469 registers are accessed through an 8-bit indexing mechanism. Two I/O addresses are used to access the VT83C469 registers. The first I/O address is the index register, which is fixed at 3E0h or 3E2h. The second I/O address is the data register, which is fixed at 3E1h or 3E3h. During PnP mode, the contents of the EEPROM resource data will determine whether the IO base will be set by the PnP BIOS or PnP utility. Each VT83C469 contains a block of 64 indirectly access registers. The starting base of the index register values in each VT83C469 is selected by pull-up/pull-down strapping resistor on INTR# and SPKROUT# pin, according to the table below. While RESETDRV is true, this pin is used for input. The falling edge of RESETDRV latches the pull up or down state of this pin, and thereafter this pin is used for normal operation. The VT83C469 will not respond to a data register read or write operation or to an index register read operation unless the index register has first been written to with a valid index.

| INTR#     | SPKROUT# RESISTOR | BASE | INDEX | DATA |

|-----------|-------------------|------|-------|------|

| Pull up   | Pull up           | 00h  | 3E0h  | 3E1h |

| Pull up   | Pull down         | 80h  | 3E0h  | 3E1h |

| Pull down | Pull up           | 00h  | 3E2h  | 3E3h |

| Pull down | Pull down         | 80h  | 3E2h  | 3E3h |

#### Memory and I/O Mapping

The VT83C469 provides logic to map portions of the 64MB common memory and/or 64MB attribute memory spaces on the PC Card into the smaller 16MB (ISA) system address space. The VT83C469 mapping function provides extension of the system address space up to the full 64MB PC Card capability.

Start and stop addresses are specified with ISA address bits 23 through 12. This sets the minimum size of a memory window into 4KB. Memory windows are specified in the ISA address from 64K to 16MB. Note that no memory window can be mapped in the first 64K of the ISA address space. Only I/O address windows are allowed to be mapped between 0 and 64KB in the ISA address space.

PC Card memory is accessed only when all of the following conditions are satisfied:

- 1. The system memory address mapping window is enabled.

- 2. The system memory address is greater than or equal to the system memory address mapping start register A23:A12.

- 3. The system memory address is less than or equal to the system memory address mapping stop register A23:A12...

An I/O PC Card is accessed when the following conditions are satisfied:

- 1. The I/O address window is enabled.

- 2. The system address is greater than or equal to the I/O address start register A15:A0.

- 3. The system address is less than or equal to the I/O address stop register A15:A0

- 4. The access is not a DMA transfer. AEN = 0 to access the I/O PC Card.

#### **Mixed Voltage Operation**

The VT83C469 has three power planes: the ISA bus interface, socket A interface and socket B interface. The ISA bus power planes connect to the core power plane and supports 5v operation. Socket A and socket B power planes each can be independently connected to 3v or 5v. The two voltage detect pins are: A\_5VDECT and B\_5VDECT.

| Pins | VT83C469 PIN DEFINITION | VG-468 PIN<br>DEFINITION |

|------|-------------------------|--------------------------|

| 191  | A_5VDet                 | Vcc                      |

| 141  | B_5VDet                 | Vcc                      |

| 27   | A_3Ven                  | GND                      |

| 101  | B_3Ven                  | GND                      |

In a mixed voltage implementation, the socket will not be powered unless there is a card in the socket. After the card is inserted, the system reads the voltage sensor pins and allows the CIS to determine the voltage to be applied to the card. Then it writes to the POWER control register, bit 4, which enables the outputs to the voltage switch.

#### **Plug and Play**

The VT83C469 supports the Plug and Play 1.0 specifications which provides automatic configuration capability. This feature allows the Plug and Play BIOS or Operating System (i.e. Windows 95) to relocate the VT83C469 register from the default to 3E0h/3E1h, 3E2h/3E3h or any other I/O address from the EEPROM containing the I/O resource.

When Plug and Play is enabled, the drive bay buffer mode cannot be enabled and the INTR# output cannot be used. In order to enable Plug and Play mode, the following register strapping must be used: pull down HDACK# and pull down HTC.

Three 8 bit ports are used by the software to access the Plug and Play configuration space. The ports are listed in the following table:

| PORT NAME  | LOCATION    | LOCATION   |

|------------|-------------|------------|

| Address    | 279Н        | Write only |

| Write_data | А79Н        | Write only |

| Read_data  | 200H ~ 3FFH | Read only  |

#### **Auto Configuration Registers**

PnP Register set

| ADD  | STD | DESCRIPTION               | DEF  | Type |

|------|-----|---------------------------|------|------|

| 0x00 | X   | SET READ_DATA PORT        | 0x00 | W    |

| 0x01 | X   | SERIAL ISOLATION          | 0x00 | R    |

| 0x02 | X   | CONFIGURE CONTROL         | 0x00 | W    |

| 0x03 | X   | WAKE CSN                  | 0x00 | W    |

| 0x04 | X   | RESOURCE DATA             | 0x00 | R/W  |

| 0x05 | X   | STATUS                    | 0x00 | R    |

| 0x06 | X   | CARD SELECT NUMBER        | 0x00 | R/W  |

| 0x07 | X   | LOGICAL DEVICE NUMBER     | 0x00 | R    |

| 0x30 | X   | ACTIVES                   | 0x00 | W    |

| 0x31 | X   | I/O RANGE CHECK           | 0x00 | R/W  |

| 0x60 | X   | I/O BASE ADDRESS 0 [15:8] | 0x00 | R/W  |

| 0x61 | X   | I/O BASE ADDRESS 0 [7:0]  | 0x00 | R/W  |

#### **PC Card DMA Operations**

The VT83C469 supports the use of a PC card as an interface with a DMA device. The VT83C469 defines an extension to the I/O card definition that allows ISA compatible DMA operation, including the Terminal Count signal required by the standard ISA floppy disk controller.

Only one socket at a time should be enabled for DMA transfer because the ISA bus DMA handshake is shared between both socket interfaces. Note: the original VG-468 pins 67 and 68 are defined as GPIO. The VT83C469 defines these pins as HDACK# and HTC.

The PCMCIA interface signals are redefined as the DMA interface signals according to the following table:

| DMA MODE SOCKET SIDE SIGNAL |                                         |       |  |

|-----------------------------|-----------------------------------------|-------|--|

| Pin                         | DEFAULT PIN ALTERNATE PIN FUNC FUNCTION |       |  |

| 61,132                      | IOIS16#                                 | DREQ# |  |

| 54,125                      | SPKR#                                   | DREQ# |  |

| 49,120                      | INPACK#                                 | DREQ# |  |

| 1,72                        | REG#                                    | DACK  |  |

| 16,87                       | OE#                                     | TC#   |  |

| 30,100                      | WE#                                     | TC#   |  |

#### **Register Set**

The following is a list of VT83C469 registers and their offset values. The General Registers, Interrupt Registers, I/O Registers and Memory Registers are fully compatible with the Intel 82365SL. The other registers are unique to the VT83C469.

| SOCKET A OFFSET | SOCKET B OFFSET | REGISTER NAME                                   |

|-----------------|-----------------|-------------------------------------------------|

| 00h             | 40h             | Identification and Revision                     |

| 01h             | 41h             | Interface Status                                |

| 02h             | 42h             | Power Control                                   |

| 03h             | 43h             | Interrupt and General Control                   |

| 04h             | 44h             | Card Status Change                              |

| 05h             | 45h             | Card Status Change Interrupt Configuration      |

| 06h             | 46h             | Address Window Enable                           |

| 07h             | 47h             | I/O Control                                     |

| 08h             | 48h             | I/O Address 0 Start Low Byte                    |

| 09h             | 49h             | I/O Address 0 Start High Byte                   |

| 0Ah             | 4Ah             | I/O Address 0 Stop Low Byte                     |

| 0Bh             | 4Bh             | I/O Address 0 Stop High Byte                    |

| 0Ch             | 4Ch             | I/O Address 1 Start Low Byte                    |

| 0Dh             | 4Dh             | I/O Address 1 Start High Byte                   |

| 0Eh             | 4Eh             | I/O Address 1 Stop Low Byte                     |

| 0Fh             | 4Fh             | I/O Address 1 Stop High Byte                    |

| 10h             | 50h             | System Memory Address 0 Mapping Start Low Byte  |

| 11h             | 51h             | System Memory Address 0 Mapping Start High Byte |

| 12h             | 52h             | System Memory Address 0 Mapping Stop Low Byte   |

| 13h             | 53h             | System Memory Address 0 Mapping Stop High Byte  |

| 14h             | 54h             | Card Memory Offset Address 0 Low Byte           |

| 15h             | 55h             | Card Memory Offset Address 0 High Byte          |

| 16h             | 56h             | Misc Control 1                                  |

| 17h             | 57h             | Reserved                                        |

| 18h             | 58h             | System Memory Address 1 Mapping Start Low Byte  |

| 19h             | 59h             | System Memory Address 1 Mapping Start High Byte |

| 1Ah             | 5Ah             | System Memory Address 1 Mapping Stop Low Byte   |

| 1Bh             | 5Bh             | System Memory Address 1 Mapping Stop High Byte  |

| 1Ch             | 5Ch             | Card Memory Offset Address 1 Low Byte           |

| 1Dh             | 5Dh             | Card Memory Offset Address 1 High Byte          |

| 1Eh             | 5Eh             | Misc Control 2                                  |

| 1Fh             | 5Fh             | Chip Information                                |

| 20h             | 60h             | System Memory Address 2 Mapping Start Low Byte  |

| 21h             | 61h             | System Memory Address 2 Mapping Start High Byte |

| 22h             | 62h             | System Memory Address 2 Mapping Stop Low Byte   |

| 23h             | 63h             | System Memory Address 2 Mapping Stop High Byte  |

| 24h             | 64h             | Card Memory Offset Address 2 Low Byte           |

| 25h             | 65h             | Card Memory Offset Address 2 High Byte          |

| 26h             | 66h             | ATA Mode Control                                |

| 27h             | 67h             | Reserved                                        |

| 28h             | 68h             | System Memory Address 3 Mapping Start Low Byte  |

| 29h             | 69h             | System Memory Address 3 Mapping Start High Byte |

| SOCKET A OFFSET | SOCKET B OFFSET | REGISTER NAME                                   |

|-----------------|-----------------|-------------------------------------------------|

| 2Ah             | 6Ah             | System Memory Address 3 Mapping Stop Low Byte   |

| 2Bh             | 6Bh             | System Memory Address 3 Mapping Stop High Byte  |

| 2Ch             | 6Ch             | Card Memory Offset Address 3 Low Byte           |

| 2Dh             | 6Dh             | Card Memory Offset Address 3 High Byte          |

| 2Eh             | 6Eh             | VIA ID                                          |

| 2Fh             | 6Fh             | DMA Control                                     |

| 30h             | 70h             | System Memory Address 4 Mapping Start Low Byte  |

| 31h             | 71h             | System Memory Address 4 Mapping Start High Byte |

| 32h             | 72h             | System Memory Address 4 Mapping Stop Low Byte   |

| 33h             | 73h             | System Memory Address 4 Mapping Stop High Byte  |

| 34h             | 74h             | Card Memory Offset Address 4 Low Byte           |

| 35h             | 75h             | Card Memory Offset Address 4 High Byte          |

| 36h             | 76h             | Reserved                                        |

| 37h             | 77h             | Reserved                                        |

| 38h             | 78h             | Reserved                                        |

| 39h             | 79h             | Reserved                                        |

| 3Ah             | 7Ah             | Reserved                                        |

| 3Bh             | 7Bh             | Reserved                                        |

| 3Ch             | 7Ch             | Reserved                                        |

| 3Dh             | 7Dh             | Reserved                                        |

| 3Eh             | 7Eh             | Reserved                                        |

| 3Fh             | 7Fh             | Reserved                                        |

## **CHIP CONTROL REGISTERS**

${\bf Identification\ and\ Revision\ Register\ (\ Read\ Only\ )}$

Address: Index ( Base + 00h )

| Віт    | Function                                                                                             |

|--------|------------------------------------------------------------------------------------------------------|

| D[7:6] | VT83C469 Interface Type                                                                              |

|        | Type of PC Card supported by the socket. These bits do not identify the type of card that is present |

|        | at the socket.                                                                                       |

|        | 00: I/O only.                                                                                        |

|        | 01: Memory only.                                                                                     |

|        | 10: Memory & I/O.                                                                                    |

|        | 11: Reserved.                                                                                        |

| D[5:4] | Reserved. These bits will be read back as zero.                                                      |

| D[3:0] | These four bits indicate the revision of the chip.                                                   |

|        | 0010 is compatible with Intel.                                                                       |

# Interface Status Register ( Read Only ) Address : Index ( Base + 01h )

| Function                                                                                                                                      |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Reserved                                                                                                                                      |  |  |

| PC Card Power Active                                                                                                                          |  |  |

| 0: Power to the socket is off ( Vcc and Vpp1 are no connection).                                                                              |  |  |

| 1: Power to the socket is on (Vcc is set according to bit 1 in Miscellaneous Control 1 register and                                           |  |  |

| DET_5 pin, Vpp1 is set according to bit 1:0 in the power control register).                                                                   |  |  |

| Ready/Busy#                                                                                                                                   |  |  |

| 0: PC Card is busy.                                                                                                                           |  |  |

| 1: PC Card is ready.                                                                                                                          |  |  |

| Memory Write Protect.                                                                                                                         |  |  |

| Bit value is the logic level of the WP signal on the memory PC Card interface.                                                                |  |  |

| 0: PC Card is not write protected.                                                                                                            |  |  |

| 1: PC Card is write protected.                                                                                                                |  |  |

| Card Detect 2                                                                                                                                 |  |  |

| Together with card detect 1 indicates a card is present at the socket and fully seated.                                                       |  |  |

| 0: CD2# signal on the PC Card interface is inactive.                                                                                          |  |  |

| 1: CD2# signal on the PC Cars interface is active.  Card Detect 1                                                                             |  |  |

|                                                                                                                                               |  |  |

| Together with card detect 2 indicates a card is present at the socket and fully seated.  0: CD1# signal on the PC Card interface is inactive. |  |  |

| 1: CD1# signal on the PC Card interface is inactive.  1: CD1# signal on the PC Cars interface is active.                                      |  |  |

| Battery Voltage Detect 2 and 1.                                                                                                               |  |  |

| BVD1 BVD2 Status                                                                                                                              |  |  |

| 0 0 battery dead                                                                                                                              |  |  |

| 0 1 battery dead                                                                                                                              |  |  |

| 1 0 warning                                                                                                                                   |  |  |

| 1 1 battery good                                                                                                                              |  |  |

| For I/O PC Cards, bit 0 indicates the current status of the (STSCHG/RI#) signal from the PC Card                                              |  |  |

| when the ring indicate enable bit in the Interrupt and General control register is set to 0.                                                  |  |  |

|                                                                                                                                               |  |  |

Power Control Register ( Read/Write )

Address: Index (Base + 02h)

| Віт    | Function                                                                                                                                                                                                                                                                         |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7     | Output Enable.  If this bit set to zero, the PC Card outputs listed below are tri-stated.  CADR<25:0>, D<15:0>, CE2#, CE1#, IORD#, IOWR#, OE#, WE#, REG#, RESET.  This bit should not be set until after this register has been written setting PC Card Power Enable previously. |

| D6     | Reserved.                                                                                                                                                                                                                                                                        |

| D5     | Auto Power Switch Enable.  0: automatic socket power switching based on card detects is disable.  1: automatic socket power switching based on card detects is enable.                                                                                                           |

| D4     | PC Card Power Enable.  0: power to the socket is disabled.  (Vcc and Vpp1 are all no connection)  1: power to the socket is enabled.  (Vcc is set according to bit 1 in Miscellaneous Control 1 register and DET_5 pin, and Vpp1 is set according to bit 1:0 in this register)   |

| D[3:2] | Reserved                                                                                                                                                                                                                                                                         |

| D[1:0] | Vpp1 Power Control 00: no connection. 01: Vcc. 10: 12V.                                                                                                                                                                                                                          |

|        | 11: reserved.(this setting then Vpp1 will be a no connection)                                                                                                                                                                                                                    |

The following table describes the slot power control function.

| Оитрит | PC<br>CARD<br>POWER<br>ENABLE | AUTO<br>POWER<br>SWITCH<br>ENABLE | CD1# | CD2# | TRI-STATE<br>OUTPUTS | PC<br>CARD<br>POWER<br>ACTIVE |

|--------|-------------------------------|-----------------------------------|------|------|----------------------|-------------------------------|

| X      | 0                             | X                                 | X    | X    | OFF                  | 0                             |

| 0      | 1                             | 0                                 | 0    | 0    | OFF                  | 1                             |

| 1      | 1                             | 0                                 | 0    | 0    | ON                   | 1                             |

| X      | 1                             | 0                                 | X    | 1    | OFF                  | 1                             |

| X      | 1                             | 0                                 | 1    | X    | OFF                  | 1                             |

| 0      | 1                             | 1                                 | 0    | 0    | OFF                  | 1                             |

| 1      | 1                             | 1                                 | 0    | 0    | ON                   | 1                             |

| X      | 1                             | 1                                 | X    | 1    | OFF                  | 0                             |

| X      | 1                             | 1                                 | 1    | X    | OFF                  | 0                             |

$\begin{array}{l} \textbf{Interrupt Register ( Read/Write )} \\ \textbf{Address} : Index ( Base + 03h ) \end{array}$

| Віт    | FUNCTION                                                                                          |

|--------|---------------------------------------------------------------------------------------------------|

| D7     | Ring Indicate Enable.                                                                             |

|        | 0: For I/O PC Card, the STSCHG/RI# signal from card is used as the status change signal           |

|        | STSCHG#. The current status of this signal is then available to be read from the interrupt status |

|        | register and this signal can be configured as a source for the card status change interrupt.      |

|        | 1: For I/O PC Card, the STSCHG/RI# signal from card is used as ring indicator signal and is       |

|        | passed through to the IRQ15(multi pin, set Misc Control 2 bit 7 to one is used as RI_OUT#). The   |

|        | ring indicate enable bit has no function when the PC Card type bit is set to zero ( memory card). |

| D6     | PC Card Reset                                                                                     |

|        | This is a software reset to PC Card.                                                              |

|        | 0: Activates the RESET to the PC Card. The RESET signal will be active until bit is set to one.   |

|        | 1: Deactivates the RESET signal to the PC Card.                                                   |

| D5     | PC Card Type.                                                                                     |

|        | 0: Memory PC Card.                                                                                |

|        | 1: I/O PC Card.                                                                                   |

| D4     | INTR# Enable.                                                                                     |

|        | 0: The INTR# does not indicate a card status change interrupt is steered to one of the IRQs lines |

|        | according to bit 7:4 in the card status change interrupt configuration register.                  |

|        | 1: Enable the card status change interrupt on the INTR# signal.                                   |

| D[3:0] | IRQ Level Selection ( I/O Cards Only ).                                                           |

|        | Refer to following table is the redirection of the PC Card interrupt according to these bits.     |

| IRQ BIT3 | IRQ BIT2 | IRQ BIT1 | IRQ BIT0 | INTERRUPT REQUEST LEVEL |

|----------|----------|----------|----------|-------------------------|

| 0        | 0        | 0        | 0        | IRQ not select          |

| 0        | 0        | 0        | 1        | Reserved                |

| 0        | 0        | 1        | 0        | Reserved                |

| 0        | 0        | 1        | 1        | IRQ3 enable             |

| 0        | 1        | 0        | 0        | IRQ4 enable             |

| 0        | 1        | 0        | 1        | IRQ5 enable             |

| 0        | 1        | 1        | 0        | Reserved                |

| 0        | 1        | 1        | 1        | IRQ7 enable             |

| 1        | 0        | 0        | 0        | Reserved                |

| 1        | 0        | 0        | 1        | IRQ9 enable             |

| 1        | 0        | 1        | 0        | IRQ10 enable            |

| 1        | 0        | 1        | 1        | IRQ11 enable            |

| 1        | 1        | 0        | 0        | IRQ12 enable            |

| 1        | 1        | 0        | 1        | Reserved                |

| 1        | 1        | 1        | 0        | IRQ14 enable            |

| 1        | 1        | 1        | 1        | IRQ15 enable            |

#### Card Status Change Register ( Read Only )

Address: Index (Base + 04h)

| Віт    | FUNCTION                                                                                             |

|--------|------------------------------------------------------------------------------------------------------|

| D[7:4] | R. 0000                                                                                              |

| D3     | Card Detect Change.                                                                                  |

|        | 0: No change detected on either CD2# or CD1#.                                                        |

|        | 1: A change has been detected on CD2# and CD1#.                                                      |

| D2     | Ready Change.                                                                                        |

|        | 0: No change on RDY/BSY#, or I/O PC Card installed.                                                  |

|        | 1: When a low to high has been detected on the RDY/BSY# signal indicating that the memory PC         |

|        | Card is ready to accept a new data transfer.                                                         |

| D1     | Battery Warning.                                                                                     |

|        | 0: No battery warning condition, or I/O PC Card installed.                                           |

|        | 1: A battery warning condition has been detected.                                                    |

| D0     | Battery Dead ( STSCHG# )                                                                             |

|        | For memory PC Cards, bit is set one when a battery dead condition has been detected.                 |

|        | For I/O PC Cards, bit is set to one if ring indicate enable bit in the interrupt and general control |

|        | register is set to zero and the STSCHG/RI# signal from the I/O PC Card has been pulled low. The      |

|        | system software then has to read the status change register in the PC Card to determine the cause of |

|        | the status change signal STSCHG#. This bit reads zero for I/O PC Cards if the ring indicate enable   |

|        | bit in the interrupt and general control register is set to one.                                     |

NOTE: The Card Status Change Register contains the status for sources of the card status change interrupt. These sources can be enabled to generate a card status change interrupt by setting the corresponding bit in the card status change interrupt configuration register. Reading the Card Status Change Register causes the register bits to be reset to zero.

If the card status change interrupt is enabled to one of the system bus interrupt request lines, the corresponding IRQ signal remains active high until this register is read.

#### $Card\ Status\ Change\ Interrupt\ Configuration\ Register\ (\ Read/Write\ )$

Address: Index (Base + 05h)

| Віт    | FUNCTION                                                                                                                                                          |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:4] | Interrupt Steering for the Card Status Change Interrupt.  These bits select the redirection of the card status change interrupt if the interrupt is not select to |

|        | the output on the INTR# pin.                                                                                                                                      |

| D3     | Card Detect Enable.                                                                                                                                               |

|        | 0: Disables the generation of a card status change interrupt when the card detect signals changed.                                                                |

|        | 1: Enables a card status change interrupt when a change has been detected on CD2# or CD1#.                                                                        |

| D2     | Ready Enable ( Memory Card Only ).                                                                                                                                |

|        | 0: Disables the generation of a card status change interrupt when a low to high transition has been detected on the RDY/BSY# signal.                              |

|        | 1: Enables a card status change interrupt when a low to high transition has been detected on the RDY/BSY# pin.                                                    |

| D1     | Battery Warning Enable ( Memory Card Only ).                                                                                                                      |

|        | 0: Disables the generation of a card status change interrupt when a battery warning condition has been detected.                                                  |

|        | 1: Enables a card status change interrupt when a battery warning condition has been detected.                                                                     |

| D0     | Battery Dead Enable ( STSCHG# ).                                                                                                                                  |

|        | 0: Disables the generation of a card status change interrupt when a battery dead condition has                                                                    |

|        | been detected. ( Memory PC Cards used ). For I/O PC Cards, bit is ignored when a Ring                                                                             |

|        | Indicate Enable bit is set one.                                                                                                                                   |

|        | 1: For memory PC Cards, enables a card status change interrupt when a battery dead condition                                                                      |

|        | has been detected.                                                                                                                                                |

|        | For I/O PC Cards, enables the VT83C469 to generate a card status change interrupt if the                                                                          |

|        | STSCHG# signal has been pulled low by the I/O PC Card, assuming that the Ring Indicate                                                                            |

|        | Enable bit is set zero.                                                                                                                                           |

| INTR<br>ENABLE | IRQ BIT3 | IRQ BIT2 | IRQ BIT1 | IRQ BIT0 | INTERRUPT REQUEST LEVEL               |

|----------------|----------|----------|----------|----------|---------------------------------------|

| 0              | 0        | 0        | 0        | 0        | IRQ not select                        |

| 0              | 0        | 0        | 0        | 1        | Reserved                              |

| 0              | 0        | 0        | 1        | 0        | Reserved                              |

| 0              | 0        | 0        | 1        | 1        | IRQ3 enable                           |

| 0              | 0        | 1        | 0        | 0        | IRQ4 enable                           |

| 0              | 0        | 1        | 0        | 1        | IRQ5 enable                           |

| 0              | 0        | 1        | 1        | 0        | Reserved                              |

| 0              | 0        | 1        | 1        | 1        | IRQ7 enable                           |

| 0              | 1        | 0        | 0        | 0        | Reserved                              |

| 0              | 1        | 0        | 0        | 1        | IRQ9 enable                           |

| 0              | 1        | 0        | 1        | 0        | IRQ10 enable                          |

| 0              | 1        | 0        | 1        | 1        | IRQ11 enable                          |

| 0              | 1        | 1        | 0        | 0        | IRQ12 enable                          |

| 0              | 1        | 1        | 0        | 1        | Reserved                              |

| 0              | 1        | 1        | 1        | 0        | IRQ14 enable                          |

| 0              | 1        | 1        | 1        | 1        | IRQ15 enable                          |

| 1              | X        | X        | X        | X        | Card Status Change Interrupt on INTR# |

${\bf Address\ Window\ Enable\ Register\ (\ Read/Write\ )}$

Address: Index ( Base + 06h )

| Віт    | FUNCTION                                                                                      |

|--------|-----------------------------------------------------------------------------------------------|

| D[7:6] | I/O Window Enable [1:0].                                                                      |

|        | 0: Inhibit the card enable signals to the PC Card when an I/O access occurs within the        |

|        | corresponding I/O address window.                                                             |

|        | 1: Generate the card enable signals to PC card when an I/O access occurs within the           |

|        | corresponding I/O address window. I/O accesses pass addresses from the system bus directly    |

|        | through to the PC Card.                                                                       |

|        | The start and stop register pairs must all be set to the desired window values before setting |

|        | this bit to one.                                                                              |

| D5     | MS16# Decode A23:12.                                                                          |

|        | 0: Generated MS16# from a decode of the system address lines A23:17 only. This means that a   |

|        | minimum, a 128K block of system memory address space is set aside as 16-bit memory only.      |

| 7.4    | 1: Generated MS16# from a decode of the system address lines A23:12.                          |

| D4     | Memory Window 4 Enable.                                                                       |

|        | 0: Inhibit the card enable signals to the PC Card when a memory access occurs within the      |

|        | corresponding system memory address window.                                                   |

|        | 1: Generate the card enable signals when a memory access occurs within the corresponding      |

|        | system memory address window. When the system address is within the window, the computed      |

| D3     | address will be generated to the PC Card.  Memory Window 3 Enable.                            |

| D3     | 0: Inhibit the card enable signals to the PC Card when a memory access occurs within the      |

|        | corresponding system memory address window.                                                   |

|        | 1: Generate the card enable signals when a memory access occurs within the corresponding      |

|        | system memory address window. When the system address is within the window, the computed      |

|        | address will be generated to the PC Card.                                                     |

| D2     | Memory Window 2 Enable.                                                                       |

|        | 0: Inhibit the card enable signals to the PC Card when a memory access occurs within the      |

|        | corresponding system memory address window.                                                   |

|        | 1: Generate the card enable signals when a memory access occurs within the corresponding      |

|        | system memory address window. When the system address is within the window, the computed      |

|        | address will be generated to the PC Card.                                                     |

| D1     | Memory Window 1 Enable.                                                                       |

|        | 0: Inhibit the card enable signals to the PC Card when a memory access occurs within the      |

|        | corresponding system memory address window.                                                   |

|        | 1: Generate the card enable signals when a memory access occurs within the corresponding      |

|        | system memory address window. When the system address is within the window, the computed      |

|        | address will be generated to the PC Card.                                                     |

| D0     | Memory Window 0 Enable.                                                                       |

|        | 0: Inhibit the card enable signals to the PC Card when a memory access occurs within the      |

|        | corresponding system memory address window.                                                   |

|        | 1: Generate the card enable signals when a memory access occurs within the corresponding      |

|        | system memory address window. When the system address is within the window, the computed      |

|        | address will be generated to the PC Card.                                                     |

|        | NOTE: The start, stop and offset registers pairs must all be set to the desired window values |

|        | before setting bit to one.( All Memory Windows ).                                             |

#### I/O Control Register ( Read/Write )

Address: Index (Base + 07h)

| Віт | FUNCTION                                                                                  |

|-----|-------------------------------------------------------------------------------------------|

| D7  | I/O Window 1 Wait State.                                                                  |

|     | 0: 16-bit system accesses occur with no additional wait state.                            |

|     | 1: 16-bit system accesses occur with one additional wait state( 4 BUSCLKs ).              |

| D6  | I/O Window 1 zero wait state.                                                             |

|     | 0: 8-bit system I/O access will occur with additional wait state.                         |

|     | 1: 8-bit system I/O access will occur with no additional wait state and the NOWS# will be |

|     | returned to the system bus.                                                               |

| D5  | I/O Window 1 IOCS16# Source.                                                              |

|     | 0: IOCS16# is generated based on the value of the data size bit.                          |

|     | 1: IOCS16# is generated based on the IOIS16# signal from PC Card.                         |

| D4  | I/O Window 1 Data Size.                                                                   |

|     | 0: 8-bit I/O data path to PC Card.                                                        |

|     | 1: 16-bit I/O data path to PC Card.                                                       |

| D3  | I/O Window 0 Wait State.                                                                  |

|     | 0: 16-bit system accesses occur with no additional wait state.                            |

|     | 1: 16-bit system accesses occur with one additional wait state( 4 BUSCLKs ).              |

| D2  | I/O Window 0 zero wait state.                                                             |

|     | 0: 8-bit system I/O access will occur with additional wait state.                         |

|     | 1: 8-bit system I/O access will occur with no additional wait state and the NOWS# will be |

|     | returned to the system bus.                                                               |

| D1  | I/O Window 0 IOCS16# Source.                                                              |

|     | 0: IOCS16# is generated based on the value of the data size bit.                          |

|     | 1: IOCS16# is generated based on the IOIS16# signal from PC Card.                         |

| D0  | I/O Window 0 Data Size.                                                                   |

|     | 0: 8-bit I/O data path to PC Card.                                                        |

|     | 1: 16-bit I/O data path to PC Card.                                                       |

#### I/O Address Start Register Low Byte ( Read/Write )

Address: Window 0 Index (Base + 08h) Address: Window 1 Index (Base + 0Ch)

| Віт    | Function                                                                                    |

|--------|---------------------------------------------------------------------------------------------|

| D[7:0] | I/O Window Start Address A[7:0]                                                             |

|        | Low order address bits used to determine the start address of the corresponding I/O address |

|        | window. This provides a minimum 1 byte window for I/O address window.                       |

#### I/O Address Start Register High Byte ( Read/Write )

Address: Window 0 Index (Base + 09h) Address: Window 1 Index (Base + 0Dh)

| Віт    | FUNCTION                                                                                                                              |

|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | I/O Window Start Address A[15:8] High order address bits used to determine the start address of the corresponding I/O address window. |

I/O Address Stop Register Low Byte ( Read/Write )

**Address**: Window 0 Index (Base + 0Ah) **Address**: Window 1 Index (Base + 0Eh)

| Віт    | FUNCTION                                                                                   |

|--------|--------------------------------------------------------------------------------------------|

| D[7:0] | I/O Window Stop Address A[7:0]                                                             |

|        | Low order address bits used to determine the stop address of the corresponding I/O address |

|        | window. This provides a minimum 1 byte window for I/O address window.                      |

#### I/O Address Stop Register High Byte (Read/Write)

Address: Window 0 Index (Base + 0Bh) Address: Window 1 Index (Base + 0Fh)

| Віт    | FUNCTION                                                                                                                            |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D[7:0] | I/O Window Stop Address A[15:8] High order address bits used to determine the stop address of the corresponding I/O address window. |  |  |

#### System Memory Address Mapping Start Low Byte Register (Read/Write)

Address: Window 0 Index (Base + 10h) Address: Window 1 Index (Base + 18h) Address: Window 2 Index (Base + 20h) Address: Window 3 Index (Base + 28h) Address: Window 4 Index (Base + 30h)

| Віт    | FUNCTION                                                                                                                                                                                                                                      |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | System Memory Window Start Address A[19:12]  Low order address bits used to determine the start address of the corresponding system memory address mapping window. This provides a minimum 4K bytes window for memory address mapping window. |

#### System Memory Address Mapping Stop High Byte Register ( Read/Write )

Address: Window 0 Index (Base + 11h) Address: Window 1 Index (Base + 19h) Address: Window 2 Index (Base + 21h) Address: Window 3 Index (Base + 29h) Address: Window 4 Index (Base + 31h)

| Віт    | FUNCTION                                                                                       |

|--------|------------------------------------------------------------------------------------------------|

| D7     | Data Size.                                                                                     |

|        | 0: 8-bit memory data path to the PC Card.                                                      |

|        | 1: 16-bit memory data path to the PC Card.                                                     |

| D6     | Zero Wait State.                                                                               |

|        | 0: System memory access will occur with additional wait states.                                |

|        | 1: System memory access will occur with no additional wait states and the NOWS# signal will be |

|        | returned to the system bus. The WAIT# signal from PC Card will override this bit.              |

| D[5:4] | R/W. 00                                                                                        |

| D[3:0] | System Memory Window Start Address A23:20.                                                     |

|        | High order address bits used to determine the start address of the corresponding system memory |

|        | address mapping window.                                                                        |

#### System Memory Address Mapping Stop Low Byte Register (Read/Write)

```

Address: Window 0 Index (Base + 12h)

Address: Window 1 Index (Base + 1Ah)

Address: Window 2 Index (Base + 22h)

Address: Window 3 Index (Base + 2Ah)

Address: Window 4 Index (Base + 32h)

```

| Віт    | FUNCTION                                                                                                                                                                                                                                    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | System Memory Window Stop Address A[19:12]  Low order address bits used to determine the stop address of the corresponding system memory address mapping window. This provides a minimum 4K bytes window for memory address mapping window. |

#### System Memory Address Mapping Start High Byte Register (Read/Write)

```

Address: Window 0 Index (Base + 13h)

Address: Window 1 Index (Base + 1Bh)

Address: Window 2 Index (Base + 23h)

Address: Window 3 Index (Base + 2Bh)

Address: Window 4 Index (Base + 33h)

```

| Віт    | FUNCTION                                                                                           |

|--------|----------------------------------------------------------------------------------------------------|

| D[7:6] | Wait State bit 1:0.                                                                                |

|        | These bits determine the number of additional wait states for a 16-bit access to the system memory |

|        | window. If the PC Card supports the WAIT# signal, wait states will be generated by the PC Card     |

|        | asserting the WAIT# signal.                                                                        |

|        | 00: standard 16-bit cycle (3 BUSCLKs per access)                                                   |

|        | 01: 1 additional wait state (4 BUSCLKs per access)                                                 |

|        | 10: 2 additional wait states ( 5 BUSCLKs per access )                                              |

|        | 11: 3 additional wait states ( 6 BUSCLKs per access )                                              |

| D[5:4] | R/W. 00                                                                                            |

| D[3:0] | System Memory Window Stop Address A23:20.                                                          |

|        | High order address bits used to determine the stop address of the corresponding system memory      |

|        | window.                                                                                            |

#### System Memory Address Mapping Offset Low Byte Register (Read/Write)

```

Address: Window 0 Index (Base + 14h)

Address: Window 1 Index (Base + 1Ch)

Address: Window 2 Index (Base + 24h)

Address: Window 3 Index (Base + 2Ch)

Address: Window 4 Index (Base + 34h)

```

| Віт    | FUNCTION                                                                                       |

|--------|------------------------------------------------------------------------------------------------|

| D[7:0] | System Memory Window Offset Address A[19:12]                                                   |

|        | Low order address bits which added to the system address bits A19:12 to generate card address. |

System Memory Address Mapping Offset High Byte Register ( Read/Write )

Address: Window 0 Index (Base + 15h) Address: Window 1 Index (Base + 1Dh) Address: Window 2 Index (Base + 25h) Address: Window 3 Index (Base + 2Dh) Address: Window 4 Index (Base + 35h)

| Віт    | FUNCTION                                                                                       |

|--------|------------------------------------------------------------------------------------------------|

| D7     | Write Protect.                                                                                 |

|        | 0: Write operations to PC Card through the corresponding system memory window are allowed.     |

|        | 1: Write operations to PC Card through the corresponding system memory window are inhibited.   |

| D6     | REG Active.                                                                                    |

|        | 0: Access to the system memory will result in common memory space.                             |

|        | 1: Access to the system memory will result in attribute memory space.                          |

| D[5:0] | Card Memory Offset Address A25:20.                                                             |

|        | High order address bits which are added to the system address A23:20 to generate card address. |

#### **EXTENSION REGISTERS**

Misc. Control 1 Register ( Read/Write )

**Address**: Index (Base + 16h)

| Віт    | FUNCTION                                                                                                          |

|--------|-------------------------------------------------------------------------------------------------------------------|

| D7     | Inpack Support.                                                                                                   |

|        | 0: Inpack not support.                                                                                            |

|        | 1: Inpack used to control data bus drivers during I/O read from the PC Card.                                      |

| D[6:5] | Reserved                                                                                                          |

| D4     | Speaker Enable.                                                                                                   |

|        | 0: SPKCSEL# is tri-state.                                                                                         |

|        | 1: SPKCSEL# is driven form the XOR of SPKR# from each enabled PC Card.                                            |

| D[3:2] | Reserved                                                                                                          |

| D1     | $V_{CC}$ 3v. This bit dtermines which output pin is to be used to enable $V_{CC}$ power to be the socket          |

|        | when card power is to be applied. It is used in conjunction with bits 5-4 of the Power Control                    |

|        | register. When this bit is "1," the 3.3v V <sub>CC</sub> is applied to the PC card. When this bit is "0," 3.3v or |

|        | 5v V <sub>CC</sub> is determined by the DET_5 pin.                                                                |

| D0     | This bit is connected to PCMCIA pin 43. Cards that will operate at 3.3v will drive this pin to a "0."             |

$Misc.\ Control\ 2\ Register\ (\ Read/Write\ )$

Address: Index (Base + 1Eh)

| Віт    | FUNCTION                                                                                     |

|--------|----------------------------------------------------------------------------------------------|

| D7     | RIOLED is RI Out.                                                                            |

|        | This bit determines the function of the RIOLED. When configured for ring indicate, RIOLED is |

|        | used to resume the 386SL when a high to low change is detected on the STSCHG#.               |

|        | 0: Tri-state RIOLED if RIOLED is not used as LED output                                      |

|        | 1: RIOLED is connected to Ring Indicate on the processor.                                    |

| D6     | R/W. 0                                                                                       |

| D5     | Tri-state SD7 bit.                                                                           |

|        | This bit enables floppy change bit compatibility.                                            |

|        | 0: Normal operation.                                                                         |

|        | 1: For I/O PC Card at address 03F7h and 0377h, do not drive SD7 bit.                         |

| D4     | Drive LED Enable.                                                                            |

|        | This bit determines when SPKR# is used to drive an LED on RIOLED for disk access.            |

|        | 0: Tri-state RIOLED if RIOLED is not used as RI out.                                         |

|        | 1: RIOLED becomes an open drain output suitable for driving an LED.                          |

| D[3:0] | R/W. 0000                                                                                    |

#### Compatible Chip Information with Cirrus Logic CL-6722 Register ( Read/Write )

Address: Index (Base + 1Fh)

| Віт    | FUNCTION                                                                                       |

|--------|------------------------------------------------------------------------------------------------|

| D[7:6] | Chip Identification. ( Read Only )                                                             |

|        | This field identifies the VT83C469 device and compatible with Cirrus Logic CL-6722 device. For |

|        | the first read of this register this field will be 11h; on the next read will be 00h.          |

| D5     | Dual/Single Socket. ( Read Only )                                                              |

|        | This bit will be 1b, because the VT83C469 is support two sockets.                              |

| D[4:2] | VT83C469 Revision. ( Read Only )                                                               |

|        | This field identifies the revision of this controller. It's initial value is 110h.             |

| D[1:0] | R/W. 00                                                                                        |

# ATA Mode Control Register ( Read/Write )

Address: Index (Base + 26h)

| Віт | Function                                                                                                                                                                                                                                                                                     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | A25/CSEL. In ATA mode, this bit is applied to the ATA A25/CSEL and is vendor specific. Certain ATA drive vendor specific performance enhancements beyond the PCMCIA 2.0 standard may be controlled through use of this bit. This bit has no hardware control function when not in ATA mode.  |

| D6  | A24/M/S#.  In ATA mode, this bit is applied to the ATA A24/M/S# and is vendor specific. Certain ATA drive vendor specific performance enhancements beyond the PCMCIA 2.0 standard may be controlled through use of this bit. This bit has no hardware control function when not in ATA mode. |

| D5  | A23/VU.  In ATA mode, this bit is applied to the ATA A23/VU and is vendor specific. Certain ATA drive vendor specific performance enhancements beyond the PCMCIA 2.0 standard may be controlled through use of this bit. This bit has no hardware control function when not in ATA mode.     |

| D4  | A22. In ATA mode, this bit is applied to the ATA A22 and is vendor specific. Certain ATA drive vendor specific performance enhancements beyond the PCMCIA 2.0 standard may be controlled through use of this bit. This bit has no hardware control function when not in ATA mode.            |

| 9D3 | A21. In ATA mode, this bit is applied to the ATA A21 and is vendor specific. Certain ATA drive vendor specific performance enhancements beyond the PCMCIA 2.0 standard may be controlled through use of this bit. This bit has no hardware control function when not in ATA mode.            |

| D2  | R/W. 0                                                                                                                                                                                                                                                                                       |

| D1  | Speaker is LED Input. 0: Normal operation. 1: The PC Card SPKR# pin will be used to drive IRQ12 if Drive LED Enable is set.                                                                                                                                                                  |

| D0  | ATA Mode. 0: Normal operation. 1: Configures the socket interface to handle ATA type III disk drives.                                                                                                                                                                                        |

#### VIA ID Register (Read) Address: Index (Base + 2Eh)

| Віт     | Function                 |

|---------|--------------------------|

| D [7:4] | Major Version<br>R. 1000 |

| D [3:0] | Minor Version R. 0001    |

**DMA Control (Read/Write) Address**: Index (Base + 2Fh)

| Віт     | Function                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------|

| D [7:6] | DMA Enable. At reset these bits are set to a "0," which is the non-DMA mode. If either or both of     |

|         | these bits is set, the socket is in DMA mode. The three codes select the use of one of three pins for |

|         | the active low DREQ# input at the PCMCIA interface.                                                   |

|         | 01: INPACK#                                                                                           |

|         | 10: WP/IOIS16#                                                                                        |

|         | 11: BVD2/SPKR#                                                                                        |

| D5      | Reserved.                                                                                             |

| D4      | DMA Data Size                                                                                         |

|         | 0: During DMA read/write cycles, data size is 8-bit.                                                  |

|         | 1: During DAM read/write cycles, data size is 16-bit.                                                 |

|         | The I/O window data size bit in I/O control register and the IOIS16# signal are irrelevant during     |

|         | actual DMA cycles.                                                                                    |

| D [3:0] | Reserved.                                                                                             |

# **VT83C469 PIN DESCRIPTION**

| Bus<br>Type | SIGNAL                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pin                                                                                                                                                      | Түре |

|-------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| I           | AEN                       | System Address Enable. High during DMA cycles, low otherwise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 204                                                                                                                                                      | I    |

| I           | BALE                      | Bus Address Latch Enable. An active high input used to latch LA [23:17] at the beginning of the bus cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 205                                                                                                                                                      | Ι    |

| S           | BVD1<br>(STSCHG#/<br>RI#) | If BVD1 is negated by a memory PC Card with a battery, it indicates that the battery is no longer serviceable and data is lost.  For I/O PC Cards, this signal is held high when either or both the Signal on Change bit and Changed bit in the Card Status Register on the PC Card are set to zero. When both of the bits are one, the signal is held low. The Changed bit is the logical OR of the bits CVBAT1, CVBAT2, CWP and CBSYRDY in the Pin Replacement Register on the PC Card. Or this pin is connected to Ring Indicate, which is qualified by Ring Indicate Enable to be passed on to the *RIO pin. | 54, 125                                                                                                                                                  | I    |

| S           | BVD2<br>(SPKR#)           | BVD1 and BVD2 are generated by memory PC Cards with onboard batteries. These signals indicate the health of the battery. Both are asserted high when the battery is in good condition. When BVD2 is negated while BVD1 is still asserted, the battery should be replaced, although data integrity on the memory PC Card is still assured.  When the I/O interface is selected, BVD2 may be used to provide a single amplitude Digital Audio waveform intended to be passed through to the system's speaker without signal conditioning.                                                                          | 52, 123                                                                                                                                                  | I    |