查询W83791D供应商

<mark>捷多邦,专业PCB打样工厂,24小时加急出货</mark>

# W83791D Winbond H/W Monitoring IC

### Preliminary

|   | Pages                                                                      | Dates  | Version | Version<br>on Web | Main Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|----------------------------------------------------------------------------|--------|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | n.a.                                                                       |        |         | n.a.              | All version before 0.20 are for internal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2 | n.a.                                                                       | 01/Jan | 0.2     | n.a.              | First publication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3 | P.7                                                                        | 01/Jan | 0.21    | n.a.              | Revise SLOTOCC# pin description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4 | P.34                                                                       | 01/Jan | 0.21    | n.a.              | Add SMI# /IRQ for Voltage/Fan description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5 | P.43/44                                                                    | 19/Mar | 0.3     | n.a.              | Register Index 1Ah~1Fh revised.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6 | P. 40<br>P. 42<br>P. 60/61<br>P. 58/59<br>P. 66<br>P. 66<br>P. 66<br>P. 87 | 21/May | 0.4     | n.a.              | <ul> <li>This update is for C version IC.</li> <li>Add EVNTRAP1-5 polarity (Index Ah )</li> <li>Add VID protection control bit (Index15h bit5)</li> <li>Add FAN1-3/PWMOUT1-3 as GPIn data register. (Index 95h/97h)</li> <li>SMARTFAN<sup>TM</sup> step up/down time registers exchanged.</li> <li>Add a bit (Index A6 bit7) to know either speech or GPIO function did you use.</li> <li>Pin44 (SMI#/LEDOUT) is a multi-function, it is programmable.</li> <li>EVENTRAP can as GPIO by programming Index A6h bit0-4.</li> <li>Updated V0.17 schematics adding LEDOUT circuit for SMI# (Pin 44)</li> </ul> |

| 7 | All pages                                                                  | 09/Aug | 0.41    | n.a.              | Repaginate datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### W83791D Data Sheet Revision History

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this data sheet belong to their respective owners.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

### Preliminary

### TABLE OF CONTENTS

| 1.         | GENERAL DESCRIPTION                                                                                                                                                   | 1     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2.         | FEATURES                                                                                                                                                              | 3     |

| 2.1        | Monitoring Items                                                                                                                                                      | 3     |

| 2.2        | Address Resolution Protocol (ARP) and Alert-Standard Forum(ASF)                                                                                                       |       |

| 2.3        | Speech Items                                                                                                                                                          | 3     |

| 2.4        | Actions Enabling                                                                                                                                                      | 3     |

| 2.5        | Enhance Monitoring VID function                                                                                                                                       | 4     |

| 2.6        | General                                                                                                                                                               | 4     |

| 2.7        | Package                                                                                                                                                               | 4     |

| 3.         | KEY SPECIFICATIONS                                                                                                                                                    | 4     |

| 4.         | PIN CONFIGURATION                                                                                                                                                     | 5     |

| 5.         | PIN DESCRIPTION                                                                                                                                                       | 6     |

| 6.         | FUNCTION DESCRIPTION                                                                                                                                                  | 10    |

| 6.1        | General Description                                                                                                                                                   | 10    |

| 6.2        | Access Interface                                                                                                                                                      | 10    |

|            | 6.2.1 The first serial bus access timing                                                                                                                              | 10    |

| 6.3        | Speech Function                                                                                                                                                       | 11    |

|            | 6.3.1 General Description                                                                                                                                             |       |

|            | 6.3.2 Event Trigger Queue                                                                                                                                             |       |

|            | 6.3.3 Connection of EEPROM                                                                                                                                            |       |

| <b>C</b> 1 | 6.3.4 Speaker Output                                                                                                                                                  |       |

| 6.4        | Address Resolution Protocol (ARP) Introduction                                                                                                                        |       |

| 6.5        | ASF(Alert Standard Format) Introduction                                                                                                                               |       |

| ~ ~        | 6.5.1 Platform Event Trap (PET)                                                                                                                                       |       |

| 6.6        | Analog Inputs                                                                                                                                                         |       |

|            | <ul><li>6.6.1 Monitor over 4.096V voltage:</li><li>6.6.2 Monitor negative voltage:</li></ul>                                                                          |       |

| 6.7        | FAN Speed Count and FAN Speed Control                                                                                                                                 |       |

| 0.7        | 6.7.1 Fan speed count                                                                                                                                                 |       |

|            | 6.7.2 Fan speed control                                                                                                                                               |       |

|            | 6.7.3 Smart Fan Control                                                                                                                                               |       |

| 6.8        | Temperature Measurement Machine                                                                                                                                       | 25    |

|            | <ul> <li>6.8.1 Monitor temperature from thermistor:</li> <li>6.8.2 Monitor temperature from Pentium II<sup>™</sup> thermal diode or bipolar transistor 2N3</li> </ul> | 25    |

|            | 6.8.2 Monitor temperature from Pentium II <sup>™</sup> thermal diode or bipolar transistor 2N3                                                                        | 90425 |

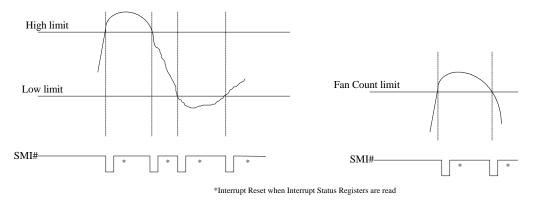

|            | 6.8.3 SMI# interrupt for W83791D Voltage                                                                                                                              |       |

|            | 6.8.4 SMI# interrupt for W83791D Fan                                                                                                                                  |       |

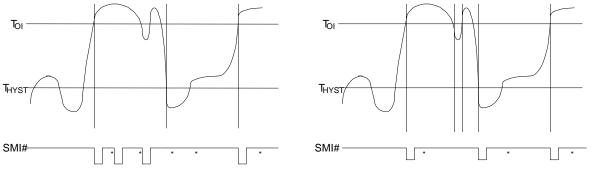

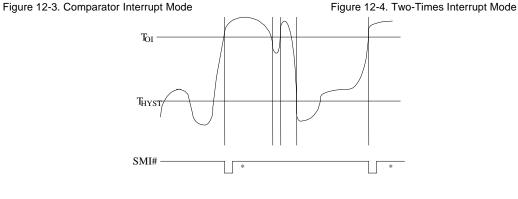

|            | 6.8.5 SMI# interrupt for W83791D temperature sensor 1/2/3                                                                                                             |       |

Publication Release Date: Aug, 2001

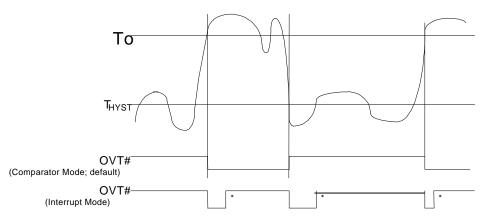

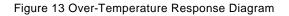

#### Preliminary 6.8.6 Over-Temperature (OVT#) for W83791D temperature sensor 1/2/3......28 7 CONTROL AND STATUS REGISTER ...... ERROR! BOOKMARK NOT DEFINED. 7.1 Speech Flash Memory Address Registers — Index 00h-02h (Bank 0)... Error! Bookmark not defined. 7.2 Speech Flash Memory Data Registers — Index 03h-06h (Bank 0) ...... Error! Bookmark not defined. 7.3 Speech Flash Memory Control Register — Index 07h (Bank 0) ..... Error! Bookmark not defined. 7.4 Event Trigger Timeout Register — Index 08h (Bank 0)..... Error! Bookmark not defined. 7.5 Speech Programmable Trigger Register — Index 09h (Bank 0) ..... Error! Bookmark not defined. 7.6 Speech Input Trigger Property Register — Index 0Ah (Bank 0)..... Error! Bookmark not defined. 7.7 Reserved Register — Index 0Bh (Bank 0)..... Error! Bookmark not defined. VID and VCORE voltage Property Register — Index 0Ch (Bank 0) ..... Error! Bookmark not defined. 7.8 7.9 Speech Flash Memory Read Data Registers — Index 0Dh-0Eh (Bank 0)Error! Bookmark not defined. 7.10 Reserved Register — Index 0Fh (Bank 0) ..... Error! Bookmark not defined. VID Control/Status Register — Index 10h (Bank 0)..... Error! Bookmark not defined. 7.11 7.12 Entry Disable VID Output Control Register — Index 11h (Bank 0) ...... Error! Bookmark not defined. 7.13 VID Output Tolerance/Limit Register — Index 12h (Bank 0)..... Error! Bookmark not defined. GPIO Control Register I — Index 13h (Bank 0)..... Error! Bookmark not defined. 7.14 7.15 GPIO Data/Status Register I — Index 14h (Bank 0) ..... Error! Bookmark not defined. GPIO Control Register II — Index 15h (Bank 0)..... Error! Bookmark not defined. 7.16 7.17 GPIO Output Data and Status Register II — Index 16h (Bank 0) ...... Error! Bookmark not defined. 7.18 LED Control Register — Index 17h (Bank 0)..... Error! Bookmark not defined. 7.19 User Defined Registers — Index 18h-1Ch (Bank 0) ..... Error! Bookmark not defined. Speech Control Register 1-- Index 1Dh (Bank 0)..... Error! Bookmark not defined. 7.20 Speech Control Register 2-- Index 1Eh (Bank 0) ..... Error! Bookmark not defined. 7.21 7.22 Speech Control Register 3-- Index 1Fh (Bank 0)..... Error! Bookmark not defined. Value RAM — Index 20h- 3Fh (Bank 0)..... Error! Bookmark not defined. 7.23 7.24 Configuration Register — Index 40h (Bank 0) ..... Error! Bookmark not defined. Interrupt Status Register 1 — Index 41h (Bank 0) ..... Error! Bookmark not defined. 7.25 Interrupt Status Register 2 — Index 42h (Bank 0) ..... Error! Bookmark not defined. 7.26 7.27 SMI# Mask Register 1 — Index 43h (Bank 0)..... Error! Bookmark not defined. 7.28 SMI# Mask Register 2 — Index 44h (Bank 0)..... Error! Bookmark not defined. 7.29 IRQ Mask Register 1 — Index 45h (Bank 0)..... Error! Bookmark not defined. 7.30 IRQ Mask Register 2 — Index 46h (Bank 0)..... Error! Bookmark not defined. VID/Fan Divisor Register — Index 47h (Bank 0)..... Error! Bookmark not defined. 7.31 Serial Bus Address Register — Index 48h (Bank 0)..... Error! Bookmark not defined. 7.32 7.33 Voltage ID (VID4) & Device ID -- Index 49h (Bank 0)..... Error! Bookmark not defined. 7.34 Temperature 2 and Temperature 3 Serial Bus Address Register -- Index4Ah (Bank 0)Error! **Bookmark** not defined. 7.35 Pin Control Register -- Index4Bh (Bank 0)..... Error! Bookmark not defined. SMI#/OVT# Property Select -- Index 4Ch (Bank 0) ..... Error! Bookmark not defined. 7.36 FAN 1-3 IN/OUT and BEEP Control Register -- Index 4Dh (Bank 0).. Error! Bookmark not defined. 7.37 Bank Select -- Index 4Eh (Bank 0)...... Error! Bookmark not defined. 7.38 Winbond Vendor ID -- Index 4Fh (Bank 0)..... Error! Bookmark not defined. 7.39 7.40 Winbond Test Register -- Index 50h - 55h (Bank 0)..... Error! Bookmark not defined. 7.41 BEEP Control Register 1-- Index 56h (Bank 0) ..... Error! Bookmark not defined.

Publication Release Date: Aug, 2001

### Preliminary

| 7.42 | BEEP Control Register 2 Index 57h (Bank 0)                                                   | . Error! Bookmark not defined. |

|------|----------------------------------------------------------------------------------------------|--------------------------------|

| 7.43 | Chip ID Index 58h (Bank 0)                                                                   | . Error! Bookmark not defined. |

| 7.44 | Diode Selection Register Index 59h (Bank 0)                                                  | . Error! Bookmark not defined. |

| 7.45 | Reserved Index 5Ah - (Bank 0)                                                                | . Error! Bookmark not defined. |

| 7.46 | FANIN 4/5 Control Index 5Bh (Bank 0)                                                         | . Error! Bookmark not defined. |

| 7.47 | FAN 4/5 Divisor Control Index 5Ch (Bank 0)                                                   | . Error! Bookmark not defined. |

| 7.48 | VBAT Monitor Control Register Index 5Dh (Bank 0)                                             | . Error! Bookmark not defined. |

| 7.49 | ACPI Temperature Increment Register Index 5Eh                                                | . Error! Bookmark not defined. |

| 7.50 | Reserved Index 5Fh (Bank 0)                                                                  | . Error! Bookmark not defined. |

| 7.51 | FAN 1 Pre-Scale Register Index 80h (Bank 0)                                                  | . Error! Bookmark not defined. |

| 7.52 | FAN 1 Duty Cycle Select Register 81h (Bank 0)                                                | . Error! Bookmark not defined. |

| 7.53 | FAN 2 Pre-Scale Register Index 82h (Bank 0)                                                  | . Error! Bookmark not defined. |

| 7.54 | FAN2 Duty Cycle Select Register Index 83h (Bank 0)                                           | . Error! Bookmark not defined. |

| 7.55 | FAN 1/2 Configuration Register Index 84h (Bank 0)                                            | . Error! Bookmark not defined. |

| 7.56 | Fan 1 Target Temperature Register/Target Fan 1 Speed Control Regist<br>Bookmark not defined. | er Index 85h (Bank 0) Error!   |

| 7.57 | Fan 2 Target Temperature Register/Target Fan 2 Speed Control Regist                          | er Index 86h (Bank 0) Error!   |

| //   | Bookmark not defined.                                                                        |                                |

| 7.58 | Tolerance of Fan1/2 Target Temperature or Speed Register Index 8' <b>defined.</b>            | 7h (Bank0)Error! Bookmark not  |

| 7.59 | Fan 1 PWM Stop Duty Cycle Register Index 88h (Bank 0)                                        | . Error! Bookmark not defined. |

| 7.60 | Fan 2 PWM Stop Duty Cycle Register 89h (Bank 0)                                              |                                |

| 7.61 | Fan 1 Start-up Duty Cycle Register Index 8Ah (Bank 0)                                        |                                |

| 7.62 | Fan 2 Start-up Duty Cycle Register Index 8Bh (Bank 0)                                        |                                |

| 7.63 | Fan 1 Stop Time Register Index 8Ch (Bank 0)                                                  |                                |

| 7.64 | Fan 2 Stop Time Register Index 8Dh (Bank 0)                                                  |                                |

| 7.65 | Fan 1/2/3 Step Down Time Register Index 8Eh (Bank 0)                                         |                                |

| 7.66 | Fan 1/2/3 Step Up Time Register Index 8Fh (Bank 0)                                           | . Error! Bookmark not defined. |

| 7.67 | Temperature Sensor 1 (VTIN1) Offset Register - Index 90h (Bank 0)                            | . Error! Bookmark not defined. |

| 7.68 | Temperature Sensor 2 (VTIN2) Offset Register - Index 91h (Bank 0)                            | . Error! Bookmark not defined. |

| 7.69 | Temperature Sensor 3 (VTIN3) Offset Register - Index 92h (Bank 0)                            | . Error! Bookmark not defined. |

| 7.70 | FAN 3 Pre-Scale Register Index 93h (Bank 0)                                                  | . Error! Bookmark not defined. |

| 7.71 | FAN 3 Duty Cycle Select Register 94h (Bank 0)                                                | . Error! Bookmark not defined. |

| 7.72 | FAN 3 Configuration Register Index 95h (Bank 0)                                              | . Error! Bookmark not defined. |

| 7.73 | Fan 3 Target Temperature Register/Target Fan 3 Speed Control Regist<br>Bookmark not defined. | er Index 96h (Bank 0) Error!   |

| 7.74 | Tolerance of Fan 3 Target Temperature or Speed Register Index 97h                            | (Bank 0)Error! Bookmark not    |

|      | defined.                                                                                     |                                |

| 7.75 | Fan 3 PWM Stop Duty Cycle Register Index 98h (Bank 0)                                        | . Error! Bookmark not defined. |

| 7.76 | Fan 3 Start-up Duty Cycle Register Index 99h (Bank 0)                                        | . Error! Bookmark not defined. |

| 7.77 | Fan 3 Stop Time Register Index 9Ah (Bank 0)                                                  | . Error! Bookmark not defined. |

| 7.78 | Interrupt Status Register III Index 9Bh (Bank 0)                                             | . Error! Bookmark not defined. |

| 7.79 | SMI# Mask Register III Index 9Ch (Bank 0)                                                    | . Error! Bookmark not defined. |

| 7.80 | Interrupt Mask Register III Index 9Dh (Bank 0)                                               | . Error! Bookmark not defined. |

| 7.81 | FAN4_PRE_SCALE register Index 9Eh (Bank 0)                                                   | . Error! Bookmark not defined. |

| 7.82 | FAN5_PRE_SCALE register Index 9Fh (Bank 0)                                                   | . Error! Bookmark not defined. |

#### **Preliminary**

| 7.83              | FAN 4 Duty Cycle Select Register – A0h (Bank 0)                                               | . Error! Bookma                  | ark not defined | ł. Č       |

|-------------------|-----------------------------------------------------------------------------------------------|----------------------------------|-----------------|------------|

| 7.84              | FAN 5 Duty Cycle Select Register –A1h (Bank 0)                                                | . Error! Bookma                  | ark not defined | ł.         |

| 7.85              | BEEP Control Register 3 Index A3h (Bank 0)                                                    | . Error! Bookma                  | ark not defined | ł.         |

| 7.86              | Speech Flash Memory Read Data Registers — Index A4h-A5h (Bank                                 | 0)Error! Bookm                   | ark not define  | ed.        |

| 7.87              | EVNTRAP1- 5 and GPIO 5-9 Select Index A6h (Bank 0)                                            | . Error! Bookma                  | ark not defined | ł.         |

| 7.88              | Flash Page count Index A7h (Bank 0)                                                           | . Error! Bookma                  | ark not defined | <b>1.</b>  |

| 7.89              | Real Time Hardware Status Register I Index A9h (Bank 0)                                       | . Error! Bookma                  | ark not defined | <b>1.</b>  |

| 7.90              | Real Time Hardware Status Register II Index AAh (Bank 0)                                      | . Error! Bookma                  | ark not defined | <b>1.</b>  |

| 7.91              | Real Time Hardware Status Register III Index ABh (Bank 0)                                     | . Error! Bookma                  | ark not defined | <b>1</b> . |

| 7.92              | Revered Index AC - AFh (Bank 0)                                                               | . Error! Bookma                  | ark not defined | 1.         |

| 7.93              | Value RAM 2— Index B0h – B7h (BANK 0)                                                         | . Error! Bookma                  | ark not defined | <b>1</b> . |

| 7.94              | Temperature Sensor 2 Temperature (High Byte) Register - Index C0h <b>defined.</b>             | (Bank 0)Error!                   | Bookmark        | not        |

| 7.95              | defined.                                                                                      |                                  | Bookmark        | not        |

| 7.96              |                                                                                               |                                  |                 | 1.         |

| 7.97              | Temperature Sensor 2 Hysteresis (High Byte) Register - Index C3h ( <i>B</i> <b>defined.</b>   | ank 0) <b>Error!</b>             | Bookmark        | not        |

| 7.98              | Temperature Sensor 2 Hysteresis (Low Byte) Register - Index C4h ( <i>Ba</i> <b>defined.</b>   | ank 0)Error!                     | Bookmark        | not        |

| 7.99              | Temperature Sensor 2 Over-temperature (High Byte) Register - Index <b>defined.</b>            | C5h ( <i>Bank 0</i> ) <b>Err</b> | or! Bookmark    | x not      |

| 7.10              | 0 Temperature Sensor 2 Over-temperature (Low Byte) Register - Index                           | C6h(Bank 0)Erro                  | r! Bookmark     | not        |

|                   | defined.                                                                                      |                                  |                 |            |

|                   | 1 Temperature Sensor 3 Temperature (High Byte) Register - Index C8h <b>defined.</b>           |                                  | Bookmark        | not        |

|                   | 2 Temperature Sensor 3 Temperature (Low Byte) Register - Index C9h (<br>defined.              |                                  | Bookmark        | not        |

|                   | 3 Temperature Sensor 3 Configuration Register - Index CAh ( <i>Bank 0</i> )                   |                                  |                 |            |

|                   | 4 Temperature Sensor 3 Hysteresis (High Byte) Register - Index CBh ( <i>B</i> <b>defined.</b> |                                  | Bookmark        | not        |

| 7.10              | 5 Temperature Sensor 3 Hysteresis (Low Byte) Register - Index CCh ( <i>B</i> <b>defined.</b>  | ank 0) <b>Error!</b>             | Bookmark        | not        |

| 7.10              | 6 Temperature Sensor 3 Over-temperature (High Byte) Register - Index <b>defined.</b>          | CDh (Bank 0)Eri                  | ror! Bookmarl   | s not      |

| 7.10              | 7 Temperature Sensor 3 Over-temperature (Low Byte) Register - Index defined.                  | CEh(Bank 0)Erro                  | or! Bookmark    | not        |

| <b>8</b><br>Not [ | ARP (ADDRESS RESOLUTION PROTOCOL) USE REGISTER<br>DEFINED.                                    | R <b>DEFINED</b> ERR             | OR! BOOKM       | ARK        |

| 8.1               | Unique Device Identifier (UDID) 20h-2Fh (Bank 1)                                              | . Error! Bookms                  | ark not defined | 1.         |

| 8.2               | ASF Sensor Environmental Event                                                                |                                  |                 |            |

|                   | 8.2.1 Temperature: Get Event Data message                                                     | Error! Bookmar                   | k not defined   | J.         |

|                   | 8.2.2 Voltage: Get Event Data message                                                         | Error! Bookmar                   | k not defined   | J.         |

|                   | 8.2.3 Fan: Get Event Data message                                                             |                                  |                 |            |

|                   | 8.2.4 Case Intrusion: Get Event Data message                                                  | rror! Bookmar                    | k not defined   | ג.         |

- 8.3 ASF Response Registers -- 40h-7Fh (Bank 1)..... Error! Bookmark not defined.

- 8.3.1 ASF Upper/Lower Temperature Registers:..... Error! Bookmark not defined.

- Sensor device: (SMBus Address, Read/Write) V Error! Bookmark not defined. Publication Release Date: Aug. 200 8.3.2

| 8.4 | 8.3.3<br>8.3.4<br>8.3.5<br>BJT RT | Relative Entity ID Table:<br>Default Entity ID<br>Entity Instance Register<br>'-Table - 50h-57h ( <i>Bank 7</i> ) – TEST mode only | Error! Bookmark not defined.<br>Error! Bookmark not defined. |

|-----|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 9   | ELECT                             | RICAL CHARACTERISTICS                                                                                                              |                                                              |

| 9.1 | Absolut                           | e Maximum Ratings                                                                                                                  |                                                              |

| 9.2 | DC Cha                            | aracteristics                                                                                                                      |                                                              |

| 9.3 | AC Cha                            | aracteristics                                                                                                                      |                                                              |

|     | 9.3.1                             | Serial Bus Timing Diagram                                                                                                          |                                                              |

| 10  | ном 1                             | O READ THE TOP MARKING                                                                                                             |                                                              |

| 11  | PACK                              | AGE SPECIFICATION                                                                                                                  |                                                              |

#### Preliminary

#### **1. GENERAL DESCRIPTION**

W83791D is an evolving version of the W83782D --- Winbond's most popular hardware status monitoring IC. Besides the conventional functions of W83782D, W83791D uniquely provides several innovative features such as speech function, ASF sensor compliant, SMBus 2.0 ARP command compatible, VID table selection trapping, and 5VID output control. Conventionally, W83791D can be used to monitor several critical hardware parameters of the system, including power supply voltages, fan speeds, and temperatures, which are very important for a high-end computer system to work stably and efficiently. As for data access, W83791D provides slave SMBus 2.0 interface which can reply PEC (Packet Error Code) when as ASF sensor.

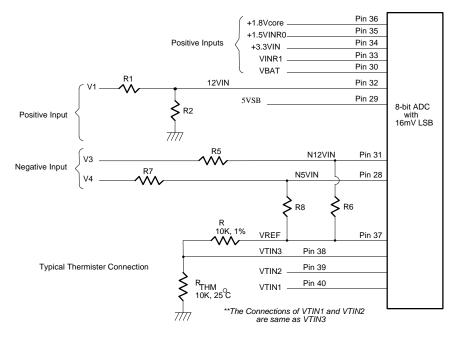

An 8-bit analog-to-digital converter (ADC) was built inside W83791D. W83791D can simultaneously monitor 10 analog voltage inputs (including power VDD/5VSB monitoring), 5 fan tachometer inputs, 3 remote temperatures, and one case open detection signal. The sense of remote temperature can be performed by thermistors, 2N3904 NPN-type transistors, or directly from Intel<sup>TM</sup> CPU with thermal diode output. W83791D provides 3 PWM (pulse width modulation) outputs for two modes of smart fan control-" Thermal Cruise<sup>TM</sup>" mode and "Speed Cruise<sup>tf</sup> mode. Under " Thermal Cruise<sup>TM</sup>" mode, temperatures of CPU and the system can be maintained within specific programmable ranges under the hardware control. "Speed Cruise<sup>tf</sup>, namely, is to keep the fan operate in the specific programmable r.p.m. As for warning mechanism, W83791D provides speech voice warning, beep tone warning, and SMI#, OVT#, IRQ signals for system protection events.

Additionally, 5 VID inputs are provided to read the VID of CPU (i.e. Pentium<sup>TM</sup> II/III) if applicable. These VID inputs provide the information of Vcore voltage that CPU expects. Furthermore, W83791D provides programmable VID output control to alter the voltage CPU consumes. W83791D also uniquely provides an optional feature: early stage (before BIOS was loaded) beep / speech warning to detect if the fatal elements present --- Vcore or +3.3V voltage fail and thus the system can not be boomed up. If the VSB power on setting refers to Intel VRM 9.x, the VID table within W83791D will be according to the new one. W83791D also has 2 specific pins to provide selectable address setting for application of multiple devices (up to 4 devices) wired through  $I^2C^{TM}$  interface.

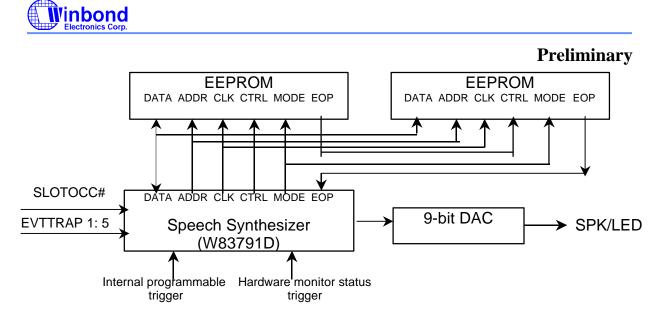

W83791D speech function is enabled by building in a programmable speech synthesizer with a 9-bit current DAC output as well as a connectable external flash memory for storing voice data. W83791D supports 1 CPU present or absent event trap, 5 external event traps, 17 hardware monitor event traps (10 analog voltage, 3 fan tachometer, 3 remote temperature, 1 case open) and 128 internal programmable event traps, amounting to 151 different speech outputs. If more than two events happen simultaneously, the priority set is: SLOTOCC# > EVNTRP1 > EVNTRP2 > EVNTRP3 > EVNTRP4 > EVNTRP5 > 128 Programmable events (Bank0 index 09h) > 17 Hardware status events. Voice data stored in the external flash memory interface with Winbond W55FXX is flexible to change by Winbond application software and **on-line** programming flash data is provided also. Besides, An external resistor is added to provide ring oscillator.

When you do not use the speech function, W83791D provides a set of flexible I/O control functions to the system designer through a set of General Purpose I/O ports. These GPIO ports may serve as simple I/O or may be individually configured to provide a pre-defined alternate function. If pin 9 (SPEECH\_SEL) is trapped to high at VSB power on, this function will be active.

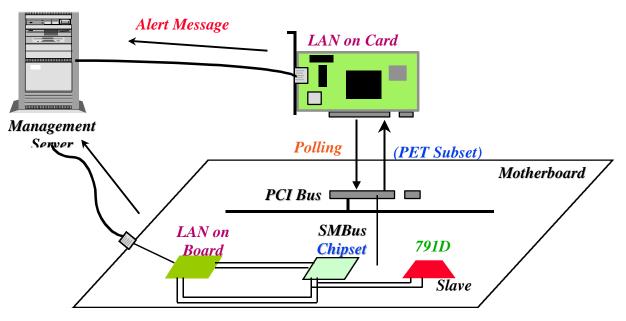

W83791D can uniquely serve as an ASF sensor to respond to ASF master's request for the implementation of network management in OS-absent state. Through W83791D's compliance with ASF sensor spec, network server is able to monitor the environmental status of the client in OS-absent state by PET frame values returned from W83791D, such as temperatures, voltages, fan speed, and case open. Moreover, W83791D supports SMBus 2.0 ARP command to solve the problem of address conflicts by dynamically assigning a new unique address to W83791D after W83791D's UDID is sent.

Through the application software or BIOS, the users can read all the monitored parameters of the system

#### Preliminary

from time to time. A pop-up warning can also be activated when the monitored item is out of the proper/preset range. The application software could be Winbond's Hardware Doctor<sup>TM</sup>, Intel<sup>TM</sup> LDCM (LanDesk Client Management), or other management application software. Besides, the users can set up the upper and lower limits (alarm thresholds) of these monitored parameters and activate one programmable and maskable interrupts. An optional beep tone could be used as a warning signal when the monitored parameters are out of the preset range.

#### Preliminary

#### 2. FEATURES

#### 2.1 Monitoring Items

- 10 voltage inputs

- --- Typical for VCORE, +3.3V, +12V, -12V, +5V, -5V, +5VSB, VBAT, and two reserved

- 5 fan speed monitoring inputs

- 3 temperature inputs from remote thermistors, 2N3904 NPN-type transistors or Pentium<sup>TM</sup> II (Deschutes) thermal diode output

- Case open detection input

- WATCHDOG comparison of all monitored values

- Programmable hysteresis and setting points (alarm thresholds) for all monitored items

#### 2.2 Address Resolution Protocol (ARP) and Alert-Standard Forum(ASF)

- Support System Management Bus (SMBus) version 2.0 specification

- Comply with hardware sensor slave ARP (Address Resolution Protocol)

- Response sensor type ARP command

- Response ASF command --- Get Event Data , Get Event Status

- Comply with ASF sensors (Monitoring fan speed, voltage, temperature, and case open)

#### 2.3 Speech Items

- Programmable speech synthesizer with new high fidelity synthesis algorithm

- Build in 8-bit current D/A converter

- 1 CPU present or absent trigger input

- 5 External trigger inputs

- 128 Internal programmable trigger inputs

- 17 H/W Monitor event trigger inputs

- Programmable 0-255 seconds timeout trigger inputs for firmware or software

- Instruction cycle is ; 400 £ § typically

- Section control provided in each voice section

- External resistor for ring oscillator

#### 2.4 Actions Enabling

- Beep tone warning separated speech output

- 5 PWM (pulse width modulation) outputs for fan speed control (1~3 support Smart Fan control) and 5 Fan speed inputs for monitoring --- Total up to 5 sets of fan speed monitoring and controlling

- Issue SMI#, OVT#, IRQ signals to activate system protection

- Warning signal pop-up in application software

### Preliminary

#### 2.5 Enhance Monitoring VID function

- CPU Voltage ID reading

- VID output control

- Enhance beep warning by detecting Intel VRM 9.0 VID

#### 2.6 General

- $I^2 C^{TM}$  serial bus interface

- 5 VID input pins for CPU VCORE identification (for Pentium<sup>TM</sup> II/III)

- Initial power fault beep (for +3.3V, VCORE)

- 2 pins (A0, A1) to provide selectable address setting for application of multiple devices (up to 4 devices) wired through  $I^2C^{TM}$  interface

Winbond hardware monitoring application software (Hardware  $Doctor^{TM}$ ) support, for both Windows 95/98/2000 and Windows NT 4.0/5.0

- Internal clock Oscillator with 3M Hz

- 5V VSB operation

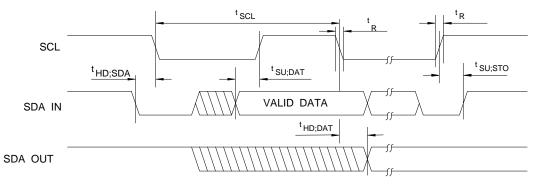

#### 2.7 Package

• 48-pin LQFP

#### 3. KEY SPECIFICATIONS

| Voltage monitoring accuracy                 | ±1% (Max)             |

|---------------------------------------------|-----------------------|

| • Intel VRM 9.x Voltage monitoring accuracy | ±0.5% (Max)           |

| Monitoring Temperature Range and Accuracy   |                       |

| - 40°C to +120°C                            | $\pm 3^{\circ}C(Max)$ |

| Supply Voltage                              | 5V                    |

| Operating Supply Current                    | 5 mA typ.             |

| ADC Resolution                              | 8 Bits                |

### Preliminary

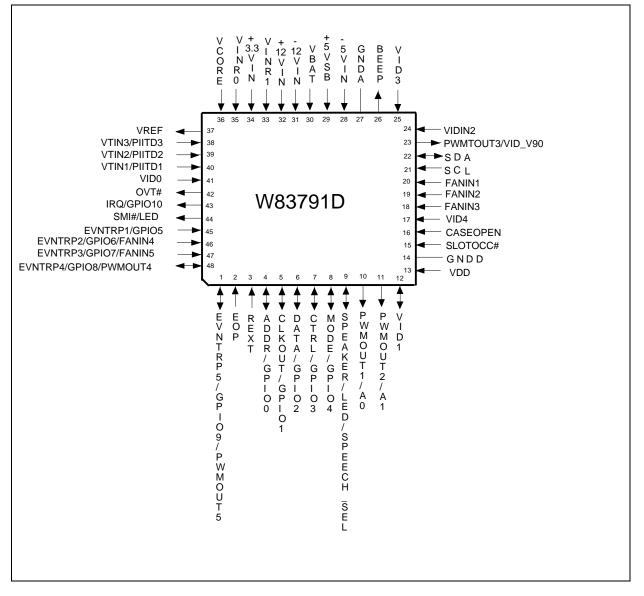

#### 4. PIN CONFIGURATION

### Preliminary

#### 5. PIN DESCRIPTION

I/O<sub>12t</sub> - TTL level bi-directional pin with 12 mA source-sink capability

I/O<sub>12ts</sub> - TTL level and schmitt trigger with 12 mA source-sink capability

I/O<sub>81s</sub> - TTL level and schmitt trigger with 8 mA source-sink capability

I/O<sub>6ts</sub> - TTL level and schmitt trigger with 6 mA source-sink capability

I/OD<sub>12ts</sub> - TTL level and schmitt trigger open drain output with 12 mA sink capability

OUT<sub>12</sub> - Output pin with 12 mA source-sink capability

OD<sub>12</sub> - Open-drain output pin with 12 mA sink capability

AOUT - Output pin(Analog)

IN<sub>t</sub> - TTL level input pin

$IN_{ts}$  - TTL level input pin and schmitt trigger

AIN - Input pin(Analog)

| Pin Name          | Pin No. | Туре                 | Description                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------------------|---------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| EVNTRP5 /         | 1       | I/O <sub>12t</sub>   | Event trapping to selection speech output sound. Default is high edge trigger.                                                                                                                                                                                                                                   |  |  |  |

| GPIO9/<br>PWMOUT5 |         |                      | General purpose I/O function. If pin 9 (SPEECH_SEL) is trapped to high<br>at VSB power on, this function will be active. The I/O control and status<br>is defined in BANK0 Index 13h~14h. Otherwise, GPIO pin o<br>PWMOUT Fan control can be selected by registers, but the PWMOUT<br>can not support Smart Fan. |  |  |  |

| EOP               | 2       | Ι                    | End of Process signal input from cascaded Flash.                                                                                                                                                                                                                                                                 |  |  |  |

| GPIO11            |         | I/OD <sub>12ts</sub> | General purpose I/O function pin. If pin 9 (SPEECH_SEL) is trapped to high at VSB power on, this function will be active.                                                                                                                                                                                        |  |  |  |

| REXT              | 3       | Ι                    | Resistor(Rosc) connect to VSB used to adjust ring oscillator frequency.                                                                                                                                                                                                                                          |  |  |  |

| ADDR /            | 4       | OUT <sub>12</sub>    | Speech address pulse output, connect to W55FXX. When this pin translates from logic high to logic low, it will latch the data pin 6 and shift it into a speech flash address counter.                                                                                                                            |  |  |  |

| GPIO0             |         | I/OD <sub>12ts</sub> | General purpose I/O function. If pin 9 (SPEECH_SEL) is trapped to high at VSB power on, this function will be active.                                                                                                                                                                                            |  |  |  |

| CLKOUT /          | 5       | OUT <sub>12</sub>    | Speech clock output, for speech data read-out and write-in, connect to W55FXX. When this pin translates from logic high to logic low, the data pin 6 will be latched by this clock.                                                                                                                              |  |  |  |

| GPIO1             |         | I/OD <sub>12ts</sub> | General purpose I/O function. If pin 9 (SPEECH_SEL) is trapped to high at VSB power on, this function will be active.                                                                                                                                                                                            |  |  |  |

| DATA /            | 6       | I/O <sub>12t</sub>   | Serial data input/output, connect to W55FXX. The pin is latched by CLKOUT and ADDR acted as speech data and address respectively.                                                                                                                                                                                |  |  |  |

| GPIO2             |         | I/OD <sub>12ts</sub> | General purpose I/O function. If pin 9 (SPEECH_SEL) is trapped to high at VSB power on, this function will be active.                                                                                                                                                                                            |  |  |  |

| CTRL /            | 7       | OUT <sub>12</sub>    | Output clock numbers of this pin decide which mode is selected. Connect to W55FXX.                                                                                                                                                                                                                               |  |  |  |

| GPIO3             |         | I/OD <sub>12ts</sub> | General purpose I/O function. If pin 9 (SPEECH_SEL) is trapped to high at VSB power on, this function will be active.                                                                                                                                                                                            |  |  |  |

| MODE /            | 8       | OUT <sub>12</sub>    | Output mode signal to W55FXX serial Flash.                                                                                                                                                                                                                                                                       |  |  |  |

|                   |       |                      | Preliminary                                                                                                                                                                                                                            |

|-------------------|-------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO4             |       | I/OD <sub>12ts</sub> | General purpose I/O function. If pin 9 (SPEECH_SEL) is trapped to high at VSB power on, this function will be active.                                                                                                                  |

| SPEAKER           | 9     | OUT <sub>12</sub>    | Current type output driving an external speaker. The function is only working in VDD 5V OK.                                                                                                                                            |

| LED               |       | OUT <sub>12</sub>    | LED output control. This is a multi-function pin with SPEAKER. When<br>the LED_SEL register (Bank0 Index 17h) is set to 1, LED output<br>function will be active. Otherwise, set to 0 (default), this pin serves as<br>SPEAKER output. |

| SPEECH_SEL        |       | IN <sub>ts</sub>     | During VSB 5V power on, this pin is used to trap whether using speech function or GPIO function.                                                                                                                                       |

|                   |       |                      | Trapping low means using speech function (i.e. pin45-48, pin1, pin4-8 are as speech function).                                                                                                                                         |

|                   |       |                      | Trapping high means using GPIO function (i.e. pin45-48, pin1, pin4-8 are as GPIO function). The I/O control and status is defined in BANK0 Index 13h~16h.                                                                              |

| PWMOUT1/          | 10    | OUT <sub>12</sub>    | Fan speed control PWM output. When the power of VDD is 0v, this pin will drive logic 0. The power of this pin is supplied by VSB 5V.                                                                                                   |

| A0                |       | IN <sub>ts</sub>     | I <sup>2</sup> C device address bit0 trapping during 5VSB power on.                                                                                                                                                                    |

| PWMOUT2 /         | 11    | OUT <sub>12</sub>    | Fan speed control PWM output. When the power of VDD is 0v, this pin will drive logic 0. The power of this pin is supplied by VSB 5V.                                                                                                   |

| A1                |       | IN <sub>ts</sub>     | I <sup>2</sup> C device address bit1 trapping during 5VSB power on.                                                                                                                                                                    |

| VID1              | 12    | I/O <sub>12ts</sub>  | Voltage Supply readouts from CPU. After programming, this pin can be VID output to voltage regulator to generate Vcore for CPU.                                                                                                        |

| VDD (5V)          | 13    | POWER                | +5V VDD power. Bypass with the parallel combination of $10\mu$ F (electrolytic or tantalum) and $0.1\mu$ F (ceramic) bypass capacitors.                                                                                                |

| GNDD              | 14    | DGROUND              | Internally connected to all digital circuitry.                                                                                                                                                                                         |

| SLOTOCC#          | 15    | IN <sub>ts</sub>     | CPU presence signal. 0, means CPU is present. 1, means CPU is absent                                                                                                                                                                   |

| CASEOPEN          | 16    | I/O <sub>6ts</sub>   | CASE OPEN detection. An active high input from an external device<br>when case is Intruded. This signal can be latched in external circuit<br>which power is supplied by VBAT, even if W83791D is power off.                           |

| VID4              | 17    | I/O <sub>12ts</sub>  | Voltage Supply readouts from CPU. After programming, this pin can be VID output to voltage regulator to generate Vcore for CPU.                                                                                                        |

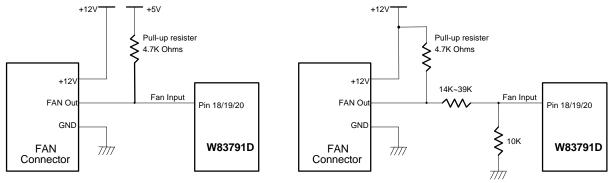

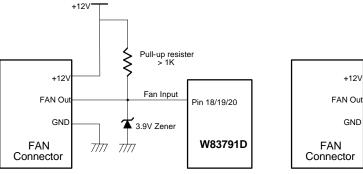

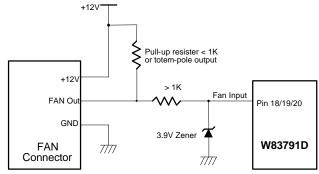

| FAN3IN-<br>FAN1IN | 18-20 | IN <sub>ts</sub>     | 0V to +5V amplitude fan tachometer input                                                                                                                                                                                               |

| SCL               | 21    | IN <sub>ts</sub>     | Serial Bus Clock.                                                                                                                                                                                                                      |

| SDA               | 22    | I/OD <sub>8ts</sub>  | Serial Bus bi-directional Data.                                                                                                                                                                                                        |

| PWMOUT3 /         | 23    | OUT <sub>12</sub>    | Fan speed control PWM output. When the power of VDD is 0v, this pin will drive logic 0. The power of this pin is supplied by VSB 5V.                                                                                                   |

| VID_V90           |       | IN <sub>ts</sub>     | VID table selection trapping during RSMRST (0: Intel VRM 8.2/8.3; 1: Intel VRM 9.0). When the trapping pin get a logic 1, the beep warning function is according to Intel VRM 9.0 VID.                                                 |

| VID2              | 24    | I/O <sub>12ts</sub>  | Voltage Supply readouts from CPU. After programming, this pin can be VID output to voltage regulator to generate Vcore for CPU.                                                                                                        |

| VID3              | 25    | I/O <sub>12ts</sub>  | Voltage Supply readouts from CPU. After programming, this pin can be VID output to voltage regulator to generate Vcore for CPU.                                                                                                        |

|                      |       |                      | Preliminary                                                                                                                                                                                                                                                         |

|----------------------|-------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BEEP                 | 26    | OD <sub>12</sub>     | Alarm beep output. Normal, this pin is low. When abnormal event happens, this pin will output alarm frequency.                                                                                                                                                      |

| GNDA                 | 27    | AGROUND              | Internally connected to all analog circuitry. The ground reference for all analog inputs.                                                                                                                                                                           |

| -5VIN                | 28    | AIN                  | 0V to 4.096V FSR Analog Inputs.                                                                                                                                                                                                                                     |

| +5VSB                | 29    | POWER                | This pin is power for W83791D. Bypass with the parallel combination of $10\mu$ F (electrolytic or tantalum) and $0.1\mu$ F (ceramic) bypass capacitors.                                                                                                             |

| VBAT                 | 30    | POWER                | This pin is power for W83791D.                                                                                                                                                                                                                                      |

| -12VIN               | 31    | AIN                  | 0V to 4.096V FSR Analog Inputs.                                                                                                                                                                                                                                     |

| +12VIN               | 32    | AIN                  | 0V to 4.096V FSR Analog Inputs.                                                                                                                                                                                                                                     |

| VINR1                | 33    | AIN                  | 0V to 4.096V FSR Analog Inputs.                                                                                                                                                                                                                                     |

| +3.3VIN              | 34    | AIN                  | 0V to 4.096V FSR Analog Inputs.                                                                                                                                                                                                                                     |

| VINR0                | 35    | AIN                  | 0V to 4.096V FSR Analog Inputs.                                                                                                                                                                                                                                     |

| VCORE                | 36    | AIN                  | 0V to 4.096V FSR Analog Inputs.                                                                                                                                                                                                                                     |

| VREF                 | 37    | AOUT                 | Reference voltage.                                                                                                                                                                                                                                                  |

| VTIN3 /              | 38    | AIN                  | Thermistor 3 terminal input.(Default).                                                                                                                                                                                                                              |

| PIITD3               |       |                      | Pentium <sup>TM</sup> II diode 3 input.                                                                                                                                                                                                                             |

|                      |       |                      | This multi-functional pin is programmable.                                                                                                                                                                                                                          |

| VTIN2 /              | 39    | AIN                  | Thermistor 2 terminal input. (Default).                                                                                                                                                                                                                             |

| PIITD2               |       |                      | Pentium <sup>TM</sup> II diode 2 input.                                                                                                                                                                                                                             |

|                      |       |                      | This multi-functional pin is programmable.                                                                                                                                                                                                                          |

| VTIN1 /              | 40    | AIN                  | Thermistor 1 terminal input. (Default).                                                                                                                                                                                                                             |

| PIITD1               |       |                      | Pentium <sup>TM</sup> II diode 1 input.                                                                                                                                                                                                                             |

|                      |       |                      | This multi-functional pin is programmable.                                                                                                                                                                                                                          |

| VID0                 | 41    | I/O <sub>12ts</sub>  | Voltage Supply readouts from CPU. After programming, this pin can be VID output to voltage regulator to generate Vcore for CPU.                                                                                                                                     |

| OVT#                 | 42    | OD <sub>12</sub>     | Over temperature Shutdown Output for temperature sensor 1-3.                                                                                                                                                                                                        |

| IRQ /                | 43    | OUT <sub>12</sub>    | Interrupt request.                                                                                                                                                                                                                                                  |

| GPIO10               |       | I/OD <sub>12ts</sub> | General purpose I/O function. If pin 9 (SPEECH_SEL) is trapped to high at VSB power on, this function will be active.                                                                                                                                               |

| SMI# /               | 44    | OD <sub>12</sub>     | System Management Interrupt (open drain).                                                                                                                                                                                                                           |

| LED                  |       | OUT <sub>12</sub>    | LED output control. This is a multi-function pin with SMI. When the register (Bank0 Index 17h bit7 and Index A6h bit 6) is set to 1, LED output function will be active. Otherwise, set to 0 (default), this pin serves as SMI#.                                    |

| EVNTRP2-3/           | 46-47 | I/O <sub>12ts</sub>  | Event trapping to selection speech output sound. Default is high edge trigger.                                                                                                                                                                                      |

| GPIO6-7/<br>FANIN4-5 |       | I/O <sub>12ts</sub>  | General purpose I/O function. If pin 9 (SPEECH_SEL) is trapped to high<br>at VSB power on, this speech function will be active. The I/O control<br>and status is defined in BANK0 Index 13h~14h. Otherwise, GPIO pin or<br>FAN inputs can be selected by registers. |

| EVNTRP4/             | 48    | I/O <sub>12ts</sub>  | Event trapping to selection speech output sound.                                                                                                                                                                                                                    |

### Preliminary

| GPIO8/<br>PWMOUT4 | I/O <sub>12ts</sub> | General purpose I/O function. If pin 9 (SPEECH_SEL) is trapped to high<br>at VSB power on, this function will be active. The I/O control and status<br>is defined in BANKO Index 13h~14h. Otherwise, GPIO pin or<br>PWMOUT Fan control can be selected by registers, but the PWMOUT<br>can not support Smart Fan. |

|-------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### Preliminary

#### 6. FUNCTION DESCRIPTION

#### 6.1 General Description

The W83791D provides 10 analog positive inputs, 5 fan speed inputs, at most 5 sets for fan PWM (Pulse Width Modulation) control, 3 thermal inputs from remote thermistors ; B2N3904 transistors or Pentium<sup>TM</sup> II/III (Deschutes) thermal diode outputs, case open detection and beep function output when the monitored values exceed preset ranges, including the voltage, temperature, and fan count. Moreover, W83791D uniquely provides several innovative and practical functions to make the whole system more efficient and compliant with future trend of network management, such as speech function, ASF sensor compliant, SMBus 2.0 ARP command compatible, VID table selection trapping, 5VID output control, and so forth. Once the monitoring function of W83791D is enabled, the watch dog machine will monitor every function and store the values to registers for comparison with preset ranges. If the monitoring value exceeds the limit value, the interrupt status will be set to 1 and W83791D will issue interrupt signals such as SMI# and IRQ if not masked..

#### 6.2 Access Interface

The W83791D provides  $I^2C$  Serial Bus for microprocessor to read/write internal registers. In the W83791D, there are three serial bus addresses. Through the first address defined at CR[48h], all the registers can be read and written except CPUT1/CPUT2 temperature sensor registers. The read/write of the CPUT1/CPUT2 temperature sensor registers can be implemented through the second address (defined at CR[4Ah] bit2-0) and the third address (defined at CR[4Ah] bit6-4).

The first serial bus address of W83791D has 2 hardware setting bits set by pin10-11. The address is 001011[pin11][pin10]. Hence, the content of CR[48h] would be 00101110 if pin11=1 and pin10=0.

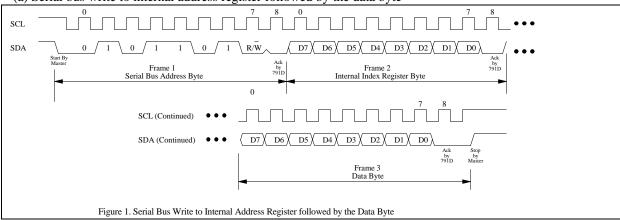

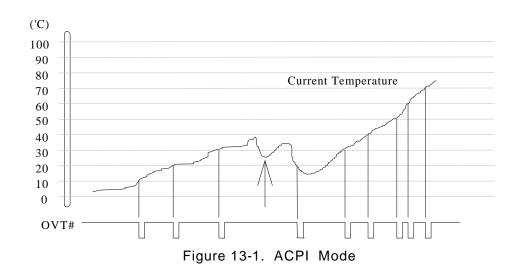

#### 6.2.1 The first serial bus access timing

(a) Serial bus write to internal address register followed by the data byte

#### **Preliminary** (b) Serial bus read from a register 0 SCL SDA R/W D7 D5 D1 D0 D6 D4 D3 D2Ack by 791D Ack by 791D Frame 1 Frame 2 Serial Bus Address Byte Internal Index Register Byte 0 SCI (Continued) • SDA (Continued) • R/WD7 D6 D5 D2 D1 D0 D4 D3 Stop by Master Repeat start by Master Frame 4 Frame Data Byt Figure 2. Serial Bus Read from Internal Address Register

#### 6.3 Speech Function

#### 6.3.1 General Description

The W83791D is a derivative of Winbond's *PowerSpeech*<sup>TM</sup> synthesizers. There are up to 5 hardware trigger inputs, 17 Hardware Monitor event and 128 programmable software event trigger inputs. If more than two events happen simultaneously, the priority set by the internal H/W is: SLOTOCC# > EVNTRAP1 > EVNTRAP2 > EVNTRAP3 > EVNTRAP4 > EVNTRAP5 > TRIGREG(Index 09h) 128 events > VIN0 > VIN1> others (VIN2 - VIN9,TEMP, FAN, case open). Software trigger is able to accommodate 128 event triggers, with timeout register (index 08h) enabled in advance for allowance of time on detecting devices. That is, once the system's power is on, BIOS can fill trigger event and speech voice will not be sent till the system fails owing to timeout. In addition, to prevent events from taking place simultaneously.

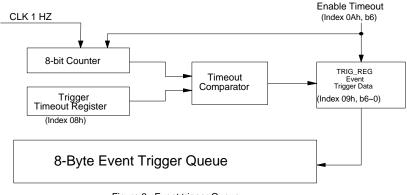

#### 6.3.2 Event Trigger Queue

W83791D provides 8 byte FIFO queue to store event trigger, i.e, the first 8 event can be served by speech and speech will clear FIFO queue after service. Coding of Speech program must assign correct CPU\_MODE event vector to issue correct speech voices correspondent to speech trigger events. For example, CPU\_MODE event vector =1 represents absence of CPU, then coding speech with CPU is absent voice. When W83791D detects no CPU exists, it will send vector = 1 to speech synthesizer and play this voice data. Following is the block diagram of the 8-Byte event trigger queue.

Figure 3. Event trigger Queue

#### Preliminary

For example: As BIOS usually has POST (Power On Self Test) program, then it will test every item step by step if no failure takes place, however, if it detects a failure on a specific item, it will hang on there. Therefore, BIOS could write timeout value to register 08h and start timer setup speech trigger event (register 09h), then is BIOS test program started. Whenever the system is hang on specific item such as DRAM testing, W83791D would say "DRAM test fails" after the timeout previously set at CR[08h]. On the contrary, if DRAM test is ok, then BIOS could update the timeout value and proceed to the next test program.

Below is the speech CPU\_MODE table of W83791D:

| CPU_MODE item | Definition                   | Vector (H) |

|---------------|------------------------------|------------|

| POI           | Reserverd                    | 0,32       |

| SLOTOCC       | CPU present or absent        | 1          |

| EVNTRAP1(TG1) | Hardware trgger1             | 2          |

| EVNTRAP2      | Hardware trgger2             | 3          |

| EVNTRAP3      | Hardware trgger3             | 4          |

| EVNTRAP4      | Hardware trgger4             | 5          |

| EVNTRAP5      | Hardware trgger5             | 6          |

| TRIGREG       | I2C setting software trigger | 80-FF      |

| INO           | Vcore(VIN0) exceed limit     | 40         |

| IN1           | VINR0(VIN1) exceed limit     | 41         |

| IN2           | (+3.3VIN)VIN2 exceed limit   | 42         |

| IN3           | (5VDD)VIN3 exceed limit      | 43         |

| IN4           | (+12VIN)VIN4 exceed limit    | 44         |

| IN5           | (-12VIN)VIN5 exceed limit    | 45         |

| IN6           | (-5VIN)VIN6 exceed limit     | 46         |

| IN7           | VSB(VIN7) exceed limit       | 47         |

| IN8           | VBAT(VIN8) exceed limit      | 48         |

| IN9           | (VINR1)VIN9 exceed limit     | 49         |

| TEMP1         | VTIN1 exceed limit           | 4A         |

| TEMP2         | VTIN2 exceed limit           | 4B         |

| TEMP3         | VTIN3 exceed limit           | 4C         |

| FAN1          | FAN1 count over limit        | 4D         |

| FAN2          | FAN2 count over limit        | 4E         |

| FAN3          | FAN3 count over limit        | 4F         |

| CHS_EV        | Case open trigger            | 50         |

Table 1. CPU\_MODE Table

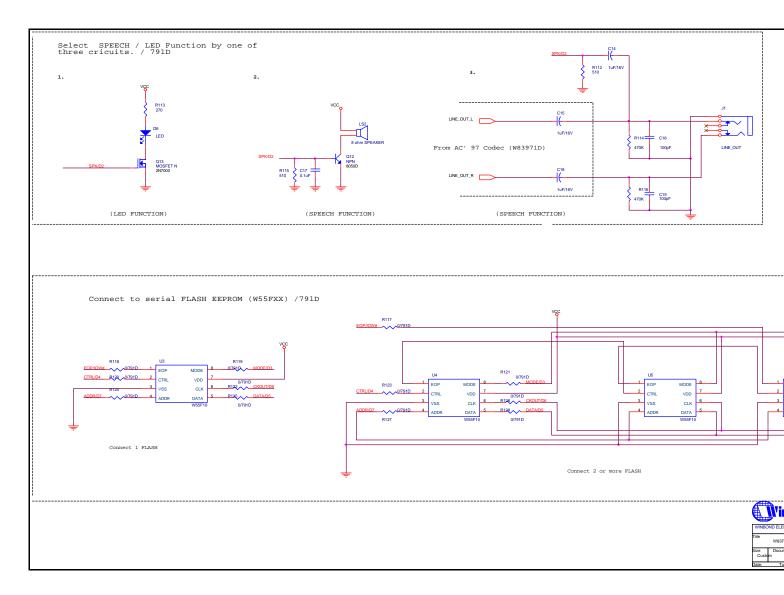

#### 6.3.3 Connection of EEPROM

As is described previously that the W83791D has connectable W55FXX to store voice data. To expand the storage capacity, users can select many W55FXX to connect with each other. The maximum capacity could be up to 16Mbit. Following is the connection chart of W55FX with W83791D.

Figure 4. Speech Function Diagram

#### 6.3.4 Speaker Output

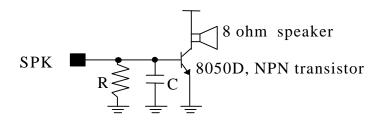

Speech output pin is a 8 bit Current D/A converter, with which loading is needed. The resistor could range from 510~1K ohm and bipolar could be a low power NPN bipolar with £ ]of 120 - 160 . Usually, an 8050D transistor is appropriate. The spec of speaker is 8  $\Omega$ . Besides, SPK can also connect to AC97 codec chip Line\_Out. C is decouple capacitor and is usually 200p- 0.01uF

Figure. 5

#### Preliminary

#### 6.4 Address Resolution Protocol (ARP) Introduction

As the W8791D is a slave device existing on the System Management Bus, it must have a unique address to prevent itself from conflicting with the other devices existing on the same bus. In order to solve the problem of address conflicts, SMBus version 2.0 introduces the concept of dynamically assigned address called Address Resolution Protocol (ARP). By such mechanism, each device existing on the SMBus will be given an unique slave address if it is a ARP-capable device. Thus, to meet the new spec, W83791D uniquely provides ARP compliant function to acquire an unique slave address.

The typical process of ARP contains several steps, including Prepare to ARP, Reset Device, Get UDID, Assign Address, and so on. Whenever the slave device accepts the command of ARP master, it must reply an Acknowledgement to the ARP master, thus the ARP master is able to carry on the next step. In order to provide a mechanism to isolate device for the purpose of address assignment, each device must implement a unique device identifier (UDID). The UDID is a 128-bit number comprised of several field, including Device Capabilities, Version Revision, Vendor ID, Device ID, Interface, Subsystem Vendor ID, Subsystem Device ID, and Vendor Specific ID. After the UDID of the device is sent to the ARP master, the ARP master will then assign a random address not in the Used Address Pool to the device

Generally speaking, there are eleven possible commands to read /write the data of SMBus device, and a slave device may use any or all of the eleven protocols to communicate. These protocols are Quick Command, Send Byte, Receive Byte, Write Byte, Write Word, Read Byte, Read word, Process Call, Block Write, and Block Write-Block Read Process Call. W83791D itself supports the Block Write-Block Read Process with PEC to communicate with ARP Master. Following is a description of the SMBus packet protocol diagrams element key.. Not all protocol elements will be present in every command, that is, not all packets are required to include the Packet Error Code.

| 1-bit | 7             | 1                                                | 1      | 8           | 1 | 8   | 1 | 1-bit |  |

|-------|---------------|--------------------------------------------------|--------|-------------|---|-----|---|-------|--|

| S     | Slave Address | Wr                                               | А      | Command     | А | PEC | А | Р     |  |

|       |               |                                                  |        |             |   |     |   |       |  |

|       | S             | Start C                                          | Condit | tion        |   |     |   |       |  |

|       | Sr            | Repeated Start Condition                         |        |             |   |     |   |       |  |

|       | Rd            | Read (bit value of 1)                            |        |             |   |     |   |       |  |

|       | Wr            | Write (bit value of 0)                           |        |             |   |     |   |       |  |

|       | А             | Acknowledge (this bit position may be '0' for an |        |             |   |     |   |       |  |

|       |               | ACK o                                            | or '1' | for a NACK) |   |     |   |       |  |

|       | Р             | Stop C                                           | ondit  | ion         |   |     |   |       |  |

|       | PEC           | Packet                                           | Erro   | r Code      |   |     |   |       |  |

|       |               | Master                                           | -to-S  | lave        |   |     |   |       |  |

|       |               | Slave-                                           | to-Ma  | aster       |   |     |   |       |  |

#### Preliminary

#### Relative command list:

| Slave address | Command        | Description            |

|---------------|----------------|------------------------|

| C2h           | 01h            | Prepare to ARP         |

| C2h           | 02h            | Reset device (general) |

| C2h           | 03h            | Get UDID (general)     |

| C2h           | 04h            | Assign address         |

| C2h           | Slave_Addr   1 | Direct Get UDID        |

| C2h           | Slave_Addr   0 | Direct Reset           |

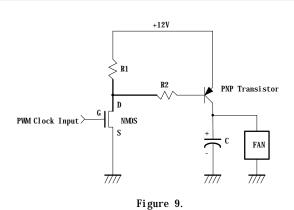

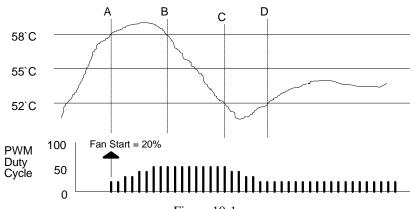

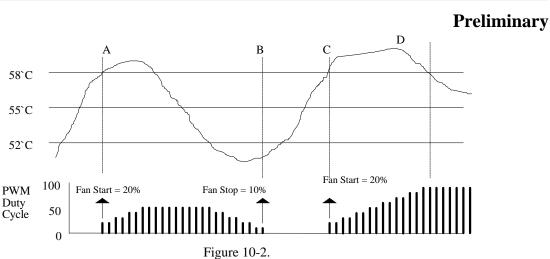

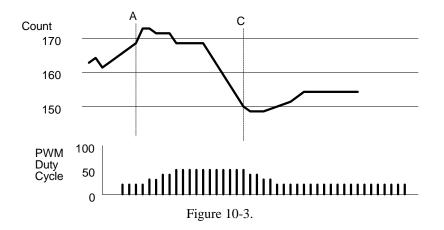

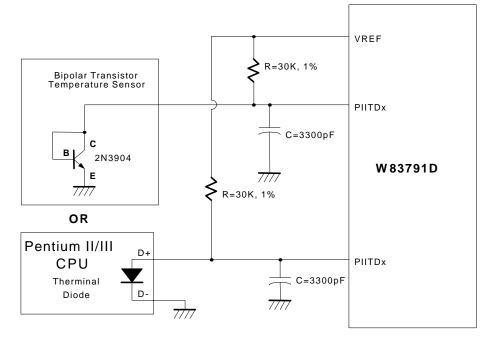

| C2h           | 05h-1Fh        | Reserved.              |