# **WM9705**

# Multimedia AC'97 CODEC with Integrated Touch Screen Controller

## **DESCRIPTION**

The WM9705 is a high-quality stereo audio codec with an integrated touch screen controller.

The audio section is compliant with the Intel AC'97 Rev 2.2 specification. It performs full-duplex 18-bit codec functions and supports variable sample rates from 8 to 48k samples/s with high signal to noise ratio. Optional AC'97 features include 3D sound enhancement, line-level outputs, stereo buffered headphone outputs, hardware sample rate conversion, primary/secondary mode operation and S/PDIF output. Headphone auto-detect, I<sup>2</sup>S output and headphone buffer on the mono output are included.

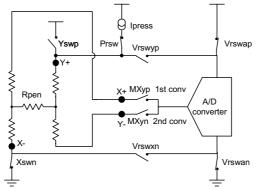

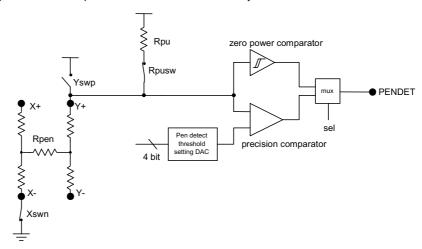

Additionally, the WM9705 integrates a complete 4-wire touch screen controller, including on-chip screen drivers, pen-down detection feature, and pressure measurement capability.

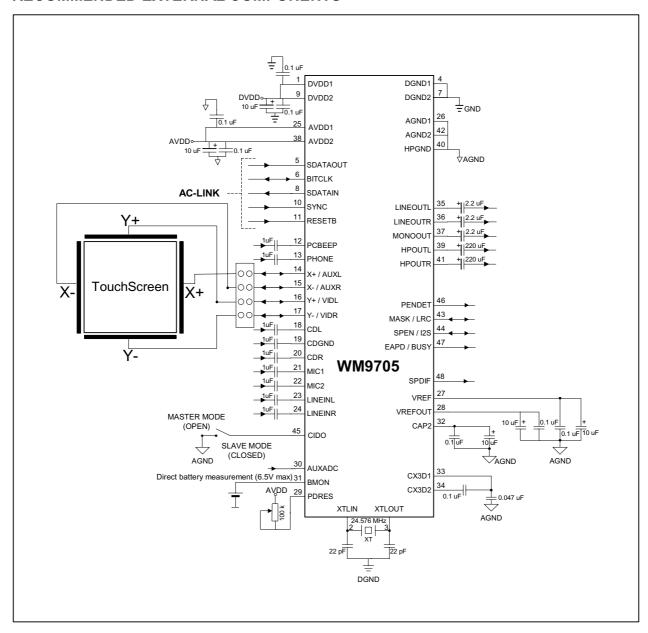

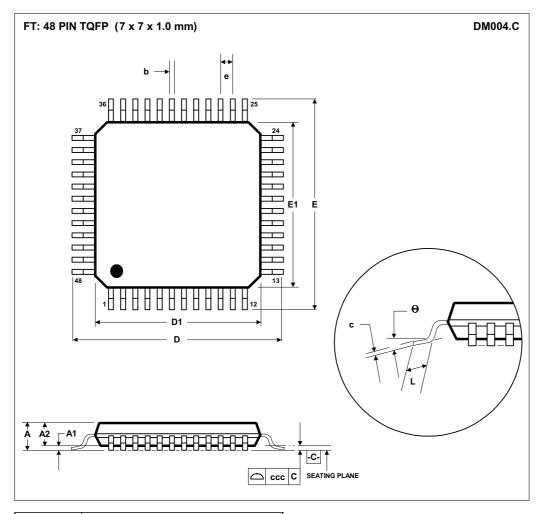

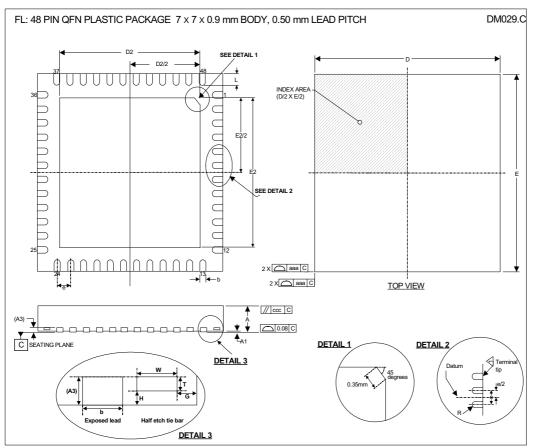

A 5-pin digital bi-directional AC-Link serial interface allows transfer of control data and DAC and ADC words to and from the AC'97 controller. The WM9705 is fully operable on 3V or 5V or mixed 3/5V supplies, and is packaged in the industry standard 48-pin TQFP package with 7mm body size, or in a smaller 7 × 7 × 0.9mm QFN.

## **FEATURES**

- AC'97 rev2.2 compliant codec with pen digitiser

- 18-bit stereo audio codecs

- On-chip sample rate conversion

- Multiple channel input mixer

- S/PDIF digital audio output

- Headphone drivers on AUX and MONO outputs

- 4-wire touch screen interface with co-ordinate and pressure measurement, and pen-down detection

- Wake-up from sleep mode on pen down

- 3V to 5V operation

- Extensive power management features including hardware power down option

- Standard AC'97 pinout in 48-pin TQFP package or 48-pin QFN package.

## **APPLICATIONS**

- Personal Digital Assistants and 'Smartphones'

- PocketPC systems

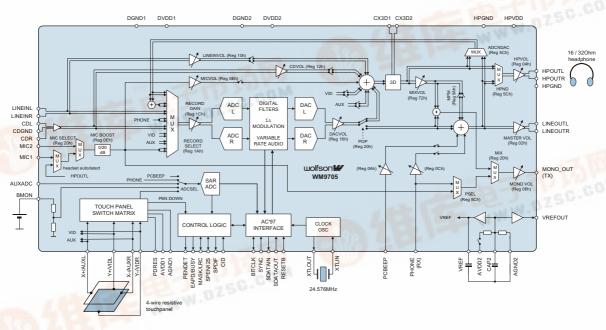

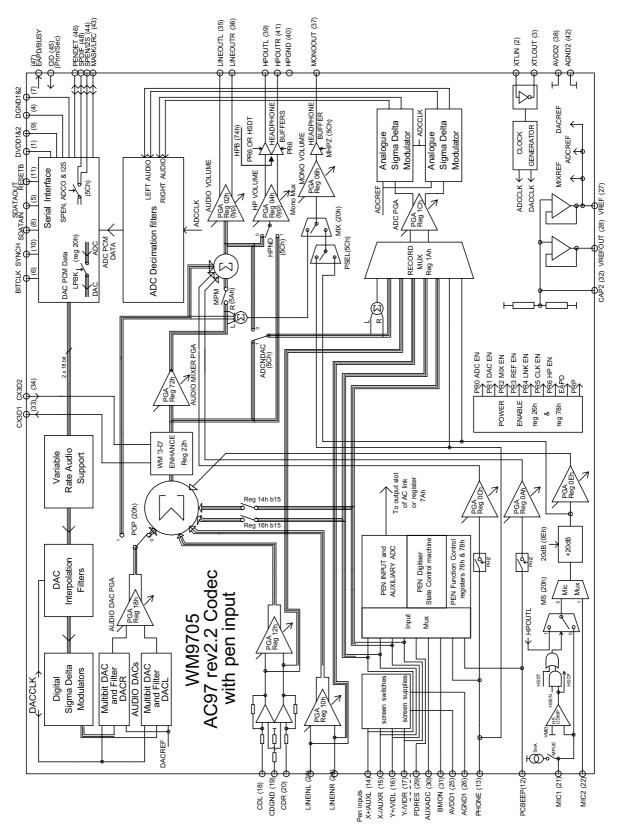

## **BLOCK DIAGRAM**

## **TABLE OF CONTENTS**

| DESCRIPTION                                                | 1  |

|------------------------------------------------------------|----|

| FEATURES                                                   | 1  |

| APPLICATIONS                                               |    |

| BLOCK DIAGRAM                                              |    |

| TABLE OF CONTENTS                                          |    |

| ORDERING INFORMATION                                       |    |

| ABSOLUTE MAXIMUM RATINGS                                   |    |

| RECOMMENDED OPERATING CONDITIONS                           |    |

| PIN CONFIGURATIONPIN CONDITIONS                            |    |

| PIN DESCRIPTION                                            |    |

| ELECTRICAL CHARACTERISTICS                                 |    |

|                                                            |    |

| POWER CONSUMPTION                                          |    |

| DETAILED TIMING DIAGRAMS                                   |    |

| AC-LINK LOW POWER MODE                                     |    |

| COLD RESETWARM RESET                                       |    |

| CLOCK SPECIFICATIONS                                       |    |

| DATA SETUP AND HOLD (50PF EXTERNAL LOAD)                   |    |

| SIGNAL RISE AND FALL TIMES                                 |    |

| DEVICE DESCRIPTION                                         |    |

| INTRODUCTION                                               |    |

| AC'97 FEATURES                                             |    |

| NON - AC'97 FEATURES                                       |    |

| PEN DIGITIZER AND AUXILIARY ADC                            |    |

| 3-D STEREO ENHANCEMENT                                     |    |

| VARIABLE SAMPLE RATE SUPPORT                               |    |

| SPDIF OR I <sup>2</sup> S DIGITAL AUDIO DATA OUTPUT        |    |

| PRIMARY/SECONDARY ID SUPPORT                               | 21 |

| HEADPHONE DRIVE AND HEADSET AUTODETECT                     |    |

| DATA SLOT MAPPING                                          | 23 |

| AC-LINK DIGITAL SERIAL INTERFACE PROTOCOL                  |    |

| AC-LINK AUDIO OUTPUT FRAME (SDATAOUT)                      |    |

| AC-LINK AUDIO INPUT FRAME (SDATAIN)                        |    |

| AC-LINK LOW POWER MODE                                     |    |

| WAKING UP THE AC-LINK                                      | 29 |

| SERIAL INTERFACE REGISTER MAP DESCRIPTION                  |    |

| REGISTER 28H – EXTENDED AUDIO ID                           | 34 |

| REGISTER 2AH – EXTENDED AUDIO STATUS AND CONTROL REGISTER  |    |

| REGISTER 2CH AND 32H – AUDIO SAMPLE RATE CONTROL REGISTERS |    |

| REGISTERS 3AH – SPDIF CONTROL REGISTER                     |    |

| VENDOR SPECIFIC REGISTERS (INDEX 5AH - 7AH)                |    |

| SERIAL INTERFACE REGISTER MAP                              | 39 |

WM9705

Production Data

| PEN DIGITISER OPERATION            | 40 |

|------------------------------------|----|

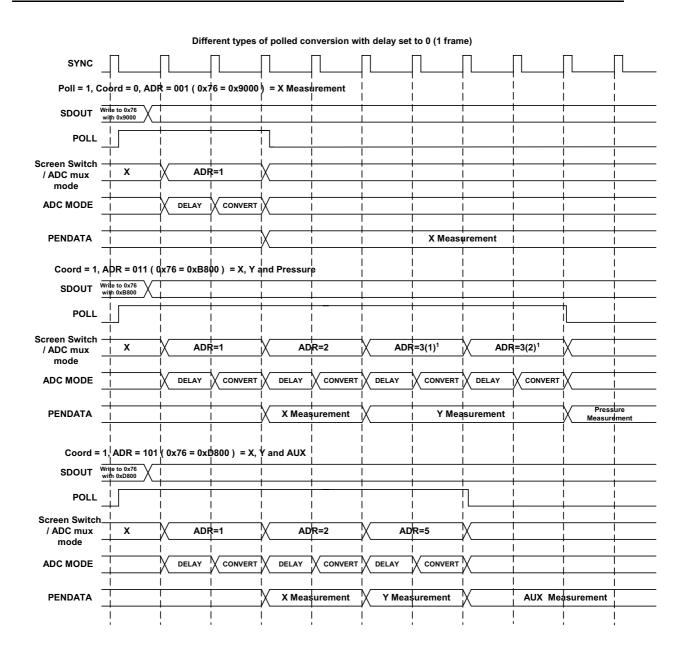

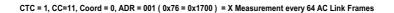

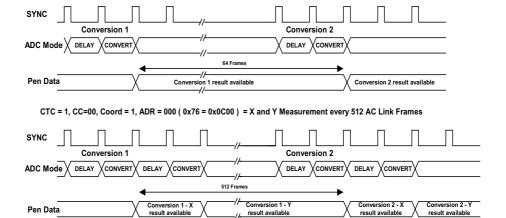

| TIMING OF PEN DIGITISER OPERATIONS | 41 |

| CONTROL OF PEN DIGITISER FUNCTIONS | 41 |

| READBACK OF PEN DIGITISER RESULTS  | 42 |

| CONVERSION CONTROL                 | 43 |

| PRESSURE MEASUREMENT               | 48 |

| MASK FUNCTION                      |    |

| STANDBY OPERATION AND WAKE-UP      | 50 |

| AUXILIARY CONVERSIONS              | 51 |

| PACKAGE DIMENSIONS - TQFP          | 53 |

| PACKAGE DIMENSIONS - QFN           | 54 |

| IMPORTANT NOTICE                   | 55 |

| ADDRESS:                           |    |

#### ORDERING INFORMATION

| DEVICE        | TEMP. RANGE | PACKAGE                                | MOISTURE<br>SENSITIVITY LEVEL |

|---------------|-------------|----------------------------------------|-------------------------------|

| XWM9705EFT/V  | -25 to 85°C | 48-pin TQFP                            | MSL1                          |

| WM9705SEFT/V  | -25 to 85°C | 48-pin TQFP<br>(lead free)             | MSL1                          |

| XWM9705EFT/RV | -25 to 85°C | 48-pin TQFP<br>(tape and reel)         | MSL1                          |

| WM9705SEFT/RV | -25 to 85°C | 48-pin TQFP (lead free, tape and reel) | MSL1                          |

| DEVICE        | TEMP. RANGE | PACKAGE                               | MOISTURE<br>SENSITIVITY LEVEL |

|---------------|-------------|---------------------------------------|-------------------------------|

| XWM9705EFL/V  | -25 to 85°C | 48-pin QFN                            | MSL3                          |

| WM9705SEFL/V  | -25 to 85°C | 48-pin QFN<br>(lead free)             | MSL3                          |

| XWM9705EFL/RV | -25 to 85°C | 48-pin QFN<br>(tape and reel)         | MSL3                          |

| WM9705SEFL/RV | -25 to 85°C | 48-pin QFN (lead free, tape and reel) | MSL3                          |

Note:

Reel quantity = 2,200

## **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

#### Note:

The TQFP version is classified as MSL1 and does not require to be drybagged but will be supplied as such, labelled as MSL1.

| CONDITION                                       | MIN        | MAX        |

|-------------------------------------------------|------------|------------|

| Digital supply voltage                          | -0.3V      | +7V        |

| Analogue supply voltage                         | -0.3V      | +7V        |

| Voltage range digital inputs                    | DVSS-0.3V  | DVDD +0.3V |

| Voltage range analogue inputs                   | AVDD -0.3V | AVDD +0.3V |

| Operating temperature range, T <sub>A</sub>     | -25°C      | +85°C      |

| Storage temperature after soldering             | -65°C      | +150°C     |

| Package body temperature (soldering 10 seconds) |            | +240°C     |

| Package body temperature (soldering 2 minutes)  |            | +183°C     |

## **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                        | SYMBOL                 | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|----------------------------------|------------------------|-----------------|------|-----|------|------|

| Digital supply range             | DVDD1, DVDD2           |                 | 2.7  |     | 5.5  | V    |

| Analogue supply range            | AVDD1, AVDD2           |                 | 2.7  |     | 5.5  | V    |

| Digital ground                   | DGND1, DGND2           |                 |      | 0   |      | V    |

| Analogue ground                  | AGND1, AGND2,<br>HPGND |                 |      | 0   |      | V    |

| Difference AGND to DGND – Note 1 |                        |                 | -0.3 | 0   | +0.3 | V    |

| Difference AVDD to DVDD – Note 2 |                        |                 | -0.3 |     | 5.5  | V    |

## Note:

- AGND is normally the same as DGND and HPGND

AVDD should be greater than or equal to DVDD

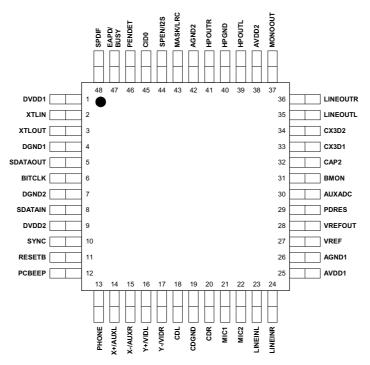

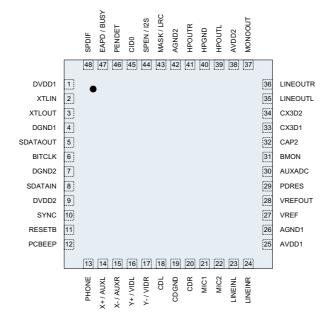

## **PIN CONFIGURATION**

Figure 1 TQFP Pinout

Figure 2 QFN Pinout

## **PIN DESCRIPTION**

| PIN | 48 PIN QFN            | 48 PIN TQFP           | TYPE            | DESCRIPTION                                                         |

|-----|-----------------------|-----------------------|-----------------|---------------------------------------------------------------------|

| 1   | DVDD1                 | DVDD1                 | Supply          | Digital positive supply                                             |

| 2   | XTLIN                 | XTLIN                 | Digital input   | Clock crystal connection or clock input (XTAL not used)             |

| 3   | XTLOUT                | XTLOUT                | Digital output  | Clock crystal connection                                            |

| 4   | DGND1                 | DGND1                 | Supply          | Digital ground supply                                               |

| 5   | SDATAOUT              | SDATAOUT              | Digital input   | Serial data input                                                   |

| 6   | BITCLK                | BITCLK                | Digital output  | Serial interface clock output to AC'97 controller                   |

|     |                       |                       | Digital input   | or input from AC'97 primary codec                                   |

| 7   | DGND2                 | DGND2                 | Supply          | Digital ground supply                                               |

| 8   | SDATAIN               | SDATAIN               | Digital output  | Serial data output to AC'97 controller                              |

| 9   | DVDD2                 | DVDD2                 | Supply          | Digital positive supply                                             |

| 10  | SYNC                  | SYNC                  | Digital input   | Serial interface sync pulse from AC'97 controller                   |

| 11  | RESETB                | RESETB                | Digital input   | NOT reset input (active low, resets registers)                      |

| 12  | PCBEEP                | PCBEEP                | Analogue input  | Mixer input, typically for PCBEEP signal (also input to AUX ADC)    |

| 13  | PHONE                 | PHONE                 | Analogue input  | PHONE input (also input to AUX ADC)                                 |

| 14  | X+/AUXL               | X+/AUXL               | Analogue I/O    | Pen X+ channel screen driver/input. (or AUXL mixer input)           |

| 15  | X-/AUXR               | X-/AUXR               | Analogue I/O    | Pen X- channel screen driver/input (or AUXR mixer input)            |

| 16  | Y+/VIDL               | Y+/VIDL               | Analogue I/O    | Pen Y+ channel screen driver/input (or VIDL mixer input)            |

| 17  | Y-/VIDR               | Y-/VIDR               | Analogue I/O    | Pen Y- channel screen driver/input (or VIDR mixer input)            |

| 18  | CDL                   | CDL                   | Analogue input  | Mixer input, typically for CD signal                                |

| 19  | CDGND                 | CDGND                 | Analogue input  | CD input common mode reference (ground)                             |

| 20  | CDR                   | CDR                   | Analogue input  | Mixer input, typically for CD signal                                |

| 21  | MIC1                  | MIC1                  | Analogue input  | Mixer input with extra gain if required – also HSET detect input    |

| 22  | MIC2                  | MIC2                  | Analogue input  | Mixer input with extra gain if required                             |

| 23  | LINEINL               | LINEINL               | Analogue input  | Mixer input, typically for LINE signal                              |

| 24  | LINEINR               | LINEINR               | Analogue input  | Mixer input, typically for LINE signal                              |

| 25  | AVDD1                 | AVDD1                 | Supply          | Analogue positive supply for screen drivers                         |

| 26  | AGND1                 | AGND1                 | Supply          | Analogue ground supply for screen drivers                           |

| 27  | VREF                  | VREF                  | Analogue output | Internal reference (buffered CAP2)                                  |

| 28  | VREFOUT               | VREFOUT               | Analogue output | Reference for microphones (buffered CAP2)                           |

| 29  | PDRES                 | PDRES                 | Analogue input  | Pen Down Detect Pull-up external resistor connection                |

| 30  | AUXADC                | AUXADC                | Analogue input  | AUX signal input to digitiser ADC                                   |

| 31  | BMON                  | BMON                  | Analogue input  | Battery input to ADC                                                |

| 32  | CAP2                  | CAP2                  | Analogue I/O    | Reference input/output; pulls to midrail if not overdriven          |

| 33  | CX3D1                 | CX3D1                 | Analogue output | Output pin for 3D difference signal                                 |

| 34  | CX3D2                 | CX3D2                 | Analogue input  | Input pin for 3D difference signal                                  |

| 35  | LINEOUTL              | LINEOUTL              | Analogue output | Main analogue output for left channel                               |

| 36  | LINEOUTR              | LINEOUTR              | Analogue output | Main analogue output for right channel                              |

| 37  | MONOOUT               | MONOOUT               | Analogue output | Main mono output                                                    |

| 38  | AVDD2                 | AVDD2                 | Supply          | Analogue positive supply                                            |

| 39  | HPOUTL                | HPOUTL                | Analogue output | Left channel line level output (or headphone, or headset mic input) |

| 40  | HPGND                 | HPGND                 | Supply          | Headphone ground supply                                             |

| 41  | HPOUTR                | HPOUTR                | Analogue output | Right channel line level output (or headphone)                      |

| 42  | AGND2                 | AGND2                 | Supply          | Analogue ground supply                                              |

| 43  | MASK/LRC              | MASK/LRC              | Digital bidir   | MASK input signal to delay PEN conversions (or LRCLK output)        |

| 44  | SPEN/I <sup>2</sup> S | SPEN/I <sup>2</sup> S | Digital bidir   | SPDIF hardware enable pin and I <sup>2</sup> S data output          |

| 45  | CID0                  | CID0                  | Digital input   | Primary/Secondary ID select (internal pull-up) Hi = Primary         |

| 46  | PENDET                | PENDET                | Digital output  | Pen Down Detection flag OR Headset detect output                    |

| 47  | EAPD/BUSY             | EAPD/BUSY             | Digital output  | External amplifier powerdown or BUSY output flag from Pen ADC       |

| 48  | SPDIF                 | SPDIF                 | Digital output  | S/PDIF output                                                       |

## **ELECTRICAL CHARACTERISTICS**

#### Test Characteristics:

AVDD = 3.3V, DVDD = 3.3V, 48kHz audio sampling,  $T_A$  = 25°C, unless otherwise stated.

| PARAMETER                                      | SYMBOL          | TEST CONDITIONS                        | MIN            | TYP               | MAX            | UNIT    |

|------------------------------------------------|-----------------|----------------------------------------|----------------|-------------------|----------------|---------|

| Digital Logic Levels (DVDD = 3.3               | BV)             | •                                      |                |                   |                |         |

| Input LOW level                                | V <sub>IL</sub> |                                        | DGND - 0.3     |                   | 0.8            | V       |

| Input HIGH level                               | V <sub>IH</sub> |                                        | 2.2            |                   | DVDD + 0.3     | V       |

| Output LOW                                     | V <sub>OL</sub> | I Load = 2mA                           |                |                   | 0.10 x DVDD    | V       |

| Output HIGH                                    | V <sub>OH</sub> | I Load = -2mA                          | 0.90 x DVDD    |                   |                | V       |

| Analogue Audio I/O Levels (Inpu                | ıt Signals on a | ny audio inputs, Outpu                 | ts on LINEOL   | JT L, R and M     | ONO and HPO    | UT L,R) |

| Input level                                    |                 | Minimum input impedance = 10k          | AGND<br>-100mV |                   | AVDD<br>+100mV | V       |

| Output level to LINEOUT L,R                    |                 | Into 10kΩ load                         | AGND<br>+300mV | Near rail to rail | AVDD<br>-300mV | V       |

| Output level to HPOUT L,<br>HPOUTR and MONOOUT |                 | Into 16Ω load                          | AGND<br>+300mV | Near rail to rail | AVDD<br>-300mV | V       |

| Reference Levels                               |                 |                                        |                | •                 |                |         |

| Reference input/output                         | CAP2            |                                        | 0.47 AVDD      | 0.50 AVDD         | 0.53 AVDD      | V       |

| CAP2 impedance                                 |                 |                                        |                | 75                |                | kΩ      |

| Mixer reference                                | VREF            |                                        |                | Buffered<br>CAP2  |                | V       |

| MIC reference                                  | VREFOUT         |                                        |                | Buffered<br>CAP2  |                | V       |

| MIDBUFF current source (pins VREF and VREFOUT) |                 | AVDD = 3.3V                            | 5              | 10                |                | mA      |

| MIDBUFF current sink (pins VREF and VREFOUT)   |                 | AVDD = 3.3V                            | -5             | -10               |                | mA      |

| AUDIO DAC to Line-out (10kΩ lo                 | ad)             | 1                                      | -11            | ı                 |                |         |

| SNR A-weighted (Note 2)                        |                 |                                        | 85             | 91                |                | dB      |

| Full scale output voltage                      |                 | VREF = 1.65V                           |                | 0.7               |                | Vrms    |

| Total Harmonic Distortion +<br>Noise           | THD+N           | -3dBfs input                           |                | -84<br>0.006      | -74<br>0.02    | dB<br>% |

| PSRR                                           |                 | 20 to 20kHz, without supply decoupling |                | -40               |                | dB      |

| AUDIO ADC                                      |                 |                                        |                |                   |                |         |

| ADC input for full scale output                |                 | VREF = 1.65V                           |                | 0.7               |                | Vrms    |

| Signal to Noise Ratio<br>A-weighted (Note 2)   | SNR             |                                        | 80             | 86                |                | dBfs    |

| Total Harmonic Distortion+Noise                | THD+N           | -6dBfs input                           |                | -79               | -72            | dB      |

| Power Supply Rejection Ratio                   | PSRR            | 20 to 20kHz, without supply decoupling |                | -40               | , , ,          | dB      |

| Digital Filter Characteristics                 |                 | 1 2-FF-7 = 0000Fm.ig                   | 1              | 1                 | <u> </u>       |         |

| Frequency response                             |                 |                                        | 20             |                   | 19,200         | Hz      |

| Transition band                                |                 |                                        | 19,200         |                   | 28,800         | Hz      |

| Stop band                                      |                 |                                        | 28,800         |                   | 1              | Hz      |

| Stop band attenuation                          |                 | ADC                                    | -74            |                   |                | dB      |

|                                                |                 | DAC                                    | -40            |                   |                |         |

Test Characteristics: AVDD = 3.3V, DVDD = 3.3V, 48kHz audio sampling,  $T_A$  = 25 $^{\circ}$ C, unless otherwise stated.

| PARAMETER                              | SYMBOL           | TEST CONDITIONS                               | MIN  | TYP          | MAX      | UNIT    |

|----------------------------------------|------------------|-----------------------------------------------|------|--------------|----------|---------|

| Mixer Inputs to Line-out (10k $\Omega$ | load)            |                                               |      |              |          |         |

| Maximum input voltage                  |                  |                                               | AGND | 0.7          | AVDD     | Vrms    |

| Maximum output voltage                 |                  | on LINEOUT                                    |      | 0.7          |          | Vrms    |

| Signal to Noise Ratio                  | SNR              | CD inputs                                     | 90   | 92           |          | dB      |

| A-weighted (Note 2)                    |                  | Other inputs                                  | 82   | 93           |          |         |

| Total Harmonic Distortion +            | THD+N            | CD and LINE inputs                            |      | -87          | -77      | dB      |

| Noise                                  |                  | ·                                             |      | 0.0044       | 0.014    | %       |

| -1dBfs input                           |                  | PHONE input                                   |      | -82          | -71      |         |

|                                        |                  |                                               |      | 0.008        | 0.028    |         |

|                                        |                  | MIC1 input                                    |      | -82          | -71      |         |

|                                        |                  |                                               |      | 0.008        | 0.028    |         |

|                                        |                  | MIC2 input                                    |      | -90          | -71      |         |

|                                        |                  |                                               |      | 0.003        | 0.028    |         |

|                                        |                  | PCBEEP input                                  |      | -78          | -67      |         |

|                                        |                  |                                               |      | 0.013        | 0.045    |         |

| Input impedance (CD inputs)            |                  | At any gain                                   |      | 15           |          | kΩ      |

| Input impedance (other mixer           |                  | At max gain                                   | 10   | 20           |          | kΩ      |

| inputs)                                |                  | At 0db gain                                   | 50   | 100          |          | kΩ      |

| Input impedance MIC inputs             |                  | At max gain                                   | 10   | 20           |          | kΩ      |

|                                        |                  | At 0db gain                                   | 55   | 100          |          | kΩ      |

| Power Supply Rejection Ratio           | PSRR             | 20 to 20kHz, without                          |      | -40          |          | dB      |

| Handahana Buffan (alian HBOH           | I UDOUD          | supply decoupling                             |      |              | <u> </u> |         |

| Headphone Buffer (pins HPOU            | IL, HPOUR an     | ia MONOOUT)                                   |      |              | 1        | 1 1/2   |

| Maximum output voltage                 | <del>  _</del> _ |                                               |      | 0.7          |          | Vrms    |

| Max Output Power (Note 1)              | Po               | RL = 32Ω                                      |      | 30           |          | mW      |

| ONID (N. 1. O)                         |                  | $RL = 16\Omega$                               | 0.5  | 40           |          | mW      |

| SNR (Note 2)                           |                  | A-weighted                                    | 85   | 92           |          | dB      |

| Total Harmonic Distortion + Noise      | THD+N            | 1kHz, $R_L = 32\Omega$ @ $P_O = 10$ mW rms    |      | -80          |          | dB      |

| Noise                                  |                  |                                               |      | 0.01         |          | %       |

|                                        |                  | 1kHz, $R_L = 32\Omega@P_0 = 20$ mW rms        |      | -77<br>0.014 |          | dB<br>% |

|                                        |                  | 1kHz, R <sub>L</sub> = 16Ω @ P <sub>O</sub> = |      | -76dB        |          |         |

|                                        |                  | 10mW rms                                      |      | 0.016        |          | dB<br>% |

|                                        |                  | 1kHz, R <sub>L</sub> = 16Ω@ P <sub>O</sub> =  |      | -75dB        |          | dB      |

|                                        |                  | 20mW rms                                      |      | 0.018        |          | %       |

| Power Supply Rejection Ratio           | PSRR             | 20 to 20kHz, without supply decoupling        |      | -40          |          | dB      |

| Clocks                                 | •                | ,                                             |      | •            | •        | •       |

| Crystal clock                          |                  |                                               |      | 24.576       |          | MHz     |

| BITCLK frequency                       |                  |                                               |      | 12.288       |          | MHz     |

| SYNC frequency                         |                  |                                               |      | 48.0         |          | KHz     |

#### **Test Characteristics:**

AVDD = 3.3V, DVDD = 3.3V, MCLK = 24.576MHz, T<sub>A</sub> = 25°C, unless otherwise stated.

| PARAMETER                                        | SYMBOL   | TEST CONDITIONS      | MIN   | TYP     | MAX   | UNIT    |

|--------------------------------------------------|----------|----------------------|-------|---------|-------|---------|

| PEN and AUXILIARY INPUT ADO                      |          | •                    |       | •       | 1     | •       |

| Resolution                                       |          |                      |       | 12      |       | Bits    |

| Differential non-linearity error                 | DNL      |                      |       | +/-0.25 |       | LSB     |

| Integral non-linearity error                     | INL      |                      |       | +/-2    |       | LSB     |

| Offset error                                     |          |                      |       | +/-4    |       | LSB     |

| Gain error                                       |          |                      |       | +/-4    |       | LSB     |

| Noise                                            |          |                      |       | 500     |       | μVrms   |

| Conversion time                                  |          |                      |       | 20.8    |       | μsec    |

| Acquisition time                                 |          |                      |       | 15      |       | μsec    |

| Throughput rate                                  |          |                      |       |         | 48    | kHz     |

| Multiplexer settling time                        |          |                      |       | 500     |       | nsec    |

| ADC positive reference                           |          | X conversion         |       | X+ pin  |       | V       |

|                                                  |          | Y conversion         |       | Y+ pin  |       |         |

|                                                  |          | auxiliary conversion |       | AVDD1   |       |         |

| ADC negative reference                           |          | X conversion         |       | X- pin  |       | V       |

|                                                  |          | Y conversion         |       | Y- pin  |       |         |

|                                                  |          | auxiliary conversion |       | AGND1   |       |         |

| ADC sampling capacitance                         |          |                      |       | 2       |       | pF      |

| AUXADC input range (fullscale)                   |          |                      | AGND1 |         | AVDD1 |         |

| AUXADC input leakage current                     |          |                      |       | +/-0.5  |       | μΑ      |

| BMON input range                                 |          |                      | AGND1 |         | 6.5V  |         |

| BMON input impedance                             |          | at sampling time     |       | 30      |       | kΩ      |

| BMON effective input                             |          | 93.75Hz sample rate  |       | 7.7     |       | MΩ      |

| impedance (Note 3)                               |          |                      |       |         |       |         |

| BMON input gain                                  |          |                      |       | 1/3     |       |         |

| PEN INTERFACE                                    |          |                      |       | T       | I     | T       |

| Full scale input range                           |          |                      |       | AVDD    |       | V       |

| Absolute input range                             |          | Positive input       |       | AVDD    |       | V       |

| Canacitanas                                      |          | Negative input       |       | 5       |       |         |

| Capacitance                                      |          |                      |       | -       |       | pF<br>^ |

| Leakage current                                  |          |                      |       | +/-0.5  |       | μΑ      |

| Screen switch on resistance                      |          | DII - O              |       | 20      |       | Ω       |

| Pressure measurement current                     |          | PIL = 0              |       | 200     |       | μΑ      |

| External Pen-detect pull up resistor value       |          | PIL = 1              | 1     | 10      | 100   | kΩ      |

| Pen Detect Comparator<br>Threshold DAC Range     | PDDACR   |                      | 0.1   |         | 1.65  | V       |

| Pen Detect Comparator<br>Threshold DAC step size | PDDACLSB |                      |       | 0.1     |       | V       |

## Note:

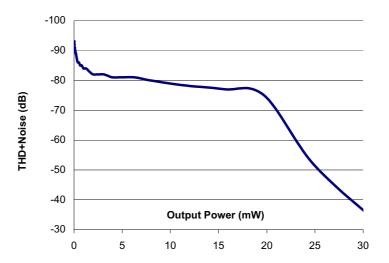

- 1. Harmonic distortion on the headphone output decreases with output power see Figure 3.

- 2. SNR is the ratio of 0dB signal amplitude to noise floor with no signal present (all 0s input code to DACs).

- 3. The input impedance of the BMON input is 30k to ground when the ADC is sampling and hi-Z when it is not. The effective input resistance is calculated dependant on how often the battery is sampled by the user. 7.7MΩ is the effective impedance if the battery is sampled once every 512 frames. For a fuller description of this and information on how to calculate the effect input impedance please see the section on auxiliary conversions on pages 46.

- 4. ADC sampling capacitance allows the user to calculate the minimum external capacitance required for a stable ADC value.

Figure 3 Distortion Versus Power on Headphone Outputs, using 32 $\Omega$  Load and AVDD = HPVDD = 3.3V

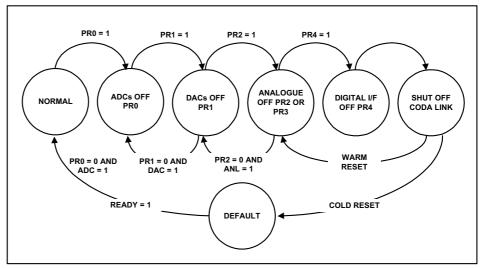

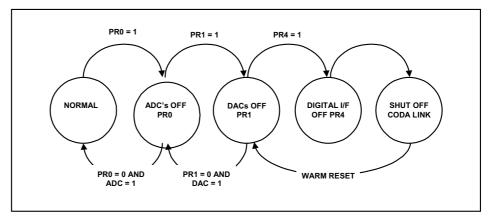

## **POWER CONSUMPTION**

| MODE<br>DESCRIPTION               | PR0 | PR1 | PR2 | PR3 | PR4 | PR5 | PR6 | EAPD | DIGITISER PD<br>REG 78H (PRP) | ISER PD<br>78H (PRP) | ORD MUX     | DIGITISER PD REG 78H (PRP) RECORD MUX | CURRENT<br>CONSUMPTION |  |  |

|-----------------------------------|-----|-----|-----|-----|-----|-----|-----|------|-------------------------------|----------------------|-------------|---------------------------------------|------------------------|--|--|

|                                   |     |     |     |     | _   |     |     | ш    | DIGIT<br>REG 7                | RECC                 | AVDD<br>(mA | DVDD<br>(mA)                          | TOTAL<br>POWER<br>(mW) |  |  |

| Record and Playback               | (   |     |     |     |     |     |     |      |                               |                      |             |                                       |                        |  |  |

| Mic Record (note 1)               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Х    | 00                            | 000L<br>000R         | 14.8        | 14.3                                  | 96                     |  |  |

| Other Input Record                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Х    | 00                            | 001L<br>001R         | 17.7        | 14.3                                  | 105.6                  |  |  |

| Other Input Record<br>PR6         | 0   | 0   | 0   | 0   | 0   | 0   | 1   | Х    | 00                            | 001L<br>001R         | 16.3        | 14.3                                  | 101                    |  |  |

| Other Input Record<br>PR6 and PR2 | 0   | 0   | 1   | 0   | 0   | 0   | 1   | Х    | 00                            | 001L<br>001R         | 10.7        | 14.3                                  | 82.5                   |  |  |

| Other Input Record PR6 and PR3    | 0   | 0   | 0   | 1   | 0   | 0   | 1   | Х    | 00                            | 001L<br>001R         | 0.5         | 14.1                                  | 48.2                   |  |  |

| Playback Only                     |     |     | •   | •   |     |     |     |      | •                             |                      | •           | •                                     |                        |  |  |

| Low Power<br>Playback (note 2)    | 1   | 0   | 1   | 0   | 0   | 0   | 0   | Х    | 00                            | 001L<br>001R         | 5.5         | 11.5                                  | 56.1                   |  |  |

| Playback Only                     | 1   | 0   | 0   | 0   | 0   | 0   | 0   | Х    | 00                            | 001L<br>001R         | 11.1        | 11.5                                  | 74.6                   |  |  |

| Playback Only<br>PR6              | 1   | 0   | 0   | 0   | 0   | 0   | 1   | Х    | 00                            | 001L<br>001R         | 9.7         | 11.5                                  | 70                     |  |  |

| Playback Only<br>PR6 and PR2      | 1   | 0   | 1   | 0   | 0   | 0   | 1   | Х    | 00                            | 001L<br>001R         | 4.0         | 11.5                                  | 51.2                   |  |  |

| Playback Only<br>PR6 and PR3      | 1   | 0   | 0   | 1   | 0   | 0   | 1   | Х    | 00                            | 001L<br>001R         | 0.4         | 11.5                                  | 39.3                   |  |  |

| Record Only                       |     |     |     |     |     |     |     |      |                               |                      |             |                                       |                        |  |  |

| Mic Record (note 1)               | 0   | 1   | 0   | 0   | 0   | 0   | 0   | Х    | 00                            | 000L<br>000R         | 12.9        | 13.3                                  | 86.5                   |  |  |

| Other Input Record                | 0   | 1   | 0   | 0   | 0   | 0   | 0   | Х    | 00                            | 100L<br>100R         | 15.8        | 13.3                                  | 96                     |  |  |

| Other Input Record<br>PR6         | 0   | 1   | 0   | 0   | 0   | 0   | 1   | Х    | 00                            | 100L<br>100R         | 14.3        | 11.3                                  | 84.5                   |  |  |

| Other Input Record<br>PR6 and PR2 | 0   | 1   | 1   | 0   | 0   | 0   | 1   | Х    | 00                            | 100L<br>100R         | 7.2         | 13.3                                  | 67.7                   |  |  |

| Other Input Record<br>PR6 and PR3 | 0   | 1   | 0   | 1   | 0   | 0   | 1   | Х    | 00                            | 100L<br>100R         | 0.3         | 12.9                                  | 43.6                   |  |  |

| Power Down                        |     |     | ı   | 1   |     | 1   | 1   | 1    |                               |                      | ı           | ı                                     |                        |  |  |

| Power Down<br>(note 3)            | 1   | 1   | 1   | 1   | 1   | 1   | 1   | Х    | 00                            | XXXL<br>XXXR         | 0.0001      | 0.002                                 | 0.007                  |  |  |

| Pen Digitiser                     |     |     | 1   | 1   |     |     |     |      |                               |                      | 1           | ı                                     |                        |  |  |

| Pen Digitiser<br>(Note 4)         | 1   | 1   | 1   | 1   | 0   | 1   | 1   | Х    | 11                            | XXXL<br>XXXR         | 0.1         | 3.6                                   | 12.2                   |  |  |

#### Notes:

- 1. When the ADC input mux is set to mic input to BOTH ADC channels, (SR2-0 and SL2-0 both set to '0'), one ADC is shared between both channels and the other is powered off to save current. The same digital data is output to both slots.

- 2. The POP bit (reg 20h) also needs to be set for this mode.

- $3. \quad \text{These values are recorded with no external clocks applied to the WM9705}.$

- 4. Pen active duty cycle is approximately 10%. Average analogue current consumption is approximately 10% of stated figure.

## **DETAILED TIMING DIAGRAMS**

## Test Characteristics:

AVDD = 3.3V, DVDD = 3.3V, AGND = 0V ...... $T_A = 0^{\circ}$ C to +70°C, unless otherwise stated.

All measurements are taken at 10% to 90% DVDD, unless otherwise stated. All the following timing information is guaranteed, not tested

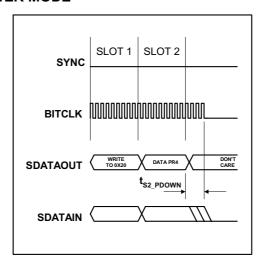

## **AC-LINK LOW POWER MODE**

Figure 4 AC-Link Powerdown Timing

| PARAMETER                       | SYMBOL                | MIN | TYP | MAX | UNIT |

|---------------------------------|-----------------------|-----|-----|-----|------|

| End of slot 2 to BITCLK SDATAIN | t <sub>S2_PDOWN</sub> |     |     | 1.0 | μs   |

| low                             |                       |     |     |     |      |

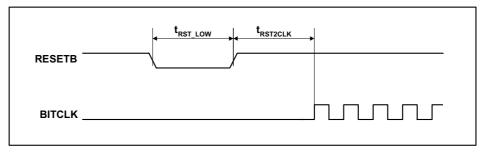

## **COLD RESET**

Figure 5 Cold Reset Timing

#### Note:

For correct operation SDATAOUT and SYNC must be held LOW for entire RESETB active low period otherwise the device may enter test mode. See AC'97 specification or Wolfson applications note WAN104 for more details.

| PARAMETER                     | SYMBOL               | MIN   | TYP | MAX | UNIT |

|-------------------------------|----------------------|-------|-----|-----|------|

| RESETB active low pulse width | t <sub>RST_LOW</sub> | 1.0   |     |     | μs   |

| RESETB inactive to BITCLK     | t <sub>RST2CLK</sub> | 162.8 |     |     | ns   |

| startup delay                 |                      |       |     |     |      |

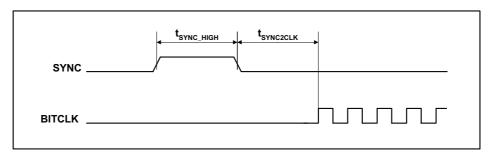

## **WARM RESET**

Figure 6 Warm Reset Timing

| PARAMETER                       | SYMBOL                | MIN   | TYP | MAX | UNIT |

|---------------------------------|-----------------------|-------|-----|-----|------|

| SYNC active high pulse width    | tsync_high            |       | 1.3 |     | μs   |

| SYNC inactive to BITCLK startup | t <sub>SYNC2CLK</sub> | 162.4 |     |     | ns   |

| delay                           |                       |       |     |     |      |

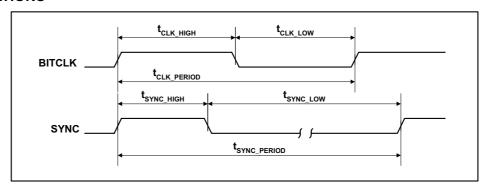

## **CLOCK SPECIFICATIONS**

Figure 7 Clock Specifications (50pF External Load)

| PARAMETER                        | SYMBOL                   | MIN | TYP    | MAX | UNIT |

|----------------------------------|--------------------------|-----|--------|-----|------|

| BITCLK frequency                 |                          |     | 12.288 |     | MHz  |

| BITCLK period                    | t <sub>CLK_PERIOD</sub>  |     | 81.4   |     | ns   |

| BITCLK output jitter             |                          |     |        | 750 | ps   |

| BITCLK high pulse width (Note 1) | t <sub>CLK_HIGH</sub>    | 36  | 40.7   | 45  | ns   |

| BITCLK low pulse width (Note 1)  | t <sub>CLK_LOW</sub>     | 36  | 40.7   | 45  | ns   |

| SYNC frequency                   |                          |     | 48.0   |     | kHz  |

| SYNC period                      | t <sub>SYNC_PERIOD</sub> |     | 20.8   |     | μs   |

| SYNC high pulse width            | tsync_high               |     | 1.3    |     | μs   |

| SYNC low pulse width             | t <sub>SYNC_LOW</sub>    |     | 19.5   |     | μs   |

## Note:

Worst case duty cycle restricted to 45/55.

## DATA SETUP AND HOLD (50PF EXTERNAL LOAD)

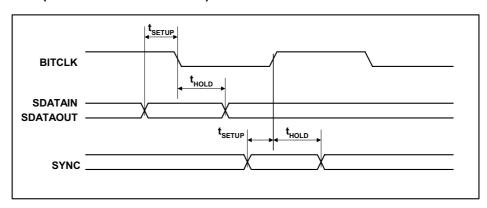

Figure 8 Data Setup and Hold (50pF External Load)

#### Note

Setup and hold time parameters for SDATAIN are with respect to AC'97 Controller.

| PARAMETER                        | SYMBOL             | MIN | TYP | MAX | UNIT |

|----------------------------------|--------------------|-----|-----|-----|------|

| Setup to falling edge of BITCLK  | t <sub>SETUP</sub> | 10  |     |     | ns   |

| Hold from falling edge of BITCLK | t <sub>HOLD</sub>  | 10  |     |     | ns   |

## **SIGNAL RISE AND FALL TIMES**

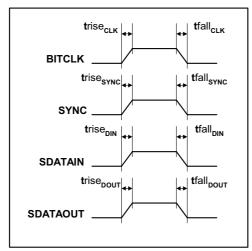

Figure 9 Signal Rise and Fall Times (50pF External Load)

| PARAMETER          | SYMBOL                | MIN | TYP | MAX | UNIT |

|--------------------|-----------------------|-----|-----|-----|------|

| BITCLK rise time   | trise <sub>CLK</sub>  | 2   |     | 6   | ns   |

| BITCLK fall time   | tfall <sub>CLK</sub>  | 2   |     | 6   | ns   |

| SYNC rise time     | trise <sub>SYNC</sub> | 2   |     | 6   | ns   |

| SYNC fall time     | tfall <sub>SYNC</sub> | 2   |     | 6   | ns   |

| SDATAIN rise time  | trise <sub>DIN</sub>  | 2   |     | 6   | ns   |

| SDATAIN fall time  | tfall <sub>DIN</sub>  | 2   |     | 6   | ns   |

| SDATAOUT rise time | triseDOUT             | 2   |     | 6   | ns   |

| SDATAOUT fall time | tfall <sub>DOUT</sub> | 2   |     | 6   | ns   |

#### **DEVICE DESCRIPTION**

#### INTRODUCTION

This specification describes the WM9705 audio codec, which is designed to be software and hardware compatible with the Intel AC'97 rev2.2 component specification. The device is a derivative of the basic AC'97 codec, with added support for resistive touch-screen pen inputs. Variable Rate Audio (VRA) is supported at rates defined in the Intel rev2.1 or rev2.2 specification, and a SPDIF output port is provided which may optionally be used to output the PCM DAC information to external processors. A key feature of operation of the pen digitiser function is the cessation of screen drive activity when the pen is lifted from the screen, so minimising audio performance degradation and reducing power consumption.

WM9705 offers the following features:

Stereo Audio Codec with Intel specified VRA support of different audio sample rates

Pen Digitiser function with 4-wire pen interface and support for pen-down detection, pen pressure measurement and wake-on-pen-down.

Auxiliary ADC inputs for temperature, supply and battery monitoring.

Pen-down flag and ADC BUSY flags, output to pins, and MASK input pin provided to allow delay of pen conversions in event of LCD activity

Optional SPDIF and  $I^2S$  audio outputs (SPDIF output may be hardware enabled so needing no driver support)

Headphone drive capability and optional auto detection of headset or headphone plug in

It is highly recommended that the Intel AC'97 rev2.2 specification be studied in parallel with this document: This specification can be downloaded from the Intel web site.

The WM9705 is fully operable on 3V or 5V or mixed 3/5V supplies, and is packaged in the industry standard  $48pin\ TQFP$  package with  $7mm\ body\ size$ .

Figure 10 shows the functional block diagram including control register bit locations for WM9705.

#### **AC'97 FEATURES**

WM9705 implements the base set of AC'97 rev2.2 features, plus several enhancements:

All rev2.2 specified variable audio sample rates supported

3-D stereo enhancement feature.

Headphone support on AUX outputs (pins 39,41)

Primary/secondary codec operation by pin programming of CID0 pin

SPDIF audio output with rev2.2 compliant control set.

#### **NON - AC'97 FEATURES**

In addition to the AC'97 features offered, WM9705 also supports:

4-wire pen digitiser with integrated screen driver, featuring highly flexible modes of operation, supporting autonomous screen conversions, and auxiliary conversions. Screen X and Y connections driven from AUX and VID stereo input pins, which are still connected.

Headphone drive capability on MONO output, with extra signal routing switch PSEL, allowing PHONE input to be routed to MONO output

Extra switch HPND after the mixer allowing MIX without DAC signal to be output to headphone outputs, and so allowing DAC with no MIX to be output to LINE outputs.

I<sup>2</sup>S audio output capability, in addition to SPDIF output, allowing support of an extra external audio DAC for multi-channel solutions. SPDIF output may be hardware enabled.

Option to route the stereo audio ADC output to the SPDIF and/or I<sup>2</sup>S digital outputs

Auto-detect of headphones or headset plugged into the AUX headphone outputs, with internal routing of microphone signal from the headphone pin to the MIC1 input.

Battery monitoring input BMON that supports direct connection to battery voltages up to 6.5V.

MPM switch allowing mix of DAC + mixer output onto MONOUT and independent mix of DAC + PHONE and/or PCBEEP onto LINEOUT or HPOUT.

Reset powerdown override – holding MASK high in reset overrides the PR bits forcing the WM9705 into a low power mode

Figure 10 Functional Block Diagram

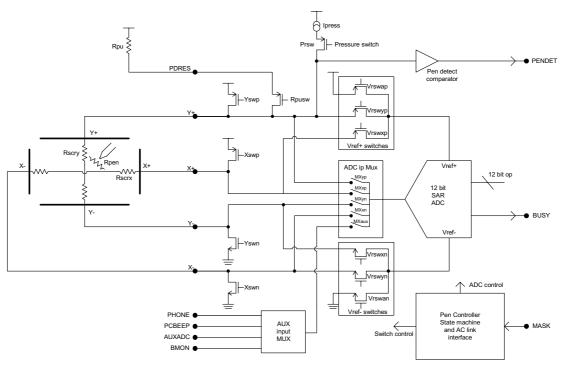

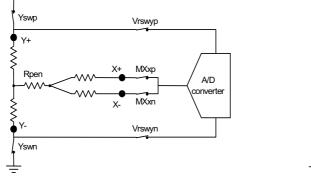

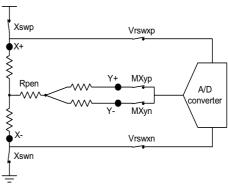

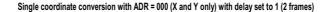

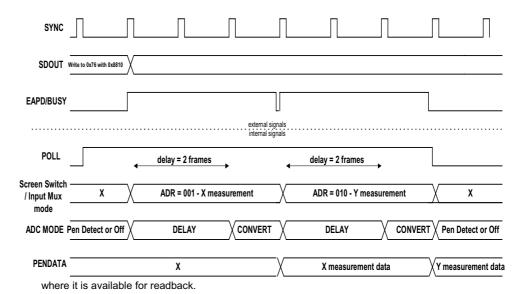

#### PEN DIGITIZER AND AUXILIARY ADC

A 4 wire input pen digitiser function is included on WM9705. This circuit comprises driver circuits to drive typical resistive touch screens of the type used on PDA's, plus a 12 bit resolution ADC to convert pen input values. This ADC may also be used to perform additional auxiliary ADC conversions of the levels present on the AUXADC, BMON, PCBEEP or PHONE pins. A control bit (PHIZ in register 78h) is provided to allow PCBEEP and PHONE inputs to be made high impedance (internally disconnected so signal paths are cut) if required.

Operation of the pen digitiser function is controlled from digitiser control registers 76h and 78h. The ADC conversion result is obtained by reading from the contents of bits [11-0] in register 7Ah, or optionally by enabling the AC link SLOT transfer method, when results are sent back in the AC'97 slot data format. The pen digitiser ADC is a 12bit successive approximation type converter with excellent differential non-linearity performance.

The pen digitiser ADC may be used to convert either pen input data, or the voltages present on the AUXADC, BMON, PCBEEP or PHONE pins. Such functions as battery monitoring or temperature measurement might therefore be implemented.

The following pen digitiser features are available:

Support for wake-on-pen-down

Pen down detection, pressure measurement, auxiliary conversions

MASK conversion delay override or synchronous operation option

SLOT or R/W register data transfer

Programmable screen drive to sample taken delay

Programmable Pen-down detection threshold

Details of pen digitiser operation are available in the Pen Digitiser description section. Note that the pins allocated for X/Y screen connections are those that would normally be used for AUX and VID stereo inputs in a conventional AC '97 codec. In WM9705 these pins remain connected to the MIXER and ADC inputs, and may be used as analogue inputs, with the restriction that gain through the mixer input is fixed at 0dB. The normal MUTE function is provided using bit 15 in the appropriate register. It is recommended that these MUTE bits are left 'mute' whenever the screen is driven. Reading back the registers will report 0dB gain, and the MUTE value as programmed. ADC gain control on the AUX and VID inputs works as normal.

#### **3-D STEREO ENHANCEMENT**

This device contains a stereo enhancement circuit, designed to optimise the listening experience when the device is used in a typical PC operating environment. That is, with a pair of speakers placed either side of the monitor with little spatial separation. This circuit creates a difference signal by differencing left and right channel playback data, then filters this difference signal using lowpass and highpass filters whose time constants are set using external capacitors connected to the CX3D pins 33 and 34. Typically the values of 100nF and 47nF set highpass and lowpass poles at about 100Hz and 1kHz respectively. This frequency band corresponds to the range over which the ear is most sensitive to directional effects.

The filtered difference signal is gain adjusted by an amount set using the 4-bit value written to Register 22h bits 3 to 0. Value 0h is disable, value Fh is maximum effect. Typically a value of 8h is optimum. The user interface would most typically use a slider type of control to allow the user to adjust the level of enhancement to suit the program material. Bit D13 3D in Register 20h is the overall 3D enable bit. The Reset Register 00h reads back the value 11000 in bits D14 to D10. This corresponds to decimal 24, which is registered with Intel as Wolfson Stereo Enhancement.

Note that the external capacitors setting the filtering poles applied to the difference signal may be adjusted in value, or even replaced with a direct connection between the pins. If such adjustments are made, then the amount of difference signal fed back into the main signal paths may be significant, and can cause large signals which may limit, distort, or overdrive signal paths or speakers. Adjust these values with care, to select the preferred acoustic effect. There is no provision for pseudo-stereo effects. Mono signals will have no enhancement applied (if the signals are in phase and of the same amplitude). Signals from the PCM DAC channels can have stereo

enhancement applied. It can also be bypassed if desired. This function is enabled by setting the bit POP in Register 20h.

#### VARIABLE SAMPLE RATE SUPPORT

The DACs and ADCs on this device support all the recommended sample rates specified in the Intel AC'97 rev2.1 and rev2.2 specifications for audio rates. The default rate is 48ks/s. If alternative rates are selected and variable rate audio is enabled (Register 2Ah, bit 0), the AC'97 interface continues to run at 48k words per second, but data is transferred across the link in bursts such that the net sample rate selected is achieved. It is up to the AC'97 Revision 2.1/2 compliant controller to ensure that data is supplied to the AC link, and received from the AC link, at the appropriate rate.

Variable rates are selected by writing to registers 2Ch (DAC) and 32h (ADC). ADC and DAC rates may be set independently, with left and right channels always at the same rate. Note that register 2Ch should only be written to when the DAC is powered ON, similarly register 32h should only be written to when the ADC is powered ON (see register 26h for power control). The device supports on demand sampling. That is, when the DAC signal processing circuits need another sample, a sample request is sent to the controller which must respond with a data sample in the next frame it sends. For example, if a rate of 24ks/s is selected, on average the device will request a sample from the controller every other frame, for each of the stereo DACs. Note that if an unsupported rate is written to one of the rate registers, the rate will default to the nearest rate supported. The Register will then respond, when interrogated, with the supported rate the device has defaulted to.

The WM9705 clocks will scale automatically dependent upon the MCLK frequency, where MCLK is not equal to 24.576MHz. With a 24MHz clock the BCLK frequency expected will be 12MHz and the sampling frequency (SYNC0 expected is BCLK/256 = 46.875kHz.

| AUDIO<br>SAMPLE RATE | CONTROL VALUE<br>D15-D0 |

|----------------------|-------------------------|

| 8000                 | 1F40                    |

| 11025                | 2B11                    |

| 16000                | 3E80                    |

| 22050                | 5622                    |

| 32000                | 7D000                   |

| 44100                | AC44                    |

| 48000                | BB80                    |

Table 1 Variable Sample Rates Supported

#### SPDIF OR I<sup>2</sup>S DIGITAL AUDIO DATA OUTPUT

The WM9705 SPDIF output may be enabled in hardware by holding pin 44 (SPEN) high when RESETB is taken high, or by writing to the SPDIF control bit in register 2Ah. If SPDIF pin 48 is pulled high at start-up by a weak pull-up (e.g. 100k), then SPDIF capability bit in register 28h is set to '0', i.e. no SPDIF capability. This allows for stuffing options, so that when SPDIF external components are not provided, the driver will see 'no SPDIF capability' and 'grey out' the relevant boxes in the control panel.

Additionally the digital audio may be output in I<sup>2</sup>S format using pin 44 (SPEN) as the data output, and outputting a frame clock or LRCLK onto pin 43. The data is clocked onto pin 44 using the regular BITCLK at 256fs, which would also then be used as the MCLK if the data is taken to an external DAC. Operation in this mode is selected by setting bit I<sup>2</sup>S in register 5Ch. A 64fs bitclk is also available and can be output on SPDIF by setting bit I2S64 in register 74h. Note that I<sup>2</sup>S operation is only supported for 48ks/s operation. Hardware selection of SPDIF operation by pulling pin SPEN 'hi' is compatible with I<sup>2</sup>S operation, provided a weak pull-up (circa 100k) was used to hold SPEN high at start-up. The SPEN pin becomes I<sup>2</sup>S data output pin when I<sup>2</sup>S is enabled, and the weak pull-up on this pin is overdriven.

For both SPDIF and I<sup>2</sup>S modes the data that is output may be sent from the WM9705 via the AC link in the same slots as normal DAC data or may be sent in different slots. The output slots that contain the SPDIF/I<sup>2</sup>S data are selected by bits SPSA[1:0] in register 2Ah. WM9705 is compliant with AC'97 rev2.2 specification with regard to slot mapping; therefore the default mode of operation is to output SPDIF or I<sup>2</sup>S data from the next data slots available after the audio data slots currently in use. Alternatively if required, data may be mapped from any of the available slots by selection using SPSA bits. The following table shows the default slot mapping for audio DACs and SPDIF/I<sup>2</sup>S data: (further details in the register description section later).

| SPEN STATE AT<br>START-UP | CODEC ID (PIN 45 STRAPPING) | AUDIO DAC SLOT<br>DEFAULT      | SPDIF OR I <sup>2</sup> S<br>DATASLOT DEFAULT |

|---------------------------|-----------------------------|--------------------------------|-----------------------------------------------|

| 'lo' (rev2.2 compliant)   | 'hi' = ID = 0 = primary     | Slots 3 and 4 - front channels | Slots 7 and 8                                 |

| 'lo' (rev2.2 compliant)   | 'lo' = ID = 1 = secondary   | Slots 7 and 8 – surround       | Slots 6 and 9                                 |

| 'hi' (WM proprietary)     | 'hi' = ID = 0 = primary     | Slots 3 and 4 - front channels | Slots 3 and 4                                 |

| 'hi' (WM proprietary)     | 'lo' = ID = 1 = secondary   | Slots 7 and 8 – surround       | Slots 3 and 4                                 |

Table 2 DAC and SPDIF Slot Mapping Defaults

However, an exception to the rev2.2 mapping table is made when SPDIF operation is enabled using the SPEN hardware enable pin (being held high at start-up): in this case SPDIF data is immediately output from the DAC primary slots 3 and 4. This allows for driver-less SPDIF operation, where the SPDIF or I<sup>2</sup>S output is simply the data contained in the main audio DAC channels. Channel status and control bits output along with the SPDIF data are as set in the SPDIF control register 3Ah. If required SPDIF data channel slot mapping may be then changed by setting SPSA bits as required. See tables 18, 19 and 20 for further details.

A mode is provided where the output from the ADC is sent out as the SPDIF or I<sup>2</sup>S data as above, rather than the data sent to the DACs over the AC link. This mode is enabled by setting bit ADCO in register 5Ch. ADC data continues to be sent via the AC link to the controller as normal.

WM9705 supports SPDIF and  $I^2S$  data only at the default 48ks/s frame rate. Writing to SPSR bits in register 3Ah any value other than the default 48ks/s rate will result in a fail to write, with the 48ks/s value being returned on subsequent reads of these values.

#### PRIMARY/SECONDARY ID SUPPORT

WM9705 supports operation as either a primary or a secondary codec. Configuration of the device as either a primary or as a secondary, is selected by tying the CID0 pin 45 on the package. Fundamentally, a device identified as a primary (ID = 0, CID0 = 'hi') produces BITCLK as an output, whereas a secondary (any other ID) must be provided with BITCLK as an input. This has the obvious implication that if the primary device on an AC link is disabled, the secondary devices cannot function. The AC'97 Revision 2.2 specification defines that the CID0 pin has inverting sense, and are provided with internal weak pull ups. Therefore, if no connections are made to the CID0 pin, then the pin pull hi and an ID = 0 is selected, i.e. primary. External connect to ground (with pull-down from 0 to  $10\text{k}\Omega$ ) will select codec ID = '1'.

| PIN 45 CID0   | ID<br>SELECTED | PRIMARY OR<br>SECONDARY | BITCLK |

|---------------|----------------|-------------------------|--------|

| NC or pull-up | 0              | Primary                 | Output |

| Ground        | 1              | Secondary               | Input  |

Table 3 Codec ID Selection

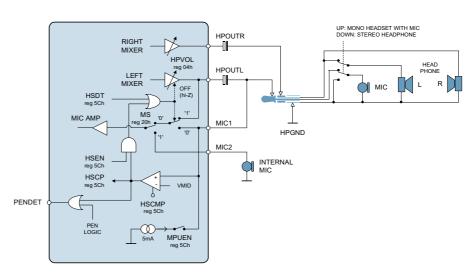

#### HEADPHONE DRIVE AND HEADSET AUTODETECT

Headphone drive capability is provided on the HPOUT output pins 39 and 41 (called AUXOUT in AC'97 rev2.2 specification) and also on the MONOOUT output pin 37.

Headphones of impedance typically from  $16\Omega$  upwards may be connected to these pins. AC coupling with an appropriately sized capacitor is recommended for removal of the mid-rail DC pedestal present on these outputs. AC'97 rev2.2 specification recommends  $32\Omega$  headphones; if a headphone is connected for use as a headset, where the stereo ear-pieces are driven in parallel, then each capsule must be of minimum  $32\Omega$  impedance.

In many applications it is desirable to be able to connect either a stereo headphone to the headphone output pins, or a mono headset, comprising ear-piece(s) and a microphone. The microphone signal is sent via the tip connected wire of the typical 3-wire jack. In this event it is desirable to be able to auto-detect the connection of either the headphone or the headset (with microphone). The main characteristic of the headset and microphone compared to the headphone is that the microphone impedance is typically much higher than the headphone capsule (assuming a typical moving coil headphone). Because of this it is possible to connect a weak pull-up to the tip connection of the headphone jack.

When a headphone is connected the low impedance to ground of the headset pulls down the DC level to near ground. If a headset with microphone is plugged in, the high impedance of the microphone does not pull down the DC level on the tip connection, the DC on this pin now rising to near positive supply. This change in DC level is detected, so allowing detection of change from headphone to microphone, (or nothing plugged in of course). When this event is detected, the headphone amplifier that drives the tip connection is turned off, and the signal on this pin is routed instead to the MIC1 input as a microphone input.

This auto-detect comparator is enabled by setting bit HSCMP. The pull-up current is enabled by setting bit MPUEN in register 5Ch and also toggles the interrupt signal on the PENDET pin. When bit HSDT is set the mic1 input is connected to a comparator with a threshold set at midrail. When the comparator output is low, then the headphone driver is enabled. When the comparator output goes high (that is the pull-up current multiplied by the external impedance to ground on the mic1 pin is greater than mid-rail), the headphone amplifier is turned off and the mic1 signal is taken internally from the headphone output pin (39).

Figure 10 Headset Autodetect

Figure 10 shows this function schematically. The output signal from the comparator is accessible by reading bit HSCP in register 5Ch. Auto detect may be used by setting HSEN bit, or external control by using the HSDT bit which is an over-ride that forces the headset tri-state and microphone path switching function to occur.

This function would allow, for example, a stereo headphone to be used that had a microphone in the connecting lead, and a switch. The switch changes the headphone into a mono headset with microphone connected via the tip connection on the jack. If used in a product such as an MP3 capable phone it would allow the user to switch from headphone use to headset use by simply switching a single switch in the headphone cable, so at the same time answering or initiating telephone calls. It may also be possible to use the pull-up current to provide so called 'phantom power' to dynamic microphones with appropriate choice of microphone.

#### **DATA SLOT MAPPING**

DAC data and SPDIF data sent to the device, ADC data sent from the device, can be optionally mapped into alternative slots under control of slot mapping bits located as follows:

| SLOT MAPPING DATA<br>TYPE | CONTROL<br>BITS | REGISTER LOCATION       |

|---------------------------|-----------------|-------------------------|

| DAC data                  | DSA[1,0]        | 28h                     |

| SPDIF data                | SPSA[1,0]       | 2Ah                     |

| ADC data                  | ASS[1,0]        | 5Ch (non-AC'97 feature) |

**Table 4 Data Slot Mapping Control**

Default values and functional behavior are further described in the Serial Interface Register Map description. DAC slot mapping defaults are in Table 2.

#### **AC-LINK DIGITAL SERIAL INTERFACE PROTOCOL**

A digital interface has been provided to control the WM9705 and transfer data to and from it. This serial interface is compatible with the Intel AC'97 specification.

The main control interface functions are:

- Control of analogue gain and signal paths through the mixer

- Bi-directional transfer of ADC and DAC words to and from AC'97 controller

- Selection of power-down modes

- Control of pen digitizer function

- Transfer of pen digitizer information and auxiliary conversion results from the codec

The WM9705 incorporates a 5-pin digital serial interface that links it to the AC'97 controller. AC-link is a bi-directional, fixed rate, serial PCM digital stream. It handles multiple input and output audio streams, as well as control register accesses employing a time division multiplexed (TDM) scheme. The AC-link architecture divides each audio frame into 12 outgoing and 12 incoming data streams, each with 20-bit sample resolution. With a minimum required DAC and ADC resolution of 16-bits, AC'97 may also be implemented with 18 or 20-bit DAC/ADC resolution, given the headroom that the AC-link architecture provides. The WM9705 provides support for 18-bit audio operation.

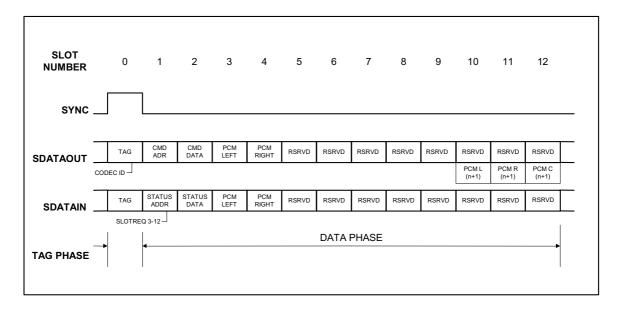

Figure 11 AC'97 Standard Bi-directional Audio Frame

Figure 12 AC-link Audio Output Frame

The datastreams currently defined by the AC'97 specification include:

| PCM playback - 2 output slots                       | 2-channel composite PCM output stream                                                       |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------|

| PCM record data - 2 input slots                     | 2-channel composite PCM input stream                                                        |

| Control - 2 output slots                            | Control Register write port                                                                 |

| Status - 2 input slots                              | Control Register read port                                                                  |

| Optional modem line codec output -<br>1 output slot | Modem line codec DAC input stream                                                           |

| Optional modem line codec input –<br>1 input slot   | Modem line codec ADC output stream                                                          |

| Optional dedicated microphone input - 1 input slot  | Dedicated microphone input stream in support of stereo AEC and/or other voice applications. |

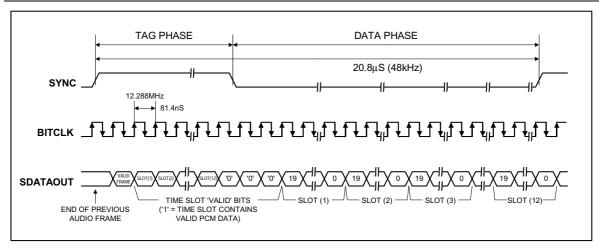

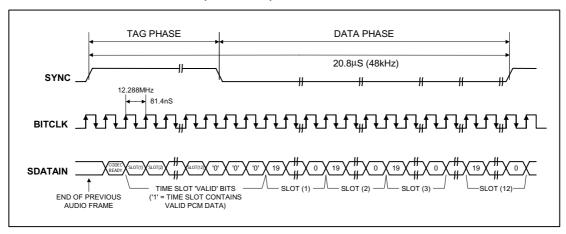

Synchronisation of all AC-link data transactions is signalled by the WM9705 controller. The WM9705 drives the serial bit clock onto AC-link, which the AC'97 controller then qualifies with a synchronisation signal to construct audio frames.

SYNC, fixed at 48kHz, is derived by dividing down the serial clock (BITCLK). BITCLK, fixed at 12.288MHz, provides the necessary clocking granularity to support 12, 20-bit outgoing and incoming time slots. AC-link serial data is transitioned on each rising edge of BITCLK. The receiver of AC-link data, (WM9705 for outgoing data and AC'97 controller for incoming data), samples each serial bit on the falling edges of BITCLK.

The AC-link protocol provides for a special 16-bit time slot (slot 0) wherein each bit conveys a valid tag for its corresponding time slot within the current audio frame. A 1 in a given bit position of slot 0 indicates that the corresponding time slot within the current audio frame has been assigned to a data stream, and contains valid data. If a slot is tagged invalid, it is the responsibility of the source of the data, (the WM9705 for the input stream, AC'97 controller for the output stream), to stuff all bit positions with 0s during that slot's active time.

SYNC remains high for a total duration of 16 BITCLKs at the beginning of each audio frame.

The portion of the audio frame where SYNC is high is defined as the Tag Phase. The remainder of the audio frame where SYNC is low is defined as the Data Phase. Additionally, for power savings, all clock, sync, and data signals can be halted. This requires that the WM9705 be implemented as a static design to allow its Register contents to remain intact when entering a power savings mode.

## **AC-LINK AUDIO OUTPUT FRAME (SDATAOUT)**

The audio output frame data streams correspond to the multiplexed bundles of all digital output data targeting the WM9705's DAC inputs, and control registers. As briefly mentioned earlier, each audio output frame supports up to 12 20-bit outgoing data time slots. Slot 0 is a special reserved time slot containing 16-bits, which are used for AC-link protocol infrastructure.

Within slot 0 the first bit is a global bit (SDATAOUT slot 0, bit 15) which flags the validity for the entire audio frame. If the Valid Frame bit is a 1, this indicates that the current audio frame contains at least one time slot of valid data. The next 12-bit positions sampled by the WM9705 indicate which of the corresponding 12 time slots contain valid data.

In this way data streams of differing sample rates can be transmitted across AC-link at its fixed 48kHz audio frame rate. Figure 11 illustrates the time slot based AC-link protocol.

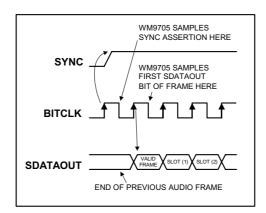

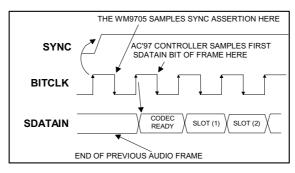

Figure 13 Start of an Audio Output Frame

A new audio output frame begins with a low to high transition of SYNC as shown in Figure 13. SYNC is synchronous to the rising edge of BITCLK. On the immediately following falling edge of BITCLK, the WM9705 samples the assertion of SYNC. This falling edge marks the time when both sides of AC-link are aware of the start of a new audio frame. On the next rising edge of BITCLK, AC'97 transitions SDATAOUT into the first bit position of slot 0 (Valid Frame bit). Each new bit position is presented to AC-link on a rising edge of BITCLK, and subsequently sampled by the WM9705 on the following falling edge of BITCLK. This sequence ensures that data transitions and subsequent sample points for both incoming and outgoing data streams are time aligned.

Baseline AC'97 specified audio functionality MUST ALWAYS sample rate convert to and from a fixed 48ks/s on the AC'97 controller. This requirement is necessary to ensure that interoperability between the AC'97 controller and the WM9705, among other things, can be guaranteed by definition for baseline specified AC'97 features.

SDATAOUT's composite stream is MSB justified (MSB first) with all non-valid slot bit positions stuffed with 0s by the AC'97 controller.

In the event that there are less than 20 valid bits within an assigned and valid time slot, the AC'97 controller always stuffs all trailing non-valid bit positions of the 20-bit slot with 0s.

As an example, consider an 8-bit sample stream that is being played out to one of the WM9705's DACs. The first 8 bit positions are presented to the DAC (MSB justified) followed by the next 12 bit positions, which are stuffed with 0s by the AC'97 controller. This ensures that regardless of the resolution of the implemented DAC (16, 18 or 20-bit), no DC biasing will be introduced by the least significant bits.

When mono audio sample streams are output from the AC'97 controller, it is necessary that BOTH left and right sample stream time slots be filled with the same data.

#### SLOT 1: COMMAND ADDRESS PORT

The command port is used to control features, and monitor status for the WM9705 functions including, but not limited to, mixer settings, and power management (refer to the Serial Interface Register Map). The control interface architecture supports up to 64, 16-bit read/write registers, addressable on even byte boundaries. Only the even Registers (00h, 02h, etc.) are valid, odd Register (01h, 03h, etc.) accesses are discouraged (if supported they should default to the preceding even byte boundary - i.e. a read to 01h will return the 16-bit contents of 00h). The WM9705's control register file is nonetheless readable as well as writeable to provide more robust testability.

Audio output frame slot 1 communicates control register address, and read/write command information to the WM9705.

#### COMMAND ADDRESS PORT BIT ASSIGNMENTS

| Bit (19)    | Read/write command (1 = read, 0 = write)                                        |  |

|-------------|---------------------------------------------------------------------------------|--|

| Bit (18:12) | Control register index (64 16-bit locations, addressed on even byte boundaries) |  |

| Bit (11:0)  | Reserved (stuffed with 0s)                                                      |  |

The first bit (MSB) sampled by the WM9705 indicates whether the current control transaction is a read or write operation. The following 7 bit positions communicate the targeted control register address. The trailing 12 bit positions within the slot are reserved and must be stuffed with 0s by the AC'97 controller.

#### **SLOT 2: COMMAND DATA PORT**

The command data port is used to deliver 16-bit control register write data in the event that the current command port operation is a write cycle. (As indicated by slot 1, bit 19).

| Bit (19:4) | Control register write data (stuffed with 0s if current operation is a read) |

|------------|------------------------------------------------------------------------------|

| Bit (3:0)  | Reserved (stuffed with 0s)                                                   |

If the current command port operation is a read then the entire time slot must be stuffed with 0s by the AC'97 controller.

#### SLOT 3 AND 4: PCM PLAYBACK LEFT AND RIGHT CHANNELS

Audio output frame slots 3 and 4 are the stereo digital audio left and right playback streams. In a typical Games Compatible PC this data is composed of standard PCM (.wav) output samples digitally mixed (on the AC'97 controller or host processor) with music synthesis output samples. If a sample stream of resolution less than 20-bits is transferred, the AC'97 controller must stuff all trailing non-valid bit positions within this time slot with 0s.

#### **SLOT 5: OPTIONAL MODEM LINE CODEC**

This data slot is not supported.

#### **SLOTS 6 AND 9: LFE AND CENTER CHANNEL DATA**

Data in these slots may be mapped onto the audio DACs or output as SPDIF/I<sup>2</sup>S data under control of the mapping bits DSA[1:0] in register 28h and SPSA[1:0] in register 2Ah.

#### **SLOTS 7 AND 8: SURROUND CHANNEL DATA**