# WM9713L

## AC'97 Audio + Touchpanel CODEC

### DESCRIPTION

The WM9713L is a highly integrated input/output device designed for mobile computing and communications.

The chip is architected for dual CODEC operation, supporting Hi-Fi stereo Codec functions via the AC link interface, and additionally supporting voice Codec functions via a PCM type Synchronous Serial Port (SSP). A third Aux DAC is provided which may be used to support generation of supervisory tones, or ring-tones etc. at different sample rates to the main codec.

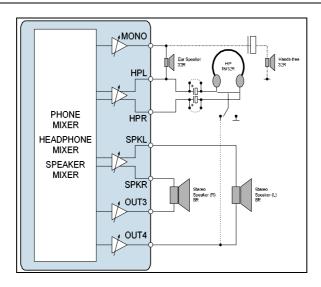

The device can connect directly to a 4-wire or 5-wire touchpanel, mono or stereo microphones, stereo headphones and a stereo speaker, reducing total component count in the system. Cap-less connections to the headphones, speakers, and earpiece may be used, saving cost and board area. Additionally, multiple analog input and output pins are provided for seamless integration with analog connected wireless communication devices.

All device functions are accessed and controlled through a single AC-Link interface compliant with the AC'97 standard. The 24.576 MHz masterclock can be input directly or generated internally from a 13MHz (or other frequency) clock by an onboard PLL. The PLL supports a wide range of input clock from 2.048Mhz to 78.6Mhz.

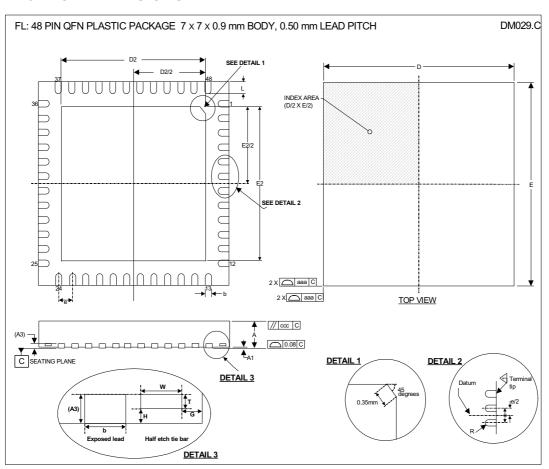

The WM9713L operates at supply voltages from 1.8 to 3.6 Volts. Each section of the chip can be powered down under software control to save power. The device is available in a small leadless 7x7mm QFN package, ideal for use in handheld portable systems.

### **FEATURES**

- AC'97 Rev 2.2 compatible stereo codec

- DAC SNR 94dB, THD -85dB

- ADC SNR 87dB, THD -86dB

- Variable Rate Audio, supports all WinCE sample rates

- Tone Control, Bass Boost and 3D Enhancement

- On-chip 45mW headphone driver

- On-chip 400mW mono or stereo speaker drivers

- Stereo, mono or differential microphone input

- Automatic Level Control (ALC)

- Mic insert and mic button press detection

- Auxiliary mono DAC (ring tone or DC level generation)

- · Seamless interface to wireless chipset

- Resistive touchpanel interface

- Supports 4-wire and 5-wire panels

- 12-bit resolution, INL ±2 LSBs (<0.5 pixels)

- X, Y and touch-pressure (Z) measurement

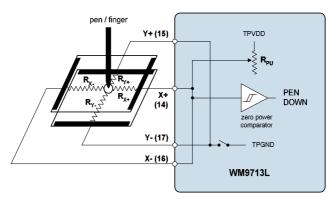

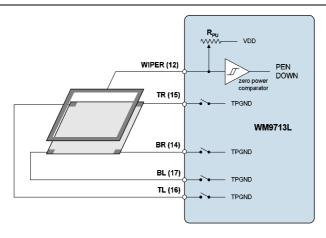

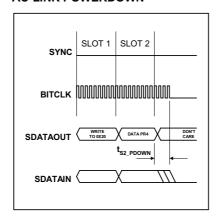

- Pen-down detection supported in Sleep Mode

- Additional PCM/I<sup>2</sup>S interface to support voice CODEC

- · PLL derived audio clocks.

- Supports input clock ranging from 2.048Mhz to 78.6Mhz

- 1.8V to 3.6V supplies (digital down to 1.62V, speaker up to 4.2V)

- 7x7mm 48-pin QFN package

### **APPLICATIONS**

- Personal Digital Assistants (PDA) with or without phone

- Smartphones

- Handheld and Tablet Computers

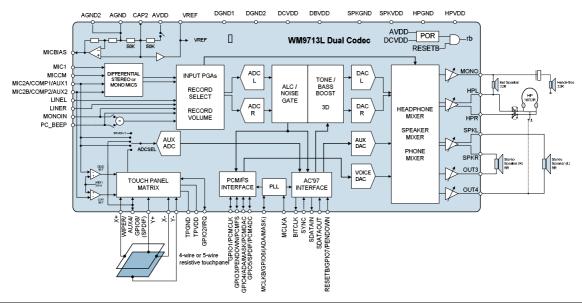

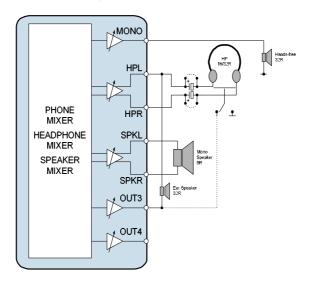

## **BLOCK DIAGRAM**

## **TABLE OF CONTENTS**

| DESCRIPTION                                                                                                                                                                                                                                                                                                                                                 | 1                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| FEATURES                                                                                                                                                                                                                                                                                                                                                    | 1                              |

| APPLICATIONS                                                                                                                                                                                                                                                                                                                                                | 1                              |

| BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                               |                                |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                           |                                |

| PIN CONFIGURATION                                                                                                                                                                                                                                                                                                                                           |                                |

| ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                        |                                |

| PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                             |                                |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                    |                                |

|                                                                                                                                                                                                                                                                                                                                                             |                                |

| RECOMMENDED OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                            |                                |

| ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                  |                                |

| AUDIO OUTPUTS                                                                                                                                                                                                                                                                                                                                               |                                |

| AUDIO INPUTS                                                                                                                                                                                                                                                                                                                                                |                                |

| AUXILIARY MONO DAC (AUXDAC)                                                                                                                                                                                                                                                                                                                                 |                                |

| PCM VOICE DAC (VXDAC)TOUCHPANEL AND AUXILIARY ADC                                                                                                                                                                                                                                                                                                           | 9<br>10                        |

| COMPARATORS                                                                                                                                                                                                                                                                                                                                                 |                                |

| REFERENCE VOLTAGES                                                                                                                                                                                                                                                                                                                                          |                                |

| DIGITAL INTERFACE CHARACTERISTICS                                                                                                                                                                                                                                                                                                                           |                                |

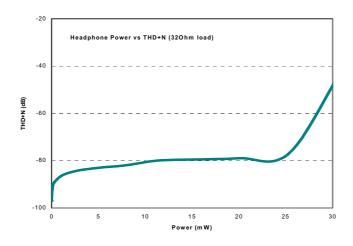

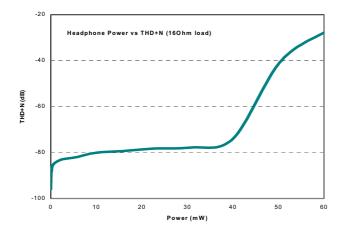

| HEADPHONE / SPEAKER OUTPUT THD VERSUS POWER                                                                                                                                                                                                                                                                                                                 |                                |

| POWER CONSUMPTION                                                                                                                                                                                                                                                                                                                                           |                                |

| DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |                                |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                |                                |

|                                                                                                                                                                                                                                                                                                                                                             |                                |

|                                                                                                                                                                                                                                                                                                                                                             |                                |

| AUDIO PATHS OVERVIEW                                                                                                                                                                                                                                                                                                                                        | 16                             |

| AUDIO PATHS OVERVIEWCLOCK GENERATION                                                                                                                                                                                                                                                                                                                        | 16<br>17                       |

| AUDIO PATHS OVERVIEWCLOCK GENERATIONCLOCK DIVISION MODES                                                                                                                                                                                                                                                                                                    | 16<br>17<br>17                 |

| AUDIO PATHS OVERVIEWCLOCK GENERATIONCLOCK DIVISION MODESPLL MODE                                                                                                                                                                                                                                                                                            | 16<br>17<br>17<br>20           |

| AUDIO PATHS OVERVIEWCLOCK GENERATIONCLOCK DIVISION MODESPLL MODEDATA AND CONTROL INTERFACE                                                                                                                                                                                                                                                                  | 16<br>17<br>20<br>22           |

| AUDIO PATHS OVERVIEWCLOCK GENERATIONCLOCK DIVISION MODESPLL MODE                                                                                                                                                                                                                                                                                            | 16<br>17<br>20<br>22           |

| AUDIO PATHS OVERVIEW                                                                                                                                                                                                                                                                                                                                        | 16<br>17<br>20<br>22<br>22     |

| AUDIO PATHS OVERVIEW CLOCK GENERATION CLOCK DIVISION MODES PLL MODE DATA AND CONTROL INTERFACE AC97 INTERFACE PCM INTERFACE.                                                                                                                                                                                                                                | 1617202222                     |

| AUDIO PATHS OVERVIEW CLOCK GENERATION CLOCK DIVISION MODES PLL MODE DATA AND CONTROL INTERFACE AC97 INTERFACE PCM INTERFACE AUDIO ADCS                                                                                                                                                                                                                      | 161720222328                   |

| AUDIO PATHS OVERVIEW CLOCK GENERATION CLOCK DIVISION MODES PLL MODE DATA AND CONTROL INTERFACE AC97 INTERFACE PCM INTERFACE PCM INTERFACE STEREO ADC RECORD SELECTOR RECORD GAIN                                                                                                                                                                            | 16172022232828                 |

| AUDIO PATHS OVERVIEW CLOCK GENERATION CLOCK DIVISION MODES PLL MODE DATA AND CONTROL INTERFACE AC97 INTERFACE PCM INTERFACE PCM INTERFACE STEREO ADC RECORD SELECTOR                                                                                                                                                                                        | 16172022232828                 |

| AUDIO PATHS OVERVIEW CLOCK GENERATION CLOCK DIVISION MODES PLL MODE DATA AND CONTROL INTERFACE AC97 INTERFACE PCM INTERFACE PCM INTERFACE STEREO ADC RECORD SELECTOR RECORD GAIN                                                                                                                                                                            | 1617202223282930               |

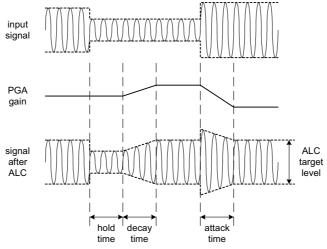

| AUDIO PATHS OVERVIEW CLOCK GENERATION CLOCK DIVISION MODES PLL MODE DATA AND CONTROL INTERFACE AC97 INTERFACE PCM INTERFACE PCM INTERFACE STEREO ADC RECORD SELECTOR RECORD GAIN AUTOMATIC LEVEL CONTROL                                                                                                                                                    | 1617202223282831               |

| AUDIO PATHS OVERVIEW. CLOCK GENERATION CLOCK DIVISION MODES. PLL MODE. DATA AND CONTROL INTERFACE. AC97 INTERFACE. PCM INTERFACE. PCM INTERFACE STEREO ADC. RECORD SELECTOR RECORD GAIN. AUTOMATIC LEVEL CONTROL  AUDIO DACS. STEREO DAC. VOICE DAC.                                                                                                        | 16172022282829303535           |

| AUDIO PATHS OVERVIEW. CLOCK GENERATION. CLOCK DIVISION MODES. PLL MODE. DATA AND CONTROL INTERFACE. AC97 INTERFACE. PCM INTERFACE. PCM INTERFACE.  STEREO ADC. RECORD SELECTOR. RECORD GAIN. AUTOMATIC LEVEL CONTROL  AUDIO DACS. STEREO DAC. VOICE DAC. AUXILIARY DAC.                                                                                     | 16172022232829303535           |

| AUDIO PATHS OVERVIEW. CLOCK GENERATION. CLOCK DIVISION MODES. PLL MODE. DATA AND CONTROL INTERFACE. AC97 INTERFACE. PCM INTERFACE. PCM INTERFACE. STEREO ADC. RECORD SELECTOR RECORD GAIN. AUTOMATIC LEVEL CONTROL. AUDIO DACS. STEREO DAC. VOICE DAC. AUXILIARY DAC. VARIABLE RATE AUDIO / SAMPLE RATE CONVERSION.                                         | 161720222328283031353535       |

| AUDIO PATHS OVERVIEW CLOCK GENERATION CLOCK DIVISION MODES PLL MODE DATA AND CONTROL INTERFACE AC97 INTERFACE PCM INTERFACE PCM INTERFACE  AUDIO ADCS STEREO ADC RECORD SELECTOR RECORD GAIN AUTOMATIC LEVEL CONTROL  AUDIO DACS STEREO DAC VOICE DAC AUXILIARY DAC  VARIABLE RATE AUDIO / SAMPLE RATE CONVERSION AUDIO INPUTS                              | 161720222328283135353535       |

| AUDIO PATHS OVERVIEW. CLOCK GENERATION CLOCK DIVISION MODES. PLL MODE. DATA AND CONTROL INTERFACE. AC97 INTERFACE. PCM INTERFACE. PCM INTERFACE.  STEREO ADC. RECORD SELECTOR RECORD GAIN. AUTOMATIC LEVEL CONTROL  AUDIO DACS. STEREO DAC. VOICE DAC. AUXILIARY DAC.  VARIABLE RATE AUDIO / SAMPLE RATE CONVERSION  AUDIO INPUTS. LINE INPUT               | 1617202228283535353535         |

| AUDIO PATHS OVERVIEW. CLOCK GENERATION CLOCK DIVISION MODES PLL MODE DATA AND CONTROL INTERFACE. AC97 INTERFACE PCM INTERFACE PCM INTERFACE STEREO ADC RECORD SELECTOR RECORD GAIN AUTOMATIC LEVEL CONTROL AUDIO DACS STEREO DAC VOICE DAC AUXILIARY DAC VARIABLE RATE AUDIO / SAMPLE RATE CONVERSION AUDIO INPUTS LINE INPUT MICROPHONE INPUT              | 1617202223282930313535353441   |

| AUDIO PATHS OVERVIEW. CLOCK GENERATION CLOCK DIVISION MODES PLL MODE DATA AND CONTROL INTERFACE. AC97 INTERFACE PCM INTERFACE PCM INTERFACE STEREO ADC RECORD SELECTOR RECORD GAIN AUTOMATIC LEVEL CONTROL AUDIO DACS STEREO DAC VOICE DAC AUXILIARY DAC VARIABLE RATE AUDIO / SAMPLE RATE CONVERSION AUDIO INPUTS LINE INPUT MICROPHONE INPUT MONOIN INPUT | 1617202223282931353537344141   |

| AUDIO PATHS OVERVIEW. CLOCK GENERATION CLOCK DIVISION MODES PLL MODE DATA AND CONTROL INTERFACE. AC97 INTERFACE PCM INTERFACE PCM INTERFACE STEREO ADC RECORD SELECTOR RECORD GAIN AUTOMATIC LEVEL CONTROL AUDIO DACS STEREO DAC VOICE DAC AUXILIARY DAC VARIABLE RATE AUDIO / SAMPLE RATE CONVERSION AUDIO INPUTS LINE INPUT MICROPHONE INPUT              | 161720222328303135353534414146 |

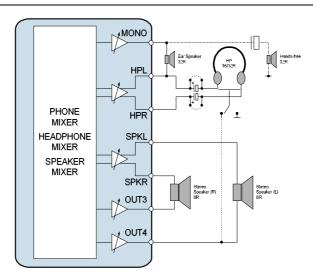

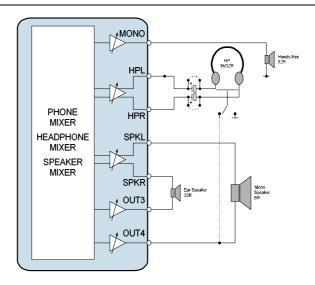

| AUDIO MIXERS                                  | 48  |

|-----------------------------------------------|-----|

| MIXER OVERVIEW                                | 48  |

| HEADPHONE MIXERS                              |     |

| SPEAKER MIXER                                 |     |

| MONO MIXER                                    |     |

| MIXER OUTPUT INVERTERS                        | 49  |

| ANALOGUE AUDIO OUTPUTS                        | 50  |

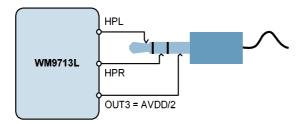

| HEADPHONE OUTPUTS – HPL AND HPR               |     |

| MONO OUTPUT                                   | 51  |

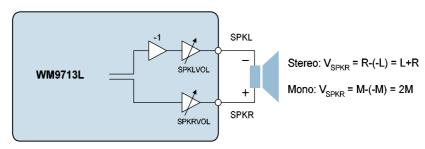

| SPEAKER OUTPUTS – SPKL AND SPKR               | 52  |

| AUXILLARY OUTPUTS – OUT3 AND OUT4             | 53  |

| THERMAL SENSOR                                |     |

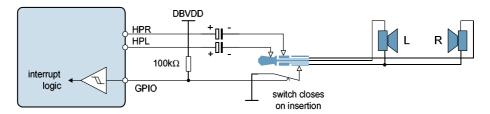

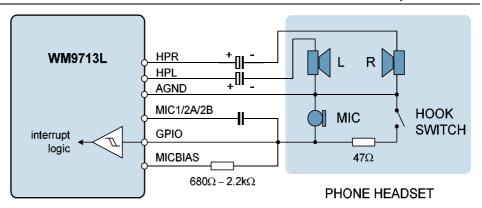

| JACK INSERTION AND AUTO-SWITCHING             | 54  |

| DIGITAL AUDIO (SPDIF) OUTPUT                  | 58  |

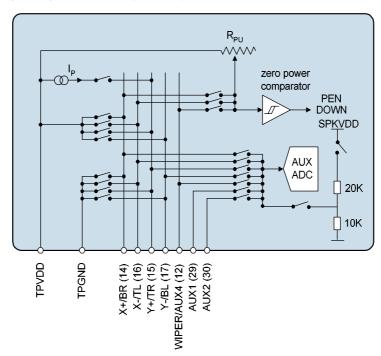

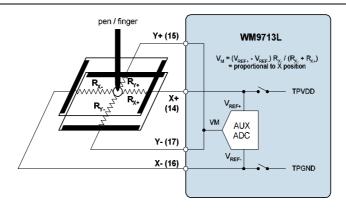

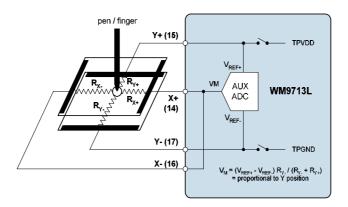

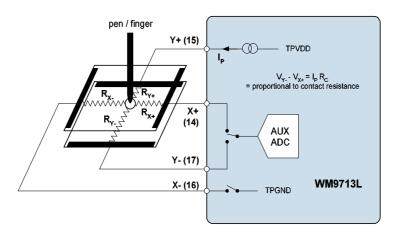

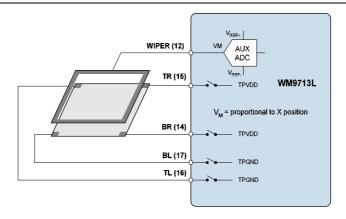

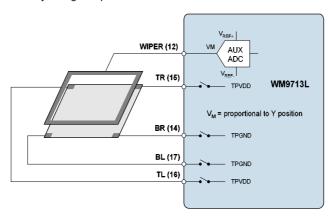

| TOUCHPANEL INTERFACE                          |     |

| PRINCIPLE OF OPERATION - FIVE-WIRE TOUCHPANEL |     |

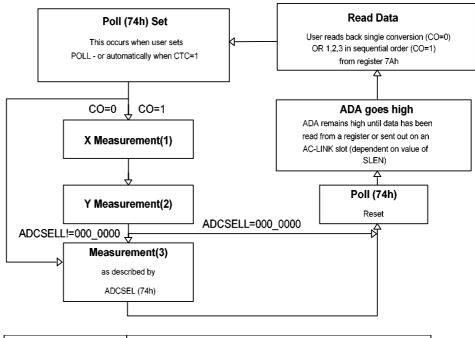

| CONTROLLING THE TOUCHPANEL DIGITISER          |     |

| ADDITIONAL FEATURES                           | 73  |

| AUXILIARY ADC INPUTS                          |     |

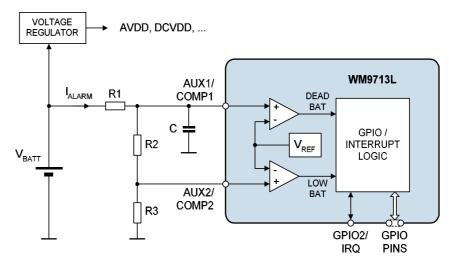

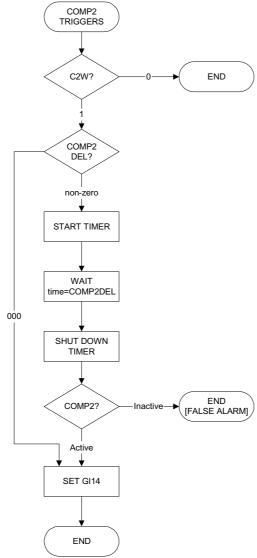

| BATTERY ALARM AND ANALOGUE COMPARATORS        | 74  |

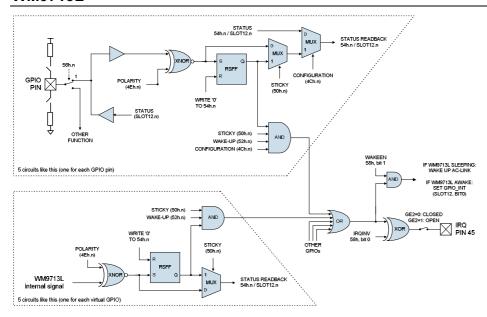

| GPIO AND INTERRUPT CONTROL                    | 77  |

| POWER MANAGEMENT                              | 82  |

| INTRODUCTION                                  | 82  |

| AC97 CONTROL REGISTER                         | 82  |

| EXTENDED POWERDOWN REGISTERS                  |     |

| ADDITIONAL POWER MANAGEMENT                   |     |

| POWER ON RESET (POR)                          |     |

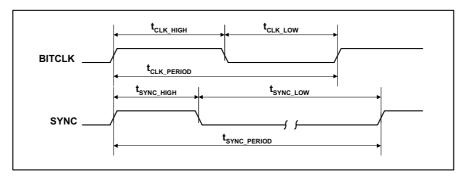

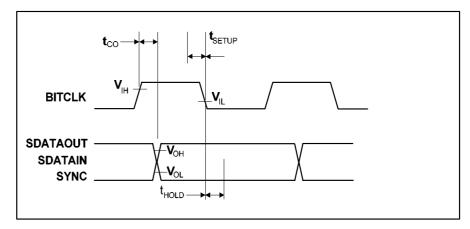

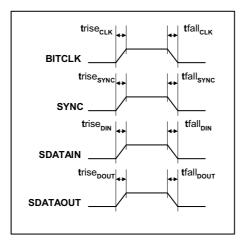

| AC97 INTERFACE TIMING                         |     |

| REGISTER MAP                                  |     |

| REGISTER BITS BY ADDRESS                      |     |

| APPLICATIONS INFORMATION                      |     |

| RECOMMENDED EXTERNAL COMPONENTS               |     |

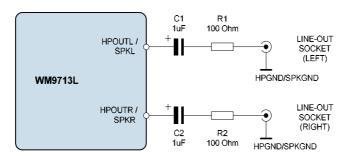

| LINE OUTPUT                                   |     |

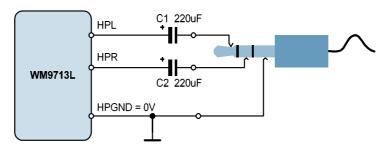

| AC-COUPLED HEADPHONE OUTPUT                   | 104 |

| DC COUPLED (CAPLESS) HEADPHONE OUTPUT         |     |

| BTL LOUDSPEAKER OUTPUT                        |     |

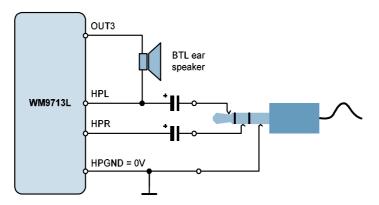

| COMBINED HEADSET / BTL EAR SPEAKER            |     |

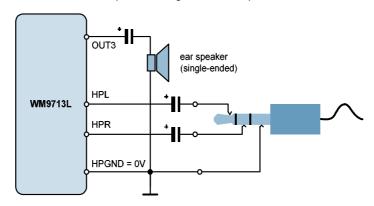

| COMBINED HEADSET / SINGLE-ENDED EAR SPEAKER   |     |

| JACK INSERT DETECTION                         |     |

| HOOKSWITCH DETECTION                          |     |

| TYPICAL OUTPUT CONFIGURATIONS                 |     |

| PACKAGE DIMENSIONS                            |     |

| IMPORTANT NOTICE                              |     |

| ADDRESS:                                      | 112 |

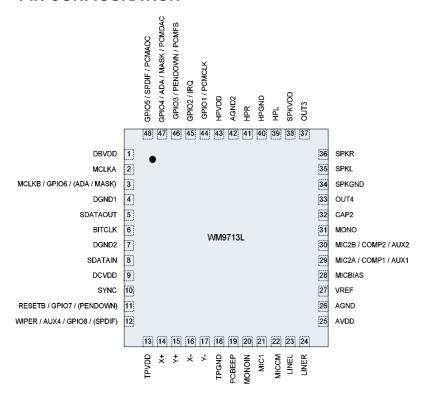

## **PIN CONFIGURATION**

## **ORDERING INFORMATION**

| DEVICE         | TEMPERATURE<br>RANGE | PACKAGE                               | MOISTURE SENSITIVITY<br>LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|----------------|----------------------|---------------------------------------|-------------------------------|-------------------------------|

| WM9713LGEFL/V  | -25 to +85°C         | 48-pin QFN<br>(lead free)             | MSL3                          | 260°C                         |

| WM9713LGEFL/RV | -25 to +85°C         | 48-pin QFN (lead free, tape and reel) | MSL3                          | 260°C                         |

Note:

Reel quantity = 2,200

## **PIN DESCRIPTION**

| PIN | NAME                           | TYPE              | DESCRIPTION                                                                                              |

|-----|--------------------------------|-------------------|----------------------------------------------------------------------------------------------------------|

| 1   | DBVDD                          | Supply            | Digital I/O Buffer Supply                                                                                |

| 2   | MCLKA                          | Digital Input     | Master Clock A Input                                                                                     |

| 3   | MCLKB / GPIO6 / (ADA / MASK)   | Digital In/Out    | Master Clock B Input / GPIO6 / (ADA output / MASK input)                                                 |

| 4   | DGND1                          | Supply            | Digital Ground (return path for both DCVDD and DBVDD)                                                    |

| 5   | SDATAOUT                       | Digital Input     | Serial Data Output from Controller / Input to WM9713L                                                    |

| 6   | BITCLK                         | Digital Output    | Serial Interface Clock Output to Controller                                                              |

| 7   | DGND2                          | Supply            | Digital Ground (return path for both DCVDD and DBVDD)                                                    |

| 8   | SDATAIN                        | Digital Output    | Serial Data Input to Controller / Output from WM9713L                                                    |

| 9   | DCVDD                          | Supply            | Digital Core Supply                                                                                      |

| 10  | SYNC                           | Digital Input     | Serial Interface Synchronisation Pulse from Controller                                                   |

| 11  | RESETB / GPIO7 / (PENDOWN)     | Digital In / Out  | Reset (asynchronous, active Low, resets all registers to their default) / GPIO7 / (pen down output)      |

| 12  | WIPER / AUX4 / GPIO8 / (SPDIF) | Analogue In / Out | Top Sheet Connection for 5-wire Touchpanels / Auxiliary ADC input / GPIO8 / (SPDIF digital audio output) |

| 13  | TPVDD                          | Supply            | Touchpanel Driver Supply                                                                                 |

| 14  | X+/ BR                         | Analogue Input    | Touchpanel Connection: X+ (Right) for 4-wire / bottom right for 5-wire                                   |

| 15  | Y+/TR                          | Analogue Input    | Touchpanel Connection: Y+ (Top) for 4-wire / top right for 5-wire                                        |

| 16  | X-/TL                          | Analogue Input    | Touchpanel Connection: X- (Left) for 4-wire / top left for 5-wire                                        |

| 17  | Y-/BL                          | Analogue Input    | Touchpanel Connection: Y- (Bottom) for 4-wire / bottom left for 5-wire                                   |

| 18  | TPGND                          | Supply            | Touchpanel Driver Ground                                                                                 |

| 19  | PCBEEP                         | Analogue Input    | Line Input to analogue audio mixers, typically used for beeps                                            |

| 20  | MONOIN                         | Analogue Input    | Mono Input (RX)                                                                                          |

| 21  | MIC1                           | Analogue Input    | Microphone preamp A input 1                                                                              |

| 22  | MICCM                          | Analogue Input    | Microphone common mode input                                                                             |

| 23  | LINEL                          | Analogue Input    | Left Line Input                                                                                          |

| 24  | LINER                          | Analogue Input    | Right Line Input                                                                                         |

| 25  | AVDD                           | Supply            | Analogue Supply (audio DACs, ADCs, PGAs, mic amps, mixers)                                               |

| 26  | AGND                           | Supply            | Analogue Ground                                                                                          |

| 27  | VREF                           | Analogue Output   | Internal Reference Voltage (buffered CAP2)                                                               |

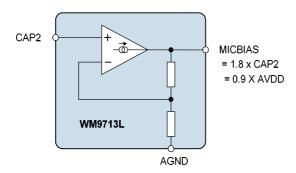

| 28  | MICBIAS                        | Analogue Output   | Bias Voltage for Microphones (buffered CAP2 × 1.8)                                                       |

| 29  | MIC2A / COMP1 / AUX1           | Analogue Input    | Microphone preamp A input 2 / COMP1 input / Auxillary ADC input                                          |

| 30  | MIC2B / COMP2 / AUX2           | Analogue Input    | Microphone preamp B input / COMP2 input / Auxillary ADC input                                            |

| 31  | MONO                           | Analog output     | Mono output driver (line or headphone)                                                                   |

| 32  | CAP2                           | Analogue In / Out | Internal Reference Voltage (normally AVDD/2, if not overdriven)                                          |

| 33  | OUT4                           | Analogue Output   |                                                                                                          |

| 34  | SPKGND                         | Supply            | Speaker ground (feeds output buffers on pins 33, 35, 36 and 37)                                          |

| 35  | SPKL                           | Analogue Output   | Left speaker driver (speaker, line or headphone)                                                         |

| 36  | SPKR                           | Analogue Output   | Right speaker driver (speaker, line or headphone)                                                        |

| 37  | OUT3                           | Analogue Output   | Auxillary output driver (speaker, line or headphone)                                                     |

| 38  | SPKVDD                         | Supply            | Speaker supply (feeds output buffers on pins 33, 35, 36 and 37)                                          |

| 39  | HPL                            | Analogue Output   | Headphone left driver (line or headphone)                                                                |

| 40  | HPGND                          | Supply            | Headphone ground (feeds output buffers on pins 39 and 41)                                                |

| 41  | HPR                            | Analogue Output   | Headphone right driver (line or headphone)                                                               |

| 42  | AGND2                          | Supply            | Analogue ground, chip substrate                                                                          |

| 43  | HPVDD                          | Supply            | Headphone supply (feeds output buffers on pins 39 and 41)                                                |

WM9713L Preliminary Technical Data

| PIN | NAME                        | TYPE             | DESCRIPTION                                                                         |

|-----|-----------------------------|------------------|-------------------------------------------------------------------------------------|

| 44  | GPIO1 / PCMCLK              | Digital In / Out | GPIO Pin 1 or PCM interface clock                                                   |

| 45  | GPIO2 / IRQ                 | Digital In / Out | GPIO Pin 2 or IRQ (Interrupt Request) output                                        |

| 46  | GPIO3 / PENDOWN / PCMFS     | Digital In / Out | GPIO Pin 3 or pen down output or PCM frame signal                                   |

| 47  | GPIO4 / ADA / MASK / PCMDAC | Digital In / Out | GPIO Pin 4 or ADA (ADC data available) output or Mask input or PCM input (DAC) data |

| 48  | GPIO5 / SPDIF / PCMADC      | Digital In / Out | GPIO Pin 5 or SPDIF digital audio output or PCM output (ADC) data                   |

## **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

$MSL1 = unlimited \ floor \ life \ at < 30^{\circ}C\ /\ 85\% \ Relative \ Humidity. \ Not \ normally \ stored \ in \ moisture \ barrier \ bag.$

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                         | MIN        | MAX         |

|---------------------------------------------------|------------|-------------|

| Digital supply voltages (DCVDD, DBVDD)            | -0.3V      | +3.63V      |

| Analogue supply voltages (AVDD, HPVDD, TPVDD)     | -0.3V      | +3.63V      |

| Speaker supply voltage (SPKVDD)                   | -0.3V      | +4.2V       |

| Touchpanel supply voltage (TPVDD)                 |            | AVDD +0.3V  |

| Voltage range digital inputs                      | DGND -0.3V | DBVDD +0.3V |

| Voltage range analogue inputs                     | AGND -0.3V | AVDD +0.3V  |

| Voltage range touchpanel Inputs X+, X-, Y+ and Y- |            | TPVDD +0.3V |

| Voltage range touchpanel Inputs X+, X-, Y+ and Y- |            | AVDD +0.3V  |

| Operating temperature range, T <sub>A</sub>       | -25°C      | +85°C       |

| Storage temperature (TQFP package only)           | -65°C      | +150°C      |

## RECOMMENDED OPERATING CONDITIONS

| PARAMETER                          | SYMBOL                        | TEST CONDITIONS | MIN      | TYP | MAX  | UNIT |

|------------------------------------|-------------------------------|-----------------|----------|-----|------|------|

| Digital input/output buffer supply | DBVDD                         |                 | 1.62     | 3.3 | 3.6  | V    |

| range                              |                               |                 | (target) |     |      |      |

| Digital core supply range          | DCVDD                         |                 | 1.62     | 1.8 | 3.6  | V    |

|                                    |                               |                 | (target) |     |      |      |

| Analogue supply range              | AVDD, HPVDD,<br>TPVDD         |                 | 1.8      | 3.3 | 3.6  | V    |

| Speaker supply range               | SPKVDD                        |                 | 1.8      | 3.3 | 4.2  | V    |

| Digital ground                     | DGND1, DGND2                  |                 |          | 0   |      | V    |

| Analogue ground                    | AGND, HPGND,<br>SPKGND, TPGND |                 |          | 0   |      | V    |

| Difference AGND to DGND            |                               | Note 1          | -0.3     | 0   | +0.3 | V    |

### Note:

- 1. AGND is normally the same as DGND1/DGND2

- 2. DCVDD <= DBVDD and DCVDD <= AVDD

## **ELECTRICAL CHARACTERISTICS**

## **AUDIO OUTPUTS**

## **Test Conditions**

DBVDD=3.3V, DCVDD = 3.3V, AVDD=HPVDD=SPKVDD =3.3V,  $T_A = +25^{\circ}C$ , 1kHz signal, fs = 48kHz, 24-bit audio data unless otherwise stated.

| PARAMETER                   | SYMBOL             | TEST CONDITIONS                            | MIN           | TYP            | MAX          | UNIT     |

|-----------------------------|--------------------|--------------------------------------------|---------------|----------------|--------------|----------|

| DAC to Line-Out (HPL/R or M | MONO with 10       | ·Ω / 50pF load)                            |               |                |              | •        |

| Full-scale output           |                    | AVDD = 3.3V, PGA gains set to 0dB          |               | 1              |              | V rms    |

| Signal to Noise Ratio       | SNR                |                                            | 85            | 94             |              | dB       |

| (A-weighted)                |                    |                                            |               |                |              |          |

| Total Harmonic Distortion   | THD                | -3dB output                                |               | -85            | -74          | dB       |

| Power Supply Rejection      | PSRR               | 100mV, 20Hz to 20kHz<br>signal on AVDD     |               | 50             |              | dB       |

| Speaker Output (SPKL/SPKI   | R with 8Ω brid     | ge tied load, INV=1)                       |               |                |              |          |

| Output Power at 1% THD      | Po                 | THD = 1%                                   |               | 400            |              | mW (rms) |

| Abs. max output power       | P <sub>O</sub> max |                                            |               | 500            |              | mW (rms) |

| Total Harmonic Distortion   | THD                | P <sub>O</sub> = 200mW                     |               | -66            |              | dB       |

|                             |                    |                                            |               | 0.05           |              | %        |

| Signal to Noise Ratio       | SNR                |                                            |               | 90             |              | dB       |

| (A-weighted)                |                    |                                            |               |                |              |          |

| Stereo Speaker Output (SPK  | L/OUT4 and S       | PKR/OUT3 with 8Ω bridge to                 | ied Ioad, IN\ | /=1)           |              |          |

| Output Power at 1% THD      | Po                 | THD = 1%                                   |               | 400            |              | mW (rms) |

| Abs. max output power       | P <sub>o</sub> max |                                            |               | 500            |              | mW (rms) |

| Total Harmonic Distortion   | THD                | P <sub>O</sub> = 200mW                     |               | -66            |              | dB       |

|                             |                    |                                            |               | 0.05           |              | %        |

| Signal to Noise Ratio       | SNR                |                                            |               | 90             |              | dB       |

| (A-weighted)                |                    |                                            |               |                |              |          |

| Headphone Output (HPL/R,    | OUT3/4 or SPK      | (L/SPKR with 16 $\Omega$ or 32 $\Omega$ lo | ad)           |                |              |          |

| Output Power per channel    | Po                 | Output power is v                          | ery closely c | orrelated with | THD; see bel | ow.      |

| Total Harmonic Distortion   | THD                | $P_0$ =10mW, $R_L$ =16 $\Omega$            |               | -80            |              | dB       |

|                             |                    | $P_O$ =10mW, $R_L$ =32 $\Omega$            |               | -80            |              |          |

|                             |                    | $P_0$ =20mW, $R_L$ =16 $\Omega$            |               | -78            |              |          |

|                             |                    | $P_0$ =20mW, $R_L$ =32 $\Omega$            |               | -79            |              |          |

| Signal to Noise Ratio       | SNR                |                                            |               | 90             |              | dB       |

| (A-weighted)                |                    |                                            |               |                |              |          |

### Note:

<sup>1.</sup> All THD values are valid for the output power level quoted above – for example, at HPVDD=3.3V and  $R_L$ =16 $\Omega$ , THD is –80dB when output power is 10mW. Higher output power is possible, but will result in a deterioration in THD.

## **AUDIO INPUTS**

### **Test Conditions**

$DBVDD=3.3V,\ DCVDD=3.3V,\ AVDD=3.3V,\ T_A=+25^{\circ}C,\ 1kHz\ signal,\ fs=48kHz,\ 24-bit\ audio\ data\ unless\ otherwise\ stated.$

| PARAMETER                       | SYMBOL            | TEST CONDITIONS                      | MIN     | TYP              | MAX     | UNIT |

|---------------------------------|-------------------|--------------------------------------|---------|------------------|---------|------|

| LINEL/R, MIC1/2A/2B and MONO    | OIN pins          |                                      |         |                  |         |      |

| Full Scale Input Signal Level   | V <sub>INFS</sub> | AVDD = 3.3V                          |         | 1.0              |         | Vrms |

| (for ADC 0dB Input at 0dB Gain) |                   | AVDD = 1.8V                          |         | 0.545            |         |      |

|                                 |                   | differential input mode<br>(MS = 01) | half of | the value listed | d above |      |

| Input Resistance                | R <sub>IN</sub>   | 0dB PGA gain                         | 25.6    | 32               | 38.4    | kΩ   |

|                                 |                   | 12dB PGA gain                        | 10.4    | 13               | 15.6    | 1    |

| Input Capacitance               |                   |                                      |         | 5                |         | pF   |

| Line input to ADC (LINEL, LINER | R, MONOIN)        |                                      |         |                  |         |      |

| Signal to Noise Ratio           | SNR               |                                      | 80      | 87               |         | dB   |

| (A-weighted)                    |                   |                                      |         |                  |         |      |

| Total Harmonic Distortion       | THD               |                                      |         | -86              | -80     | dB   |

| Power Supply Rejection          | PSRR              | 20Hz to 20kHz                        |         | 50               |         | dB   |

| Microphone input to ADC (MIC1   | /2A/2B pins)      |                                      |         |                  |         |      |

| Signal to Noise Ratio           | SNR               | 20dB boost enabled                   |         | 80               |         | dB   |

| (A-weighted)                    |                   |                                      |         |                  |         |      |

| Total Harmonic Distortion       | THD               | 20dB boost enabled                   |         | -80              |         | dB   |

| Power Supply Rejection Ratio    | PSRR              |                                      |         | 50               |         | dB   |

| Common Mode Rejection Ratio     | CMRR              | Differential mic mode                |         | TBD              |         | dB   |

## **AUXILIARY MONO DAC (AUXDAC)**

## **Test Conditions**

AVDD = 3.3V,  $T_A = +25^{\circ}C$ , unless otherwise stated.

| PARAMETER                 | SYMBOL | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------------|--------|-----------------|-----|-----|-----|------|

| Resolution                |        |                 |     | 12  |     | bits |

| Full scale output voltage |        | AVDD=3.3V       |     | 1   |     | Vrms |

| Signal to Noise Ratio     | SNR    |                 |     | TBD |     | dB   |

| (A-weighted)              |        |                 |     |     |     |      |

| Total Harmonic Distortion | THD    |                 |     | TBD |     | dB   |

## **PCM VOICE DAC (VXDAC)**

### **Test Conditions**

AVDD = 3.3V,  $T_A = +25^{\circ}C$ , unless otherwise stated.

| PARAMETER                 | SYMBOL | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------------|--------|-----------------|-----|-----|-----|------|

| Resolution                |        |                 |     | 16  |     | bits |

| Sample rates              |        |                 |     | 8   | 16  | Ks/s |

| Full scale output voltage |        | AVDD=3.3V       |     | 1   |     | Vrms |

| Signal to Noise Ratio     | SNR    |                 |     | 80  |     | dB   |

| (A-weighted)              |        |                 |     |     |     |      |

| Total Harmonic Distortion | THD    |                 |     | 74  |     | dB   |

## **TOUCHPANEL AND AUXILIARY ADC**

### **Test Conditions**

DBVDD=3.3V, DCVDD = 3.3V, AVDD = TPVDD = 3.3V,  $T_A = +25^{\circ}C$ , MCLK = 24.576 MHz, unless otherwise stated.

| PARAMETER                        | SYMBOL          | TEST CONDITIONS                       | MIN  | TYP   | MAX  | UNIT |

|----------------------------------|-----------------|---------------------------------------|------|-------|------|------|

| Input Pins X+, X-, Y+, Y-, WIPEF | R/AUX4, CON     | P1/AUX1, COMP2/AUX2                   |      |       | •    |      |

| Input Voltage                    |                 |                                       | AGND |       | AVDD | V    |

| Input leakage current            |                 | AUX pin not selected as AUX ADC input |      | <10   |      | nA   |

| ADC Resolution                   |                 |                                       |      | 12    |      | bits |

| Differential Non-Linearity Error | DNL             |                                       |      | ±0.25 | ±1   | LSB  |

| Integral Non-Linearity Error     | INL             |                                       |      |       | ±2   | LSB  |

| Offset Error                     |                 |                                       |      |       | ±4   | LSB  |

| Gain Error                       |                 |                                       |      |       | ±6   | LSB  |

| Power Supply Rejection           | PSRR            |                                       |      | 50    |      | dB   |

| Channel-to-channel isolation     |                 |                                       |      | 80    |      | dB   |

| Throughput Rate                  |                 | DEL = 1111<br>(zero settling time)    |      |       | 48   | kHz  |

| Settling Time (programmable)     |                 | MCLK = 24.576MHz                      | 0    |       | 6    | ms   |

| Switch matrix resistance         |                 |                                       |      | 20    |      | Ω    |

| Programmable Pull-up resistor    | R <sub>PU</sub> | RPU = 000001                          | 1    |       | 63   | kΩ   |

| Pen down detector threshold      |                 |                                       |      | VDD/2 |      | V    |

| Pressure measurement current     | IР              | PIL = 1                               |      | 400   |      | μΑ   |

|                                  |                 | PIL = 0                               |      | 200   |      |      |

## **COMPARATORS**

### **Test Conditions**

AVDD = 3.3V,  $T_A = +25^{\circ}C$ , unless otherwise stated.

| PARAMETER                                                             | SYMBOL | TEST CONDITIONS                      | MIN  | TYP | MAX  | UNIT |  |  |

|-----------------------------------------------------------------------|--------|--------------------------------------|------|-----|------|------|--|--|

| COMP1/AUX1 and COMP2/AUX2 (pins 29, 30 – when not used as mic inputs) |        |                                      |      |     |      |      |  |  |

| Input Voltage                                                         |        |                                      | AGND |     | AVDD | V    |  |  |

| Input leakage current                                                 |        | pin not selected as AUX<br>ADC input |      | <10 |      | nA   |  |  |

| Comparator Input Offset                                               |        |                                      | -50  |     | +50  | mV   |  |  |

| (COMP1, COMP2 only)                                                   |        |                                      |      |     |      |      |  |  |

| COMP2 delay (COMP2 only)                                              |        | MCLK = 24.576MHz                     | 0    |     | 10.9 | s    |  |  |

## **REFERENCE VOLTAGES**

## **Test Conditions**

DBVDD=3.3V, DCVDD = 3.3V, AVDD = 3.3V,  $T_A$  =  $+25^{\circ}C$ , 1kHz signal, fs = 48kHz, 24-bit audio data unless otherwise stated.

| PARAMETER                 | SYMBOL               | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT   |  |

|---------------------------|----------------------|-----------------|------|------|------|--------|--|

| Audio ADCs, DACs, Mixers  |                      |                 |      |      |      |        |  |

| Reference Input/Output    | CAP2 pin             |                 | 1.63 | 1.65 | 1.66 | V      |  |

| Buffered Reference Output | VREF pin             |                 | 1.64 | 1.65 | 1.67 | V      |  |

| Microphone Bias           |                      |                 |      |      |      |        |  |

| Bias Voltage              | V <sub>MICBIAS</sub> |                 | 2.92 | 2.97 | 3.00 | V      |  |

| Bias Current Source       | I <sub>MICBIAS</sub> |                 |      |      | 3    | mA     |  |

| Output Noise Voltage      | Vn                   | 1K to 20kHz     |      | 15   |      | nV/√Hz |  |

## **DIGITAL INTERFACE CHARACTERISTICS**

## **Test Conditions**

DBVDD = 3.3V, DCVDD = 3.3V,  $T_A = +25^{\circ}$ C, unless otherwise stated.

| PARAMETER                                                             | SYMBOL          | TEST CONDITIONS      | MIN       | TYP    | MAX       | UNIT |  |  |

|-----------------------------------------------------------------------|-----------------|----------------------|-----------|--------|-----------|------|--|--|

| Digital Logic Levels (all digital input or output pins) – CMOS Levels |                 |                      |           |        |           |      |  |  |

| Input HIGH level                                                      | V <sub>IH</sub> |                      | DBVDD×0.7 |        |           | V    |  |  |

| Input LOW level                                                       | V <sub>IL</sub> |                      |           |        | DBVDD×0.3 | V    |  |  |

| Output HIGH level                                                     | V <sub>OH</sub> | source current = 2mA | DBVDD×0.9 |        |           |      |  |  |

| Output LOW level                                                      | V <sub>OL</sub> | sink current = 2mA   |           |        | DBVDD×0.1 |      |  |  |

| Clock Frequency                                                       |                 |                      |           |        |           |      |  |  |

| Master clock (MCLKA pin)                                              |                 |                      |           | 24.576 |           | MHz  |  |  |

| AC'97 bit clock (BIT_CLK pin)                                         |                 |                      |           | 12.288 |           | MHz  |  |  |

| AC'97 sync pulse (SYNC pin)                                           |                 |                      |           | 48     |           | kHz  |  |  |

### Note:

- 1. All audio and non-audio sample rates and other timing scales proportionately with the master clock.

- 2. For signal timing on the AC-Link, please refer to the AC'97 specification (Revision 2.2)

## **HEADPHONE / SPEAKER OUTPUT THD VERSUS POWER**

## **POWER CONSUMPTION**

TBA

## **DEVICE DESCRIPTION**

### INTRODUCTION

The WM9713L is a largely pin compatible upgrade to WM9712, with a PCM voice codec added. This codec is interfaced via a PCM type audio interface which makes use of GPIO pins for connection.

It is designed to meet the mixed-signal requirements of portable and wireless smartphone systems. It includes audio recording and playback, touchpanel digitisation, battery monitoring, auxiliary ADC and GPIO functions, all controlled through a single 5-wire AC-Link interface. Additionally, PCM voice codec functions are supported through provision of an additional voice DAC and a PCM audio serial interface.

A PLL is included to allow unrelated reference clocks to be used for generation of the AC link system clock. Typically 13MHz or 2.048MHz references might be used as a reference.

### SOFTWARE SUPPORT

The basic audio features of the WM9713L are software compatible with standard AC'97 device drivers. However, to better support the touchpanel and other additional functions, Wolfson Microelectronics supplies custom device drivers for selected CPUs and operating systems. Please contact your local Wolfson Sales Office for more information.

### **AC'97 COMPATIBILITY**

The WM9713L uses an AC'97 interface to communicate with a microprocessor or controller. The audio and GPIO functions are largely compliant with AC'97 Revision 2.2. The following **differences** from the AC'97 standard are noted:

- Pinout: The function of some pins has been changed to support device specific features. The PHONE and PCBEEP pins have been moved to different locations on the device package.

- Package: The default package for the WM9713L is a 7×7mm leadless QFN package.

- Audio mixing: The WM9713L handles all the audio functions of a smartphone, including audio playback, voice recording, phone calls, phone call recording, ring tones, as well as simultaneous use of these features. The AC'97 mixer architecture does not fully support this. The WM9713L therefore uses a modified AC'97 mixer architecture with three separate mixers.

- Tone Control, Bass Boost and 3D Enhancement: These functions are implemented in the digital domain and therefore affect only signals being played through the audio DACs, not all output signals as stipulated in AC'97.

Some other functions are additional to AC'97:

- On-chip BTL loudspeaker driver for mono or stereo speakers

- On-chip BTL driver for ear speaker (phone receiver)

- Auxiliary mono DAC for ring tones, system alerts etc.

- Touchpanel controller

- Auxiliary ADC Inputs

- 2 Analogue Comparators for Battery Alarm

- Programmable Filter Characteristics for Tone Control and 3D Enhancement

- PCM interface to additional Voice DAC and existing audio ADCs

- PLL to create AC'97 system clock from unrelated reference clock input

## **PCM CODEC**

The PCM voice codec functions typically required by mobile telephony devices are provided by an extra voice DAC on the WM9713L, which is interfaced via a standard PCM type data interface, which is constructed through optional use of 4 of the GPIO pins on WM9713L. The audio output data from one or both of the audio ADCs can also be output over this PCM interface, allowing a full voice codec function to be implemented. This codec supports sample rates from 8 to 48ks/s using the standard AC'97 masterclock, with the WM9713L PCM interface always acting as a master.

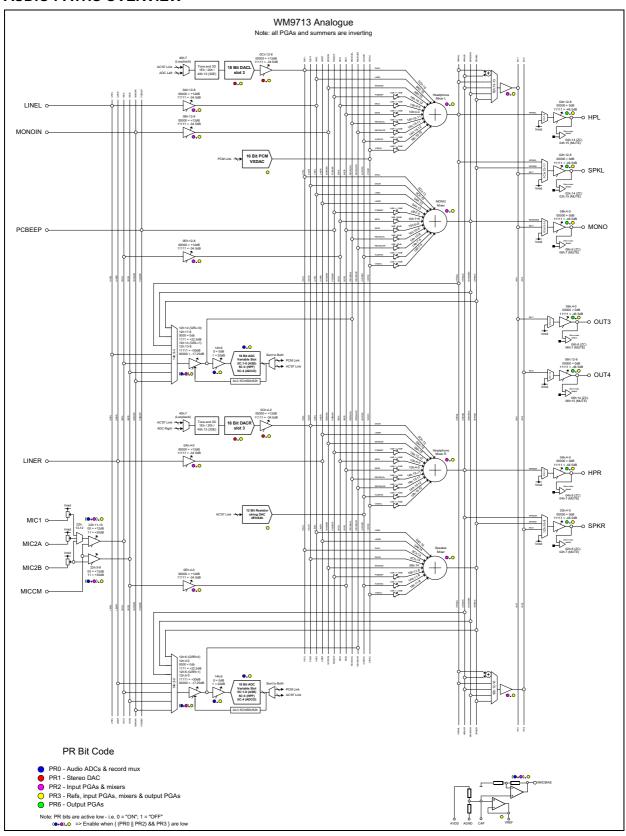

## **AUDIO PATHS OVERVIEW**

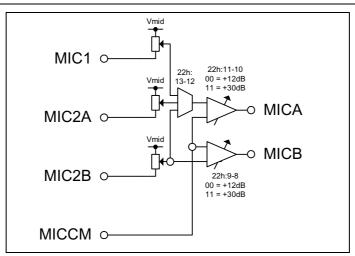

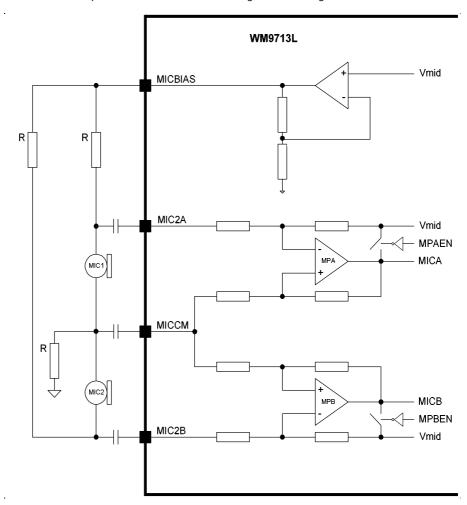

Figure 1 Audio Paths Overview

### **CLOCK GENERATION**

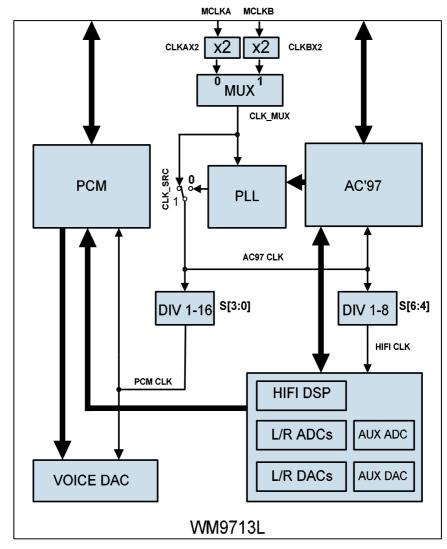

WM9713L supports clocking from 2 separate sources, which can be selected via the AC'97 interface:

- External clock input MCLKA

- External clock input MCLKB

The source clock is divided to appropriate frequencies in order to run the AC'97 interface, PCM interface, voice DAC and Hi-fi DSP by means of a programmable divider block. Clock rates may be changed during operation via the AC'97 link in order support alternative modes, for example low power mode when voice data is being transmitted only. A PLL is present to add flexibility in selection of input clock frequencies, typical choices being 2.048MHz, 4.096MHz or 13MHz.

Default mode on power-up assumes a clock will be present on MCLKA with the PLL powered down. This enables data to be clocked via the AC'97 link to define the desired clock divider mode and whether PLL needs to be activated.

Note: This clock can be any available frequency.

When muxing between MCLKA and MCLKB both clocks must be active for at least two clock cycles after the switching event.

## **CLOCK DIVISION MODES**

Figure 2 shows the clocking strategy for WM9713L. Clocking is controlled by CLK\_MUX, CLK\_SRC and S[6:0].

- CLKAX2, CLKBX2 clock doublers on inputs MCLKA and MCLKB.

- CLK\_MUX selects between MCLKA and MCLKB.

- CLK\_SRC selects between external or PLL derived clock reference.

- S[3:0] sets the voice DAC clock rate and PCM interface clock when in master mode (division ratio 1 to 16 available).

- S[6:4] sets the hi-fi clocking rate (division ratio 1 to 8 available).

The registers used to set these switches can be accessed from register address 44h (see Table 1).

If a mode change requires switching from an external clock to a PLL generated clock then it is recommended to set the clock division ratios required for the PLL clock scheme prior to switching between clocks. This option is accommodated by means of two sets of registers  $S_{PLL}[6:0]$  and  $S_{EXT}[6:0]$ . If the PLL is selected (CLK\_SRC = 0)  $S[6:0] = S_{PLL}[6:0]$ , if an external clock is selected (CLK\_SRC = 1)  $S[6:0] = S_{EXT}[6:0]$ .  $S_{EXT}[6:0]$  is defined in register address 44h.  $S_{PLL}[6:0]$  is defined in register 46h (see Table 3) which also contains a number of separate control bits relating to the PLL's function.

Writing to registers 44h and 46h enables pre-programming of the required clock mode before the PLL output is selected.

# data bus

Figure 2 Clocking Architecture for WM9713L

Clock mode and division ratios are controlled by register 44h as shown in Table 1.

| REGISTER<br>ADDRESS | BIT   | LABEL                                         | DEFAULT      | DESCRIPTION                                                                                                                                      |

|---------------------|-------|-----------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 44h                 | 14:12 | S <sub>EXT</sub> [6:4] S <sub>EXT</sub> [3:0] | 000 (div 1)  | Defines clock division ratio for Hi-fi block: 000: f 001: f/2 111: f/8 Defines clock division ratio for PCM                                      |

|                     |       |                                               |              | interface and voice DAC: 0000: f 0001: f/1 1111: f/16                                                                                            |

|                     | 7     | CLKSRC                                        | 1 (ext clk)  | Selects between PLL clock and External clock                                                                                                     |

|                     | 5:3   | PENDIV                                        | 000 (div 16) | Sets PENADC clock divisor 000: f/16 001: f/12 010: f/8 011: f/6 100: f/4 101: f/3 110: f/2 111: f                                                |

|                     | 2     | CLKBX2                                        | 0 (Off)      | Clock doubler for MCLKB                                                                                                                          |

|                     | 1     | CLKAX2                                        | 0 (Off)      | Clock doubler for MCLKA                                                                                                                          |

|                     | 0     | CLKMUX                                        | 0 (MCLKA)    | Selects between MCLKA and MCLKB (N.B. On power-up clock must be present on MCLKA and must be active for 2 clock cycles after switching to MCLKB) |

**Table 1 Clock Muxing and Division Control**

### **INTERNAL CLOCK FREQUENCIES**

The internal clock frequencies are defined as follows (refer to Figure 2):

- AC97 CLK nominally 24.576MHz, used to generate AC97 BITCLK at 12.288MHz.

- HIFI CLK for HIFI playback at 48ks/s HIFI CLK = 24.576MHz. See Table 2 for voice only playback.

- PCM CLK see Table 2 for sample rate vs clock frequency.

| SAMPLE RATE                    | PCM CLK<br>FREQUENCY | HIFI CLK<br>FREQUENCY |

|--------------------------------|----------------------|-----------------------|

| 8ks/s voice and HIFI           | 2.048MHz             | 24.576MHz             |

| 8ks/s voice only (power save)  | 2.048MHz             | 4.096MHz              |

| 16ks/s voice and HIFI          | 4.096MHz             | 24.576MHz             |

| 16ks/s voice only (power save) | 4.096MHz             | 8.192MHz              |

| 32ks/s voice and HIFI          | 8.192MHz             | 24.576MHz             |

| 48ks/s voice and HIFI          | 12.288MHz            | 24.576MHz             |

Table 2 Clock Division Mode Table

### **PEN ADC**

The clock for the PENADC nominally runs at 768kHz and is derived from BITCLK. The divisor for the clock generator is set by PENDIV. This enables the PENADC clock frequency to be set according to power consumption and conversion rate considerations.

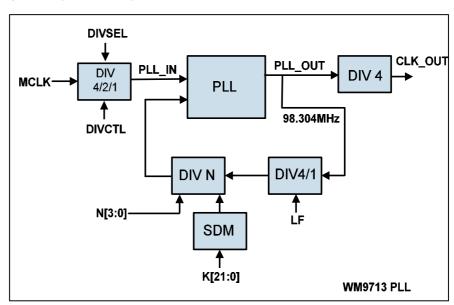

## **PLL MODE**

The PLL operation is controlled by register 46h (see Table 3) and has two modes of operation:

- Integer N

- Fractional N

The PLL has been optimized for nominal input clock (PLL\_IN) frequencies in the range 8.192MHz - 19.661MHz (LF=0) and 2.048MHz - 4.9152MHz (LF=1).

Through use of a clock divider (div by 2/4) on the input to the PLL frequencies up to 78.6MHz can be accommodated. The input clock divider is enabled by DIVSEL (0=Off) and the division ratio is set by DIVCTL (0=div2, 1=div4).

Figure 3 PLL Architecture

| REGISTER<br>ADDRESS | BIT   | LABEL  | DEFAULT | DESCRIPTION                                                                             |

|---------------------|-------|--------|---------|-----------------------------------------------------------------------------------------|

| 46h                 | 15:12 | N[3:0] | 0000    | PLL integer division control (must be set between 5-12 for integer N mode)              |

|                     | 11    | LF     | 0 = off | Allows PLL operation with low frequency input clocks (< 8.192MHz)                       |

|                     | 10    | SDM    | 0 = off | Sigma Delta Modulator enable. Allows fractional N division                              |

|                     | 9     | DIVSEL | 0 = off | Enables input clock to PLL to be divided by 2 or 4. Use if input clock is above 14.4MHz |

|                     | 8     | DIVCTL | 0       | Controls division mode when DIVSEL is high. 0 = div by 2, 1= div by 4.                  |

|                     | 6:4   | PGADDR | 000     | Pager address bits to access programming of K[21:0] and S <sub>PLL</sub> [7:0]          |

|                     | 3:0   | PGDATA | 0000    | Pager data bits                                                                         |

Table 3 PLL Clock Control

### **INTEGER N MODE**

The nominal output frequency of the PLL (PLL\_OUT) is 98.304MHz which is divided by 4 to achieve a nominal system clock of 24.576MHz.

The integer division ratio (N) is determined by:  $F_{PLL\_out} / F_{PLL\_IN}$ , and is set by N[3:0] and must be in the range 5 to 12 for integer N operation (0101 = div by 5, 1100 = div by 12). Note that setting LF=1 enables a further division by 4 required for input frequencies in the range 2.048MHz – 4.096MHz.

Integer N mode is selected by setting SDM=0.

### **FRACTIONAL N MODE**

Fractional N mode provides a divide resolution of  $1/2^{22}$  and is set by K[21:0] (register 46h, see section PLL Register Page Address Mapping). The relationship between the required division X, the fractional division K[21:0] and the integer division N[3:0] is:

$$K = 2^{22} \left( X - N \right)$$

where 0 < (X - N) < 1 and K is rounded to the nearest whole number.

For example, if the PLL\_IN clock is 13MHz and the desired PLL\_OUT clock is 98.304MHz then the desired division, X, is 7.5618. So N[3:0] will be 7h and K[21:0] will be 23F488h to produce the desired 98.304MHz clock (see Table 4).

| INPUT CLOCK (PLL_IN) | DESIRED PLL OUTPUT (PLL_OUT) | DIVISION<br>REQUIRED<br>(X) | FRACTIONAL<br>DIVISION (K) | INTEGER<br>DIVISION (N) |

|----------------------|------------------------------|-----------------------------|----------------------------|-------------------------|

| 2.048MHz             | 98.304MHz                    | 48                          | 0                          | 12x4*                   |

| 4.096MHz             | 98.304MHz                    | 24                          | 0                          | 6x4*                    |

| 12.288MHz            | 98.304MHz                    | 8                           | 0                          | 8                       |

| 13MHz                | 98.304MHz                    | 7.5618                      | 0.5618                     | 7                       |

| 27MHz (13.5MHz)**    | 98.304MHz                    | 7.2818                      | 0.2818                     | 7                       |

<sup>\*</sup>Divide by 4 enabled in PLL feedback path for low frequency inputs. (LF = 1)

Table 4 PLL Modes of Operation

## PLL REGISTER PAGE ADDRESS MAPPING

The clock division control bits S<sub>PLL</sub>[6:0] and the PLL fractional N division bits are accessed through register 46h using a sub-page address system. The 3 bit pager address allows 8 blocks of 4 bit data words to be accessed whilst the register address is set to 46h. This means that when register address 46h is selected a further 7 cycles of programming are required to set all of the page data bits. Control bit allocation for these page addresses is described in Table 5.

| PAGE<br>ADDRESS | BIT   | LABEL                  | DEFAULT | DESCRIPTION                                       |

|-----------------|-------|------------------------|---------|---------------------------------------------------|

| 111             | 31:28 | S <sub>PLL</sub> [6:4] | 0h      | Clock division control bus SPLL[6:0]. Clock       |

| 110             | 27:24 | S <sub>PLL</sub> [3:0] | 0h      | divider reads this control word if PLL is enabled |

| 101             | 23:22 | SPARE                  | 0h      | Spare control bits                                |

|                 | 21:20 | K[21:0]                | 0h      | Sigma Delta Modulator control word for            |

| 100             | 19:16 |                        | 0h      | fractional N division. Division resolution is     |

| 011             | 15:12 |                        | 0h      | 1/22 <sup>2</sup>                                 |

| 010             | 11:8  |                        | 0h      |                                                   |

| 001             | 7:4   |                        | 0h      |                                                   |

| 000             | 3:0   |                        | 0h      |                                                   |

Table 5 Pager Control Bit Allocation

<sup>\*\*</sup>Divide by 2 enabled at PLL input for frequencies > 14.4 MHz > 38 MHz (DIVSEL = 1, DIVCTL = 0)

Powerdown for the PLL and internal clocks is via registers 26h and 3Ch (see Table 6).

| REGISTER<br>ADDRESS                                              | BIT | LABEL | DEFAULT | DESCRIPTION                          |  |  |

|------------------------------------------------------------------|-----|-------|---------|--------------------------------------|--|--|

| 26h                                                              | 13  | PR5   | 1 (Off) | Internal clock disable (active high) |  |  |

| 3Ch 9 PLL 1 (Off) PLL powerdown (active high)                    |     |       |         |                                      |  |  |

| N.B. both PR5 and PLL must be asserted low before PLL is enabled |     |       |         |                                      |  |  |

Table 6 PLL Powerdown Control

### DATA AND CONTROL INTERFACE

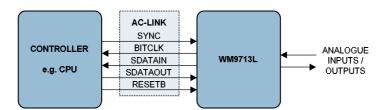

The WM9713L has two interfaces, a data and control AC'97 interface and a data only PCM interface. The AC'97 interface is available through dedicated pins (SDATAOUT, SDATAIN, SYNC, BITCLK and RESETB) and is the sole control interface with access to all data streams on the device except for the Voice DAC. The PCM interface is available through the GPIO pins (PCMCLK, PCMFS, PCMDAC and PCMADC) and provides access to the Voice DAC. It can also transmit the data from the Stereo ADC. This can be useful, for example, to allow both sides of a phone conversation to be recorded by mixing the transmit and receive paths on one of the ADC channels and transmitting it over the PCM interface.

### **AC97 INTERFACE**

### INTERFACE PROTOCOL

The WM9713Lhas a single AC'97 interface for both data transfer and control. The AC-Link uses 5 wires:

- SDATAIN (pin 8) carries data from the WM9713L to the controller

- SDATAOUT (pin 5) carries data from the controller to the WM9713L

- BITCLK (pin 6) is a clock, derived from either MCLKA or MCLKB inputs and supplied to the controller.

- SYNC is a synchronization signal generated by the controller and passed to the WM9713I

- RESETB resets the WM9713L to its default state

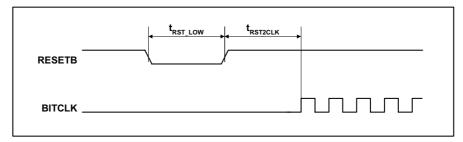

Figure 4 AC-Link Interface (typical case with BITCLK generated by the AC97 codec)

The SDATAIN and SDATAOUT signals each carry 13 time-division multiplexed data streams (slots 0 to 12). A complete sequence of slots 0 to 12 is referred to as an AC-Link frame, and contains a total of 256 bits. The frame rate is 48kHz. This makes it possible to simultaneously transmit and receive multiple data streams (e.g. audio, touchpanel, AUXDAC, control) at sample rates up to 48kHz.

Detailed information can be found in the AC'97 (Revision 2.2) specification, which can be obtained at <a href="https://www.intel.com/labs/media/audio/">www.intel.com/labs/media/audio/</a>

#### Note:

SDATAOUT and SYNC must be held low for when RESETB is applied. These signals must be held low for the entire duration of the RESETB pulse and especially during the low-to-high transition of RESETB. If either is set high during reset the AC'97 device may enter test modes. Information relating to this operation is available in the AC'97 specification or in Wolfson applications note WAN-0104 available at www.wolfsonmirco.com.

### **PCM INTERFACE**

### **OPERATION**

WM9713L can implement a PCM voice codec function using the dedicated VXDAC and either one or both of the existing hi-fi ADC's. In PCM codec mode, VXDAC input and ADC output are interfaced via a PCM style port via GPIO pins.

This interface can support one ADC channel, or stereo/dual ADC channels if required, (two channels of data are sent per PCM frame as back to back words).

In voice only mode, the AC link is used only for control information, not audio data. Therefore it will generally be shut down (PR4=1), except when control data must be sent.

The PCM interface makes use of 4 of the GPIO interface pins, for clock, frame, and data in/out. If the PCM codec function is not enabled then the GPIO pins may be used for other functions as on WM9713I

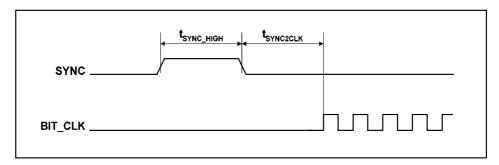

### INTERFACE PROTOCOL

The WM9713L PCM audio interface is used for the input of data to the Voice DAC and the output of data from the Stereo ADC. When enabled, the PCM audio interface uses four GPIO pins:

- GPIO1/PCMCLK: Bit clock

- GPIO3/PCMFS: Frame Sync

- GPIO4/PCMDAC: Voice DAC data input

- GPIO5/PCMADC: Stereo ADC data output

When not enabled the GPIOs may be used for other functions on the WM9713L.

### **PCM INTERFACE MODES**

The WM9713L PCM audio interface may be configured in one of four modes:

- Disabled Mode: The WM9713L disables and tri-states all PCM interface pins. Any clock input is ignored and ADC/DAC data is not transferred.

- Slave Mode: The WM9713L accepts PCMCLK and PCMFS as inputs from an external source.

- Master Mode: The WM9713L generates PCMCLK and PCMFS as outputs.

- Partial Master Mode: The WM9713L generates PCMCLK as an output, and accepts PCMFS as an external input.

The PCMDAC and PCMADC pins are normally used as DAC input and ADC output respectively. The WM9713L allows these functions to be swapped allowing DAC input on PCMADC and ADC output on PCMDAC.

### **PCM AUDIO DATA FORMATS**

Four different audio data formats are supported:

- DSP mode

- Left justified

- Right justified

- ) 1<sup>2</sup>S

All four of these modes are MSB first. They are described below. Refer to the Electrical Characteristic section for timing information.

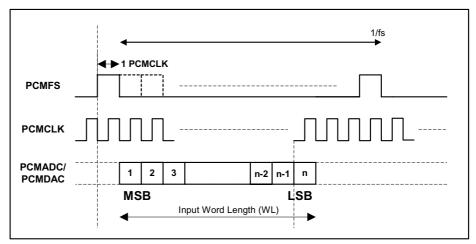

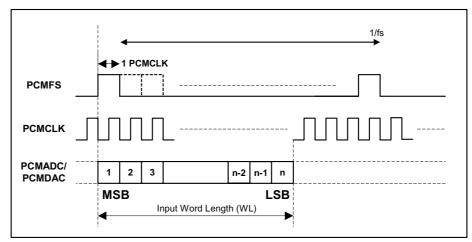

The PCM Interface may be configured for Mono mode, where only one channel of ADC data is output. In this mode the interface should be configured for DSP mode. A short or long frame sync is supported and the MSB is available on either the 1st (mode B) or 2nd (mode A) rising edge of VXCLK.

Note that when operating in stereo mode the mono Voice DAC always uses the left channel data as its input.

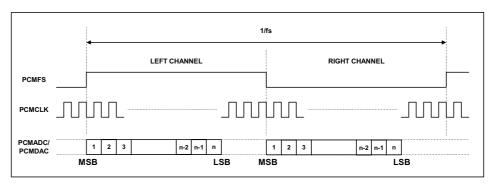

Figure 5 PCM Interface Mono Mode (mode A, FSP=0)

Figure 6 PCM Interface Mono Mode (mode B, FSP=1)

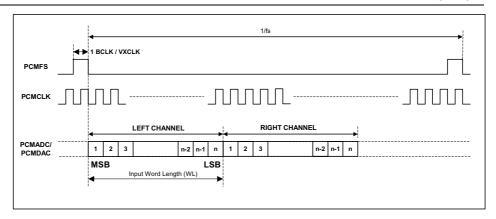

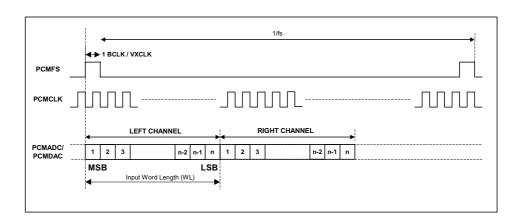

In DSP mode, the left channel MSB is available on either the 1st (mode B) or 2nd (mode A) rising edge of PCMCLK (selectable by FSP) following a rising edge of PCMFS. Right channel data immediately follows left channel data. Depending on word length, PCMCLK frequency and sample rate, there may be unused PCMCLK cycles between the LSB of the right channel data and the next sample.

Figure 7 DSP Mode Audio Interface (mode A, FSP=0)

Figure 7 DSP Mode Audio Interface (mode B, FSP=1)

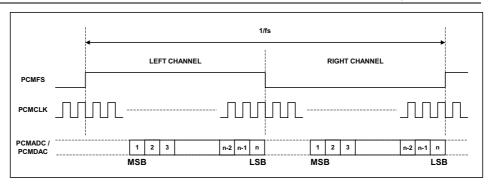

In Left Justified mode, the MSB is available on the first rising edge of PCMCLK following a PCMFS transition. The other bits up to the LSB are then transmitted in order. Depending on word length, PCMCLK frequency and sample rate, there may be unused PCMCLK cycles before each PCMFS transition.

Figure 8 Left Justified Audio Interface (assuming n-bit word length)

In Right Justified mode, the LSB is available on the last rising edge of PCMCLK before a PCMFS transition. All other bits are transmitted before (MSB first). Depending on word length, PCMCLK frequency and sample rate, there may be unused PCMCLK cycles after each PCMFS transition.

Figure 9 Right Justified Audio Interface (assuming n-bit word length)

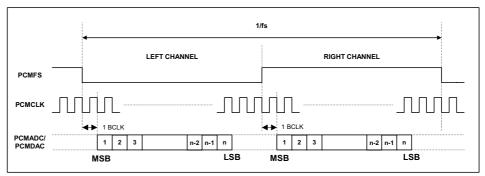

In I<sup>2</sup>S mode, the MSB is available on the second rising edge of PCMCLK following a PCMFS transition. The other bits up to the LSB are then transmitted in order. Depending on word length, PCMCLK frequency and sample rate, there may be unused PCMCLK cycles between the LSB of one sample and the MSB of the next.

Figure 10  $\ I^2S$  Justified Audio Interface (assuming n-bit word length)

### CONTROL

The register bits controlling PCM audio format, word length and operating modes are summarised below. CTRL must be set to override the normal use of the PCM interface pins as GPIOs, MODE must be set to specify master/slave modes.

| REGISTER<br>ADDRESS | BIT   | LABEL | DEFAULT | DESCRIPTION                                                                  |

|---------------------|-------|-------|---------|------------------------------------------------------------------------------|

| 36h<br>PCM          | 15    | CTRL  | 0       | Sets function and control registers for GPIO / PCM interface pins.           |

| Control             |       |       |         | 0 = GPIO pins as GPIOs                                                       |