### **General Description**

The MAX1304–MAX1306/MAX1308–MAX1310/MAX1312– MAX1314 12-bit, analog-to-digital converters (ADCs) offer eight, four, or two independent input channels. Independent track-and-hold (T/H) circuitry provides simultaneous sampling for each channel. The MAX1304/ MAX1305/MAX1306 provide a 0 to +5V input range with  $\pm$ 6V fault-tolerant inputs. The MAX1308/MAX1309/ MAX1310 provide a  $\pm$ 5V input range with  $\pm$ 16.5V fault-tolerant inputs. The MAX1312/MAX1313/MAX1314 have a  $\pm$ 10V input range with  $\pm$ 16.5V fault-tolerant inputs. These ADCs convert two channels in 0.9µs, and up to eight channels in 1.98µs, with an 8-channel throughput of 456ksps per channel. Other features include a 20MHz T/H input bandwidth, internal clock, internal (+2.5V) or external (+2.0V to +3.0V) reference, and power-saving modes.

A 20MHz, 12-bit, bidirectional parallel data bus provides the conversion results and accepts digital inputs that activate each channel individually.

All devices operate from a +4.75V to +5.25V analog supply and a +2.7V to +5.25V digital supply and consume 57mA total supply current when fully operational.

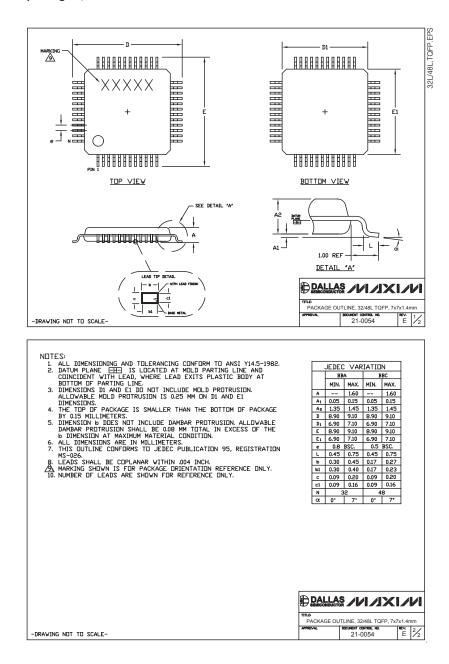

Each device is available in a 48-pin 7mm x 7mm TQFP package and operates over the extended -40°C to  $+85^{\circ}$ C temperature range.

### **Applications**

SIN/COS Position Encoder

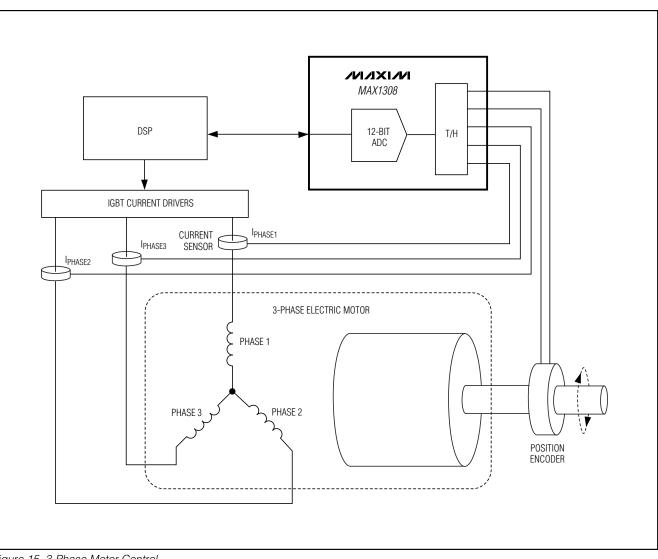

Multiphase Motor Control

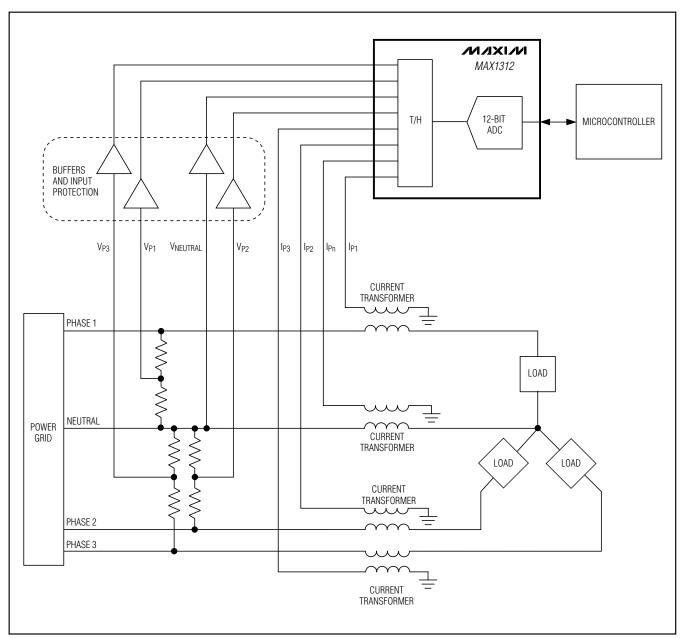

Multiphase Power Monitoring

Power-Grid Synchronization

Power-Factor Monitoring

Vibration and Waveform Analysis

| PART       | INPUT RANGE (V) | CHANNEL COUNT |

|------------|-----------------|---------------|

| MAX1304ECM | 0 to +5         | 8             |

| MAX1305ECM | 0 to +5         | 4             |

| MAX1306ECM | 0 to +5         | 2             |

| MAX1308ECM | ±5              | 8             |

| MAX1309ECM | ±5              | 4             |

| MAX1310ECM | ±5              | 2             |

| MAX1312ECM | ±10             | 8             |

| MAX1313ECM | ±10             | 4             |

| MAX1314ECM | ±10             | 2             |

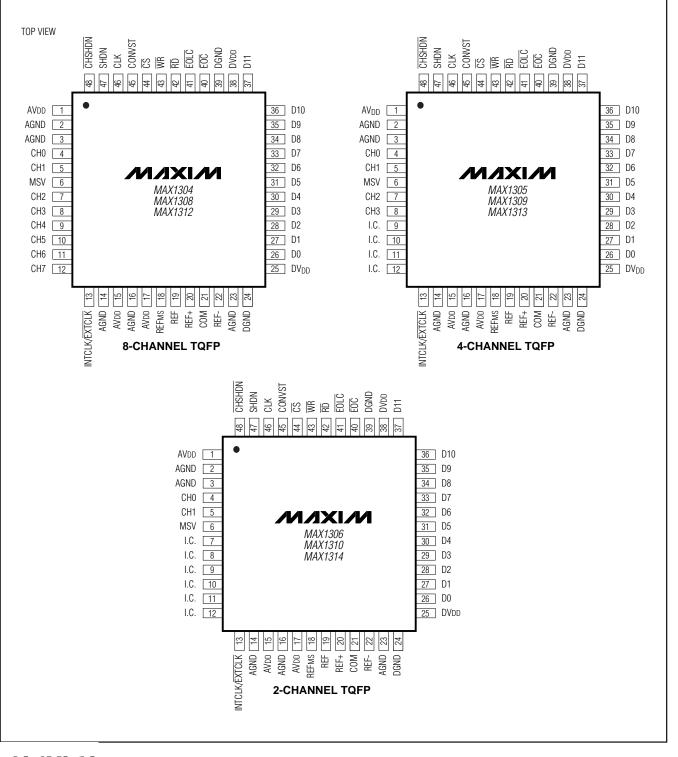

Pin Configurations appear at end of data sheet.

###

# **Selector Guide**

# us-Sampling ADCs

### \_Features

- Up to Eight Channels of Simultaneous Sampling 8ns Aperture Delay 100ps Channel-to-Channel T/H Match

- Extended Input Ranges

0 to +5V (MAX1304/MAX1305/MAX1306)

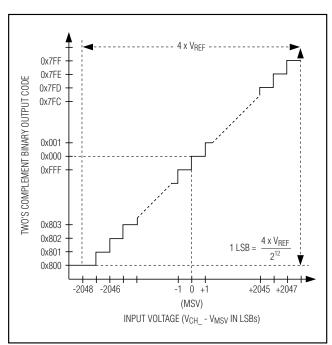

-5V to +5V (MAX1308/MAX1309/MAX1310)

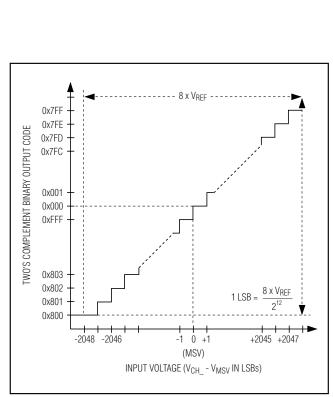

-10V to +10V (MAX1312/MAX1313/MAX1314)

- Fast Conversion Time One Channel in 0.72µs Two Channels in 0.9µs Four Channels in 1.26µs Eight Channels in 1.98µs

- High Throughput 1075ksps/Channel for One Channel 901ksps/Channel for Two Channels 680ksps/Channel for Four Channels 456ksps/Channel for Eight Channels

- + ±1 LSB INL, ±0.9 LSB DNL (max)

- 84dBc SFDR, -86dBc THD, 71dB SINAD, f<sub>IN</sub> = 500kHz at 0.4dBFS

- + 12-Bit, 20MHz, Parallel Interface

- Internal or External Clock

- +2.5V Internal Reference or +2.0V to +3.0V External Reference

- +5V Analog Supply, +3V to +5V Digital Supply 55mA Analog Supply Current 1.3mA Digital Supply Current Shutdown and Power-Saving Modes

- 48-Pin TQFP Package (7mm x 7mm Footprint)

## **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1304ECM | -40°C to +85°C | 48 TQFP     |

| MAX1305ECM | -40°C to +85°C | 48 TQFP     |

| MAX1306ECM | -40°C to +85°C | 48 TQFP     |

| MAX1308ECM | -40°C to +85°C | 48 TQFP     |

| MAX1309ECM | -40°C to +85°C | 48 TQFP     |

| MAX1310ECM | -40°C to +85°C | 48 TQFP     |

| MAX1312ECM | -40°C to +85°C | 48 TQFP     |

| MAX1313ECM | -40°C to +85°C | 48 TQFP     |

| MAX1314ECM | -40°C to +85°C | 48 TQFP     |

### \_\_\_\_\_ Maxim Integrated Products 1

For pricing delivery, and ordering information please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to AGND0.3V to +6V<br>DV <sub>DD</sub> to DGND0.3V to +6V |

|----------------------------------------------------------------------------|

| AGND to DGND0.3V to +0.3V                                                  |

| CH0–CH7, I.C. to AGND (MAX1304/MAX1305/MAX1306)±6V                         |

| CH0-CH7, I.C. to AGND (MAX1308/MAX1309/MAX1310)±16.5V                      |

| CH0-CH7, I.C. to AGND (MAX1312/MAX1313/MAX1314)±16.5V                      |

| D0–D11 to DGND0.3V to (DV <sub>DD</sub> + 0.3V)                            |

| EOC, EOLC, RD, WR, CS to DGND0.3V to (DV <sub>DD</sub> + 0.3V)             |

| CONVST, CLK, SHDN, CHSHDN to DGND0.3V to (DV <sub>DD</sub> + 0.3V)         |

| INTCLK/EXTCLK to AGND0.3V to (AV <sub>DD</sub> + 0.3V)                     |

| REF <sub>MS</sub> , REF, MSV to AGND0.3V to (AV <sub>DD</sub> + 0.3V)           |  |

|---------------------------------------------------------------------------------|--|

| REF+, COM, REF- to AGND0.3V to (AV <sub>DD</sub> + 0.3V)                        |  |

| Maximum Current into Any Pin Except AV <sub>DD</sub> , DV <sub>DD</sub> , AGND, |  |

| DGND±50mA                                                                       |  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                           |  |

| TQFP (derate 22.7mW/°C above +70°C)1818.2mW                                     |  |

| Operating Temperature Range40°C to +85°C                                        |  |

| Junction Temperature+150°C                                                      |  |

| Storage Temperature Range65°C to +150°C                                         |  |

| Lead Temperature (soldering, 10s)+300°C                                         |  |

|                                                                                 |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(AV_{DD} = +5V, DV_{DD} = +3V, AGND = DGND = 0, V_{REF} = V_{REFMS} = +2.5V$  (external reference),  $C_{REF} = C_{REFMS} = 0.1\mu$ F,  $C_{REF+} = C_{REF-} = 0.1\mu$ F,  $C_{REF+-t0-REF-} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{COM} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{MSV} = 2.2\mu$ F II  $0.1\mu$ F (unipolar devices), MSV = AGND (bipolar devices),  $f_{CLK} = 16.67$ MHz 50% duty cycle, INTCLK/EXTCLK = AGND (external clock), SHDN = DGND,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C. See Figures 3 and 4.)

| PARAMETER                          | SYMBOL                      | CONDITIONS                     | MIN | ТҮР  | MAX  | UNITS  |  |  |  |  |

|------------------------------------|-----------------------------|--------------------------------|-----|------|------|--------|--|--|--|--|

| STATIC PERFORMANCE (Note 1         | STATIC PERFORMANCE (Note 1) |                                |     |      |      |        |  |  |  |  |

| Resolution                         | Ν                           |                                | 12  |      |      | Bits   |  |  |  |  |

| Integral Nonlinearity              | INL                         | (Note 2)                       |     | ±0.5 | ±1.0 | LSB    |  |  |  |  |

| Differential Nonlinearity          | DNL                         | No missing codes (Note 2)      |     | ±0.3 | ±0.9 | LSB    |  |  |  |  |

| Offset Error                       |                             | Unipolar, 0x000 to 0x001       |     | ±3   | ±16  | LSB    |  |  |  |  |

| Unset Error                        |                             | Bipolar, 0xFFF to 0x000        |     | ±3   | ±16  | LOD    |  |  |  |  |

| Offeet Error Metebing              |                             | Unipolar, between all channels |     | ±9   | ±20  | LSB    |  |  |  |  |

| Offset-Error Matching              |                             | Bipolar, between all channels  |     | ±9   | ±20  | LOD    |  |  |  |  |

| Offerst Error Terror ersturg Drift |                             | Unipolar, 0x000 to 0x001       |     | 7    |      | ppm/°C |  |  |  |  |

| Offset-Error Temperature Drift     |                             | Bipolar, 0xFFF to 0x000        |     | 7    |      |        |  |  |  |  |

| Gain Error                         |                             |                                |     | ±2   | ±16  | LSB    |  |  |  |  |

| Gain-Error Matching                |                             | Between all channels           |     | ±3   | ±14  | LSB    |  |  |  |  |

| Gain-Error Temperature Drift       |                             |                                |     | 4    |      | ppm/°C |  |  |  |  |

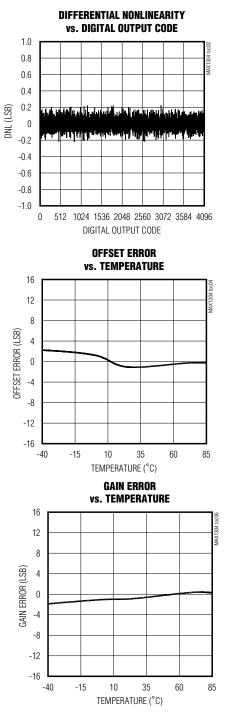

| DYNAMIC PERFORMANCE at fin         | = 500kHz, A                 | NIN = -0.4dBFS (Note 2)        |     |      |      |        |  |  |  |  |

| Signal-to-Noise Ratio              | SNR                         |                                | 68  | 71   |      | dB     |  |  |  |  |

| Signal-to-Noise Plus Distortion    | SINAD                       |                                | 68  | 71   |      | dB     |  |  |  |  |

| Total Harmonic Distortion          | THD                         |                                |     | -86  | -80  | dBc    |  |  |  |  |

| Spurious-Free Dynamic Range        | SFDR                        |                                |     | 84   |      | dBc    |  |  |  |  |

| Channel-to-Channel Isolation       |                             |                                | 80  | 86   |      | dB     |  |  |  |  |

| ANALOG INPUTS (CH0 through         | CH7)                        |                                |     |      |      |        |  |  |  |  |

| Input Voltage                      |                             | MAX1304/MAX1305/MAX1306        | 0   |      | +5   |        |  |  |  |  |

|                                    | VCH                         | MAX1308/MAX1309/MAX1310        | -5  |      | +5   | V      |  |  |  |  |

|                                    |                             | MAX1312/MAX1313/MAX1314        | -10 |      | +10  |        |  |  |  |  |

MAX1304-MAX1306/MAX1308-MAX1310/MAX1312-MAX131

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = +5V, DV_{DD} = +3V, AGND = DGND = 0, V_{REF} = V_{REFMS} = +2.5V$  (external reference),  $C_{REF} = C_{REFMS} = 0.1\mu$ F,  $C_{REF+} = C_{REF-} = 0.1\mu$ F,  $C_{REF+-to}$ -REF- = 2.2 $\mu$ F II 0.1 $\mu$ F,  $C_{COM} = 2.2\mu$ F II 0.1 $\mu$ F,  $C_{MSV} = 2.2\mu$ F II 0.1 $\mu$ F (unipolar devices), MSV = AGND (bipolar devices), f<sub>CLK</sub> = 16.67MHz 50% duty cycle, INTCLK/EXTCLK = AGND (external clock), SHDN = DGND, T\_A = T\_{MIN} to  $T_{MAX}$ , unless otherwise noted. Typical values are at T\_A = +25°C. See Figures 3 and 4.)

| PARAMETER                                     | SYMBOL                                    | CONDITIONS                             |                        | MIN    | TYP   | MAX   | UNITS    |  |

|-----------------------------------------------|-------------------------------------------|----------------------------------------|------------------------|--------|-------|-------|----------|--|

|                                               |                                           | MAX1304/MAX1305/MAX1306                |                        |        | 7.58  |       |          |  |

| Input Resistance                              | RCH                                       | MAX1308/MAX1309MAX1310                 |                        |        | 8.66  |       | kΩ       |  |

| (Note 3)                                      |                                           | MAX1312/MAX1313/MAX1314                |                        |        | 14.26 |       |          |  |

|                                               |                                           |                                        | $V_{CH} = +5V$         |        | 0.54  | 0.72  |          |  |

|                                               |                                           | MAX1304/MAX1305/MAX1306                | $V_{CH} = 0V$          | -0.157 | -0.12 |       | ]        |  |

| Input Current                                 |                                           |                                        | $V_{CH} = +5V$         |        | 0.29  | 0.39  |          |  |

| (Note 3)                                      | ICH                                       | MAX1308/MAX1309/MAX1310                | V <sub>CH</sub> = -5V  | -1.16  | -0.87 |       | mA       |  |

|                                               |                                           |                                        | $V_{CH} = +10V$        |        | 0.56  | 0.74  |          |  |

|                                               |                                           | MAX1312/MAX1313/MAX1314                | V <sub>CH</sub> = -10V | -1.13  | -0.85 |       |          |  |

| Input Capacitance                             | Ссн                                       |                                        | •                      |        | 15    |       | рF       |  |

| TRACK/HOLD                                    |                                           |                                        |                        |        |       |       |          |  |

|                                               |                                           | One channel selected for conve         | ersion                 |        | 1075  |       |          |  |

| External-Clock Throughput Rate                | £                                         | Two channels selected for conv         | version                |        | 901   |       |          |  |

| (Note 4)                                      | fтн                                       | Four channels selected for conversion  |                        |        | 680   |       | ksps     |  |

|                                               |                                           | Eight channels selected for conversion |                        |        | 456   |       |          |  |

|                                               | f                                         | One channel selected for conversion    |                        |        | 983   |       |          |  |

| Internal-Clock Throughput Rate                |                                           | Two channels selected for conv         |                        | 821    |       | kana  |          |  |

| (Note 4, Table 1)                             | fтн                                       | Four channels selected for conversion  |                        | 618    |       |       | ksps     |  |

|                                               |                                           | Eight channels selected for conversion |                        |        | 413   |       | <u> </u> |  |

| Small-Signal Bandwidth                        |                                           |                                        |                        |        | 20    |       | MHz      |  |

| Full-Power Bandwidth                          |                                           |                                        |                        |        | 20    |       | MHz      |  |

| Aperture Delay                                | t <sub>AD</sub>                           |                                        |                        |        | 8     |       | ns       |  |

| Aperture-Delay Matching                       |                                           |                                        |                        |        | 100   |       | ps       |  |

| Aperture Jitter                               | t <sub>AJ</sub>                           |                                        |                        |        | 50    |       | psrms    |  |

| INTERNAL REFERENCE                            |                                           |                                        |                        |        |       |       |          |  |

| REF Output Voltage                            | VREF                                      |                                        |                        | 2.475  | 2.500 | 2.525 | V        |  |

| Reference Output-Voltage<br>Temperature Drift |                                           |                                        |                        |        | 30    |       | ppm/°C   |  |

| REF <sub>MS</sub> Output Voltage              | VREFMS                                    |                                        |                        | 2.475  | 2.500 | 2.525 | V        |  |

| REF+ Output Voltage                           | V <sub>REF+</sub>                         |                                        |                        |        | 3.850 |       | V        |  |

| COM Output Voltage                            | V <sub>COM</sub>                          |                                        |                        |        | 2.600 |       | V        |  |

| REF- Output Voltage                           | VREF-                                     |                                        |                        |        | 1.350 |       | V        |  |

| Differential Reference Voltage                | V <sub>REF+</sub> -<br>V <sub>REF</sub> - |                                        |                        |        | 2.500 |       | V        |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = +5V, DV_{DD} = +3V, AGND = DGND = 0, V_{REF} = V_{REFMS} = +2.5V$  (external reference),  $C_{REF} = C_{REFMS} = 0.1\mu$ F,  $C_{REF+} = C_{REF-} = 0.1\mu$ F,  $C_{REF+-to-REF-} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{COM} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{MSV} = 2.2\mu$ F II  $0.1\mu$ F (unipolar devices), MSV = AGND (bipolar devices), f<sub>CLK</sub> = 16.67MHz 50% duty cycle, INTCLK/EXTCLK = AGND (external clock), SHDN = DGND, T\_A = T\_{MIN} to  $T_{MAX}$ , unless otherwise noted. Typical values are at T\_A = +25°C. See Figures 3 and 4.)

| PARAMETER                              | SYMBOL                                    | CONDITIONS                                                     | MIN                   | TYP   | MAX                  | UNITS |

|----------------------------------------|-------------------------------------------|----------------------------------------------------------------|-----------------------|-------|----------------------|-------|

| EXTERNAL REFERENCE (REF an             | d REF <sub>MS</sub> a                     | re externally driven)                                          |                       |       |                      |       |

| REF Input Voltage Range                | VREF                                      |                                                                | 2.0                   | 2.5   | 3.0                  | V     |

| REF Input Resistance                   | R <sub>REF</sub>                          | (Note 5)                                                       |                       | 5     |                      | kΩ    |

| REF Input Capacitance                  |                                           |                                                                |                       | 15    |                      | рF    |

| REF <sub>MS</sub> Input Voltage Range  | VREFMS                                    |                                                                | 2.0                   | 2.5   | 3.0                  | V     |

| REF <sub>MS</sub> Input Resistance     | RREFMS                                    | (Note 6)                                                       |                       | 5     |                      | kΩ    |

| REF <sub>MS</sub> Input Capacitance    |                                           |                                                                |                       | 15    |                      | pF    |

| REF+ Output Voltage                    | V <sub>REF+</sub>                         | $V_{\text{REF}} = +2.5V$                                       |                       | 3.850 |                      | V     |

| COM Output Voltage                     | VCOM                                      | $V_{\text{REF}} = +2.5V$                                       |                       | 2.600 |                      | V     |

| REF- Output Voltage                    | V <sub>REF-</sub>                         | $V_{REF} = +2.5V$                                              |                       | 1.350 |                      | V     |

| Differential Reference Voltage         | V <sub>REF+</sub> -<br>V <sub>REF</sub> - | $V_{\text{REF}} = +2.5V$                                       |                       | 2.500 |                      | V     |

| DIGITAL INPUTS (D0–D7, RD, WR          | , CS, CLK,                                | SHDN, CHSHDN, CONVST)                                          |                       |       |                      |       |

| Input-Voltage High                     | VIH                                       |                                                                | 0.7 x DV[             | D     |                      | V     |

| Input-Voltage Low                      | VIL                                       |                                                                |                       | 0.5   | 3 x DV <sub>DD</sub> | V     |

| Input Hysteresis                       |                                           |                                                                |                       | 20    |                      | mV    |

| Input Capacitance                      | CIN                                       |                                                                |                       | 15    |                      | pF    |

| Input Current                          | l <sub>IN</sub>                           | $V_{IN} = 0 \text{ or } DV_{DD}$                               |                       | 0.02  | ±1                   | μA    |

| CLOCK-SELECT INPUT (INTCLK/            | EXTCLK)                                   |                                                                |                       |       |                      |       |

| Input-Voltage High                     | VIH                                       |                                                                | 0.7 x AV <sub>E</sub> | D     |                      | V     |

| Input-Voltage Low                      | VIL                                       |                                                                |                       | 0.    | 3 x AV <sub>DD</sub> | V     |

| DIGITAL OUTPUTS (D0-D11, EOC           | , EOLC)                                   |                                                                | <u>.</u>              |       |                      |       |

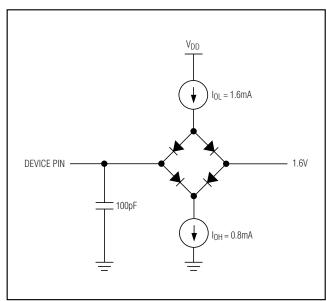

| Output-Voltage High                    | VOH                                       | ISOURCE = 0.8mA, Figure 1                                      | DV <sub>DD</sub> - 0  | .6    |                      | V     |

| Output-Voltage Low                     | VOL                                       | I <sub>SINK</sub> = 1.6mA, Figure 1                            |                       |       | 0.4                  | V     |

| D0-D11 Tri-State Leakage Current       |                                           | $\overline{\text{RD}}$ = high or $\overline{\text{CS}}$ = high |                       | 0.06  | 1                    | μA    |

| D0–D11 Tri-State Output<br>Capacitance |                                           | $\overline{\text{RD}}$ = high or $\overline{\text{CS}}$ = high |                       | 15    |                      | pF    |

| POWER SUPPLIES                         |                                           |                                                                |                       |       |                      |       |

| Analog Supply Voltage                  | AVDD                                      |                                                                | 4.75                  |       | 5.25                 | V     |

| Digital Supply Voltage                 | DVDD                                      |                                                                | 2.70                  |       | 5.25                 | V     |

|                                        |                                           | MAX1304/MAX1305/MAX1306,<br>all channels selected              |                       | 55    | 60                   |       |

| Analog Supply Current                  | IAVDD                                     | MAX1308/MAX1309/MAX1310,<br>all channels selected              |                       | 54    | 60                   | mA    |

|                                        |                                           | MAX1312/MAX1313/MAX1314,<br>all channels selected              |                       | 54    | 60                   |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = +5V, DV_{DD} = +3V, AGND = DGND = 0, V_{REF} = V_{REFMS} = +2.5V$  (external reference),  $C_{REF} = C_{REFMS} = 0.1\mu$ F,  $C_{REF+} = C_{REF-} = 0.1\mu$ F,  $C_{REF+} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{COM} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{MSV} = 2.2\mu$ F II  $0.1\mu$ F (unipolar devices), MSV = AGND (bipolar devices), f<sub>CLK</sub> = 16.67MHz 50% duty cycle, INTCLK/EXTCLK = AGND (external clock), SHDN = DGND, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C. See Figures 3 and 4.)

| PARAMETER                                                      | SYMBOL            | CONDITIONS                                                | MIN | ТҮР       | MAX    | UNITS         |

|----------------------------------------------------------------|-------------------|-----------------------------------------------------------|-----|-----------|--------|---------------|

|                                                                |                   | MAX1304/MAX1305/MAX1306,<br>all channels selected         |     | 1.3       | 2.6    |               |

| Digital Supply Current<br>(C <sub>LOAD</sub> = 100pF) (Note 7) | IDVDD             | MAX1308/MAX1309/MAX1310,<br>all channels selected         |     | 1.3       | 2.6    | mA            |

|                                                                |                   | MAX1312/MAX1313/MAX1314, all channels selected            |     | 1.3       | 2.6    |               |

| Shutdown Current                                               | IAVDD             | SHDN = $DV_{DD}$ , $V_{CH}$ = float                       |     | 0.6       | 10     |               |

| (Note 8)                                                       | IDVDD             | SHDN = $DV_{DD}$ , $\overline{RD} = \overline{WR} = high$ |     | 0.02      | 1      | μA            |

| Power-Supply Rejection Ratio                                   | PSRR              | AV <sub>DD</sub> = +4.75V to +5.25V                       |     | 50        |        | dB            |

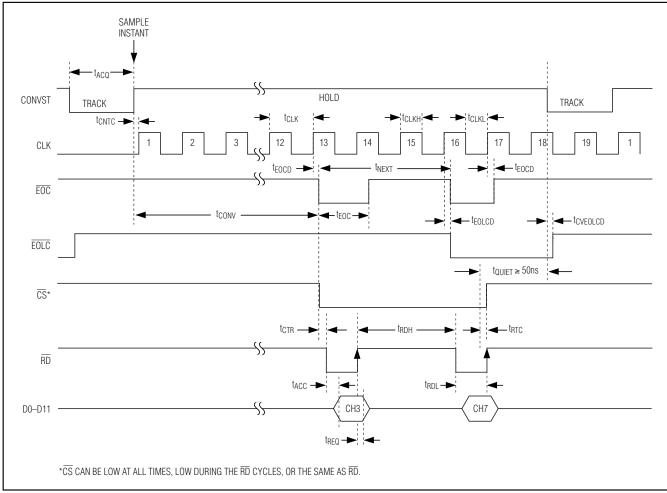

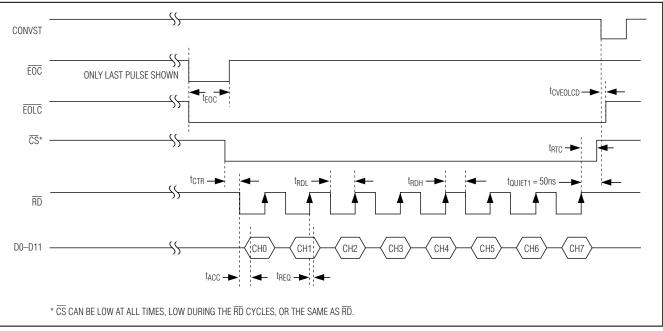

| TIMING CHARACTERISTICS (Figu                                   | re 1)             | ·                                                         |     |           |        |               |

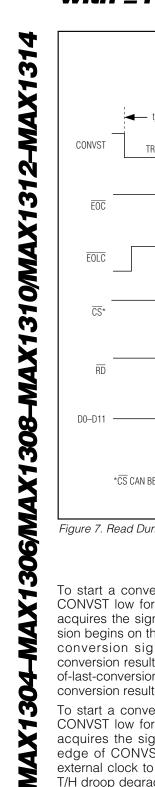

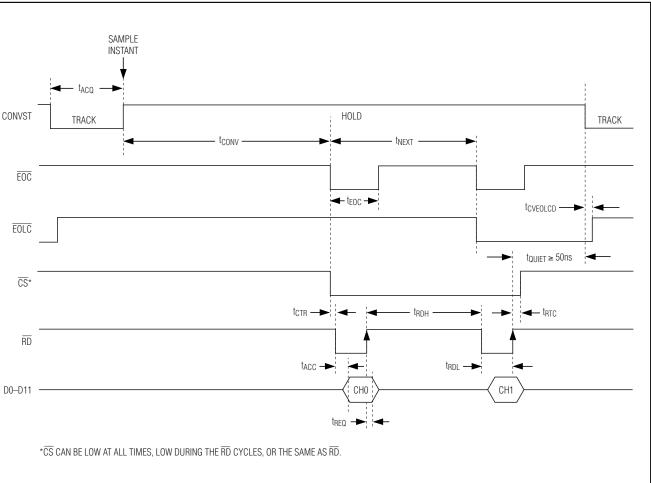

|                                                                |                   | Internal clock, Figure 7                                  |     | 800       | 900    | ns            |

| Time to First Conversion Result                                | tCONV             | External clock, Figure 8                                  |     | 12        |        | CLK<br>Cycles |

|                                                                |                   | Internal clock, Figure 7                                  |     | 200       | 225    | ns            |

| Time to Subsequent Conversions                                 | t <sub>NEXT</sub> | External clock, Figure 8                                  |     | 3         |        | CLK<br>Cycles |

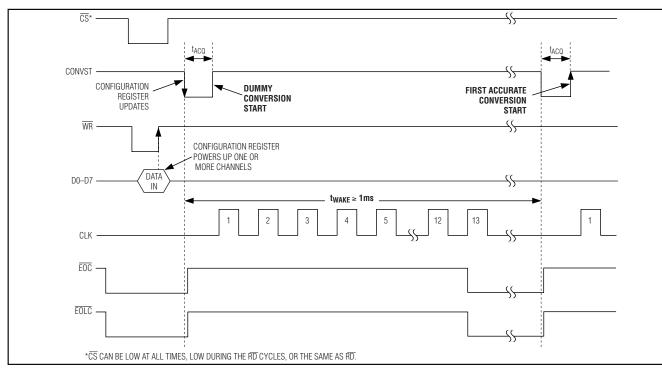

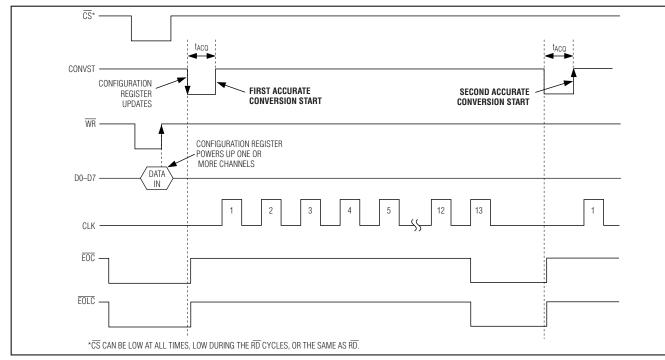

| CONVST Pulse-Width Low<br>(Acquisition Time)                   | tacq              | (Note 9) Figures 6–10                                     | 0.1 |           | 1000.0 | μs            |

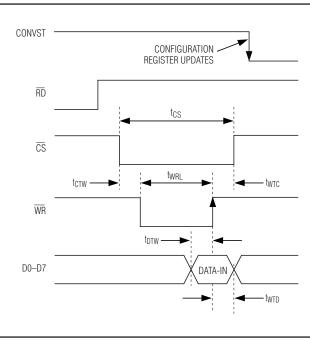

| CS Pulse Width                                                 | tcs               | Figure 6                                                  | 30  |           |        | ns            |

| RD Pulse-Width Low                                             | t <sub>RDL</sub>  | Figures 7, 8, 9                                           | 30  |           |        | ns            |

| RD Pulse-Width High                                            | t <sub>RDH</sub>  | Figures 7, 8, 9                                           | 30  |           |        | ns            |

| WR Pulse-Width Low                                             | twrl              | Figure 6                                                  | 30  |           |        | ns            |

| CS to WR                                                       | tctw              | Figure 6                                                  |     | (Note 10) |        | ns            |

| $\overline{\text{WR}}$ to $\overline{\text{CS}}$               | twrc              | Figure 6                                                  |     | (Note 10) |        | ns            |

| CS to RD                                                       | <b>t</b> CTR      | Figures 7, 8, 9                                           |     | (Note 10) |        | ns            |

| RD to CS                                                       | <b>t</b> RTC      | Figures 7, 8, 9                                           |     | (Note 10) |        | ns            |

| Data Access Time<br>(RD Low to Valid Data)                     | tacc              | Figures 7, 8, 9                                           |     |           | 30     | ns            |

| Bus Relinquish Time (RD High)                                  | treq              | Figures 7, 8, 9                                           | 5   |           | 30     | ns            |

| CLK Rise to EOC Delay                                          | teocd             | Figure 8                                                  |     | 20        |        | ns            |

| CLK Rise to EOLC Fall Delay                                    | <b>t</b> EOLCD    | Figure 8                                                  |     | 20        |        | ns            |

| CONVST Fall to EOLC Rise Delay                                 | <b>t</b> CVEOLCD  | Figures 7, 8, 9                                           | Ì   | 20        |        | ns            |

|                                                                |                   | Internal clock, Figure 7                                  | 50  |           |        | ns            |

| EOC Pulse Width                                                | tEOC              | External clock, Figure 8                                  |     | 1         |        | CLK<br>Cycle  |

### ELECTRICAL CHARACTERISTICS (continued)

$(AV_{DD} = +5V, DV_{DD} = +3V, AGND = DGND = 0, V_{REF} = V_{REFMS} = +2.5V$  (external reference),  $C_{REF} = C_{REFMS} = 0.1\mu$ F,  $C_{REF+} = C_{REF+} = 0.1\mu$ F,  $C_{REF+-to-REF-} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{COM} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{MSV} = 2.2\mu$ F II  $0.1\mu$ F (unipolar devices), MSV = AGND (bipolar devices),  $f_{CLK} = 16.67$ MHz 50% duty cycle, INTCLK/EXTCLK = AGND (external clock), SHDN = DGND,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C. See Figures 3 and 4.)

| PARAMETER                | SYMBOL           | CONDITIONS                                       | MIN  | ТҮР | MAX   | UNITS |

|--------------------------|------------------|--------------------------------------------------|------|-----|-------|-------|

| Input-Data Setup Time    | tDTW             | Figure 6                                         | 10   |     |       | ns    |

| Input-Data Hold Time     | twtd             | Figure 6                                         | 10   |     |       | ns    |

| External CLK Period      | <b>t</b> CLK     | Figures 8, 9                                     | 0.05 |     | 10.00 | μs    |

| External CLK High Period | tсікн            | Logic sensitive to rising edges,<br>Figures 8, 9 | 20   |     |       | ns    |

| External CLK Low Period  | <b>t</b> CLKL    | Logic sensitive to rising edges,<br>Figures 8, 9 | 20   |     |       | ns    |

| External Clock Frequency | fclk             | (Note 11)                                        | 0.1  |     | 20    | MHz   |

| Internal Clock Frequency | f <sub>INT</sub> |                                                  |      | 15  |       | MHz   |

| CONVST High to CLK Edge  | <b>t</b> CNTC    | Figures 8, 9                                     | 20   |     |       | ns    |

Note 1: For the MAX1304/MAX1305/MAX1306,  $V_{IN} = 0$  to +5V. For the MAX1308/MAX1309/MAX1310,  $V_{IN} = -5V$  to +5V. For the MAX1312/MAX1313/MAX1314,  $V_{IN} = -10V$  to +10V.

Note 2: All channel performance is guaranteed by correlation to a single channel test.

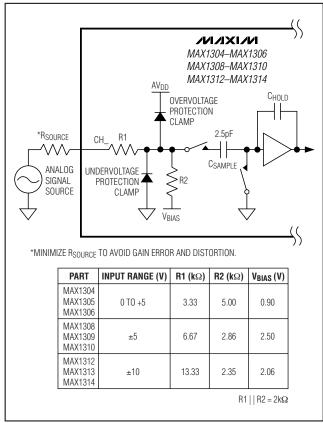

Note 3: The analog input resistance is terminated to an internal bias point (Figure 5). Calculate the analog input current using:

$$I_{CH_{-}} = \frac{V_{CH_{-}} - V_{BIAS}}{R_{CH_{-}}}$$

for V<sub>CH</sub> within the input voltage range.

**Note 4:** Throughput rate is given per channel. Throughput rate is a function of clock frequency ( $f_{CLK}$ ). The external clock throughput rate is specified with  $f_{CLK}$  = 16.67MHz and the internal clock throughput rate is specified with  $f_{CLK}$  = 15MHz. See the *Data Throughput* section for more information.

Note 5: The REF input resistance is terminated to an internal +2.5V bias point (Figure 2). Calculate the REF input current using:

$$I_{\text{REF}} = \frac{V_{\text{REF}} - 2.5V}{R_{\text{REF}}}$$

for V<sub>REF</sub> within the input voltage range.

**Note 6:** The REF<sub>MS</sub> input resistance is terminated to an internal +2.5V bias point (Figure 2). Calculate the REF<sub>MS</sub> input current using:

$$I_{\text{REFMS}} = \frac{V_{\text{REFMS}} - 2.5V}{R_{\text{REFMS}}}$$

for VREFMS within the input voltage range.

Note 7: All analog inputs are driven with a -0.4dBFS 500kHz sine wave.

**Note 8:** Shutdown current is measured with the analog input floating. The large amplitude of the maximum shutdown current specification is due to automated test equipment limitations.

**Note 9:** CONVST must remain low for at least the acquisition period. The maximum acquisition time is limited by internal capacitor droop. **Note 10:** CS to WR and CS to RD are internally AND together. Setup and hold times do not apply.

Note 11: Minimum CLK frequency is limited only by the internal T/H droop rate. Limit the time between the rising edge of CONVST and the falling edge of EOLC to a maximum of 1ms.

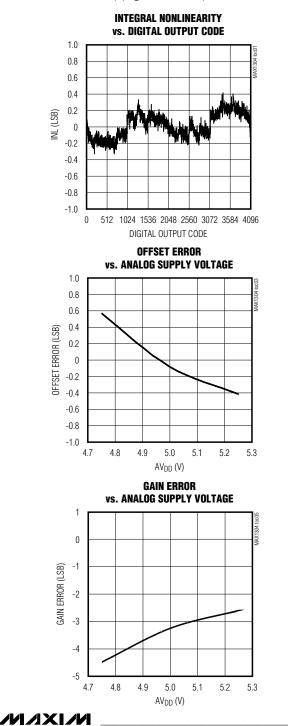

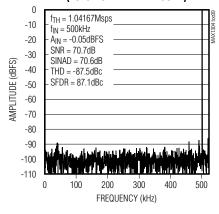

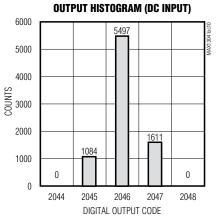

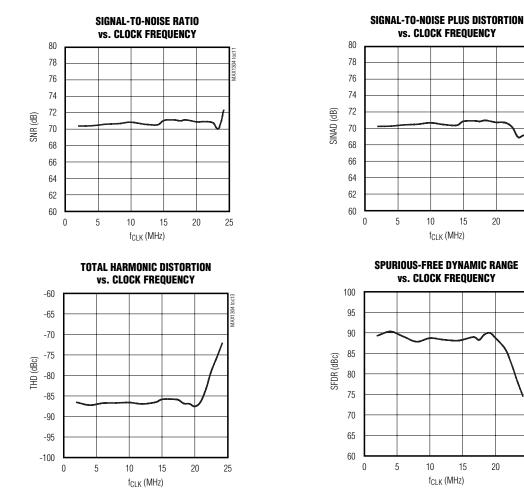

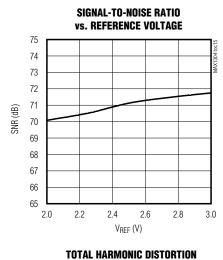

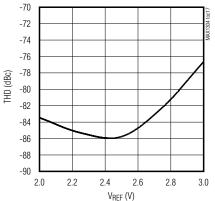

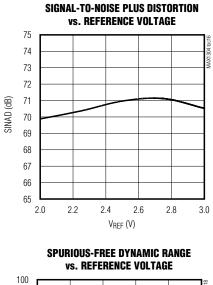

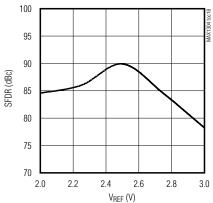

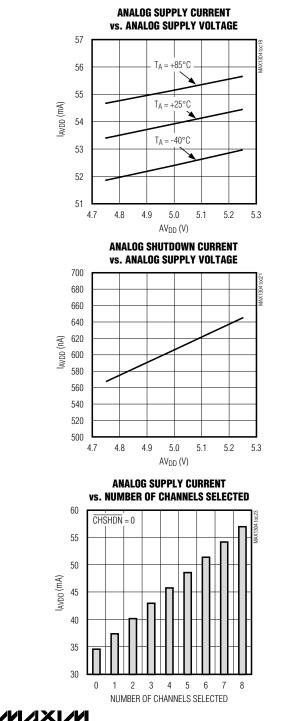

## **Typical Operating Characteristics**

$(AV_{DD} = +5V, DV_{DD} = +3V, AGND = DGND = 0, V_{REF} = V_{REFMS} = +2.5V$  (external reference),  $C_{REF} = C_{REFMS} = 0.1\mu$ F,  $C_{REF+} = C_{REF+} = 0.1\mu$ F,  $C_{REF+} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{COM} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{MSV} = 2.2\mu$ F II  $0.1\mu$ F (unipolar devices), MSV = AGND (bipolar devices),  $f_{CLK} = 16.67$ MHz 50% duty cycle, INTCLK/EXTCLK = AGND (external clock),  $f_{IN} = 500$ kHz,  $A_{IN} = -0.4$ dBFS.  $T_A = +25^{\circ}$ C, unless otherwise noted.) (Figures 3 and 4)

# MAX1304-MAX1306/MAX1308-MAX1310/MAX1312-MAX1314

$(AV_{DD} = +5V, DV_{DD} = +3V, AGND = DGND = 0, V_{REF} = V_{REFMS} = +2.5V$  (external reference),  $C_{REF} = C_{REFMS} = 0.1\mu$ F,  $C_{REF+} = C_{REF-} = 0.1\mu$ F,  $C_{REF+10-REF-} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{COM} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{MSV} = 2.2\mu$ F II  $0.1\mu$ F (unipolar devices), MSV = AGND (bipolar devices), fCLK = 16.67MHz 50% duty cycle, INTCLK/EXTCLK = AGND (external clock), fIN = 500kHz, AIN = -0.4dBFS. TA = +25°C,

### unless otherwise noted.) (Figures 3 and 4) **SMALL-SIGNAL BANDWIDTH** vs. ANALOG INPUT FREQUENCY 2 A<sub>IN</sub> = -20dBFS 0 -2 (gB) -4 GAIN ( -6 -8 -10 -12 0.1 10 100 1 ANALOG INPUT FREQUENCY (MHz)

### **Typical Operating Characteristics (continued)**

### Typical Operating Characteristics (continued)

5

5

10

15

f<sub>CLK</sub> (MHz)

20

25

10

f<sub>CLK</sub> (MHz)

vs. CLOCK FREQUENCY

15

20

25

vs. CLOCK FREQUENCY

(AVDD = +5V, DVDD = +3V, AGND = DGND = 0, VREF = VREFMS = +2.5V (external reference), CREF = CREFMS = 0.1µF, CREF+ =  $C_{REF-} = 0.1 \mu$ F,  $C_{REF+to-REF-} = 2.2 \mu$ F II  $0.1 \mu$ F,  $C_{COM} = 2.2 \mu$ F II  $0.1 \mu$ F,  $C_{MSV} = 2.2 \mu$ F II  $0.1 \mu$ F (unipolar devices), MSV = AGND (bipolar devices), f<sub>CLK</sub> = 16.67MHz 50% duty cycle, INTCLK/EXTCLK = AGND (external clock), f<sub>IN</sub> = 500kHz, A<sub>IN</sub> = -0.4dBFS. T<sub>A</sub> = +25°C, unless otherwise noted.) (Figures 3 and 4)

### **Typical Operating Characteristics (continued)**

$(AV_{DD} = +5V, DV_{DD} = +3V, AGND = DGND = 0, V_{REF} = V_{REFMS} = +2.5V$  (external reference),  $C_{REF} = C_{REFMS} = 0.1\mu$ F,  $C_{REF+} = C_{REF-} = 0.1\mu$ F,  $C_{REF+-to-REF-} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{COM} = 2.2\mu$ F II  $0.1\mu$ F,  $C_{MSV} = 2.2\mu$ F II  $0.1\mu$ F (unipolar devices), MSV = AGND (bipolar devices), f<sub>CLK</sub> = 16.67MHz 50% duty cycle, INTCLK/EXTCLK = AGND (external clock), f<sub>IN</sub> = 500kHz, A<sub>IN</sub> = -0.4dBFS. T<sub>A</sub> = +25°C, unless otherwise noted.) (Figures 3 and 4)

###

MAX1304-MAX1306/MAX1308-MAX1310/MAX1312-MAX1314

$(AV_{DD} = +5V, DV_{DD} = +3V, AGND = DGND = 0, V_{REF} = V_{REFMS} = +2.5V$  (external reference),  $C_{REF} = C_{REFMS} = 0.1\mu$ F,  $C_{REF+} = C_{REF-} = 0.1\mu$ F,  $C_{REF+10}$ -REF- = 2.2 $\mu$ F II 0.1 $\mu$ F,  $C_{COM} = 2.2\mu$ F II 0.1 $\mu$ F,  $C_{MSV} = 2.2\mu$ F II 0.1 $\mu$ F (unipolar devices), MSV = AGND (bipolar devi

### devices), f<sub>CLK</sub> = 16.67MHz 50% duty cycle, INTCLK/EXTCLK = AGND (external clock), f<sub>IN</sub> = 500kHz, A<sub>IN</sub> = -0.4dBFS. T<sub>A</sub> = +25°C, unless otherwise noted.) (Figures 3 and 4) INTERNAL REFERENCE VOLTAGE INTERNAL REFERENCE VOLTAGE vs. ANALOG SUPPLY VOLTAGE vs. TEMPERATURE 2.5004 2.504 2.5003 2.503 2.5002 2.502 2.5001 2.501 S 2 늝 2.5000 늝 2.500 2.4999 2.499 2.4998 2.498 2.4997 2.497 2.4996 2.496 48 4.9 5.0 5.1 52 53 4.7 -40 -15 10 35 60 85 TEMPERATURE (°C) AV<sub>DD</sub> (V) INTERNAL CLOCK CONVERSION TIME **INTERNAL CLOCK CONVERSION TIME** vs. ANALOG SUPPLY VOLTAGE vs. TEMPERATURE 900 820 800 800 700 tCONV tCONV 600 780 TIME (ns) TIME (ns) 500 400 **t**NEXT 300 **t**NFX1 200 200 180 100 0 160 4.7 4.8 4.9 5.0 5.1 5.2 5.3 -40 35 -15 10 60 85 AV<sub>DD</sub> (V) TEMPERATURE (°C) **ANALOG INPUT CHANNEL CURRENT ANALOG INPUT CHANNEL CURRENT** ANALOG INPUT CHANNEL CURRENT vs. ANALOG INPUT CHANNEL VOLTAGE vs. ANALOG INPUT CHANNEL VOLTAGE vs. ANALOG INPUT CHANNEL VOLTAGE 2.0 2.0 3.0 MAX1304/MAX1305/MAX1306 MAX1308/MAX1309/MAX1310 MAX1312/MAX1313/MAX1314 2.5 1.5 1.5 2.0 1.0 1.0 1.5 1.0 0.5 0.5 (mA) 0.5 (mA) 0 0 0 프 -0.5 핑 -0.5 -0.5 -1.0 -1.0 -1.5 -1.0 -2.0 -1.5 -1.5 -2.5 -2.0 -3.0 -2.0 -4 -2 0 2 4 -6 6 -20 -15 -10 -5 0 5 10 15 20 -20 -15 -10 -5 0 5 10 15 20 V<sub>CH</sub>(V) $V_{CH\_}\left(V\right)$ V<sub>CH</sub>(V)

**Typical Operating Characteristics (continued)**

/N/IXI/N

MAX1304-MAX1306/MAX1308-MAX1310/MAX1312-MAX1314 I<sub>CH</sub> (mA) 12

# \_Pin Description

| PIN                           |                               |                               |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|-------------------------------|-------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1304<br>MAX1308<br>MAX1312 | MAX1305<br>MAX1309<br>MAX1313 | MAX1306<br>MAX1310<br>MAX1314 | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1, 15, 17                     | 1, 15, 17                     | 1, 15, 17                     | AV <sub>DD</sub>  | Analog Power Input. $AV_{DD}$ is the power input for the analog section of the converter. Apply +5V to $AV_{DD}$ . Connect all $AV_{DD}$ pins together. See the <i>Layout</i> , <i>Grounding, and Bypassing</i> section for additional information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2, 3, 14,<br>16, 23           | 2, 3, 14,<br>16, 23           | 2, 3, 14,<br>16, 23           | AGND              | Analog Ground. AGND is the power return for AV <sub>DD</sub> . Connect all AGND pins together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4                             | 4                             | 4                             | CH0               | Channel 0 Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5                             | 5                             | 5                             | CH1               | Channel 1 Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6                             | 6                             | 6                             | MSV               | Midscale Voltage Bypass. For the unipolar MAX1304/MAX1305/MAX1306,<br>connect a 2.2µF and a 0.1µF capacitor from MSV to AGND. For the bipolar<br>MAX1308/MAX1309/MAX1310/MAX1312/MAX1313/MAX1314, connect<br>MSV to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7                             | 7                             | —                             | CH2               | Channel 2 Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8                             | 8                             | _                             | CH3               | Channel 3 Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9                             | _                             | —                             | CH4               | Channel 4 Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10                            | _                             | _                             | CH5               | Channel 5 Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11                            | _                             | _                             | CH6               | Channel 6 Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12                            | _                             | _                             | CH7               | Channel 7 Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13                            | 13                            | 13                            | INTCLK/<br>EXTCLK | Clock-Mode Select Input. Connect INTCLK/EXTCLK to AV <sub>DD</sub> to select the internal clock. Connect INTCLK/EXTCLK to AGND to use an external clock connected to CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 18                            | 18                            | 18                            | REF <sub>MS</sub> | Midscale Reference Bypass or Input. REF <sub>MS</sub> connects through a 5k $\Omega$ resistor to the internal +2.5V bandgap reference buffer.<br>For the MAX1304/MAX1305/MAX1306 unipolar devices, V <sub>REFMS</sub> is the input to the unity-gain buffer that drives MSV. MSV sets the midpoint of the input voltage range. For internal reference operation, bypass REF <sub>MS</sub> with a ≥0.01µF capacitor to AGND. For external reference operation, drive REF <sub>MS</sub> with an external voltage from +2V to +3V.<br>For the MAX1308/MAX1309/MAX1310/MAX1312/MAX1313/MAX1314 bipolar devices, connect REF <sub>MS</sub> to REF. For internal reference operation, bypass the REF <sub>MS</sub> /REF node with a ≥0.01µF capacitor to AGND. For external voltage from +2V to +3V. |

| 19                            | 19                            | 19                            | REF               | ADC Reference Bypass or Input. REF connects through a $5k\Omega$ resistor to the internal +2.5V bandgap reference buffer.<br>For internal reference operation, bypass REF with a $\geq 0.01\mu$ F capacitor.<br>For external reference operation with the MAX1304/MAX1305/MAX1306<br>unipolar devices, drive REF with an external voltage from +2V to +3V.<br>For external reference operation with the MAX1308/MAX1309/MAX1310/<br>MAX1312/MAX1313/MAX1314 bipolar devices, connect REF <sub>MS</sub> to REF and<br>drive the REF <sub>MS</sub> /REF node with an external voltage from +2V to +3V.                                                                                                                                                                                           |

### **Pin Description (continued)**

|                               | PIN                           |                               | PIN              |                                                                                                                                                                                                                                                                            |  |  |

|-------------------------------|-------------------------------|-------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX1304<br>MAX1308<br>MAX1312 | MAX1305<br>MAX1309<br>MAX1313 | MAX1306<br>MAX1310<br>MAX1314 | NAME             | FUNCTION                                                                                                                                                                                                                                                                   |  |  |

| 20                            | 20                            | 20                            | REF+             | Positive Reference Bypass. Bypass REF+ with a 0.1 $\mu$ F capacitor to AGND. Also bypass REF+ to REF- with a 2.2 $\mu$ F and a 0.1 $\mu$ F capacitor.<br>V <sub>REF+</sub> = V <sub>COM</sub> + V <sub>REF</sub> / 2.                                                      |  |  |

| 21                            | 21                            | 21                            | СОМ              | Reference Common Bypass. Bypass COM to AGND with a 2.2 $\mu$ F and a 0.1 $\mu$ F capacitor. V <sub>COM</sub> = 13 / 25 x AV <sub>DD</sub> .                                                                                                                                |  |  |

| 22                            | 22                            | 22                            | REF-             | Negative Reference Bypass. Bypass REF- with a 0.1 $\mu$ F capacitor to AGND.<br>Also bypass REF- to REF+ with a 2.2 $\mu$ F and a 0.1 $\mu$ F capacitor.<br>V <sub>REF+</sub> = V <sub>COM</sub> - V <sub>REF</sub> / 2.                                                   |  |  |

| 24, 39                        | 24, 39                        | 24, 39                        | DGND             | Digital Ground. DGND is the power return for DV <sub>DD</sub> . Connect all DGND pins together.                                                                                                                                                                            |  |  |

| 25, 38                        | 25, 38                        | 25, 38                        | DV <sub>DD</sub> | Digital Power Input. DV <sub>DD</sub> powers the digital section of the converter, including the parallel interface. Apply +2.7V to +5.25V to DV <sub>DD</sub> . Bypass DV <sub>DD</sub> to DGND with a 0.1 $\mu$ F capacitor. Connect all DV <sub>DD</sub> pins together. |  |  |

| 26                            | 26                            | 26                            | D0               | Digital I/O 0 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                                |  |  |

| 27                            | 27                            | 27                            | D1               | Digital I/O 1 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                                |  |  |

| 28                            | 28                            | 28                            | D2               | Digital I/O 2 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                                |  |  |

| 29                            | 29                            | 29                            | D3               | Digital I/O 3 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                                |  |  |

| 30                            | 30                            | 30                            | D4               | Digital I/O 4 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                                |  |  |

| 31                            | 31                            | 31                            | D5               | Digital I/O 5 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                                |  |  |

| 32                            | 32                            | 32                            | D6               | Digital I/O 6 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                                |  |  |

| 33                            | 33                            | 33                            | D7               | Digital I/O 7 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                                |  |  |

| 34                            | 34                            | 34                            | D8               | Digital Output 8 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                             |  |  |

| 35                            | 35                            | 35                            | D9               | Digital Output 9 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                             |  |  |

| 36                            | 36                            | 36                            | D10              | Digital Output 10 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                            |  |  |

| 37                            | 37                            | 37                            | D11              | Digital Output 11 of 12-Bit Parallel Data Bus. High impedance when $\overline{RD} = 1$ or $\overline{CS} = 1$ .                                                                                                                                                            |  |  |

| 40                            | 40                            | 40                            | EOC              | End-of-Conversion Output. EOC goes low to indicate the end of a conversion. It returns high on the next rising CLK edge or the falling CONVST edge.                                                                                                                        |  |  |

| 41                            | 41                            | 41                            | EOLC             | End-of-Last-Conversion Output. EOLC goes low to indicate the end of the last conversion. It returns high when CONVST goes low for the next conversion sequence.                                                                                                            |  |  |

| 42                            | 42                            | 42                            | RD               | Read Input. Pulling RD low initiates a read command of the parallel data bus.                                                                                                                                                                                              |  |  |

| 43                            | 43                            | 43                            | WR               | Write Input. Pulling WR low initiates a write command for configuring the devic with D0–D7.                                                                                                                                                                                |  |  |

## **Pin Description (continued)**

|                               | PIN                           |                               |        |                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------|-------------------------------|-------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1304<br>MAX1308<br>MAX1312 | MAX1305<br>MAX1309<br>MAX1313 | MAX1306<br>MAX1310<br>MAX1314 | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                             |

| 44                            | 44                            | 44                            | CS     | Chip-Select Input. Pulling $\overline{CS}$ low activates the digital interface. Forcing $\overline{CS}$ high places D0–D11 in high-impedance mode.                                                                                                                                                                                                                                                   |

| 45                            | 45                            | 45                            | CONVST | Conversion Start Input. Driving CONVST high initiates the conversion process.<br>The analog inputs are sampled on the rising edge of CONVST.                                                                                                                                                                                                                                                         |

| 46                            | 46                            | 46                            | CLK    | External Clock Input. For external clock operation, connect INTCLK/EXTCLK to DGND and drive CLK with an external clock signal from 100kHz to 20MHz. For internal clock operation, connect INTCLK/EXTCLK to DV <sub>DD</sub> and connect CLK to DGND.                                                                                                                                                 |

| 47                            | 47                            | 47                            | SHDN   | Shutdown Input. Driving SHDN high initiates device shutdown. Connect SHDN to DGND for normal operation.                                                                                                                                                                                                                                                                                              |

| 48                            | 48                            | 48                            | CHSHDN | Active-Low Analog-Input Channel-Shutdown Input. Drive CHSHDN low to<br>power down analog inputs that are not selected for conversion in the<br>configuration register. Drive CHSHDN high to power up all analog input<br>channels regardless of whether they are selected for conversion in the<br>configuration register. See the <i>Channel Shutdown</i> (CHSHDN) section for more<br>information. |

|                               | 9, 10,<br>11, 12              | 7, 8, 9,<br>10, 11, 12        | I.C.   | Internally connected. Connect I.C. to AGND.                                                                                                                                                                                                                                                                                                                                                          |

Figure 1. Digital Load Test Circuit

### **Detailed Description**

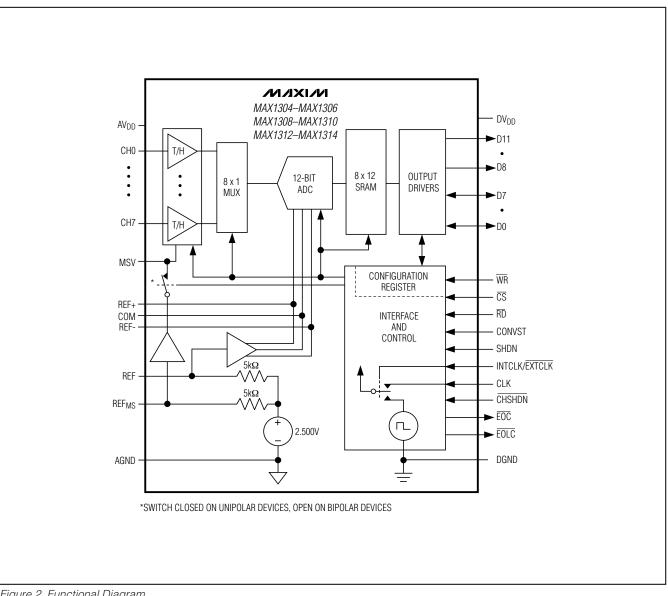

The MAX1304-MAX1306/MAX1308-MAX1310/MAX1312-MAX1314 are 12-bit ADCs. The devices offer 8, 4, or 2 independently selectable input channels, each with dedicated T/H circuitry. Simultaneous sampling of all active channels preserves relative phase information making these devices ideal for motor control and power monitoring. Three input ranges are available, 0 to +5V,  $\pm$ 5V and  $\pm$ 10V. The 0 to  $\pm$ 5V devices provide  $\pm$ 6V faulttolerant inputs. The  $\pm 5V$  and  $\pm 10V$  devices provide ±16.5V fault-tolerant inputs. Two-channel conversion results are available in 0.9µs. Conversion results from all eight channels are available in 1.98µs. The 8-channel throughput is 456ksps per channel. Internal or external reference and clock capability offer great flexibility, and ease of use. A write-only configuration register can mask out unused channels and a shutdown feature reduces power. A 20MHz, 12-bit, parallel data bus outputs the conversion results. Figure 2 shows the functional diagram of these ADCs.

Figure 2. Functional Diagram

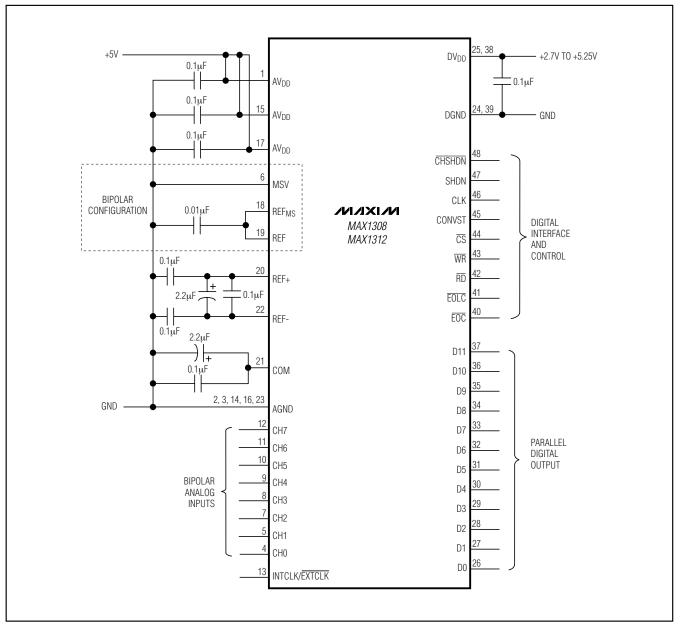

Figure 3. Typical Bipolar Operating Circuit

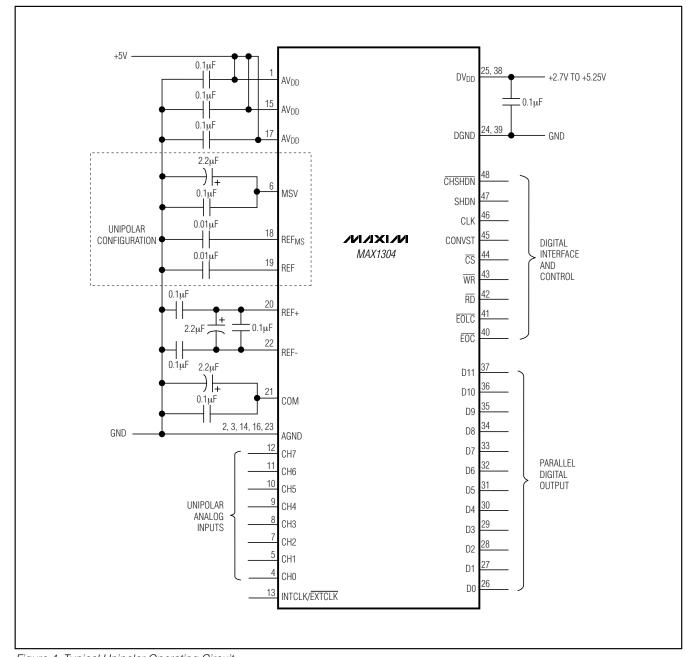

Figure 4. Typical Unipolar Operating Circuit

Figure 5. Single-Channel, Equivalent Analog Input T/H Circuit

### Analog Inputs

### Track and Hold (T/H)

To preserve phase information across the multichannel MAX1304–MAX1306/MAX1308–MAX1310/MAX1312–MAX1314, all input channels have dedicated T/H amplifiers. Figure 5 shows the equivalent analog input T/H circuit for one channel.

The input T/H circuit is controlled by the CONVST input. When CONVST is low, the T/H circuit tracks the analog input. When CONVST is high the T/H circuit holds the analog input. The rising edge of CONVST is the analog input sampling instant. There is an aperture delay (t<sub>AD</sub>) of 8ns and a 50ps<sub>RMS</sub> aperture jitter (t<sub>AJ</sub>). The aperture delay of each dedicated T/H input is matched within 100ps of each other.

To settle the charge on C<sub>SAMPLE</sub> to 12-bit accuracy, use a minimum acquisition time ( $t_{ACQ}$ ) of 100ns. Therefore, CONVST must be low for at least 100ns. Although longer acquisition times allow the analog input to settle to its final value more accurately, the maximum

acquisition time must be limited to 1ms. Accuracy with conversion times longer than 1ms cannot be guaranteed due to capacitor droop in the input circuitry.

Due to the analog input resistive divider formed by R1 and R2 in Figure 5, any significant analog input source resistance (R<sub>SOURCE</sub>) results in gain error. Furthermore, R<sub>SOURCE</sub> causes distortion due to nonlinear analog input currents. Limit R<sub>SOURCE</sub> to a maximum of  $100\Omega$ .

### **Selecting an Input Buffer**

To improve the input signal bandwidth under AC conditions, drive the input with a wideband buffer (>50MHz) that can drive the ADC's input capacitance (15pF) and settle quickly. For example, the MAX4431 or the MAX4265 can be used for the 0 to +5V unipolar devices, or the MAX4350 can be used for  $\pm$ 5V bipolar inputs.

Most applications require an input buffer to achieve 12-bit accuracy. Although slew rate and bandwidth are important, the most critical input buffer specification is settling time. The simultaneous sampling of multiple channels requires an acquisition time of 100ns. At the beginning of the acquisition, the ADC internal sampling capacitor array connects to the analog inputs, causing some disturbance. Ensure the amplifier is capable of settling to at least 12-bit accuracy during this interval. Use a low-noise, low-distortion, wideband amplifier that settles quickly and is stable with the ADC's 15pF input capacitance.

See the Maxim website at www.maxim-ic.com for application notes on how to choose the optimum buffer amplifier for your ADC application.

### Input Bandwidth

The input-tracking circuitry has a 20MHz small-signal bandwidth, making it possible to digitize high-speed transient events and measure periodic signals with bandwidths exceeding the ADC's sampling rate by using undersampling techniques. To avoid high-frequency signals being aliased into the frequency band of interest, anti-alias filtering is recommended.

### Input Range and Protection

The MAX1304/MAX1305/MAX1306 provide a 0 to +5V input voltage range with fault protection of  $\pm$ 6V. The MAX1308/MAX1309/MAX1310 provide a  $\pm$ 5V input voltage range with fault protection of  $\pm$ 16.5V. The MAX1312/MAX1313/MAX1314 provide a  $\pm$ 10V input voltage range with fault protection of  $\pm$ 16.5V. Figure 5 shows the single-channel equivalent input circuit.

### Data Throughput

The data throughput (fTH) of the MAX1304–MAX1306/ MAX1308–MAX1310/MAX1312–MAX1314 is a function of the clock speed (f<sub>CLK</sub>). In internal clock mode, f<sub>CLK</sub> = 15MHz (typ). In external clock mode, 100kHz  $\leq$  f<sub>CLK</sub>  $\leq$ 20MHz. When reading during conversion (Figures 7 and 8), calculate f<sub>TH</sub> as follows:

$$f_{TH} = \frac{1}{t_{ACQ} + t_{QUIET} + \frac{12 + 3 \times (N-1) + 1}{f_{CLK}}}$$

where N is the number of active channels and tQUIET is the period of bus inactivity before the rising edge of CONVST. See the *Starting a Conversion* section for more information.

Table 1 uses the above equation and shows the total throughput as a function of the number of channels selected for conversion.

### **Clock Modes**

The MAX1304–MAX1306/MAX1308–MAX1310/MAX1312– MAX1314 provide a 15MHz internal conversion clock. Alternatively, an external clock can be used.

### Internal Clock

Internal clock mode frees the microprocessor from the burden of running the ADC conversion clock. For internal clock operation, connect INTCLK/EXTCLK to AV<sub>DD</sub> and connect CLK to DGND. Note that INTCLK/EXTCLK is referenced to AV<sub>DD</sub>, not DV<sub>DD</sub>.

### External Clock

For external clock operation, connect INTCLK/EXTCLK to AGND and connect an external clock source to CLK. Note that INTCLK/EXTCLK is referenced to AV<sub>DD</sub>, not DV<sub>DD</sub>. The external clock frequency can be up to 20MHz. Linearity is not guaranteed with clock frequencies below 100kHz due to droop in the T/H circuits.

|                            |                                      | •                                             | -                                |                               |                                    |

|----------------------------|--------------------------------------|-----------------------------------------------|----------------------------------|-------------------------------|------------------------------------|

| CHANNELS<br>SAMPLED<br>(N) | CLOCK CYCLES<br>UNTIL<br>LAST RESULT | CLOCK CYCLE<br>FOR READING<br>LAST CONVERSION | TOTAL<br>CONVERSION<br>TIME (ns) | TOTAL<br>THROUGHPUT<br>(ksps) | THROUGHPUT<br>PER CHANNEL<br>(fth) |

| 1                          | 12                                   | 1                                             | 800                              | 983                           | 983                                |

| 2                          | 15                                   | 1                                             | 1000                             | 1643                          | 821                                |

| 3                          | 18                                   | 1                                             | 1200                             | 2117                          | 705                                |

| 4                          | 21                                   | 1                                             | 1400                             | 2474                          | 618                                |

| 5                          | 24                                   | 1                                             | 1600                             | 2752                          | 550                                |

| 6                          | 27                                   | 1                                             | 1800                             | 2975                          | 495                                |

| 7                          | 30                                   | 1                                             | 2000                             | 3157                          | 451                                |

| 8                          | 33                                   | 1                                             | 2200                             | 3310                          | 413                                |

### Table 1. Throughput vs. Channels Sampled: f<sub>CLK</sub> = 15MHz, t<sub>ACQ</sub> = 100ns, t<sub>QUIET</sub> = 50ns

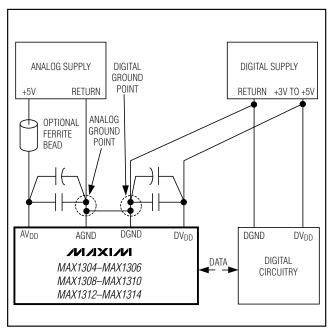

### Applications Information

### **Digital Interface**