19-2192: Rev 0: 10/01

# **Dual-Rate Fibre Channel Repeaters**

### **General Description**

The MAX3772-MAX3775 are dual-rate (1.0625Gbps and 2.125Gbps) fibre channel repeaters. They are optimized for use in fibre channel arbitrated loop applications and operate from a +3.3V supply. The MAX3772-MAX3775 exceed fibre channel jitter tolerance requirements and can recover data signals with up to 0.7 unit interval (UI) jitter. The circuit's fully integrated phase-locked loop (PLL) provides a frequency lock indication and does not need an external reference clock. These repeaters provide low-jitter CML clock and data outputs, and are pin compatible with the MAX3770 repeater (except RATESEL pin and exposed paddle). The MAX3773/MAX3774 can also be used for impedance transformation between  $100\Omega$  (differential) and  $150\Omega$  (differential) systems. To reduce the number of external components, all signal inputs and outputs are internally terminated. The MAX3772-MAX3775 are available in 16-pin QSOP-EP packages.

## **Applications**

1.0625Gbps/2.125Gbps Dual-Rate Fibre Channel

Fibre Channel Data Storage Systems

Storage Area Networks

Fibre Channel Hubs

$100\Omega/150\Omega$  (Differential) Impedance Transformation

#### **Features**

- ♦ Pin Selectable 1.0625Gbps/2.125Gbps Dual-Rate Fibre Channel Operation

- ♦ Exceeds Fibre Channel Jitter Tolerance Requirements

- ◆ 1400mV Differential Output Swing

- ♦ +3.0V to +3.6V Operation

- ♦ No Reference Clock Required

- ♦ Frequency Lock Indication

- ◆ 290mW Power Consumption (MAX3775) at +3.3V

- ♦  $100\Omega/150\Omega$  (differential) Input/Output **Terminations**

### **Ordering Information**

| PART       | TEMP. RANGE  | PIN-PACKAGE |

|------------|--------------|-------------|

| MAX3772CEE | 0°C to +70°C | 16 QSOP-EP  |

| MAX3773CEE | 0°C to +70°C | 16 QSOP-EP  |

| MAX3774CEE | 0°C to +70°C | 16 QSOP-EP  |

| MAX3775CEE | 0°C to +70°C | 16 QSOP-EP  |

Pin Configuration appears at end of data sheet.

Selector Guide appears at end of data sheet.

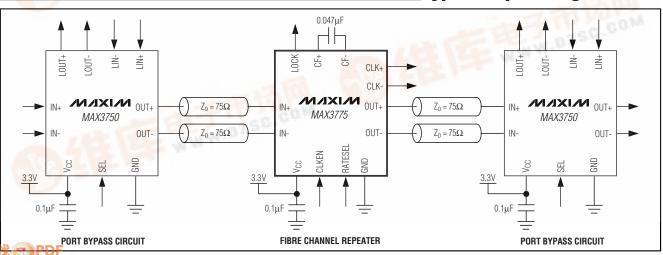

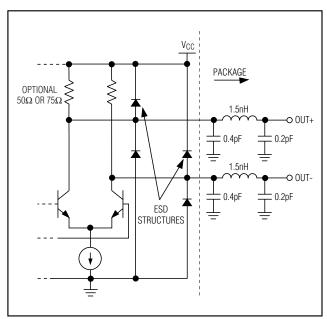

# Typical Operating Circuits

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> 0.5V to +5.0V                                | Continuous Po |

|--------------------------------------------------------------|---------------|

| Pin Voltage Levels (IN±, CF±,                                | 16-Pin QSC    |

| RATESEL, CLKEN, LOCK)0.5V to (V <sub>CC</sub> + 0.5V)        | Operating Jur |

| Current into LOCK1mA to +10mA                                | Operating Ter |

| CML Output Currents (OUT±, CLK±), $R_{OUT} = 75\Omega$ +22mA | Storage Temp  |

| CML Output Currents (OUT±, CLK±), $R_{OUT} = 50\Omega$ +33mA | Lead Tempera  |

Continuous Power Dissipation (TA = +70°C)

16-Pin QSOP-EP (derate 18.9mW/°C above +70°C) ...702mW

Operating Junction Temperature Range ......55°C to +150°C

Operating Temperature Range .....55°C to +110°C

Storage Temperature Range .....55°C to +150°C

Lead Temperature (soldering, 10s) .....+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, 8B/10B \text{ data coding, } C_F = 0.047 \mu\text{F, lock pin loaded with } \geq 15 \text{k}\Omega$  resistor, all high-speed inputs and outputs AC-coupled,  $T_A = 0^{\circ}\text{C}$  to +70°C, unless otherwise noted. Typical values are at  $V_{CC} = +3.3 \text{V}$ ,  $T_A = +25^{\circ}\text{C}$ .)

| PARAMETER                        | CONDITIONS                                     |                                          | MIN  | TYP                    | MAX                       | UNITS   |

|----------------------------------|------------------------------------------------|------------------------------------------|------|------------------------|---------------------------|---------|

|                                  | CLKEN = GND                                    | MAX3772/MAX3773                          | 80   | 101                    | 140                       |         |

| Council Comment (Nate 1)         | CLKEN = GND                                    | MAX3774/MAX3775                          | 68   | 88                     | 124                       | mA      |

| Supply Current (Note 1)          | CLICENT Voc                                    | MAX3772/MAX3773                          | 115  | 146                    | 195                       |         |

|                                  | CLKEN = V <sub>CC</sub>                        | MAX3774/MAX3775                          | 95   | 121                    | 164                       |         |

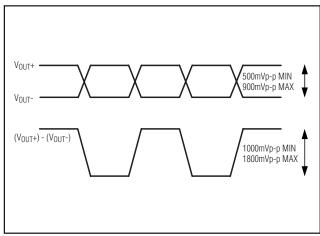

| Differential Voltage Signal      | Figure 4                                       | MAX3772/MAX3773, 100 $\Omega$ terminated | 1000 | 1400                   | 1800                      | mVp-p   |

| at OUT±                          | Figure 1                                       | MAX3774/MAX3775, $150\Omega$ terminated  | 1000 | 1400                   | 1800                      |         |

| Differential Voltage Signal      | Figure 1                                       | MAX3772/MAX3773<br>100Ω terminated       | 1000 | 1400                   | 1800                      | mVp-p   |

| at CLK±                          | Figure 1                                       | MAX3774/MAX3775, $150\Omega$ terminated  | 1000 | 1400                   | 1800                      | - mvp-p |

| Input Data Rate Range            | 1.0625Gbps operation, RATESEL = GND            |                                          | -100 |                        | +100                      | nnm     |

| Input Data Rate Range            | 2.125Gbps operation, RATESEL = V <sub>CC</sub> |                                          | -100 |                        | +100                      | ppm     |

| Input Edge Speed                 | 20% to 80% 1.0625Gbps operation                |                                          | 136  |                        | 325                       | ps      |

| input Lage Speed                 | 20% to 80% 2.125Gbps operation                 |                                          | 75   |                        | 160                       | þδ      |

| Data Transition Time (OUT±)      | 20% to 80% (Note 2)                            |                                          | 100  | 130                    | 175                       | ps      |

| Clock Transition Time (CLK±)     | 20% to 80% (Note 2)                            |                                          | 50   | 75                     | 100                       | ps      |

| LOCK Output Low                  | $I_{OL} = +250\mu A \text{ (sinking)}$         |                                          |      |                        | 0.4                       | V       |

| LOCK Output High                 | I <sub>OH</sub> = -100μA (sourcing)            |                                          | 2.4  |                        |                           | V       |

| CLKEN, RATESEL Input Current     |                                                |                                          |      |                        | 50                        | μΑ      |

| CLKEN, RATESEL Input Low         |                                                |                                          | -0.3 |                        | 0.8                       | V       |

| CLKEN, RATESEL Input High        |                                                |                                          | 2    |                        | V <sub>C</sub> C<br>+ 0.3 | V       |

| Differential Input Voltage Swing |                                                |                                          | 200  |                        | 2200                      | mVp-p   |

| Input Common-Mode Voltage        |                                                |                                          |      | V <sub>CC</sub> - 0.45 |                           | V       |

| Differential Voltage across CF±  | (Note 2)                                       |                                          |      |                        | Vcc                       | V       |

| CDR Lock Time                    | Input = CJTPAT (Note 3)                        |                                          |      | 500                    |                           | μs      |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=+3.0V\ to\ +3.6V,\ 8B/10B\ data\ coding,\ C_F=0.047\mu F,\ lock\ pin\ loaded\ with\ \ge\ 15k\Omega$  resistor, all high-speed inputs and outputs AC-coupled,  $T_A=0^{\circ}C$  to +70°C, unless otherwise noted. Typical values are at  $V_{CC}=+3.3V,\ T_A=+25^{\circ}C$ .)

| PARAMETER                                                              | CONDITIONS                       |                                | MIN | TYP | MAX  | UNITS |

|------------------------------------------------------------------------|----------------------------------|--------------------------------|-----|-----|------|-------|

| Differential Input Resistance                                          | MAX3772/MAX3774                  |                                | 78  | 100 | 122  |       |

| (IN <u>+</u> )                                                         | MAX3773/MAX3775                  |                                | 118 | 150 | 182  | Ω     |

| Differential Output Resistance                                         | MAX3772/MAX3773                  |                                |     | 100 | 122  |       |

| (OUT <u>+,</u> CLK <u>+</u> )                                          | MAX3774/MAX3775                  |                                | 118 | 150 | 182  | Ω     |

|                                                                        | 10Hz ≤ f < 100Hz                 |                                |     | 100 |      |       |

| Supply Noise Tolerance (Note 4)                                        | 100Hz ≤ f < 1MHz                 | 100Hz ≤ f < 1MHz               |     | 40  |      | mVp-p |

| (Note 4)                                                               | 1MHz ≤ f < 2.5GHz                |                                |     | 10  |      | 1     |

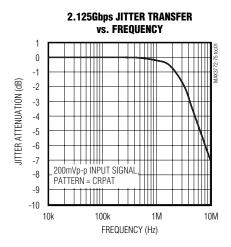

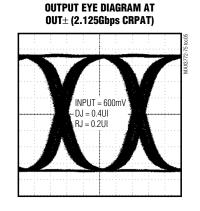

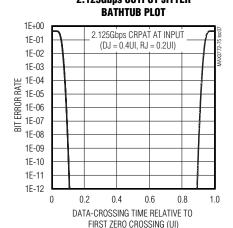

| OPERATION AT 2.125Gbps (No                                             | te 2)                            |                                |     |     |      |       |

| Dandon litter Consertion at                                            | Input = K28.7 (Note 5)           |                                |     | 4.4 |      |       |

| Random Jitter Generation at OUT± and CLK±                              | Input = CRPAT (Note 6)           |                                |     | 2.8 |      | psRMS |

|                                                                        | Input = CRPAT (Notes 6,          | 7)                             |     | 2.9 |      |       |

| Deterministic Jitter on OUT+                                           | Input = K28.5 (Note 8)           |                                |     |     | 22   | nen r |

| Deterministic ditter on COT+                                           | Input = RPAT (Notes 7, 9         | 9)                             |     |     | 48   | psp-p |

| Total Jitter at OUT±                                                   | Input = RPAT (Notes 7, 9         | 9, 10)                         |     |     | 99   | psp-p |

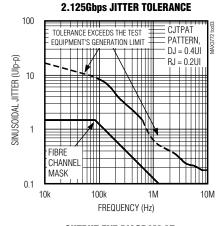

| 0: .1.10                                                               | L CITDAT                         | f = 85kHz                      | 1.5 |     |      |       |

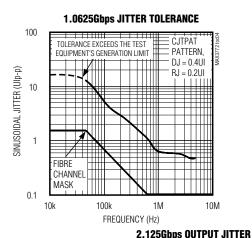

| Sinusoidal Component of Jitter Tolerance (BER = 10 <sup>-12</sup> )    | Input = CJTPAT (Notes 3, 7)      | f = 1270kHz                    | 0.1 |     |      | UI    |

| Tolerance (BETT = To )                                                 | (140103 0, 1)                    | f = 10MHz                      | 0.1 |     |      |       |

| Total High-Frequency Jitter Tolerance                                  | Input = CJTPAT (Notes 3          | Input = CJTPAT (Notes 3, 7, 9) |     |     |      | UI    |

| Jitter Transfer Bandwidth                                              | Measured with 50% edge density   |                                |     |     | 11   | MHz   |

| Jitter Transfer Peaking                                                | (Note 11)                        |                                |     |     | 0.05 | dB    |

| Propagation Delay                                                      |                                  |                                |     | 1.0 | 1.5  | ns    |

| Clock to Q Delay                                                       | Falling clock to data transition |                                | 150 | 280 | 300  | ps    |

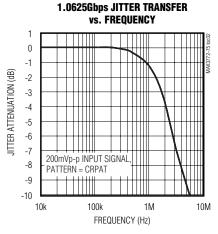

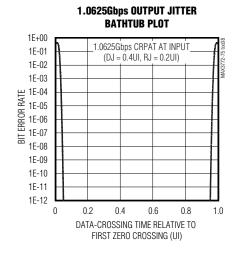

| $ \textbf{OPERATION AT 1.0625Gbps} \; (N \\$                           | ote 2)                           |                                |     |     |      |       |

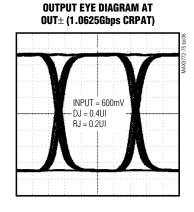

| D 1 177 0 17                                                           | Input = K28.7 (Note 5)           |                                |     | 6.2 |      |       |

| Random Jitter Generation at OUT± and CLK±                              | Input = CRPAT (Note 6)           |                                |     | 3.6 |      | psRMS |

| OUT AND CLIVE                                                          | Input = CRPAT (Notes 6, 7)       |                                |     | 4.9 |      |       |

| Deterministic litter on OLIT                                           | Input = K28.5 (Note 8)           |                                |     |     | 40   | 200 0 |

| Deterministic Jitter on OUT±                                           | Input = RPAT (Notes 7, 9)        |                                |     |     | 75   | psp-p |

| Total Jitter at OUT±                                                   | Input = RPAT (Notes 7, 9, 10)    |                                |     |     | 160  | psp-p |

| Sinusoidal Component of Jitter<br>Tolerance (BER = 10 <sup>-12</sup> ) | In and OITDAT                    | f = 42.5kHz                    | 1.5 |     |      |       |

|                                                                        | Input = CJTPAT<br>(Notes 3, 7)   | f = 635kHz                     | 0.1 |     |      | UI    |

|                                                                        | (140103 0, 1)                    | f = 5MHz                       | 0.1 |     |      |       |

| Total High-Frequency Jitter<br>Tolerance                               | Input = CJTPAT (Notes 3, 7, 9)   |                                | 0.7 |     |      | UI    |

| Jitter Transfer Bandwidth                                              | Measured with 50% edge density   |                                |     |     | 6    | MHz   |

| Jitter Transfer Peaking                                                | (Note 11)                        |                                |     |     | 0.05 | dB    |

| Propagation Delay                                                      |                                  |                                |     |     | 5    | ns    |

|                                                                        | Falling clock to data transition |                                |     |     |      | +     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, 8B/10B \text{ data coding, } C_F = 0.047 \mu\text{F, lock pin loaded with} \ge 15 \text{k}\Omega$  resistor, all high-speed inputs and outputs AC-coupled,  $T_A = 0^{\circ}\text{C}$  to +70°C, unless otherwise noted. Typical values are at  $V_{CC} = +3.3 \text{V}$ ,  $T_A = +25^{\circ}\text{C}$ .)

Note 1: Supply current includes output currents.

Note 2: Guaranteed by design and characterization.

Note 3: Compliant jitter tolerance pattern in hex (CJTPAT):

| Pattern Sequence:             | Repetitions: |

|-------------------------------|--------------|

| 3E AA 2A AA AA                | 6            |

| 3E AA A6 A5 A9                | 1            |

| 87 1E 38 71 E3                | 41           |

| 87 1E 38 70 BC 78 F4 AA AA AA | 1            |

| AA AA AA AA                   | 12           |

| AA A1 55 55 E3 87 1E 38 71 E1 | 1            |

| AB 9C 96 86 E6                | 1            |

| C1 6A AA 9A A6                | 1            |

Note 4: Meets jitter output specifications with noise applied.

Note 5: K28.7 Pattern: 00 1111 1000.

Note 6: Compliant random pattern in hex (CRPAT):

| Pattern Sequence:                       | Repetitions: |

|-----------------------------------------|--------------|

| 3E AA 2A AA AA                          | 6            |

| 3E AA A6 A5 A9                          | 1            |

| 86 BA 6C64 75 D0 E8 DC A8 B4 79 49 EA A | 6 65 16      |

| 72 31 9A 95 AB                          | 1            |

| C1 6A AA 9A A6                          | 1            |

|                                         |              |

- **Note 7:** Parameter measured with 0.40UI deterministic jitter (patterns other than K28.7), and 0.20UI random jitter (BER =  $10^{-12}$ ) applied to the input. Jitter is in compliance with the inter-enclosure, fibre channel jitter tolerance (at compliance point  $\alpha_R$ ) and jitter output (at compliance point  $\alpha_T$ ) specifications (FC-PI rev 10.0). Output jitter is specified as an output total given a non-zero jitter input.

- Note 8: K28.5 Pattern: 00 1111 1010 11 0000 0101

- Note 9: Random Pattern in hex (RPAT): 3EB0 5C67 85D3 172C A856 D84B B6A6 65

- Note 10: Using differential drive over the entire input amplitude range. The input signal bandwidth is limited to 0.75 x (bit-rate) by a 4th-order Bessel Thompson filter or equivalent. Total jitter (TJ) is the range of the eye pattern where the BER exceeds 10-12. TJ can be estimated as TJ = DJ + 14 x RJ. DJ is deterministic jitter. RJ is a one sigma distribution (RMS) of random jitter.

- Note 11: Simulation shows peaking of 0.01dB max. Characterization results limited by test equipment.

### **Typical Operating Characteristics**

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

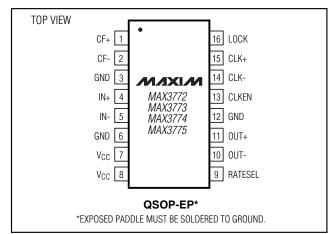

### Pin Description

| PIN      | NAME              | FUNCTION                                                                                                                                                                              |

|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | CF+               | CDR Filter Capacitor Positive Connection. $C_F = 0.047 \mu F$ .                                                                                                                       |

| 2        | CF-               | CDR Filter Capacitor Negative Connection. $C_F = 0.047 \mu F$ .                                                                                                                       |

| 3, 6, 12 | GND               | Electrical Ground                                                                                                                                                                     |

| 4        | IN+               | Noninverted Data Input                                                                                                                                                                |

| 5        | IN-               | Inverted Data Input                                                                                                                                                                   |

| 7, 8     | Vcc               | Supply Voltage                                                                                                                                                                        |

| 9        | RATESEL           | Rate Select Pin. TTL low selects 1.0625Gbps operation. TTL high selects 2.125Gbps operation.                                                                                          |

| 10       | OUT-              | Inverted Data Output                                                                                                                                                                  |

| 11       | OUT+              | Noninverted Data Output                                                                                                                                                               |

| 13       | CLKEN             | Clock Output Enable. TTL high enables the clock output. TTL low disables the clock output.                                                                                            |

| 14       | CLK-              | Inverted Clock Output. Enabled when CLKEN is forced high; disabled when CLKEN is forced low.                                                                                          |

| 15       | CLK+              | Noninverted Clock Output. Enabled when CLKEN is forced high; disabled when CLKEN is forced low.                                                                                       |

| 16       | LOCK              | Frequency Lock Indicator. When data is present, a high level indicates the PLL is frequency-locked. The output of the LOCK pin may chatter when large jitter is applied to the input. |

| EP       | Exposed<br>Paddle | The exposed paddle must be soldered to the circuit board ground for proper thermal performance.                                                                                       |

Figure 1. Example of Output Signal with Matched Output Loads

# **Detailed Description**

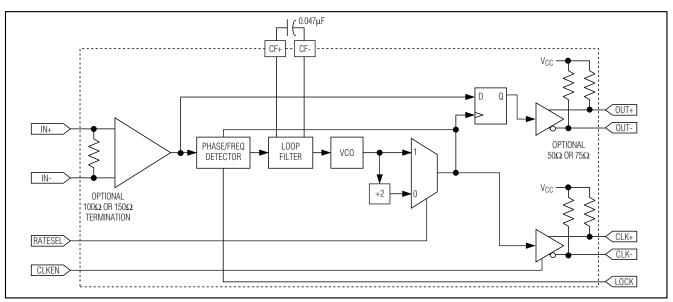

Figure 2 shows the functional block diagram of the MAX3772–MAX3775 fibre channel repeaters. They consist of a fully integrated PLL, CML input and output buffers, and a data latch. The PLL consists of a combined phase detector (PD) and frequency detector (FD), a loop filter, and a voltage-controlled oscillator (VCO). The input and output signal buffers employ lownoise CML architecture and are terminated on-chip.

#### Phase and Frequency Detector

The frequency difference between the VCO clock and the received data is derived by sampling the in-phase and quadrature VCO outputs on the edges of the input data signal. The FD drives the VCO until the frequency difference is reduced to zero. Once frequency acquisition is complete, the PD produces a voltage proportional to the phase difference between the incoming data and the internal clock. The PLL drives this error voltage to zero, aligning the recovered clock to the center of the incoming eye.

Figure 2. Block Diagram

#### Loop Filter, VCO, and Latch

The phase detector and frequency detector outputs are summed into a loop filter. An external capacitor (between CF+ and CF-) is required to set the PLL damping factor. The fully integrated VCO contains an internal current reference and filter circuitry to minimize the influence of V<sub>CC</sub> noise. The VCO creates a clock output with frequency proportional to the control voltage applied by the loop filter. Data recovery is accomplished by using the recovered clock signal to latch the incoming data to the CML output buffers, significantly reducing output jitter.

#### **LOCK Output**

An active high LOCK output monitor derived from the frequency detector indicates that the PLL is frequency-locked onto the input data. Without input data, the LOCK signal may settle high or low. The use of a low-pass RC filter is recommended to reduce the effects of chatter that could be caused by high input-jitter content. For optimum jitter performance, keep the load  $\geq 15 k\Omega$  on the output of the LOCK pin.

#### **RATESEL Input**

The RATESEL input is used to select between input data rates of 2.125Gbps and 1.0625Gbps. This function allows the repeater to sample data at the correct data rate by selecting a divide-by-2 network, giving maximum jitter tolerance at both data rates. The loop bandwidth of the repeater scales with the selected frequency; i.e., the loop-bandwidth at an input rate of 1.0625Gbps is half that at the input rate of 2.125Gbps.

See the *Applications Information* section for the functionality of the RATESEL pin.

# Applications Information

#### **Input and Output Terminations**

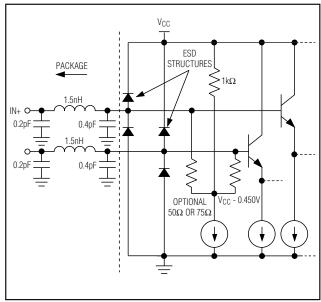

Figures 3 and 4 show models for the MAX3772–MAX3775 inputs and outputs, including packaging parasitics.

Figure 3. Input Structure

Figure 4. Output Structure

#### **Control Functions**

The MAX3772-MAX3775 have two control inputs: RATESEL and CLKEN.

RATESEL is an input that sets the operational data rate for the repeaters. Table 1 shows the selected input data rates when using the RATESEL function.

CLKEN is an input that can be used to enable or disable the output clock, as shown in Table 2.

Table 1. Input Data Rate Using RATESEL Function

| RATESEL LEVEL | DATA RATE SELECTED |

|---------------|--------------------|

| GND           | 1.0625Gbps         |

| Vcc           | 2.125Gbps          |

**Table 2. CLKEN Function**

| CLKEN LEVEL | CLOCK OUTPUT |

|-------------|--------------|

| GND         | Disabled     |

| Vcc         | Enabled      |

### Layout Procedure

The MAX3772-MAX3775 performance can be greatly affected by circuit-board layout and design. Use good high-frequency design techniques, including minimizing ground inductance and using fixed-impedance transmission lines on the data and clock signals. All IN, OUT, and CLK pins should be connected with 0.1µF coupling capacitors equivalent or better than X5R. A 0.047µF capacitor should be used for the loop filter. If DC coupling is desired pay particular attention to the DC voltage and current requirements at the pins of interest (see DC Electrical Characteristics). The MAX3750/MAX3754/MAX3755 port bypass circuits can be DC-coupled to the Maxim dual-rate repeaters. The exposed paddle of the repeater must be connected to ground and should be soldered onto the circuit board for optimal thermal and electrical operation.

### **Pin Configuration**

#### **Selector Guide**

| PART       | DIFFERENTIAL<br>INPUT<br>TERMINATION | DIFFERENTIAL<br>OUTPUT<br>TERMINATION |

|------------|--------------------------------------|---------------------------------------|

| MAX3772CEE | 100Ω                                 | 100Ω                                  |

| MAX3773CEE | 150Ω                                 | 100Ω                                  |

| MAX3774CEE | 100Ω                                 | 150Ω                                  |

| MAX3775CEE | 150Ω                                 | 150Ω                                  |

## **Chip Information**

TRANSISTOR COUNT: 1280

PROCESS: Si

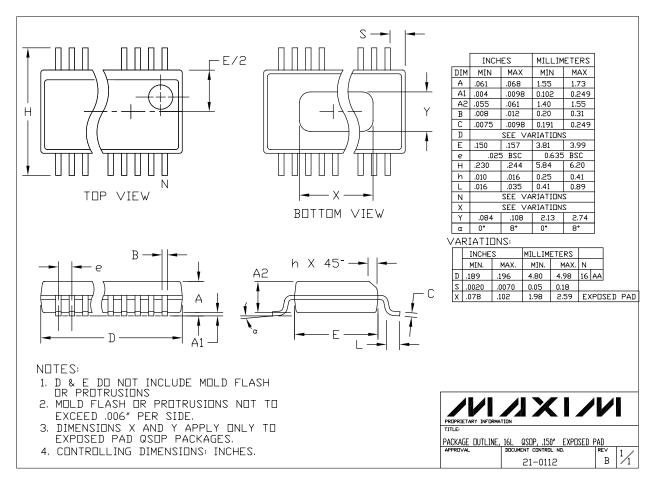

### **Package Information**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.