### **General Description**

The MAX8740 is a high-performance, step-up DC-DC converter that provides a regulated supply voltage for active-matrix, thin-film transistor (TFT), liquid-crystal displays (LCDs). The MAX8740 incorporates currentmode, fixed-frequency, pulse-width modulation (PWM) circuitry with a built-in n-channel power MOSFET to achieve high efficiency and fast transient response.

Users can select 640kHz or 1.2MHz operation using a logic input pin (FREQ). The high switching frequencies allow the use of ultra-small inductors and low-ESR ceramic capacitors. The current-mode architecture provides fast transient response to pulsed loads. A compensation pin (COMP) gives users flexibility in adjusting loop dynamics. The 30V internal MOSFET can generate output voltages up to 28V from a 2.6V and 5.5V input voltage range. Soft-start slowly ramps the input current and is programmed with an external capacitor.

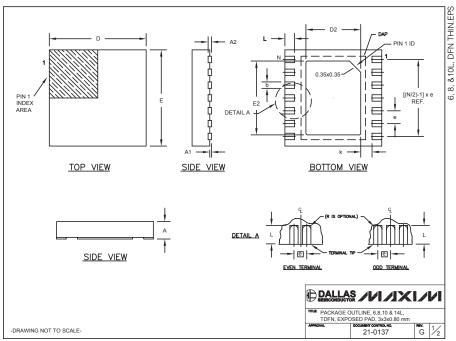

The MAX8740 is available in a 10-pin thin DFN package.

**Features**

- ♦ 90% Efficiency

- ◆ Adjustable Output from V<sub>IN</sub> to 28V

- ♦ 2.6V to 5.5V Input Supply Range

- ♦ Input Supply Undervoltage Lockout

- ♦ Pin-Programmable 640kHz/1.2MHz Switching Frequency

- ♦ Programmable Soft-Start

- ♦ 0.1µA Shutdown Current

- ♦ Small, 10-Pin Thin DFN Package

### **Applications**

Notebook Computer Displays LCD Monitor Panels

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE       |

|------------|----------------|-------------------|

| MAX8740ETB | -40°C to +85°C | 10 TDFN 3mm x 3mm |

## Pin Configuration

# TOP VIEW FREQ SS 10 6 /VI/IXI/VI MAX8740 5 4 THIN DFN 3mm x 3mm

MAXMA

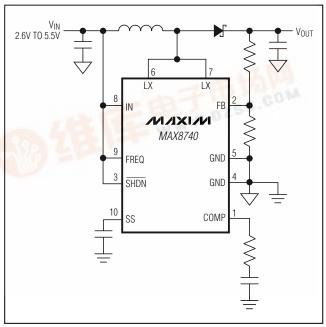

## Minimal Operating Circuit

## **ABSOLUTE MAXIMUM RATINGS**

| LX to GND0.3V to +30V                                 | Operating Temperature Range40°C to +85° |

|-------------------------------------------------------|-----------------------------------------|

| IN, SHDN, FREQ, FB to GND0.3V to +6V                  | Junction Temperature+150°               |

| COMP, SS to GND0.3V to (V <sub>IN</sub> + 0.3V)       | Storage Temperature Range65°C to +160°  |

| LX Switch Maximum Continuous RMS Current2.4A          | Lead Temperature (soldering, 10s)+300°  |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                                         |

| 10-Pin TDFN (derate 24.1mW/°C above +70°C)1481.5mW    |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{\overline{SHDN}} = 3V, T_A = 0^{\circ}C \text{ to } +85^{\circ}C.$  Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                            | CONDITIONS                                                                          | MIN  | TYP   | MAX  | UNITS  |

|--------------------------------------|-------------------------------------------------------------------------------------|------|-------|------|--------|

| Innut Valtage Denge                  | V <sub>OUT</sub> < 18V                                                              | 2.6  |       | 5.5  | V      |

| Input Voltage Range                  | 18V < V <sub>OUT</sub> < 24V                                                        | 4.0  |       | 5.5  | V      |

| Output Voltage Range                 |                                                                                     |      |       | 28   | V      |

| IN Undervoltage-Lockout<br>Threshold | V <sub>IN</sub> rising, typical hysteresis is 50mV; LX remains off below this level | 2.20 | 2.38  | 2.57 | V      |

| IN G : 1 G :                         | V <sub>FB</sub> = 1.3V, not switching                                               |      | 0.22  | 0.44 |        |

| IN Quiescent Current                 | V <sub>FB</sub> = 1.0V, switching, FREQ = GND                                       |      | 2     | 5    | mA     |

| IN Shutdown Current                  | SHDN = GND                                                                          |      | 0.1   | 10.0 | μΑ     |

| ERROR AMPLIFIER                      |                                                                                     | •    |       |      |        |

| FB Regulation Voltage                | Level to produce V <sub>COMP</sub> = 1.24V                                          | 1.22 | 1.24  | 1.26 | V      |

| FB Input Bias Current                | V <sub>FB</sub> = 1.24V                                                             | 50   | 125   | 250  | nA     |

| FB Line Regulation                   | Level to produce V <sub>COMP</sub> = 1.24V, V <sub>IN</sub> = 2.6V to 5.5V          |      | 0.05  | 0.15 | %/V    |

| Transconductance                     |                                                                                     | 100  | 200   | 315  | μS     |

| Voltage Gain                         |                                                                                     |      | 2400  |      | V/V    |

| OSCILLATOR                           |                                                                                     |      |       |      |        |

| English and a second                 | FREQ = GND                                                                          | 540  | 640   | 740  | 1.1.1- |

| Frequency                            | FREQ = IN                                                                           | 1000 | 1220  | 1500 | kHz    |

| Maximum Duty Cycle                   |                                                                                     | 88   | 91    | 94   | %      |

| n-CHANNEL MOSFET                     |                                                                                     |      |       |      |        |

| Current Limit                        | V <sub>FB</sub> = 1V, 71% duty cycle                                                | 3.9  | 4.6   | 5.3  | А      |

| On Basistanas                        | V <sub>IN</sub> = 3V (typ value at T <sub>A</sub> = +25°C)                          |      | 0.11  | 0.17 | 0      |

| On-Resistance                        | $V_{IN} = 5V$ (typ value at $T_A = +25^{\circ}C$ )                                  |      | 0.095 | 0.15 | Ω      |

| Leakage Current                      | V <sub>L</sub> X = 28V                                                              |      | 30    | 55   | μΑ     |

| Current-Sense Transresistance        |                                                                                     | 0.09 | 0.15  | 0.25 | V/A    |

| SOFT-START                           |                                                                                     |      |       |      |        |

| Reset Switch Resistance              |                                                                                     |      |       | 100  | Ω      |

| Charge Current                       | V <sub>SS</sub> = 1.2V                                                              | 2.5  | 4.5   | 7.5  | μΑ     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{\overline{SHDN}} = 3V, T_A = 0^{\circ}C \text{ to } +85^{\circ}C.$  Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                     | CONDITIONS                     | MIN                      | TYP                      | MAX                      | UNITS |

|-------------------------------|--------------------------------|--------------------------|--------------------------|--------------------------|-------|

| CONTROL INPUTS                |                                |                          |                          |                          |       |

| SHDN, FREQ Input Low Voltage  | V <sub>IN</sub> = 2.6V to 5.5V |                          |                          | 0.3 x<br>V <sub>IN</sub> | V     |

| SHDN, FREQ Input High Voltage | V <sub>IN</sub> = 2.6V to 5.5V | 0.7 x<br>V <sub>IN</sub> |                          |                          | V     |

| SHDN, FREQ Input Hysteresis   | V <sub>IN</sub> = 2.6V to 5.5V |                          | 0.1 x<br>V <sub>IN</sub> |                          | V     |

| FREQ Pulldown Current         |                                | 2.3                      | 6.0                      | 9.5                      | μΑ    |

| SHDN Input Current            | SHDN = GND                     |                          | 0.001                    | 1                        | μΑ    |

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{\overline{SHDN}} = 3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) (Note 1)$

| PARAMETER                     | CONDITIONS                                                                 | MIN                      | TYP  | MAX                      | UNITS   |  |

|-------------------------------|----------------------------------------------------------------------------|--------------------------|------|--------------------------|---------|--|

| Input Valtage Dange           | V <sub>OUT</sub> < 18V                                                     | 2.6                      |      | 5.5                      | V       |  |

| Input Voltage Range           | 18V < V <sub>OUT</sub> < 28V                                               | 4.0                      |      | 5.5                      | V       |  |

| Output Voltage Range          |                                                                            |                          |      | 28                       | V       |  |

| INI Quiaggent Current         | V <sub>FB</sub> = 1.3V, not switching                                      |                          |      | 0.44                     | m ^     |  |

| IN Quiescent Current          | V <sub>FB</sub> = 1.0V, switching, FREQ = GND                              |                          |      | 5                        | mA      |  |

| IN Shutdown Current           | SHDN = GND                                                                 |                          |      | 10                       | μΑ      |  |

| ERROR AMPLIFIER               |                                                                            |                          |      |                          |         |  |

| FB Regulation Voltage         | Level to produce V <sub>COMP</sub> = 1.24V                                 | 1.215                    |      | 1.260                    | V       |  |

| FB Line Regulation            | Level to produce V <sub>COMP</sub> = 1.24V, V <sub>IN</sub> = 2.6V to 5.5V |                          |      | 0.15                     | %/V     |  |

| Transconductance              |                                                                            | 100                      |      | 330                      | μS      |  |

| OSCILLATOR                    |                                                                            |                          |      |                          |         |  |

| - Francisco de la company     | FREQ = GND                                                                 | 490                      |      | 770                      | kHz     |  |

| Frequency                     | FREQ = IN                                                                  | 900                      | 1600 |                          | K⊓Z<br> |  |

| n-CHANNEL MOSFET              |                                                                            |                          |      |                          |         |  |

| Current Limit                 | V <sub>FB</sub> = 1V, 71% duty cycle                                       | 3.9                      |      | 5.3                      | А       |  |

| Current-Sense Transresistance |                                                                            | 0.09                     |      | 0.25                     | V/A     |  |

| CONTROL INPUTS                |                                                                            |                          |      |                          |         |  |

| SHDN, FREQ Input Low Voltage  | V <sub>IN</sub> = 2.6V to 5.5V                                             |                          |      | 0.3 x<br>V <sub>IN</sub> | V       |  |

| SHDN, FREQ Input High Voltage | V <sub>IN</sub> = 2.6V to 5.5V                                             | 0.7 x<br>V <sub>IN</sub> |      |                          | V       |  |

**Note 1:** -40°C specifications are guaranteed by design, not production tested.

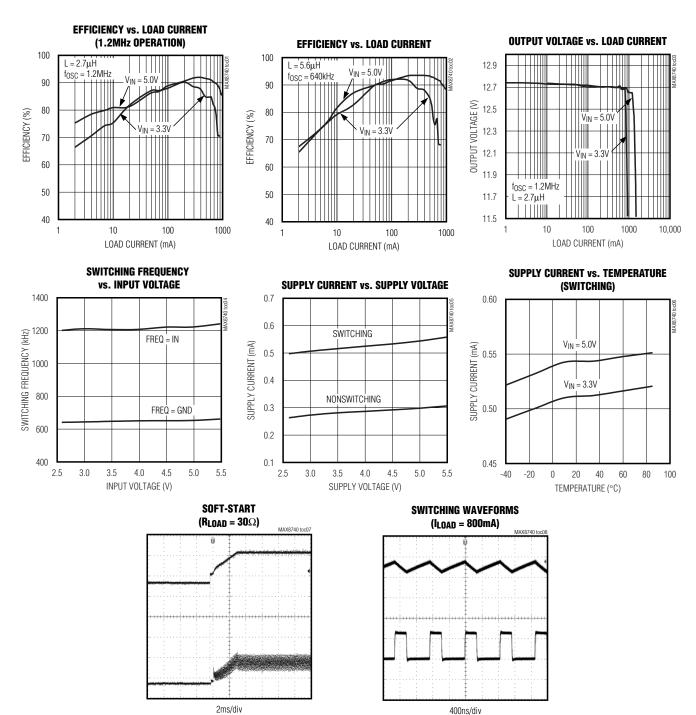

## **Typical Operating Characteristics**

(Circuit of Figure 1. V<sub>IN</sub> = 5V, V<sub>MAIN</sub> = 15V, T<sub>A</sub> = +25°C, unless otherwise noted.)

## Pin Description

| PIN  | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | COMP | Compensation Pin for Error Amplifier. Connect a series RC from COMP to ground. See the <i>Loop Compensation</i> section for component selection guidelines.                                                                                                                                                                                                                                                                                     |

| 2    | FB   | Feedback Pin. The FB regulation voltage is 1.24V nominal. Connect an external resistive voltage-divider between the step-up regulator's output (V <sub>OUT</sub> ) and GND, with the center tap connected to FB. Place the divider close to the IC and minimize the trace area to reduce noise coupling. Set V <sub>OUT</sub> according to the Output Voltage Selection section.                                                                |

| 3    | SHDN | Shutdown Control Input. Drive SHDN low to turn off the MAX8740.                                                                                                                                                                                                                                                                                                                                                                                 |

| 4, 5 | GND  | Ground. Connect pins 4 and 5 directly together.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6, 7 | LX   | Switch Pin. LX is the drain of the internal MOSFET. Connect the inductor/rectifier diode junction to LX and minimize the trace area for lower EMI. Connect pins 6 and 7 directly together.                                                                                                                                                                                                                                                      |

| 8    | IN   | Supply Pin. Bypass IN with a minimum 1µF ceramic capacitor directly to GND.                                                                                                                                                                                                                                                                                                                                                                     |

| 9    | FREQ | Frequency-Select Input. When FREQ is low, the oscillator frequency is set to 640kHz. When FREQ is high, the frequency is 1.2MHz. This input has a 5µA pulldown current.                                                                                                                                                                                                                                                                         |

| 10   | SS   | Soft-Start Control Pin. Connect a soft-start capacitor (CSS) to this pin. Leave open for no soft-start. The soft-start capacitor is charged with a constant current of $4.5\mu$ A. Full current limit is reached after $t = 2.5 \times 10^5$ CSS. The soft-start capacitor is discharged to ground when $\overline{SHDN}$ is low. When $\overline{SHDN}$ goes high, the soft-start capacitor is charged to 0.4V, after which soft-start begins. |

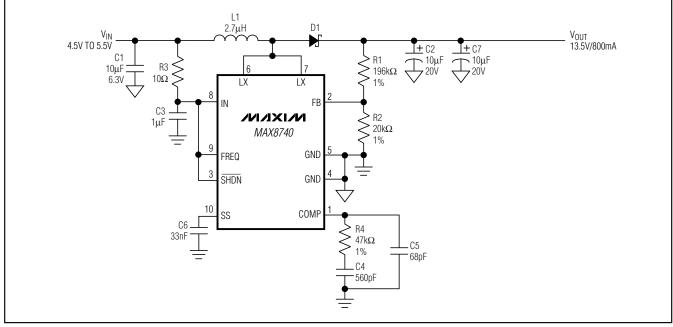

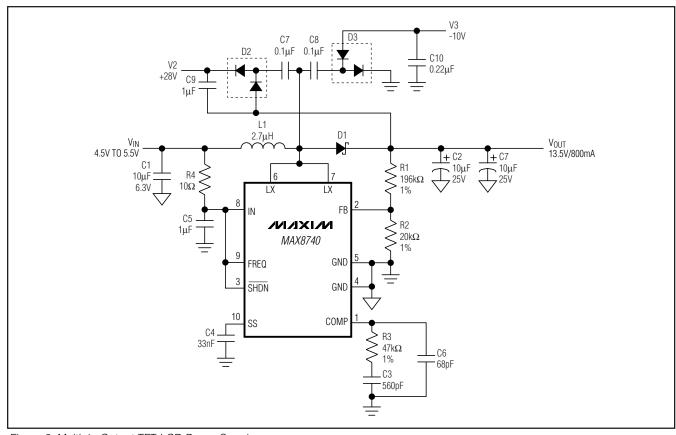

Figure 1. Typical Operating Circuit

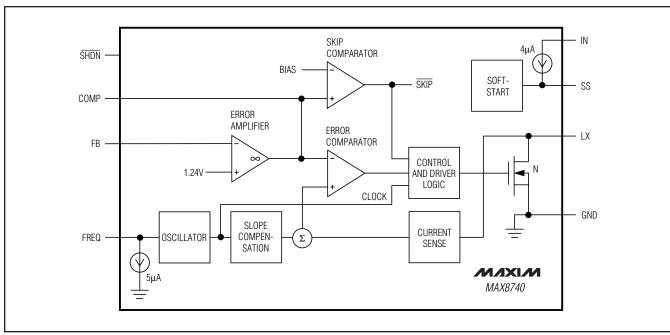

Figure 2. Functional Diagram

### Detailed Description

The MAX8740 is a highly efficient power supply that employs a current-mode, fixed-frequency, PWM architecture for fast transient response and low-noise operation. The device regulates the output voltage through a combination of an error amplifier, two comparators, and several signal generators (Figure 2). The error amplifier compares the signal at FB to 1.24V and varies the COMP output. The voltage at COMP determines the current trip point each time the internal MOSFET turns on. As the load changes, the error amplifier sources or sinks current to the COMP output to command the inductor peak current necessary to service the load. To maintain stability at high duty cycles, a slope-compensation signal is summed with the current-sense signal.

At light loads, this architecture allows the MAX8740 to "skip" cycles to prevent overcharging the output voltage.

In this region of operation, the inductor ramps up to a peak value of approximately 150mA, discharges to the output, and waits until another pulse is needed again.

### **Output Current Capability**

The output current capability of the MAX8740 is a function of current limit, input voltage, operating frequency, and inductor value. Because of the slope compensation used to stabilize the feedback loop, the inductor

current limit depends on the duty cycle. The current limit is determined by the following equation:

$$I_{LIM} = (1.26 - 0.35 \times D) \times I_{LIM} EC$$

where I<sub>LIM\_EC</sub> is the current limit specified at 71% duty cycle (see the *Electrical Characteristics* table) and D is the duty cycle.

The output current capability depends on the currentlimit value and is governed by the following equation:

$$I_{OUT(MAX)} \; = \left[I_{LIM} \; - \; \frac{0.5 \times \; D \, \times \; V_{IN}}{f_{OSC} \, \times \; L}\right] \times \; \frac{V_{IN}}{V_{OUT}} \, \times \; \eta$$

where  $I_{LIM}$  is the current limit calculated above,  $\eta$  is the regulator efficiency (85% nominal), and D is the duty cycle. The duty cycle when operating at the current limit is:

$$D = \frac{V_{OUT} - V_{IN} + V_{DIODE}}{V_{OUT} - I_{LIM} \times R_{ON} + V_{DIODE}}$$

where  $V_{DIODE}$  is the rectifier diode forward voltage and  $R_{ON}$  is the on-resistance of the internal MOSFET.

#### Soft-Start

The MAX8740 can be programmed for soft-start upon power-up with an external capacitor. When the shutdown pin is taken high, the soft-start capacitor (CSS) is immediately charged to 0.4V. Then the capacitor is charged at a constant current of 4.5µA (typ). During this time, the SS voltage directly controls the peak inductor current, allowing 0A at  $V_{SS} = 0.4V$  to the full current limit at  $V_{SS} = 1.5V$ . The maximum load current is available after the soft-start is completed. When the  $\overline{SHDN}$  pin is taken low, the soft-start capacitor is discharged to ground.

### Frequency Selection

The MAX8740's frequency can be user selected to operate at either 640kHz or 1.2MHz. Connect FREQ to GND for 640kHz operation. For a 1.2MHz switching frequency, connect FREQ to IN. This allows the use of small, minimum-height external components while maintaining low output noise. FREQ has an internal pulldown, allowing the user the option of leaving FREQ unconnected for 640kHz operation.

**Table 1. Component List**

| DESIGNATION | DESCRIPTION                                                                                               |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| C1          | 10μF ±10%, 6.3V X5R ceramic capacitor (0805)<br>Murata GRM21BR60J106K<br>Taiyo Yuden JMK212BJ106KD        |  |  |  |  |

| C2, C7      | 10μF ±20%, 25V X5R ceramic capacitors<br>(1210)<br>TDK C3225X5R1E106M,<br>Taiyo Yuden TMK325BJ106MM       |  |  |  |  |

| D1          | 3A, 40V Schottky diode (SM8)<br>Central Semiconductor CMSH3-40M                                           |  |  |  |  |

| L1          | 3.3µH ±30%, 4.0A power inductor<br>Sumida CDRH8D28-3R3, 3.3µH<br>(alternate : Sumida CDRH103R-3R3, 3.3µH) |  |  |  |  |

#### Shutdown

The MAX8740 shuts down to reduce the supply current to 0.1µA when SHDN is low. In this mode, the internal reference, error amplifier, comparators, and biasing circuitry turn off, and the n-channel MOSFET is turned off. The step-up regulator's output is connected to IN by the external inductor and rectifier diode.

### **Applications Information**

Step-up regulators using the MAX8740 can be designed by performing simple calculations for a first iteration. All designs should be prototyped and tested prior to production. Table 1 provides a list of power components for the typical applications circuit. Table 2 lists component suppliers.

External-component-value choice is primarily dictated by the output voltage and the maximum load current, as well as maximum and minimum input voltages. Begin by selecting an inductor value. Once L is known, choose the diode and capacitors.

#### **Inductor Selection**

The minimum inductance value, peak current rating, and series resistance are factors to consider when selecting the inductor. These factors influence the converter's efficiency, maximum output load capability, transient-response time, and output voltage ripple. Physical size and cost are also important factors to be considered.

The maximum output current, input voltage, output voltage, and switching frequency determine the inductor value. Very high inductance values minimize the current ripple and therefore reduce the peak current, which decreases core losses in the inductor and I<sup>2</sup>R losses in the entire power path. However, large inductor values also require more energy storage and more turns of wire, which increase physical size and can increase I<sup>2</sup>R losses in the inductor. Low inductance values decrease the physical size but increase the current ripple and peak current. Finding the best inductor involves choosing the best compromise between circuit efficiency, inductor size, and cost.

**Table 2. Component Suppliers**

| SUPPLIER    | PHONE        | FAX          | WEBSITE               |

|-------------|--------------|--------------|-----------------------|

| Murata      | 770-436-1300 | 770-436-3030 | www.murata.com        |

| Sumida      | 847-545-6700 | 847-545-6720 | www.sumida.com        |

| Taiyo Yuden | 800-348-2496 | 847-925-0899 | www.t-yuden.com       |

| TDK         | 847-803-6100 | 847-390-4405 | www.component.tdk.com |

| Toshiba     | 949-455-2000 | 949-859-3963 | www.toshiba.com/taec  |

The equations used here include a constant LIR, which is the ratio of the inductor peak-to-peak ripple current to the average DC inductor current at the full load current. The best trade-off between inductor size and circuit efficiency for step-up regulators generally has an LIR between 0.3 and 0.5. However, depending on the AC characteristics of the inductor core material and the ratio of inductor resistance to other power path resistances, the best LIR can shift up or down. If the inductor resistance is relatively high, more ripple can be accepted to reduce the number of turns required and increase the wire diameter. If the inductor resistance is relatively low, increasing inductance to lower the peak current can decrease losses throughout the power path. If extremely thin high-resistance inductors are used, as is common for LCD panel applications, the best LIR can increase to between 0.5 and 1.0.

Once a physical inductor is chosen, higher and lower values of the inductor should be evaluated for efficiency improvements in typical operating regions.

Calculate the approximate inductor value using the typical input voltage ( $V_{IN}$ ), the maximum output current ( $I_{OUT(MAX)}$ ), the expected efficiency ( $\eta_{TYP}$ ) taken from an appropriate curve in the *Typical Operating Characteristics*, and an estimate of LIR based on the above discussion:

$$L = \left(\frac{V_{IN}}{V_{OUT}}\right)^2 \left(\frac{V_{OUT} - V_{IN}}{I_{OUT(MAX)} \times f_{OSC}}\right) \left(\frac{\eta_{TYP}}{LIR}\right)$$

Choose an available inductor value from an appropriate inductor family. Calculate the maximum DC input current at the minimum input voltage  $V_{IN(MIN)}$  using conservation of energy and the expected efficiency at that operating point ( $\eta_{MIN}$ ) taken from an appropriate curve in the *Typical Operating Characteristics*:

$$I_{IN(DC,\,MAX)} \ = \ \frac{I_{OUT(MAX)} \ \times \ V_{OUT}}{V_{IN(MIN)} \ \times \ \eta_{MIN}}$$

Calculate the ripple current at that operating point and the peak current required for the inductor:

$$I_{RIPPLE} = \frac{V_{IN(MIN)} \times (V_{OUT} - V_{IN(MIN)})}{L \times V_{OUT} \times f_{OSC}}$$

$$I_{PEAK} = I_{IN(DC, MAX)} + \frac{I_{RIPPLE}}{2}$$

The inductor's saturation current rating and the MAX8740's LX current limit ( $I_{LIM}$ ) should exceed IPEAK, and the inductor's DC current rating should exceed IIN(DC,MAX). For good efficiency, choose an inductor with less than  $0.1\Omega$  series resistance.

Considering the typical operating circuit, the maximum load current (IOUT(MAX)) is 900mA with a 13.5V output and a 5V typical input voltage. Choosing an LIR of 0.35 and estimating efficiency of 85% at this operating point:

$$L = \left(\frac{5V}{13.5V}\right)^{2} \left(\frac{13.5V - 5V}{0.9A \times 1.2MHz}\right) \left(\frac{0.85}{0.35}\right) \approx 2.7 \mu H$$

Using the circuit's minimum input voltage (4.5V) and estimating efficiency of 85% at that operating point:

$$I_{IN(DC, MAX)} = \frac{0.9A \times 3.5V}{4.5V \times 0.85} \approx 3.2A$$

The ripple current and the peak current are:

$$I_{RIPPLE} = \frac{4.5V \times (12.5V - 4.5V)}{2.7\mu H \times 13.5V \times 1.2MHz} \approx 0.93A$$

$$I_{PEAK} = 3.2A + \frac{0.93A}{2} \approx 3.7A$$

### **Output Capacitor Selection**

The total output voltage ripple has two components: the capacitive ripple caused by the charging and discharging of the output capacitance, and the ohmic ripple due to the capacitor's equivalent series resistance (ESR):

$$V_{RIPPLE} = V_{RIPPLE(C)} + V_{RIPPLE(ESR)}$$

$$V_{RIPPLE(C)} \approx \frac{I_{OUT}}{C_{OUT}} \left( \frac{V_{OUT} - V_{IN}}{V_{OUT} f_{OSC}} \right)$$

, and

$$V_{RIPPLE(ESR)} \approx I_{PEAK} R_{ESR(COUT)}$$

where IPEAK is the peak inductor current (see the *Inductor Selection* section). For ceramic capacitors, the output voltage ripple is typically dominated by VRIPPLE(C). The voltage rating and temperature characteristics of the output capacitor must also be considered.

#### Input Capacitor Selection

The input capacitor ( $C_{IN}$ ) reduces the current peaks drawn from the input supply and reduces noise injection into the IC. A 10µF ceramic capacitor is used in the typical operating circuit (Figure 1) because of the high source impedance seen in typical lab setups. Actual applications usually have much lower source impedance since the step-up regulator often runs directly from the output of another regulated supply. Typically,  $C_{IN}$  can be reduced below the values used in the typical operating circuit. Ensure a low noise supply at IN by using adequate  $C_{IN}$ . Alternatively, greater voltage variation can be tolerated on  $C_{IN}$  if IN is decoupled from  $C_{IN}$  using an RC lowpass filter (see R3 and C3 in Figure 1).

#### Rectifier Diode Selection

The MAX8740's high switching frequency demands a high-speed rectifier. Schottky diodes are recommended for most applications because of their fast recovery time and low forward voltage. The diode should be rated to handle the output voltage and the peak switch current. Make sure that the diode's peak current rating is at least IPEAK calculated in the *Inductor Selection* section and that its breakdown voltage exceeds the output voltage.

### **Output Voltage Selection**

The MAX8740 operates with an adjustable output from V<sub>IN</sub> to 28V. Connect a resistive voltage-divider from the output (V<sub>OUT</sub>) to GND with the center tap connected to FB (see Figure 1). Select R2 in the  $10k\Omega$  to  $50k\Omega$  range. Calculate R1 with the following equation:

$$R1 = R2 \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

where V<sub>FB</sub>, the step-up regulator's feedback set point, is 1.28V (typ). Place R1 and R2 close to the IC.

#### **Loop Compensation**

The voltage feedback loop needs proper compensation to prevent excessive output ripple and poor efficiency caused by instability. This is done by connecting a resistor (R<sub>COMP</sub>) and capacitor (C<sub>COMP</sub>) in series from COMP to GND, and another capacitor (C<sub>COMP2</sub>) from COMP to GND. R<sub>COMP</sub> is chosen to set the high-frequency integrator gain for fast transient response, while C<sub>COMP</sub> is chosen to set the integrator zero to maintain loop stability. The second capacitor, C<sub>COMP2</sub>, is cho-

sen to cancel the zero introduced by output-capacitance ESR. For optimal performance, choose the components using the following equations:

$$R_{COMP} \approx \frac{315 \times V_{IN} \times V_{OUT} \times C_{OUT}}{L \times I_{OUT(MAX)}}$$

$$C_{COMP} \approx \frac{V_{OUT} \times C_{OUT}}{10 \times I_{OUT(MAX)} \times R_{COMP}}$$

$$C_{COMP2} \approx \frac{0.0036 \times R_{ESR} \times L \times I_{OUT(MAX)}}{V_{IN} \times V_{OUT}}$$

For the ceramic output capacitor, where ESR is small, CCOMP2 is optional. The best gauge of correct loop compensation is by inspecting the transient response of the MAX8740. Adjust RCOMP and CCOMP as necessary to obtain optimal transient performance.

### **Soft-Start Capacitor**

The soft-start capacitor should be large enough that it does not reach final value before the output has reached regulation. Calculate Css to be:

$$C_{SS} > 21 \times 10^{-6} \times C_{OUT} \times \left( \frac{V_{OUT}^2 - V_{IN} \times V_{OUT}}{V_{IN} \times I_{INRUSH} - I_{OUT} \times V_{OUT}} \right)$$

where C<sub>OUT</sub> is the total output capacitance including any bypass capacitor on the output bus, V<sub>OUT</sub> is the maximum output voltage, I<sub>INRUSH</sub> is the peak inrush current allowed, I<sub>OUT</sub> is the maximum output current during power-up, and V<sub>IN</sub> is the minimum input voltage.

The load must wait for the soft-start cycle to finish before drawing a significant amount of load current. The duration after which the load can begin to draw maximum load current is:

$$t_{MAX} = 6.77 \times 10^5 \times C_{SS}$$

Figure 3. Multiple-Output TFT-LCD Power Supply

#### **Multiple-Output Power Supply for TFT LCD**

Figure 3 shows a power supply for active-matrix TFT-LCD flat-panel displays. Output-voltage transient performance is a function of the load characteristic. Add or remove output capacitance (and recalculate compensation-network component values) as necessary to meet the required transient performance. Regulation performance for secondary outputs (V2 and V3) depends on the load characteristics of all three outputs.

#### PC Board Layout and Grounding

Careful PC board layout is important for proper operation. Use the following guidelines for good PC board layout:

1) Minimize the area of high-current loops by placing the inductor, rectifier diode, and output capacitors near the input capacitors and near the LX and GND pins. The high-current input loop goes from the positive terminal of the input capacitor to the inductor, to the IC's LX pin, out of GND, and to the input capacitor's negative terminal. The high-current output loop is from the positive terminal of the input capacitor to the inductor, to the rectifier diode (D1),

- and to the positive terminal of the output capacitors, reconnecting between the output capacitor and input capacitor ground terminals. Connect these loop components with short, wide connections. Avoid using vias in the high-current paths. If vias are unavoidable, use many vias in parallel to reduce resistance and inductance.

- 2) Create a power ground island (PGND) consisting of the input and output capacitor grounds and GND pins. Connect all of these together with short, wide traces or a small ground plane. Maximizing the width of the power ground traces improves efficiency and reduces output voltage ripple and noise spikes. Create an analog ground plane (AGND) consisting of the feedback-divider ground connection, the COMP and SS capacitor ground connections, and the device's exposed backside pad. Connect the AGND and PGND islands by connecting the GND pins directly to the exposed backside pad. Make no other connections between these separate ground planes.

- 3) Place the feedback voltage-divider-resistors as close to the FB pin as possible. The divider's center trace should be kept short. Placing the resistors far away causes the FB trace to become an antenna that can pick up switching noise. Avoid running the feedback trace near LX.

- 4) Place the IN pin bypass capacitor as close to the device as possible. The ground connection of the IN bypass capacitor should be connected directly to GND pins with a wide trace.

- 5) Minimize the length and maximize the width of the traces between the output capacitors and the load for best transient responses.

- 6) Minimize the size of the LX node while keeping it wide and short. Keep the LX node away from the feedback node and analog ground. Use DC traces as a shield if necessary.

Refer to the MAX8740 evaluation kit for an example of proper board layout.

\_Chip Information

TRANSISTOR COUNT: 2746

PROCESS: BiCMOS

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

| COMM                                                    | ON DIME                       | NSIONS             | 1         |          |                |           |               |                      |   |  |

|---------------------------------------------------------|-------------------------------|--------------------|-----------|----------|----------------|-----------|---------------|----------------------|---|--|

| SYMBOL                                                  | MIN.                          | MAX.               | 1         |          |                |           |               |                      |   |  |

| A                                                       | 0.70                          | 0.80               | 1         |          |                |           |               |                      |   |  |

| D                                                       | 2.90                          | 3.10               | ]         |          |                |           |               |                      |   |  |

| E                                                       | 2.90                          |                    | 1         |          |                |           |               |                      |   |  |

| A1                                                      | 0.00                          |                    | ļ         |          |                |           |               |                      |   |  |

| L                                                       | 0.20                          |                    | ļ         |          |                |           |               |                      |   |  |

| k<br>A2                                                 | _                             | 25 MIN.<br>20 REF. | 1         |          |                |           |               |                      |   |  |

| L AZ                                                    | 1 0                           | ZU NLF.            | J         |          |                |           |               |                      |   |  |

|                                                         |                               |                    |           |          |                |           |               |                      | _ |  |

| PACKAGE VAR                                             | RIATIONS                      | 3                  |           |          |                |           |               |                      | 1 |  |

| PKG. CODE                                               | N                             | D2                 | E2        | е        | JEDEC SPEC     | b         | [(N/2)-1] x e | DOWNBONDS<br>ALLOWED | 1 |  |

| T633-1                                                  | 6                             | 1.50±0.10          | 2.30±0.10 | 0.95 BSC | MO229 / WEEA   | 0.40±0.05 | 1.90 REF      | NO                   | 1 |  |

| T633-2                                                  | 6                             | 1.50±0.10          | 2.30±0.10 | 0.95 BSC | MO229 / WEEA   | 0.40±0.05 | 1.90 REF      | NO                   | 1 |  |

| T833-1                                                  | 8                             | 1.50±0.10          | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      | NO                   | 1 |  |

| T833-2                                                  | 8                             | 1.50±0.10          | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      | NO                   | 1 |  |

| T833-3                                                  | 8                             | 1.50±0.10          | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      | YES                  | 1 |  |

| T1033-1                                                 | 10                            | 1.50±0.10          | 2.30±0.10 | 0.50 BSC | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      | NO                   | 1 |  |

| T1433-1                                                 | 14                            | 1.70±0.10          | 2.30±0.10 | 0.40 BSC |                | 0.20±0.05 | 2.40 REF      | YES                  | 1 |  |

| T1433-2                                                 | 14                            | 1.70±0.10          | 2.30±0.10 | 0.40 BSC |                | 0.20±0.05 | 2.40 REF      | NO                   | ] |  |

| NOTES:<br>. ALL DIMENS<br>2. COPLANARIT<br>3. WARPAGE S | Y SHALL<br>HALL NO<br>ENGTH/F | NOT EXCEED         | ED 0.08 n | nm.      | AS             | ) "E2".   |               |                      |   |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.