捷多邦,专业PCB打样工厂,24小时加急出货

SONY

**CXA1782CQ/CR**

# **RF Signal Processing Servo Amplifier for CD players**

#### Description

The CXA1782CQ/CR is a bipolar IC with built-in RF signal processing and various servo ICs. A CD player servo can be configured by using this IC, DSP and driver.

#### **Features**

- Low operating voltage (Vcc VEE = 3.0 to 11.0V)

- Low power consumption (39mW, Vcc = 3.0V)

- Supports pickup of either current output, voltage output

- Automatic adjustment comparator for tracking balance gain

- Single power supply and positive/negative dual power supplies

#### **Applications**

- RF I-V amplifier, RF amplifier

- Focus and tracking error amplifier

- APC circuit

- Mirror detection circuit

- Defect detection and prevention circuits

- · Focus servo control

- Tracking servo control

- Sled servo control

- · Comparators of tracking adjustment for balance WWW.DZSC.COM and gain

## Structure

Bipolar silicon monolithic IC

#### Absolute Maximum Ratings (Ta = 25°C)

- Supply voltage Vcc 12 V

- Operating temperature Topr -20 to +75 °C

- Storage temperature °C Tstg -65 to +150

- Allowable power dissipation

- PD 833 (CXA1782CQ) mW 457 (CXA1782CR) mW

V

#### **Recommended Operating Condition**

Operating supply voltage

Vcc - VEE 3.0 to 11.0

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by my implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the peration of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits. .dzsc.com

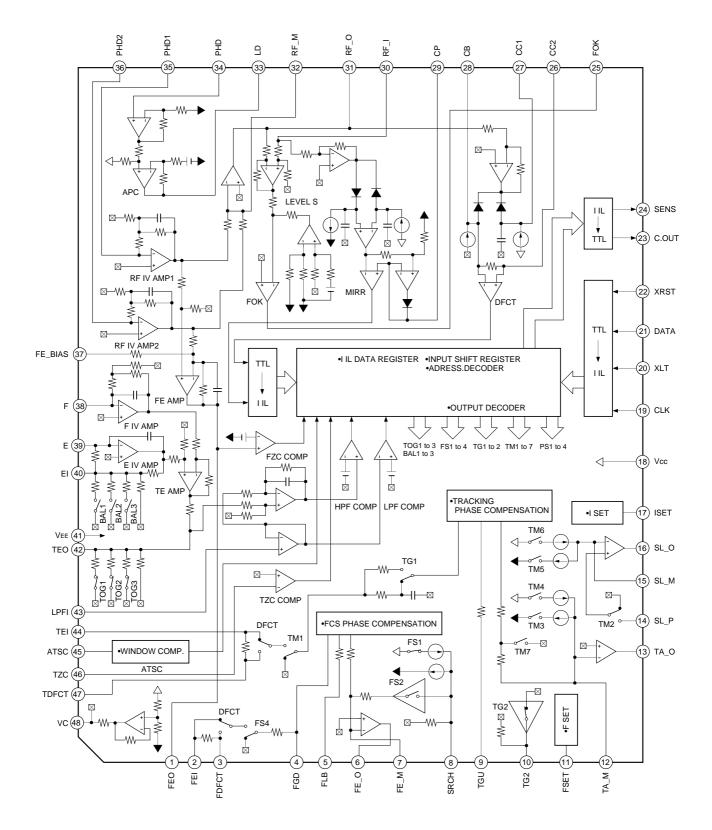

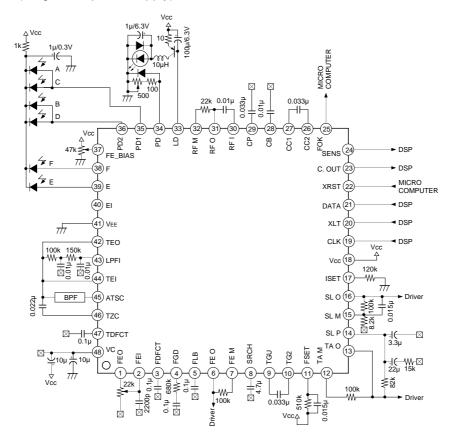

#### **Block Diagram**

- The switch state in Block Diagram is for initial resetting.

- Switch turns to  $\circ$  side for 1 and to  $\bullet$  side for 0 in Serial Data Truth Table.

- DFCT switch turns to side when defect signal generates for DEFECT = E in Serial Data Truth Table.

- TG1 switch turns to o side and TG2 switch is left open when TG1 and TG2 (address 1 : D3) is 1.

# **Pin Description**

| Pin<br>No. | Symbol | I/O | Equivalent circuit                                                            | Description                                                                                    |

|------------|--------|-----|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 1          | FEO    | 0   | 147<br>147<br>147<br>174k<br>↓ 300µ<br>↓ 10k<br>↓ \$51k<br>↓ \$9k             | Focus error amplifier output.<br>Connected internally to the FZC<br>comparator input.          |

| 2          | FEI    | I   |                                                                               | Focus error input.                                                                             |

| 3          | FDFCT  | I   |                                                                               | Capacitor connection pin for defect time constant.                                             |

| 4          | FGD    | I   | (4)<br>↓ 147<br>↓ 68k<br>↓ 147<br>↓ 147<br>↓ 130k<br>↓ 20µ                    | Ground this pin through a capacitor<br>when decreasing the focus servo<br>high-frequency gain. |

| 5          | FLB    | I   |                                                                               | External time constant setting pin for increasing the focus servo low-frequency.               |

| 6          | FE_O   | 0   |                                                                               | Focus drive output.                                                                            |

| 13         | TA_O   | 0   |                                                                               | Tracking drive output.                                                                         |

| 16         | SL_O   | 0   | 250μ                                                                          | Sled drive output.                                                                             |

| 7          | FE_M   | I   | 7         147         90k           147         ≶ 90k           50k         ↓ | Focus amplifier inverted input.                                                                |

| Pin<br>No. | Symbol | I/O | Equivalent circuit                                                                                                                       | Description                                                                             |

|------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 8          | SRCH   | I   | 8<br>147<br>₩<br>50k<br>50k<br>11μ                                                                                                       | External time constant setting pin for generating focus servo waveform.                 |

| 9          | TGU    | I   | $9 \qquad \qquad$ | External time constant setting pin for switching tracking high-frequency gain.          |

| 10         | TG2    | I   | $10 \qquad 470 k \leq 1 \qquad 2 \mu$                                                                                                    | External time constant setting pin for switching tracking high-frequency gain.          |

| 11         | FSET   | I   | 147k<br>147k<br>147k<br>147k<br>15k<br>15k                                                                                               | High cut-off frequency setting pin for focus and tracking phase compensation amplifier. |

| 12         | TA_M   | I   | 147<br>12<br>↓ 147<br>↓ 100k<br>↓ ↓ 11µ                                                                                                  | Tracking amplifier inverted input.                                                      |

| 14         | SL_P   | I   |                                                                                                                                          | Sled amplifier non-inverted input.                                                      |

| 15         | SL_M   | I   | 147<br>15<br>↓ 147<br>↓ ↓ ↓ 22µ                                                                                                          | Sled amplifier inverted input.                                                          |

| Pin<br>No. | Symbol | I/O | Equivalent circuit                                                                          | Description                                                                          |

|------------|--------|-----|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 17         | ISET   | I   |                                                                                             | Setting pin for Focus search, Track<br>jump, and Sled kick current.                  |

| 19         | CLK    | I   | Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ<br>Δ | Serial data transfer clock input from CPU. (no pull-up resistance)                   |

| 20         | XLT    | I   |                                                                                             | Latch input from CPU.<br>(no pull-up resistance)                                     |

| 21         | DATA   | I   | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                       | Serial data input from CPU.<br>(no pull-up resistance)                               |

| 22         | XRST   | I   |                                                                                             | Reset input; resets at Low.<br>(no pull-up resistance)                               |

| 23         | C. OUT | 0   | 23) ↓ 147<br>(23) ↓ 147                                                                     | Track number count signal output.                                                    |

| 24         | SENS   | 0   | 23<br>24<br>24<br>5 100k                                                                    | Outputs FZC, DFCT, TZC, gain, balance, and others according to the command from CPU. |

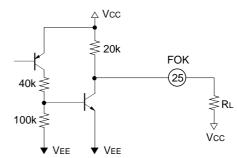

| 25         | FOK    | 0   | 25<br>147<br>25<br>147<br>25<br>147<br>20k<br>40k<br>100k                                   | Focus OK comparator output.                                                          |

| 26         | CC2    | I   |                                                                                             | Input for the DEFECT bottom hold output with capacitance coupled.                    |

| 27         | CC1    | 0   |                                                                                             | DEFECT bottom hold output.                                                           |

| 28         | СВ     | I   |                                                                                             | Connection pin for DEFECT bottom hold capacitor.                                     |

| Pin<br>No. | Symbol       | I/O | Equivalent circuit                                                                          | Description                                                                                                                                    |

|------------|--------------|-----|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 29         | СР           | I   |                                                                                             | Connection pin for MIRR hold<br>capacitor.<br>MIRR comparator non-inverted<br>input.                                                           |

| 30         | RF_I         | I   |                                                                                             | Input for the RF summing amplifier output with capacitance coupled.                                                                            |

| 31         | RF_O         | О   |                                                                                             | RF sunning amplifier output.<br>Eye-pattern check point.                                                                                       |

| 32         | RF_M         | I   |                                                                                             | RF summing amplifier inverted<br>input.<br>The RF amplifier gain is determined<br>by the resistance connected<br>between this pin and RFO pin. |

| 33         | LD           | Ο   | 33                                                                                          | APC amplifier output.                                                                                                                          |

| 34         | PHD          | I   | 34                                                                                          | APC amplifier input.                                                                                                                           |

| 35<br>36   | PHD1<br>PHD2 | I   | $\begin{array}{c} 10k \\ 147 \\ 36 \\ 36 \\ 100\mu \\ 100\mu \\ 11.6k \\ 11.6k \end{array}$ | RF I-V amplifier inverted input.<br>Connect these pins to the photo<br>diode A + C and B + D pins.                                             |

| Pin<br>No. | Symbol  | I/O | Equivalent circuit                                                                                                  | Description                                                                                    |

|------------|---------|-----|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 37         | FE_BIAS | I   | $\begin{array}{c} 37 \\ \hline \\ $ | Bias adjustment of focus error amplifier.                                                      |

| 38<br>39   | F<br>E  | 1   | (38)                                                                                                                | F I-V and E I-V amplifier inverted<br>input.<br>Connect these pins to photo diodes<br>F and E. |

| 40         | EI      |     | 40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40                                                            | I-V amplifier E gain adjustment.<br>(When not using automatic balance<br>adjustment)           |

| 42         | TEO     | 0   | $\begin{array}{c} 42 \\ \hline \\ 42 \\ \hline \\ \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $             | Tracking error amplifier output.<br>E-F signal is output.                                      |

| 43         | LPFI    | I   |                                                                                                                     | Comparator input for balance<br>adjustment.<br>(Input from TEO through LPF)                    |

| Pin<br>No. | Symbol | I/O | Equivalent circuit                                       | Description                                        |

|------------|--------|-----|----------------------------------------------------------|----------------------------------------------------|

| 44         | TEI    | I   |                                                          | Tracking error input.                              |

| 47         | TDFCT  | I   |                                                          | Capacitor connection pin for defect time constant. |

| 45         | ATSC   | I   | (45)                                                     | Window comparator input for ATSC detection.        |

| 46         | TZC    | I   | 46<br>↓ 10k<br>↓ 75k<br>↓ 10k<br>↓ 10k<br>↓ 10k<br>↓ 10k | Tracking zero-cross comparator input.              |

| 48         | VC     | ο   | 48 $120$ $48$ $VC$ $VC$                                  | (Vcc + VEE)/2 DC voltage output.                   |

(Vcc = 1.5V, VEE = -1.5V, Ta = 25°C)

| S          |

|------------|

| Ü          |

| ÷.         |

| 5          |

|            |

| <u> </u>   |

| Ð          |

| Ť          |

| ğ          |

|            |

| a          |

| 2          |

| <u>+</u>   |

| 0          |

| —          |

| g          |

| ö          |

| . <u> </u> |

| 5          |

| 5          |

| ð          |

| <u> </u>   |

| ш          |

|            |

| tic<br>T               |          | ШA                    | ШA                    | ><br>u | дB               | >                        | >                       | ><br>u< | dВ                  | дB                  | дB                      | >                        | >                       | ><br>E | Вb                        | dВ                                    | dВ                                    | dB                                    | В                         | dB                                    | В                                     |

|------------------------|----------|-----------------------|-----------------------|--------|------------------|--------------------------|-------------------------|---------|---------------------|---------------------|-------------------------|--------------------------|-------------------------|--------|---------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------|---------------------------------------|---------------------------------------|

|                        | Max.     | 20                    | -10                   | 50     | 31.1             |                          | -0.3                    | 120     | 33.0                | 33.0                | 3.0                     |                          | -1.0                    | 25 1   | 6.5                       | -1.33                                 | -2.93                                 | -5.69                                 | 5.4                       | 0.7                                   | 1.0                                   |

| Ratings                |          |                       |                       |        |                  |                          |                         |         |                     |                     |                         | ო                        |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

| Rati                   | Typ.     | 14                    | -14                   | 0      | 28.1             | 1.3                      | 6.0                     | 0       | 30.0                | 30.0                | 0                       | 1.3                      | -1.3                    | 0      | 3.5                       | 3 -1.83                               | 3 -3.43                               | 6.19                                  | 2.4                       | 0.4                                   | 0.7                                   |

|                        | Min.     | 10                    | -20                   | -50    | 25.1             | 1.2                      | Ι                       | -120    | 27.0                | 27.0                | -3.0                    | 1.0                      | Ι                       | -25    | 0.5                       | -2.33                                 | -3.93                                 | -6.69                                 | -0.6                      | 0.1                                   | 0.4                                   |

| Measurament conditions |          |                       |                       |        | 1kHz input ratio | V1 = 100mVDC             | V1 = -100mVDC           |         | V1 = 1kHz I/O ratio | V1 = 1kHz I/O ratio |                         | V1 = 100mVDC             | V1 = 100mVDC            |        | V1 = 1kHz TOG1, 2, 3: OFF | V1 = 1kHz TOG1: ON<br>Reference to F0 | V1 = 1kHz TOG2: ON<br>Reference to F0 | V1 = 1kHz TOG3: ON<br>Reference to F0 | V1 = 1kHz TOG1, 2, 3: OFF | V1 = 1kHz BAL1: ON<br>Reference to Eo | V1 = 1kHz BAL2: ON<br>Reference to Eo |

|                        | ment pin | T 18                  | 41                    | 31     |                  |                          |                         | -       |                     |                     |                         |                          |                         | 42     |                           |                                       |                                       |                                       |                           |                                       |                                       |

| 5                      |          | RST                   |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        | ЗF                        | 3E                                    | 3D                                    | 3B                                    | 37                        | 36                                    | 35                                    |

|                        | 17 18    |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | 16 1     |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | 15       |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | 14       |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | 13       |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | 12       |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

| suo                    | 1        |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

| SW conditions          | 10       |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

| W co                   | ര        |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

| S                      | ø        |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | ~        |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | 5 6      |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | 4 5      |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        |                           |                                       |                                       |                                       | 0                         | 0                                     | 0                                     |

|                        | ۲<br>۳   |                       |                       |        |                  |                          |                         |         |                     |                     |                         |                          |                         |        | 0                         | 0                                     | 0                                     | 0                                     |                           |                                       |                                       |

|                        | N        |                       |                       |        | 0                |                          | 0                       |         |                     | 0                   |                         | 0                        |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | -        |                       |                       |        | 0                | 0                        |                         |         | 0                   |                     |                         |                          | 0                       |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | I        | n 1                   | n 2                   |        |                  | age-High                 | age-Low                 |         |                     |                     | erence                  | age-High                 |                         |        |                           |                                       |                                       |                                       |                           |                                       |                                       |

|                        | lieli    | Current consumption 1 | Current consumption 2 | Offset | Voltage gain     | Max. output voltage-High | Max. output voltage-Low | Offset  | Voltage gain 1      | Voltage gain 1      | Voltage gain difference | Max. output voltage-High | Max. output voltage-Low | Offset | Voltage gain Fo           | Voltage gain F1                       | Voltage gain F2                       | Voltage gain F3                       | Voltage gain Eo           | Voltage gain E1                       | Voltage gain E2                       |

|                        |          | U<br>U                |                       | r      |                  | L am                     |                         |         |                     |                     | E 9W                    |                          |                         |        |                           |                                       |                                       | TE amp                                |                           |                                       | _                                     |

|                        |          | 1                     | T2                    | Т3     | T4               | T5                       | Т6                      | 17      | Т8                  | Т9                  | T10                     | T11                      | T12                     | T13    | T14                       | T15                                   | T16                                   | T17                                   | T18                       | Т19                                   | T20                                   |

CXA1782CQ/CR

Unit > E <u>></u>ш کر ۲ У ш ž ž 2 M ž В dВ В В В dВ В > > > > > -0.5 -480 1120 -1.0 -360 17.6 1.68 20.1 Max. 380 500 00 -35 640 265 -39 24 53 Ratings 21.0 9.0 | -1 .0 -500 14.6 18.1 Typ. 1.38 1.3 500 225 1.3 0.6 5 12.25 -180 006-006--200 -100 -640 1.08 16.1 1.0 Min. 0.5 1.0 360 185 38 49 Ι Output gain difference between SD = 20 and SD = 25. Output gain difference between SD = 00 and SD = 08. Pin 1 threshold (preliminary) Measurement conditions V1 = 1kHz BAL3: ON V1 = 1Vbc BAL2: ON V1 = 1Vbc BAL2: ON Reference to E0 T29 + T8 (or T9) V1 = -200 mVbcV1 = 200 mVbcV1 = -0.5 VDCV2 = 120mVV2 = 145mV V2 = 170mV 0.8mA sink T37 + T14 Measure-ment pin 42 33 48 24 13 ဖ ► SD 33 ЗF 3F 80 8 80 80 8 8 8 25 -> 18 17 0 0 0 0 16 0 15 4 13 0 12 ;-0 0 SW conditions 10 0 0 0 0 ი 0 ω  $\sim$ ശ 0 0 0 ഹ 0 0 4 0 ო 2 ~ 0 Max. output voltage-High Max. output voltage-High Max. output voltage-High Max. output voltage-Low Max. output voltage-Low Center amplifier output Search voltage (-) Search voltage (+) Output voltage 2 Output voltage 3 Output voltage 4 Output voltage 1 DC voltage gain DC voltage gain Voltage gain E3 FZC threshold FCS total gain TRK total gain Feed through Feed through ltem offset TE amplifier FCS servo ∀ЬС TRK servo T25 T35 T40 T23 T32 T24 T26 T29 T33 Т34 T36 T22 T27 T28 T30 T37 T38 T39 T21 T31

CXA1782CQ/CR

#### Vp-p Vp-p Vp-p kНz kНz kНz Vp-p Unit 2 2 m 2 m 2 m 2 m کر ۳ 2 m 2 L ž 2 В Вb > > > -1.0 -330 -450 -360 -1.0 Max. 640 140 -34 750 0.3 0.5 22 $\sim$ 25 20 ~ Ratings -1.3 -500 -356 -1.3 -600 -15 Typ. 500 130 1.3 600 15 17 0 -640 -400 -750 -25 120 1.0 2.5 1.8 Min. 360 -20 450 1.8 5 50 30 $\sim$ Output gain difference between SD = 20 and SD = 25. Measurement conditions Measures at C. OUT pin. Measures at C. OUT pin. Measures at C. OUT pin Measures at SENS pin. Measures at SENS pin. Measures at SENS pin. Measures at SENS pin. V1 = +0.4 VDC= -0.4Vbc V1 = +0.5 VDC 5 Measure-ment pin 13 16 23 10 24 25 24 -> > > -> SD 25 2C 28 25 25 25 30 38 25 20 25 23 22 4 10 -> 18 0 17 16 15 0 0 0 0 4 0 0 0 0 13 0 7 5 SW conditions 10 ი ω 0 0 0 0 0 0 $\sim$ ശ 0 S 0 4 ო 0 0 0 0 2 0 0 0 0 <del>.</del> Min. input operating voltage Max. output voltage-High Min. input operating voltage Min. operating frequency Max. input operating voltage Max. output voltage-Low Max. output voltage-Low Max. input operating voltage Max. operating frequency Max. operating frequency Jump output voltage (–) Jump output voltage (+) GAIN COMP threshold **BAL COMP threshold** ATSC threshold (-) ATSC threshold (+) Kick voltage (-) Kick voltage (+) TZC threshold FOK threshold DC open gain Feed through ltem TRK Servo pəlS DEFECT ЯЯІМ T45 T46 T48 T49 T42 T43 Т44 T55 T56 T59 T60 T41 Т47 T50 T52 T53 T54 T57 T58 T62 T61 T51

#### CXA1782CQ/CR

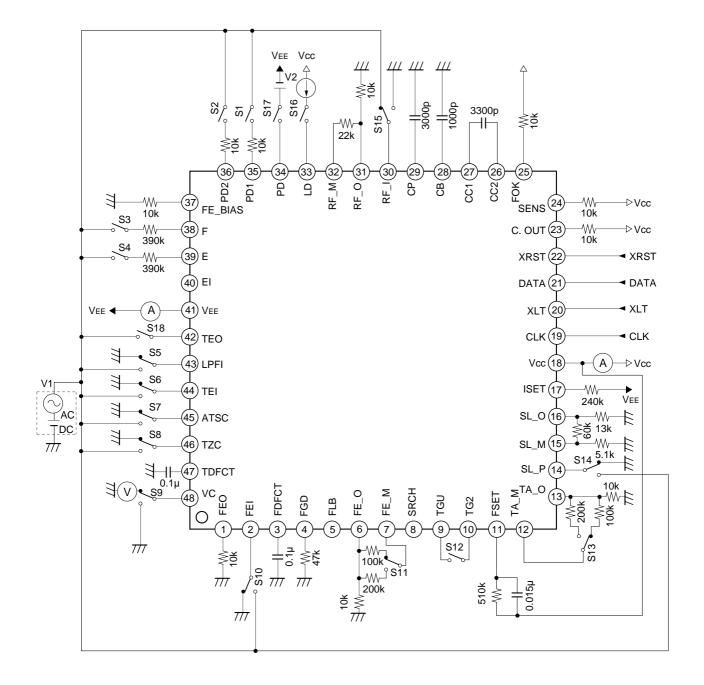

# **Electrical Characteristics Measurement Circuit**

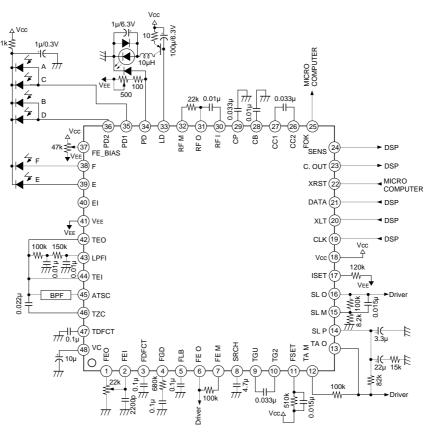

## Application Circuit (Dual ±5V power supplies)

Application Circuit (Single +3V power supply)

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### **Description of Functions**

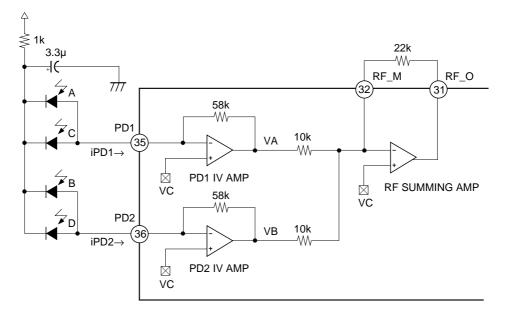

#### **RF Amplifier**

The photo diode currents input to the input pins (PD1 and PD2) are each I-V converted via a  $58k\Omega$  equivalent resistor by the PD I-V amplifiers. these signals are added by the RF summing amplifier, and the photo diode (A + B + C + D) current-voltage converted voltage is output to the RFO pin. An eye-pattern check can be performed at this pin.

The low frequency component of the RFO output voltage is  $V_{RFO} = 2.2 \times (V_A + V_B) = 127.6 k\Omega \times (iPD1 + iPD2)$ .

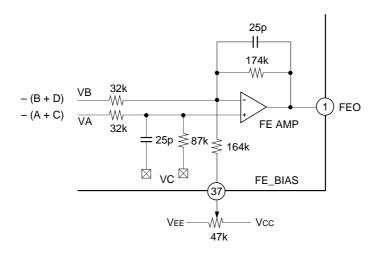

#### Focus Error Amplifier

The focus error amplifier calculates the difference between output VA and VB of the RF I-V amplifier, and output current-voltage converted voltage of the photo diode (A + C - B - D).

The FEO output voltage (low frequency) is  $V_{FEO} = 5.4 \times (V_A - V_B) = (iPD2 - iPD1) \times 315 k\Omega$ .

Be aware that the rotation of the focus bias volume has reversed for the usual CD RF IC.

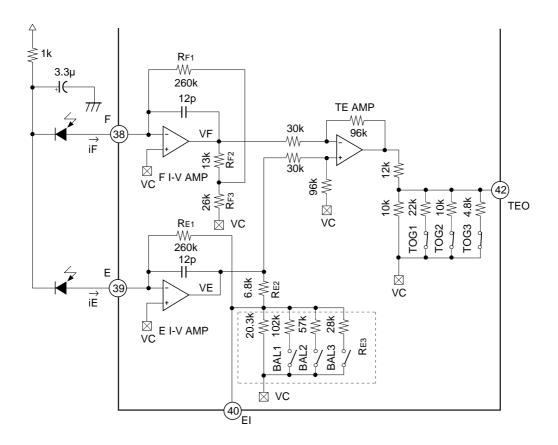

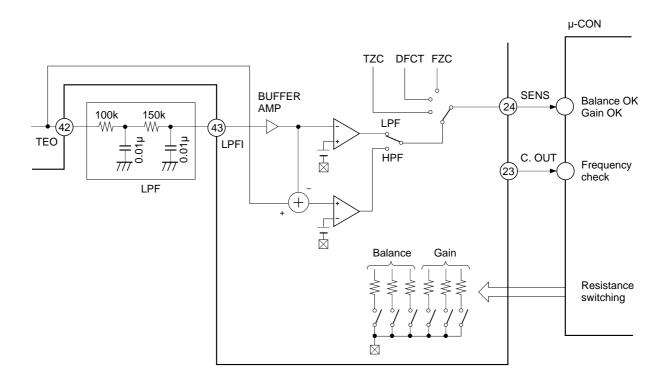

## **Tracking Error Amplifier**

The photo diode currents input to E and F pins are each current-voltage converted by the E I-V and F I-V amplifiers.

The CXA1782 tracking block has built-in circuits for balance and gain adjustments to enable software-based automatic adjustment.

The balance adjustment is performed by varying the combined resistance value of the T-configured feedback resistance at E I-V AMP.

F I-V AMP feedback resistance =  $R_{F1} + R_{F2} + \frac{R_{F1} \times R_{F2}}{R_{F3}} = 403k\Omega$ E I-V AMP feedback resistance =  $R_{E1} + R_{E2} + \frac{R_{E1} \times R_{E2}}{R_{E3}}$

Vary the value of RE3 in the formula above by using the balance adjustment switches (BAL1 to BAL3). For the gain adjustment, the TE AMP output is resistance-divided by the gain adjustment switches (TOG1 to TOG3), and it is output at Pin 42.

These balance and gain adjustment switches are controlled through software commands.

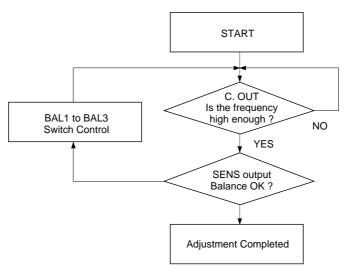

#### Tracking Automatic Adjustment for Gain/Balance

The CXA1782 has balance control, gain control, and comparator circuits required to perform tracking automatic adjustment. LPF is set externally at approximately 100Hz.

Balance adjustment

This adjustment is performed by routing the tracking error signal (TE signal) through the LPF, extracting the offset DC, and comparing it to the reference level.

However, the TE signal frequency distribution ranges form DC to 2kHz. Merely sending the signal through the LPF leaves lower frequency components, and the complete DC offset can not be extracted. To extract it, monitor the TE signal frequency at all times, and perform adjustment only when, a frequency that can lower a sufficient gain appears on the LPF. Use the C. OUT output to check this frequency.

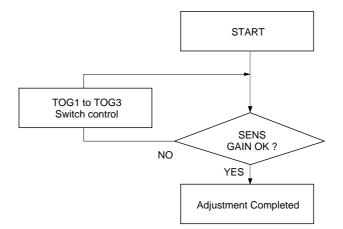

Gain adjustment

This adjustment is performed by passing the TE signal through the HPF and comparing the AC component to the reference level. The HPF signal is implemented by taking the difference between the TE signal and the LPF component input to Pin 43.

The comparison signal is output from Pin 24 (SENS). Address 3 selects the automatic adjustment comparator output, and HPF for data (D3) = 1 or LPF for data (D3) = 0 is selected.

• The anti-shock circuit always operates in the CXA1782 so that TG1 and TG2 (address 1 : D3) should be set to 1 for tracking adjustment to prevent this effect.

When the anti-shock function is not used, Pin 45 (ATSC) should be fixed to VC.

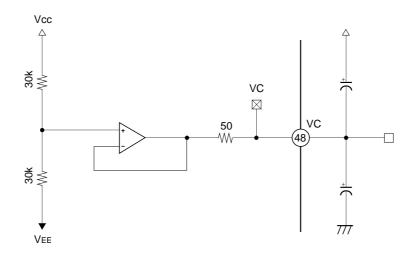

## **Center Voltage Generation Circuit**

(Single voltage application; Connect to GND when it's positive/negative dual power supplies.) Maximum current is approximately  $\pm 3$ mA. Output impedance is approximately  $50\Omega$ .

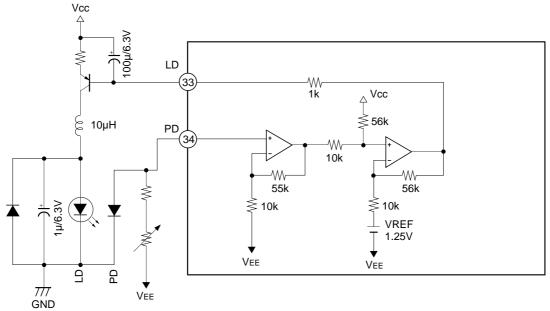

# **APC Circuit**

When the laser diode is driven with constant current, the optical output possesses large negative temperature characteristics. Therefore, the current must be controlled with the monitor photo diode to ensure the output remains constant.

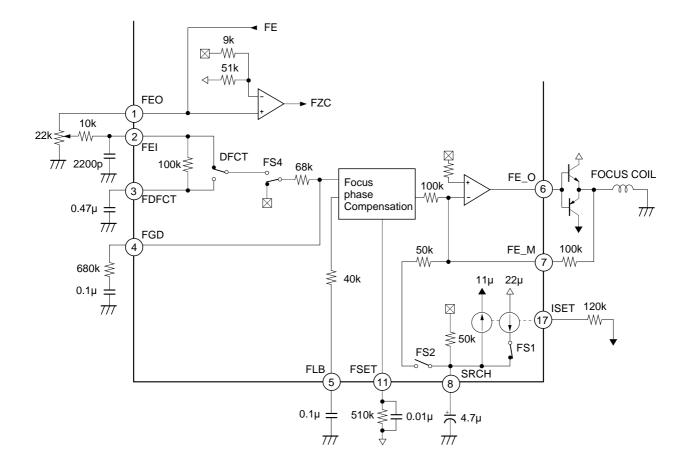

#### **Focus Servo**

The above figure shows a block diagram of the focus servo.

Ordinarily the FE signal is input to the focus phase compensation circuit through a  $68k\Omega$  resistance; however, when DFCT is detected, the FE signal is switched to pass through a low-pass filter formed by the internal  $100k\Omega$  resistance and the capacitance connected to Pin 3. When this DFCT prevention circuit is not used, leave Pin 3 open. The defect switch operation can be enabled and disabled with command.

The capacitor connected between Pin 5 and GND is a time constant to raise the low frequency in the normal playback state.

The peak frequency of the focus phase compensation is approximately 1.2kHz when a resistance of  $510\Omega$  is connected to Pin 11.

The focus search height is approximately  $\pm 1.1$ Vp-p when using the constants indicated in the above figure. This height is inversely proportional to the resistance connected between Pin 17 and VEE. However, changing this resistance also changes the height of the track jump and sled kick as well.

The FZC comparator inverted input is set to 15% of Vcc and VC (Pin 48); (Vcc - VC)  $\times$  15%.

\* 510k $\Omega$  resistance is recommended for Pin 11.

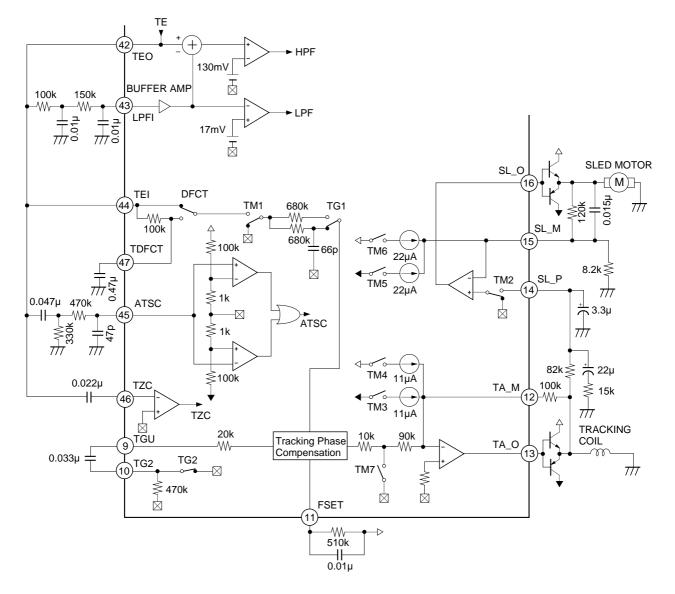

#### **Tracking Sled Servo**

The above figure shows a block diagram of the tracking and sled servo.

The capacitor connected between Pins 9 and 10 is a time constant to decrease the high-frequency gain when TG2 is OFF. The peak frequency of the tracking phase compensation is approximately 1.2kHz when a 510k $\Omega$  resistance connected to Pin 11. In the CXA1782, TG1 and TG2 are inter-linked switches.

To jump tracks in FWD and REV directions, turn TM3 or TM4 ON. During this time, the peak voltage applied to the tracking coil is determined by the TM3 or TM4 current and the feedback resistance from Pin 12. To be more specific,

Track jump peak voltage = TM3 (or TM4) current imes feedback resistance value

The FWD and REV sled kick is performed by turning TM5 or TM6 ON. During this time, the peak voltage applied to the sled motor is determined by the TM5 or TM6 current and the feedback resistance from Pin 15;

Sled kick peak voltage = TM5 ( or TM6) current × feedback resistance The values of the current for each switch are determined by the resistance connected between Pin 17 and VEE. When this resistance is  $120k\Omega$ :

TM3 ( or TM4) =  $\pm 11\mu$ A, and TM5 (or TM6) =  $\pm 22\mu$ A.

As is the case with the FE signal, the TE signal is switched to pass through a low-pass filter formed by the internal resistance ( $100k\Omega$ ) and the capacitance connected to Pin 47.

#### Focus OK Circuit

The focus OK circuit creates the timing window okaying the focus servo from the focus search state. The HPF output is obtained at Pin 30 from Pin 31 (RF signal), and the LPF output (opposite phase) of the focus OK amplifier output is also obtained.

The focus OK output reverses when  $V{\mbox{\scriptsize RFI}}-V{\mbox{\scriptsize RFO}}\approx-0.37V.$

Note that, C5 determines the time constant of the HPF for the EFM comparator and mirror circuit and the LPF of the focus OK amplifier. Ordinarily, with a C5 equal to 0.01µF selected, the fc is equal to 1kHz, and block error rate degradation brought about by RF envelope defects caused by scratched discs can be prevented.

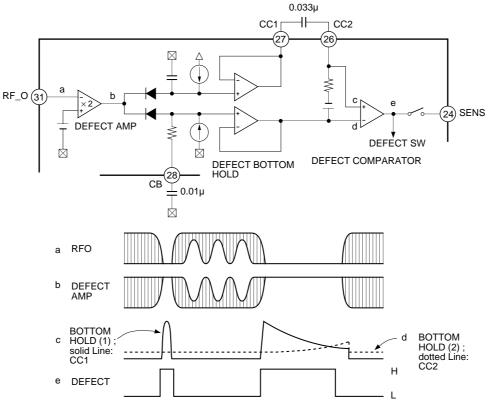

## **DEFECT Circuit**

After the RFI signal is reverted, two time constants, long and short, are held at bottom. The short time constant bottom hold responds to 0.1ms or greater disc mirror defects, and the long time constant bottom hold holds the pre-defect mirror level. By differentiating and level-shifting these constants with capacitor coupling and comparing both signals, the mirror defect detection signal is generated.

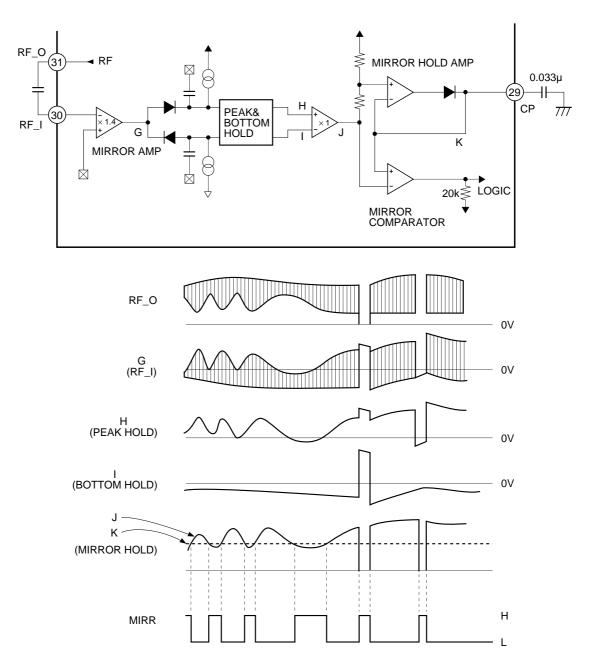

## **Mirror Circuit**

The mirror circuit performs peak and bottom hold after the RFI signal has been amplified.

The peak and bottom holds are both held through the use of a time constant. For the peak hold, a time constant can follow a 30kHz traverse, and, for the bottom hold, one can follow the rotation cycle envelope fluctuation.

The DC playback envelope signal J is obtained by amplifying the difference between the peak and bottom hold signals H and I. Signal J has a large time constant of 2/3 its peak value, and the mirror output is obtained by comparing it to the peak hold signal K. Accordingly, when on the disc track, the mirror output is Low; when between tracks (mirrored portion), it is High; and when a defect is detected, it is High. The mirror hold time constant must be sufficiently large compared with the traverse signal.

In the CXA1782, this mirror output is used only during braking operations, and no external output pin is attached. Accordingly, when connecting DSP such as the CXD2500 with MIRR input pin, input the C. OUT output to the MIRR input of the DSP.

## Commands

The input data to operate this IC is configured as 8-bit data; however, below, this input data is represented by 2-digit hexadecimal numerals in the form \$XX, where X is a hexadecimal numeral between 0 and F. Commands for the CXA1782 can be broadly divided into four groups ranging in value from \$0X to \$3X.

1. \$0X ("FZC" at SENS pin (Pin 24))

These commands are related to focus servo control. The bit configuration is as shown below.

| D7 | D6 | D5 | D4 | D3  | D2     | D1  | D0  |

|----|----|----|----|-----|--------|-----|-----|

| 0  | 0  | 0  | 0  | FS4 | DEFECT | FS2 | FS1 |

Four focus-servo related switches exist: FS1, FS2, FS4, and DEFECT corresponding to D0 to D3, respectively.

- \$00 When FS1 = 0, Pin 8 is charged to  $(22\mu A 11\mu A) \times 50k\Omega = 0.55V$ .

- If, in addition, FS2 = 0, this voltage is no longer transferred, and the output at Pin 6 becomes 0V.

- \$02 From the state described above, the only FS2 becomes 1. When this occurs, a negative signal is output to Pin 6. This voltage level is obtained by equation 1 below.

$(22\mu A - 11\mu A) \times 50 k\Omega \times \frac{\text{resistance between Pins 6 and 7}}{50 k\Omega} \qquad \dots \qquad \text{Equation 1}$

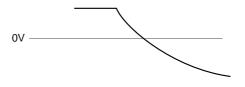

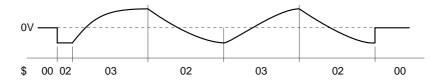

\$03 From the state described above, FS1 becomes 1, and a current source of +22µA is split off. Then, a CR charge/discharge circuit is formed, and the voltage at Pin 8 decreases with the time as shown in Fig. 1 below.

Fig. 1. Voltage at Pin 8 when FS1 gose from  $0 \rightarrow 1$

This time constant is obtained with the  $50k\Omega$  resistance and an external capacitor.

By alternating the commands between \$02 and \$03, the focus search voltage can be constructed. (Fig. 2)

Fig. 2. Constructing the search voltage by alternating between \$02 and \$03. (Voltage at Pin 6)

\$04 When the fact that the RF signal is missing is detected and the scratches on the disc are detected with DEFECT = 0, DFCT (FS3) is turned ON.

## 1-1. FS4

This switch is provided between the focus error input (Pin 2) and the focus phase compensation, and is in charge of turning the focus servo ON and OFF.

$00 \rightarrow 08$ Focus OFF  $\leftarrow$  Focus ON

## 1-2. Procedure of focus activation

For description, suppose that the polarity is as described below.

- a) The lens is searching the disc from far to near;

- b) The output voltage (Pin 6) is changing from negative to positive; and

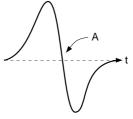

- c) The focus S-curve is varying as shown below.

Fig. 3. S-curve

The focus servo is activated at the operating point indicated by A in Fig. 3. Ordinarily, focus searching and the turning the focus servo switch ON are performed during the focus S-curve transits the point A indicated in Fig. 3. To prevent misoperation, this signal is ANDed with the focus OK signal.

In this IC, FZC (Focus Zero Cross) signal is output from the SENS pin (Pin 24) as the point A transit signal. In addition, focus OK is output as a signal indicating that the signal is in focus (can be in focus in this case).

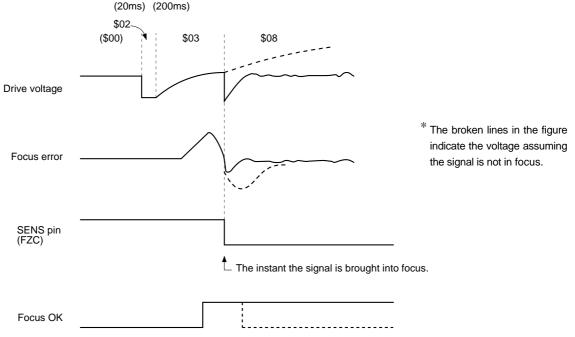

Following the line of the above description, focusing can be well obtained by observing the following timing chart.

Fig. 4. Focus ON timing chart

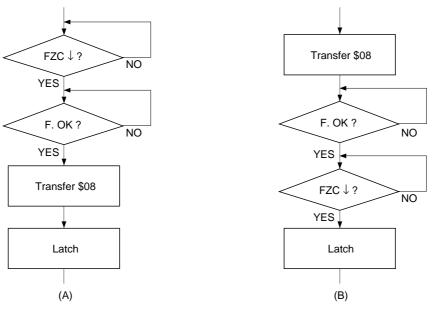

Note that the time from the High to Low transition of FZC to the time command \$08 is asserted must be minimized. To do this, the software sequence shown in B is better than the sequence shown in A.

Fig. 5. Poor and good software command sequences

## 1-3. SENS pin (Pin 24)

The output of the SENS pin differs depending on the input data as shown below.

\$0X: FZC\$1X: DEFECT\$2X: TZC\$3X: Automatic adjustment comparator output\$4X to 7X: HIGH-Z

## 2. \$1X ("DEFECT" at SENS pin (Pin 24))

These commands deal with switching TG1/TG2, brake circuit ON/OFF, and the sled kick output.

| The bit of | configurat | ion is as f | ollows |          |         |                     |    | Sled kic    | k height    |                   |

|------------|------------|-------------|--------|----------|---------|---------------------|----|-------------|-------------|-------------------|

| D7         | D6         | D5          | D4     | D3       | D2      |                     | D0 | D1<br>(PS1) | D0<br>(PS0) | Relative<br>value |

| 0          | 0          | 0           | 1      | TG1, TG2 | circuit | Sled kick<br>height |    | 0<br>0      | 0<br>1      | ±1<br>±2          |

|            |            |             |        | ON/OFF   | ON/OFF  |                     |    | 1           | 0<br>1      | ±3<br>±4          |

#### TG1, TG2

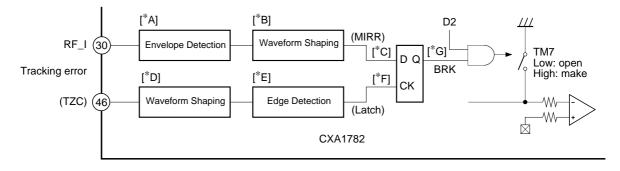

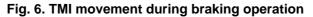

The purpose of these switches is to switch the tracking servo gain Up/Normal. TG1 and TG2 are interlinked switches. The brake circuit (TM7) is to prevent the occurrence of such frequently occurring phenomena as extremely degraded actuator settling due to the servo motor exceeding the linear range causing what should be a 100-track jump to fall back down to a 10-track jump after a 100 or 10-track jump has been performed. To do this, when the actuator travels radially; that is, when it traverses from the inner track to the outer track of the disc and vice versa, the brake circuit utilizes the fact that the phase relationship between the RF envelope and the tracking error is 180° out-of-phase to cut the unneeded portion of the tracking error and apply braking.

# 3. \$2X ("TZC" at SENS pin (Pin 24))

These commands deal with turning the tracking servo and sled servo ON/OFF, and creating the jump pulse and fast forward pulse during access operations.

| D7 | D6 | D5 | D4 | D3           | D2           | D1      | D0           |

|----|----|----|----|--------------|--------------|---------|--------------|

|    |    |    |    |              |              |         |              |

| 0  | 0  | 1  | 0  | Tracking     |              | Sled    |              |

|    |    |    |    | control      |              | control |              |

|    |    |    |    | 00: OFF      |              | 00: OF  | F            |

|    |    |    |    | 01: Serve    | 01: Servo ON |         | rvo ON       |

|    |    |    |    | 10: F-JU     | MP           | 10: F-F | AST FORWARD  |

|    |    |    |    | 11: R-JU     | IMP          | 11: R-I | AST FORWARD  |

|    |    |    |    | $\downarrow$ | /            |         | $\downarrow$ |

|    |    |    |    | TM1, TM      | 13, TM4      | TM2, 1  | M5, TM6      |

## 4. \$3X

These commands control the balance and gain control circuit switches used during automatic tracking adjustment.

In the initial resetting state, BAL1 to BAL3 switches are OFF and TOG1 to TOG3 switches are ON.

#### Balance adjustment

The balance adjustment switches BAL1 to BAL3 can be controlled by setting D3 = 0. The switches are set using D0 to D2.

At this time, the balance adjustment LPF comparator output is selected at the SENS pin.

Data is set by specifying switch conditions D0 to D2 and sending a latch pulse with D3 = 0.

Sending a latch pulse with D3 = 1 does not change the balance switch settings.

#### **Balance adjustment**

## Gain adjustment

The gain adjustment switches TOG1 to TOG3 can be controlled by setting D3 = 1. These switches are set using D0 to D2. At this time, the balance adjustment HPF comparator output is selected for SENS pin.

In a fashion similar to the method used with the balance adjustment, set the data by sending a latch pulse with D3 = 1, specifying the switch conditions D0 to D2.

#### Gain adjustment

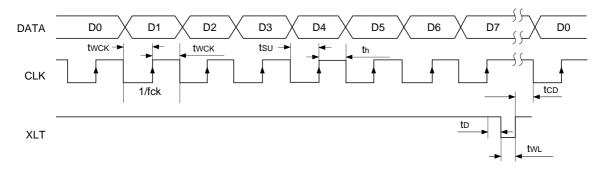

# **CPU Serial Interface Timing Chart**

|                        |        |      |       | (V   | cc = 3.0V) |

|------------------------|--------|------|-------|------|------------|

| Item                   | Symbol | Min. | Type. | Max. | Unit       |

| Clock frequency        | fck    |      |       | 1    | MHz        |

| Clock pulse width      | fwck   | 500  |       |      | ns         |

| Setup time             | tsu    | 500  |       |      | ns         |

| Hold time              | th     | 500  |       |      | ns         |

| Delay time             | t⊳     | 500  |       |      | ns         |

| Latch pulse width      | tw∟    | 1000 |       |      | ns         |

| Data transfer interval | tcd    | 1000 |       |      | ns         |

# System Control

| Item             | ADRESS      |   |   |                                 |                                           | SENS                             |                                   |                  |        |

|------------------|-------------|---|---|---------------------------------|-------------------------------------------|----------------------------------|-----------------------------------|------------------|--------|

| nem              | D7 D6 D5 D4 |   |   |                                 | D3                                        | D2 D1 D0                         |                                   | D0               | output |

| Focus Control    | 0 0 0 0     |   | 0 | FS4<br>Focus<br>ON = 1, OFF = 0 | DEFECT (FS3)<br>Disable = 1<br>Enable = 0 | FS2<br>Search<br>ON = 1, OFF = 0 | FS1<br>Search<br>Up = 1, Down = 0 | FZC              |        |

| Tracking Control | 0           | 0 | 0 | 1                               | TG1, TG2<br>ON = 1, OFF = 0               | Brake<br>ON = 1, OFF = 0         | Sled<br>Kick + 2                  | Sled<br>Kick + 1 | DEFECT |

| Tracking Mode    | 0           | 0 | 1 | 0                               | Tracking Mode                             | TZC                              |                                   |                  |        |

| Select           | 0           | 0 | 1 | 1                               | Automatic tracl                           | Gain/Bal                         |                                   |                  |        |

# \*1 TRACKING MODE

|          | D3 | D2 |

|----------|----|----|

| OFF      | 0  | 0  |

| ON       | 0  | 1  |

| FWD JUMP | 1  | 0  |

| REV JUMP | 1  | 1  |

# \*2 SLED MODE

| D1 | D0 |

|----|----|

| 0  | 0  |

| 0  | 1  |

| 1  | 0  |

| 1  | 1  |

|    | 0  |

DEFECT E: enable D: disable

# Serial Data Truth Table

| Serial Data   | Hex  | Functions |        |     |     |  |  |

|---------------|------|-----------|--------|-----|-----|--|--|

|               |      | FS = 4321 |        |     |     |  |  |

| FOCUS CONTROL |      | FS4       | DEFECT | FS2 | FS1 |  |  |

| 0000000       | \$00 | 0         | Е      | 0   | 0   |  |  |

| 0000001       | \$01 | 0         | Е      | 0   | 1   |  |  |

| 0000010       | \$02 | 0         | Е      | 1   | 0   |  |  |

| 0000011       | \$03 | 0         | Е      | 1   | 1   |  |  |

| 00000100      | \$04 | 0         | D      | 0   | 0   |  |  |

| 00000101      | \$05 | 0         | D      | 0   | 1   |  |  |

| 00000110      | \$06 | 0         | D      | 1   | 0   |  |  |

| 00000111      | \$07 | 0         | D      | 1   | 1   |  |  |

| 00001000      | \$08 | 1         | E      | 0   | 0   |  |  |

| 00001001      | \$09 | 1         | Е      | 0   | 1   |  |  |

| 00001010      | \$0A | 1         | Е      | 1   | 0   |  |  |

| 00001011      | \$0B | 1         | Е      | 1   | 1   |  |  |

| 00001100      | \$0C | 1         | D      | 0   | 0   |  |  |

| 00001101      | \$0D | 1         | D      | 0   | 1   |  |  |

| 00001110      | \$0E | 1         | D      | 1   | 0   |  |  |

| 00001111      | \$0F | 1         | D      | 1   | 1   |  |  |

| TRACKING MODE | Hex  | TM = 6 5 4 3 2 1 |

|---------------|------|------------------|

| 0010000       | \$20 | 0 0 0 0 0 0      |

| 00100001      | \$21 | 000010           |

| 00100010      | \$22 | 01000            |

| 00100011      | \$23 | 10000            |

| 00100100      | \$24 | 00001            |

| 00100101      | \$25 | 000011           |

| 00100110      | \$26 | 010001           |

| 00100111      | \$27 | 100001           |

| 00101000      | \$28 | 000100           |

| 00101001      | \$29 | 000110           |

| 00101010      | \$2A | 010100           |

| 00101011      | \$2B | 100100           |

| 00101100      | \$2C | 001000           |

| 00101101      | \$2D | 001010           |

| 00101110      | \$2E | 011000           |

| 00101111      | \$2F | 101000           |

| Automatic       |      | TOG SW | BAL SW |

|-----------------|------|--------|--------|

| adjustment mode | Hex  | 321    | 321    |

| 00110000        | \$30 |        | 1 1 1  |

| 00110001        | \$31 |        | 110    |

| 00110010        | \$32 |        | 101    |

| 00110011        | \$33 |        | 100    |

| 00110100        | \$34 |        | 011    |

| 00110101        | \$35 |        | 010    |

| 00110110        | \$36 |        | 001    |

| 00110111        | \$37 |        | 000    |

| 00111000        | \$38 | 111    |        |

| 00111001        | \$39 | 110    |        |

| 00111010        | \$3A | 101    |        |

| 00111011        | \$3B | 100    |        |

| 00111100        | \$3C | 011    |        |

| 00111101        | \$3D | 010    |        |

| 00111110        | \$3E | 001    |        |

| 00111111        | \$3F | 000    |        |

DATA D3 = 0: Balance switch setting DATA D3 = 1: Gain switch setting

**Note)** 0 means OFF and 1 means ON for TOG SW and BAL SW. These are not equal to the setting values of each bit for serial data.

# Initial State (resetting state)

| Itom             | A | DDF         | RES | S | DATA |             |   |   | HEXADECIMAL  |

|------------------|---|-------------|-----|---|------|-------------|---|---|--------------|

| ltem             |   | D7 D6 D5 D4 |     |   |      | D3 D2 D1 D0 |   |   | HEARDECINIAE |

| Focus Control    | 0 | 0           | 0   | 0 | 0    | 0           | 0 | 0 | \$00         |

| Tracking Control | 0 | 0           | 0   | 1 | 0    | 0           | 0 | 0 | \$10         |

| Tracking Mode    | 0 | 0           | 1   | 0 | 0    | 0           | 0 | 0 | \$20         |

| Select           | 0 | 0           | 4   | 1 | 0    | 1           | 1 | 1 | \$37         |

|                  |   | 0           | ľ   | 1 | 1    | 0           | 0 | 0 | \$38         |

The above data means the following operation modes.

| Focus Control    | Focus off, Defect enable, Focus Search off, Focus Search down  |

|------------------|----------------------------------------------------------------|

| Tracking Control | TG1 – TG2 off, Brake off, Sled Kick + 2 off, Sled Kick + 1 off |

| Tracking Mode    | Tracking off, Sled off                                         |

| Select           | Tracking gain $\rightarrow$ min. (TOG SW: 1 1 1)               |

|                  | Tracking balance: RE3 $\rightarrow$ max. (TBAL SW: 0 0 0)      |

#### Notes on Operation

#### 1. FSET pin

The FSET pin determines the fc for the focus and tracking high-frequency phase compensation.

#### 2. ISET pin

ISET current = 1.27V/R

= Focus search current

= Tracking jump current

= Sled kick current (\$1X: PS1 = PS0 = 0)

$$\times \frac{1}{2}$$

Use the setting resistance within the range of  $120k\Omega$  to  $240k\Omega$ . If the resistance value is out of this range, the oscillation may be occurred in the ISET block.

3. FE (focus error)/TE (tracking error) gain changing method

- 1) High gain: Resistance between FE pins (pins 6 and 7)  $100k\Omega \rightarrow Large$ Resistance between TE pins (pins 12 and 13)  $100k\Omega \rightarrow Large$

- 2) Low gain: A signal, whose resistance is divided between Pins 1 and 2, is input to FE. The internal gain adjustment circuit is used for TE.

- Input voltage at Pins 19 to 22 of the microcomputer interface should be as follows: VIH Vcc × 90% or more VIL Vcc × 10% or less

- 5. Focus OK circuit

- 1) Refer to the "Description of Operation" for the time constant setting of the focus OK amplifier LPF and the mirror amplifier HPF.

Output voltage High: VFOKH ≈ near Vcc Output voltage Low: VFOKL ≈ Vsat (NPN)

The FOK and comparator output are as follows:

6. Sled amplifier

The sled amplifier may oscillate when used by the buffer amplifier. Use with a gain of approximately 20dB.

#### Sled/Tracking internal phase compensation and reference design material

|             | Item         | SD    | Measurement pin | Conditions            | Тур. | Unit |

|-------------|--------------|-------|-----------------|-----------------------|------|------|

| ပ္ပ         | 1.2kHz gain  | 08    | 6               | Сғів = 0.1µF          | 21.5 | dB   |

| L<br>L<br>L | 1.2kHz phase | 08    | 0               | $C_{FGD} = 0.1 \mu F$ | 63   | deg  |

|             | 1.2kHz gain  | 25    |                 |                       | 13   | dB   |

| ×           | 1.2kHz phase | 25    | 13              | Стои = 0.1µF          | -125 | deg  |

| TRK         | 2.7kHz gain  | 25→13 | 13              | $C_{1GU} = 0.1 \mu F$ | 26.5 | dB   |

|             | 2.7kHz phase | 25→13 |                 |                       | -130 | deg  |

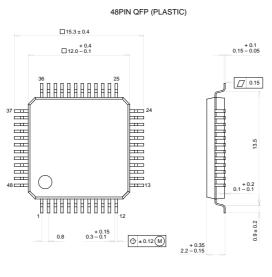

#### Package Outline Unit: mm

CXA1782CQ

#### NOTE : PALLADIUM PLATING This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).

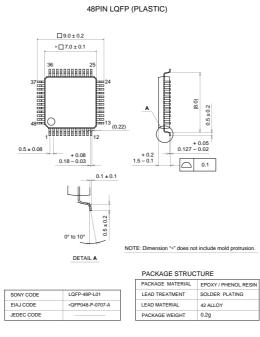

CXA1782CR

NOTE : PALLADIUM PLATING This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).