捷多邦,专业PCB打样工厂,24小时加急出货

SONY

# **RX Gain Control Amplifier**

### Description

24 pin SSOP (Plastic) CXA3001N is an RX gain control amplifier for

V

mW

V

V

V

V

# CDMA cellular mobile phone.

# **Features**

- Wide gain control range

- · Linear gain slope

- Typ. 6dB at Gain = 45dB Noise figure

- Output IP3 Typ. +2dBm at Gain = 40dB

- 2 input ports

- Power save function included

## **Absolute Maximum Ratings**

Supply voltage Vcc 6 • Operating temperature -40 to +85 °C Topr Storage temperature Tstg -65 to +150 °C

PD

420

-0.3 to 6

-0.3 to Vcc +0.3

-0.3 to Vcc +0.3

0 to 2.5

3.1 to 3.8

- Allowable power dissipation

- Supply voltage range

- Logic input voltage

- Signal input voltage

- Differential signal input voltage

#### **Operating Conditions**

Supply voltage

### **Applications**

- CDMA cellular mobile phone

- CDMA & AMPS cellular phone

#### Structure

Bipolar sillicon monolithic IC

**CXA3001N**

# SONY

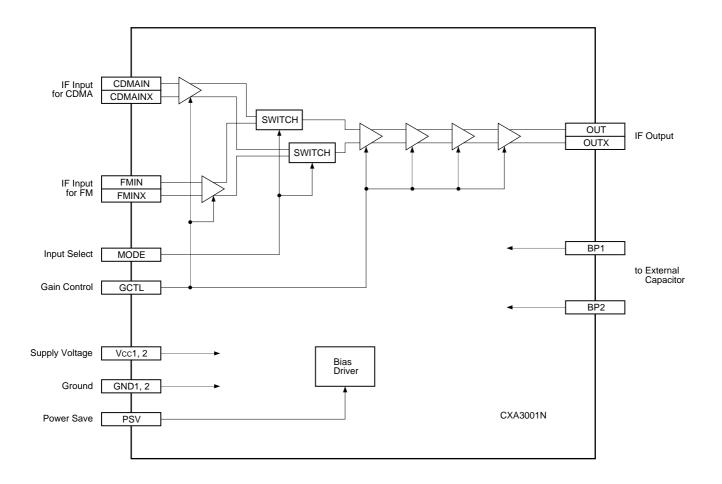

# Block Diagram

CXA3001N

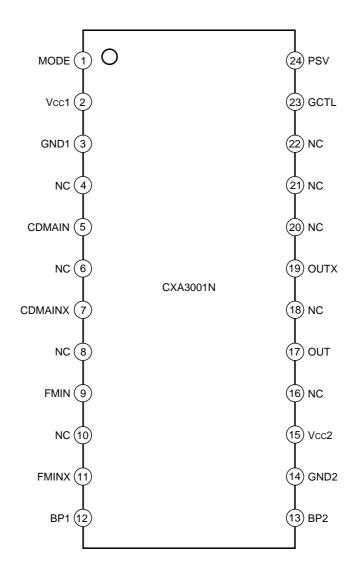

# **Pin Configuration**

# **Pin Description**

| Pin<br>No.        | Symbol  | Pin voltage<br>Typ. (V) | Equivalent circuit | Description                                            |

|-------------------|---------|-------------------------|--------------------|--------------------------------------------------------|

| 1                 | MODE    |                         | Ucc1               | Input select pin.<br>CDMAIN for High.<br>FMIN for Low. |

| 2                 | Vcc1    | 3.6                     |                    | Positive power supply.                                 |

| 3                 | GND1    | 0                       |                    | Ground.                                                |

| 4<br>6<br>8<br>10 | N.C.    |                         |                    | No connection.                                         |

| 5                 | CDMAIN  | 1.2                     |                    | Differential input pins for                            |

| 7                 | CDMAINX | 1.2                     | (5) $(7)$ $(7)$    | received CDMA IF signal.                               |

| 9                 | FMIN    | 1.2                     |                    | Differential input pins for                            |

| 11                | FMINX   | 1.2                     | 9 (1)              | received FM IF signal.                                 |

| 12                | BP1     |                         |                    |                                                        |

| 13                | BP2     | 2.4                     |                    | Connected to GND with capacitor 0.01µF.                |

| 14                | GND2    | 0                       |                    | Ground for output stage.                               |

| 15                | Vcc2    | 3.6                     |                    | Positive power supply for output stage.                |

| 16                | N.C.    |                         |                    | No connection.                                         |

| 17                | OUT     | 1.7                     |                    | Differential output pins for                           |

| 19                | OUTX    | 1.7                     | GND2               | received IF signal.                                    |

| Pin<br>No.           | Symbol | Pin voltage<br>Typ. (V) | Equivalent circuit   | Description                                                 |

|----------------------|--------|-------------------------|----------------------|-------------------------------------------------------------|

| 18<br>20<br>21<br>22 | N.C.   |                         |                      | No connection.                                              |

| 23                   | GCTL   |                         | Vcc1<br>(23)<br>GND1 | Gain control pin with a ripple filter.                      |

| 24                   | PSV    |                         | 24<br>40k<br>GND1    | Power save function pin.<br>High: Active<br>Low: Power save |

# SONY

# **Electrical Characteristics**

# **DC** characteristics

(Vcc = 3.6V, Ta = 25°C)

| Parameter                  | Symbol  | Conditions                       | Min. | Тур. | Max. | Unit |

|----------------------------|---------|----------------------------------|------|------|------|------|

| Current consumption 1      | lcc1    | VGCTL = 1.5V, Pin 2              | 10   | 14   | 19   | mA   |

| Current consumption 2 Icc2 |         | V <sub>GCTL</sub> = 1.5V, Pin 15 | 4.7  | 6.6  | 9.0  |      |

| Current consumption 3 Icc3 |         | VPSV = 0.5V, Pin 2               |      |      | 1    |      |

| Current consumption 4      | Icc4    | VPSV = 0.5V, Pin 15              |      |      | 1    |      |

| Input current pin 1H       | Imode h | VMODE = 3V                       |      |      | 10   |      |

| Input current pin 1L       | IMODE L | VMODE = 0.5V -2                  |      |      |      |      |

| Input current pin 23H      | IGCTL H | Vgctl = 3V                       |      |      | 10   | μA   |

| Input current pin 23L      | IGCTL L | Vgctl = 0.5V                     | -10  |      |      |      |

| Input current pin 24H      | IPSV H  | VPSV = 3V                        |      |      | 10   |      |

| Input current pin 24L      | IPSV L  | VPSV = 0.5V                      | -10  |      |      |      |

| MODE high voltage          | Vмн     | Pin 1                            | 3    |      |      |      |

| MODE low voltage           | Vml     | Pin 1                            |      |      | 0.5  | v    |

| PSV high voltage           | Vpsh    | Pin 24                           | 3    |      |      |      |

| PSV low voltage            | Vpsl    | Pin 24                           |      |      | 0.5  |      |

# AC characteristics

(Vcc = 3.6V, Ta = 25°C)

| Parameter                                | Symbol   | Conditions                                                                                                                          |                                | Min. | Тур. | Max. | Unit |

|------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|------|------|------|

| Operating frequency range                | Fr       |                                                                                                                                     |                                | 10   |      | 100  | MHz  |

| Gain CDMA2.3                             | GCDMA2.3 | Vmode = "H"<br>Vgctl = 2.3V                                                                                                         | f = 85.38MHz<br>Level = –50dBm | 37   | 41   | 46   |      |

| Gain CDMA1.5                             | GCDMA1.5 | Vmode = "H"<br>Vgctl = 1.5V                                                                                                         | Level = -30dBm                 | -7.5 | -3   | 1.5  | dB   |

| Gain CDMA0.7                             | GCDMA0.7 | Vmode = "H"<br>Vgctl = 0.7V                                                                                                         | Level = -10dBm                 | -55  | -49  | -44  |      |

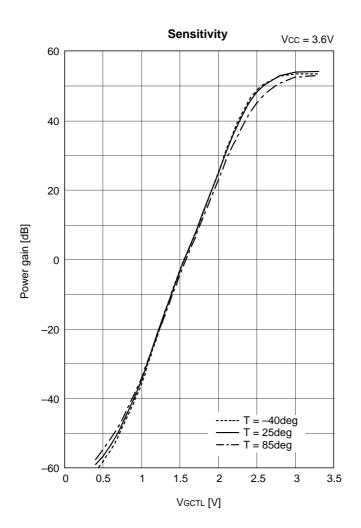

| CDMA Gain slope                          | GCLIN    | VMODE = "H"                                                                                                                         | VGCTL = 1 to 2V                | 57   | 60   | 63   | dB/V |

| Gain FM2.3                               | GFм2.3   | Vmode = "L"<br>Vgctl = 2.3V                                                                                                         | f = 85.38MHz<br>Level = –50dBm | 37   | 41   | 46   |      |

| Gain FM1.5                               | GFM1.5   | Vmode = "L"<br>Vgctl = 1.5V                                                                                                         | Level = -30dBm                 | -7.5 | -3   | 1.5  | dB   |

| Gain FM0.7                               | GFM0.7   | Vmode = "L"<br>Vgctl = 0.7V                                                                                                         | Level = -10dBm                 | -55  | -49  | -44  |      |

| FM Gain slope                            | GFMLIN   | VMODE = "L"                                                                                                                         | VGCTL = 1 to 2V                | 57   | 60   | 63   | dB/V |

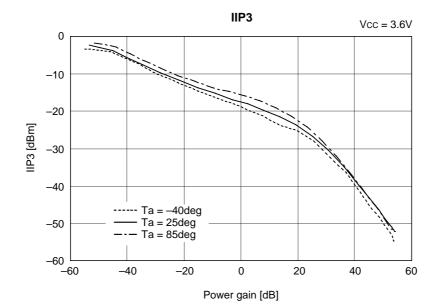

| Input level<br>3rd order intercept point | IIP3     | $\begin{array}{l} V_{MODE} = "H" \\ G_{CDMA} = 40 dB^{*} \\ F_{1} = 86.38 MHz \\ F_{2} = 87.38 MHz \\ Measure of 85.38 \end{array}$ | SMHz                           | -42  | -38  |      | dBm  |

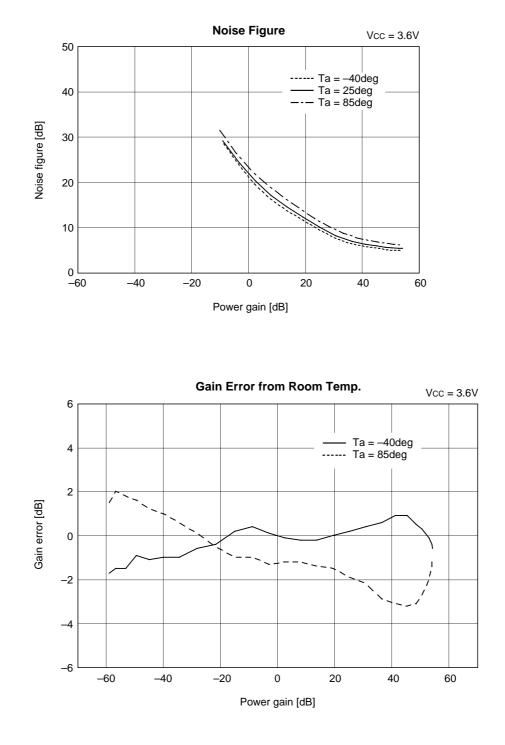

| Noise Figure                             | NF       | VMODE = "H"<br>GCDMA = 40dB*<br>Used 1MHz BPF<br>Measure of 85.38                                                                   | MHz                            |      | 6.5  | 9.5  | dB   |

$^{\ast}$  Adjust GCTL voltage, and set the overall gain to 40dB.

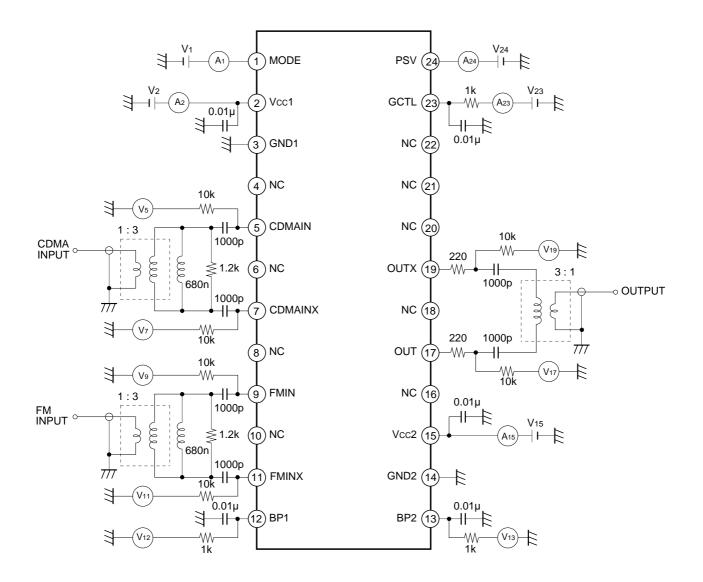

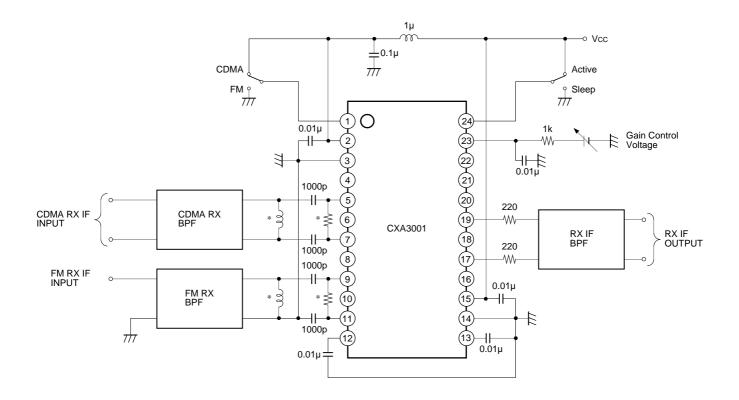

# **Application Circuit**

\* Must be adjusting values to result a best impedance matching between BPF filter and this IC.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

## **Design Reference Values**

### Single ended measurement

(Vcc = 3.6V, Ta = 25°C)

| Item              | Symbol | Conditions                 | Тур. | Unit |

|-------------------|--------|----------------------------|------|------|

| Input resistance  | Rin    |                            | 900  | Ω    |

| Input capacitance | CIN    | f = 85.38MHz, Vgст∟ = 1.5V | 9    | pF   |

| Output resistance | Rout   |                            | 30   | Ω    |

### **Notes on Operation**

- 1) This IC is a wideband amplifier with wide gain control range. Separate Pin 3 (GND1) and Pin 14 (GND2) to prevent interference between input and output. Furthermore, the decoupling capacitors between Pins 2 and 3, Pins 14 and 15 should be as close to the IC as possible.

- 2) The resistors connected to Pins 17 and 19 should be as close to the IC as possible.

- This IC assumes the excellent characteristics when the differential input impedance between Pins 5 and 7, Pins 9 and 11 is 500Ω. Refer to the Measurement Circuit for the external element settings, etc.

- 4) Connect the capacitors, which are connected to Pins 12 and 13, to Pin 14 (GND2).

- 5) Pay attention to handling this IC because its electrostatic discharge strength is weak.

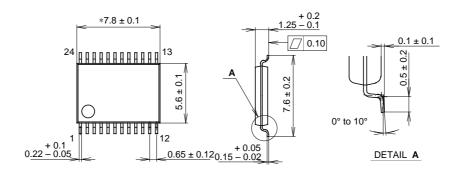

# Package Outline Unit: mm

###

NOTE : \*NOT INCLUDE MOLD FINS.

### PACKAGE STRUCTURE

|            |                             | PACKAGE MATERIAL | EPOXY / PHENOL RESIN |

|------------|-----------------------------|------------------|----------------------|

| SONY CODE  | SSOP-24P-L01                | LEAD TREATMENT   | SOLDER PLATING       |

| EIAJ CODE  | A SIMILAR TO SSOP024-P-0300 | LEAD MATERIAL    | 42 ALLOY             |

| JEDEC CODE |                             | PACKAGE WEIGHT   |                      |