# LCD Driver

#### Description

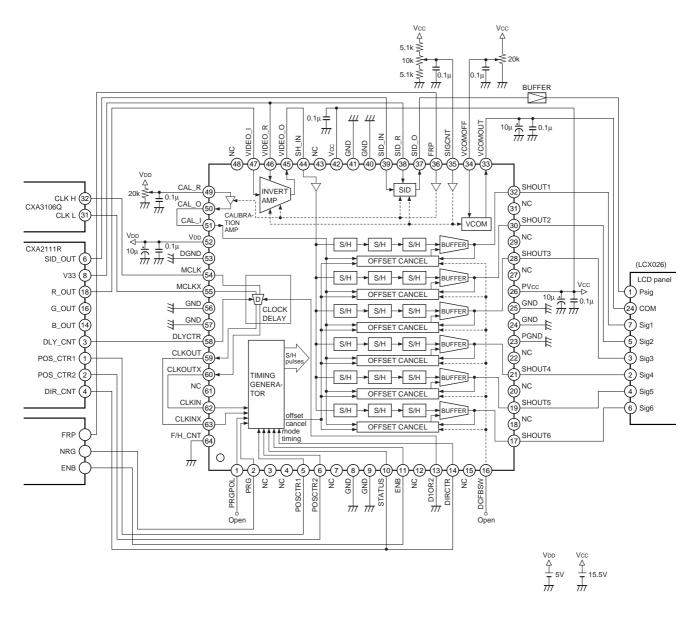

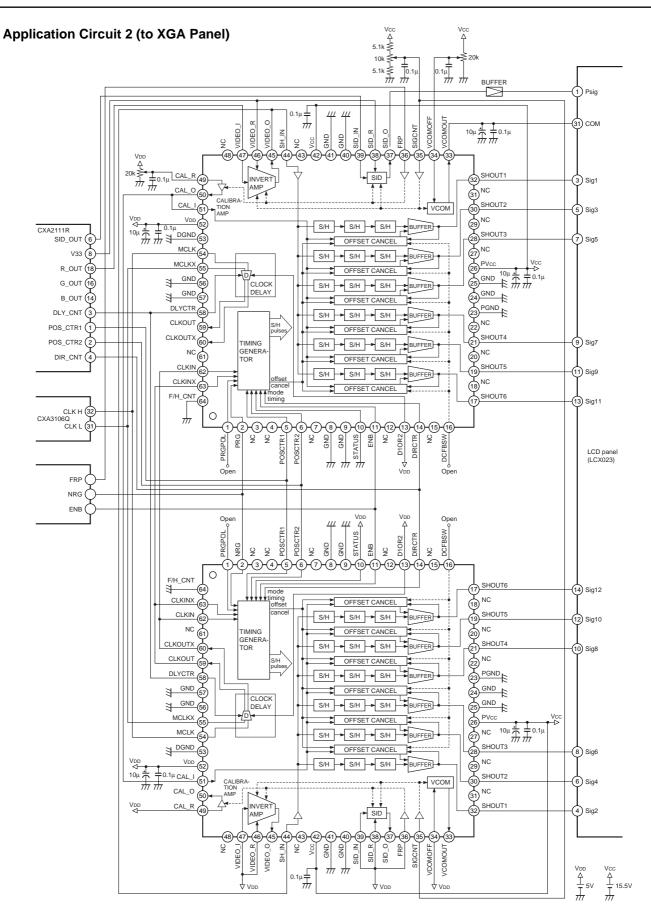

The CXA3512R is a driver IC for the analog inputs of SVGA or higher Sony polycrystalline silicon TFT LCD panels. It has a line invert amplifier and analog demultiplexers, as well as the timing generator and output buffers required for these. The CXA3512R can directly drive an LCD panel. The VCOM setting circuit and precharge pulse waveform generator are WWW.DZSC.COM also on-chip.

**CXA3512R**

#### Features

- High-speed signal processing supports XGA high refresh signal

- Overall wide band response

- · Low output deviation by on-chip output offset cancel circuit

- Invert amplifier with small phase delay difference between inverted signal and non-inverted signal

- On-chip timing generator with ECL

- · Dot clock phase adjustment function

- VCOM voltage generation circuit

- Precharge pulse waveform generation circuit

# **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul>        | Vcc | 16          |

|-------------------------------------------|-----|-------------|

|                                           | Vdd | 5.5         |

| <ul> <li>Operating temperature</li> </ul> |     | -20 to +70  |

| <ul> <li>Storage temperature</li> </ul>   |     | –65 to +150 |

| · Allowable nover discipation             | D-  | 2200        |

Allowable power dissipation PD 2300

# **Recommended Operating Conditions**

| Supply voltage                          | Vcc | 15.0 to 15.5 |

|-----------------------------------------|-----|--------------|

|                                         | Vdd | 4.75 to 5.25 |

| <ul> <li>Ambient temperature</li> </ul> |     | -20 to +70   |

mW (single layered board mounted)

V V

°C

V V °C °C

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# SONY

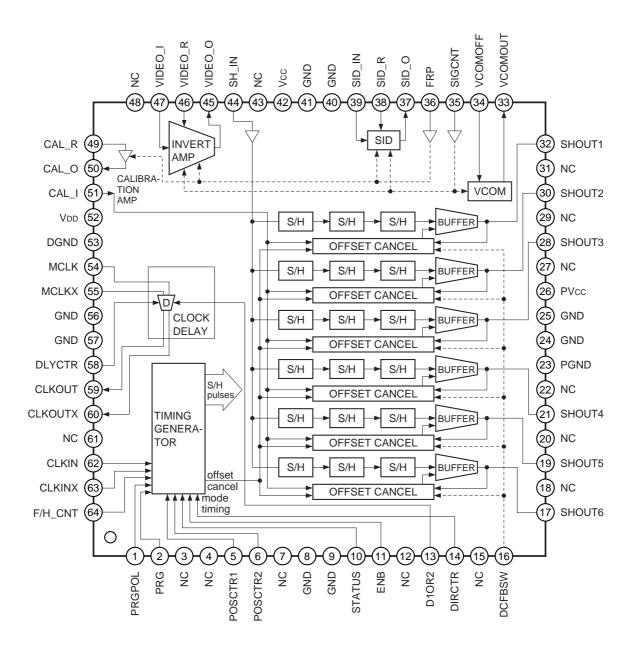

#### **Block Diagram**

CXA3512R

# **Pin Description**

| Pin<br>No. | Symbol             | I/O | Standard voltage level                   | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                         |

|------------|--------------------|-----|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | PRGPOL             | 1   | High: ≥ 2.5V<br>Low: ≤ 0.8V<br>OPEN High | VDD VDD VDD VDD<br>100k ≥ 20k ≥ 20k<br>100k ≥ 100k ≥ 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Selects the latch polarity of the PRG<br>pulse used as the time reference.<br>High: PRG pulse is latched at the<br>falling edge of CLKIN.<br>Low: PRG pulse is latched at the<br>rising edge of CLKIN.<br>Select the polarity with sufficient<br>timing margin after adjusting the<br>analog video and CLKIN phases<br>with DLYCTR. |

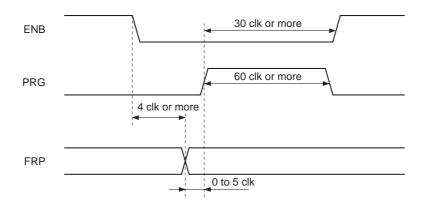

| 2          | PRG                | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V              | VDD<br>50k<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PRG pulse input.<br>See the Timing Chart.                                                                                                                                                                                                                                                                                           |

| 5<br>6     | POSCTR1<br>POSCTR2 | I   | See Table<br>A-1.                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Output phase adjustment.<br>Each pin has 4 setting values, for a<br>total of 16 settings.<br>(Adjustment in 1 dot clock units in<br>XGA mode, 1/2 dot clock units in<br>SVGA mode, and 1 dot clock units in<br>SXGA mode.)<br>See Tables A-1, A-2 and A-3.                                                                          |

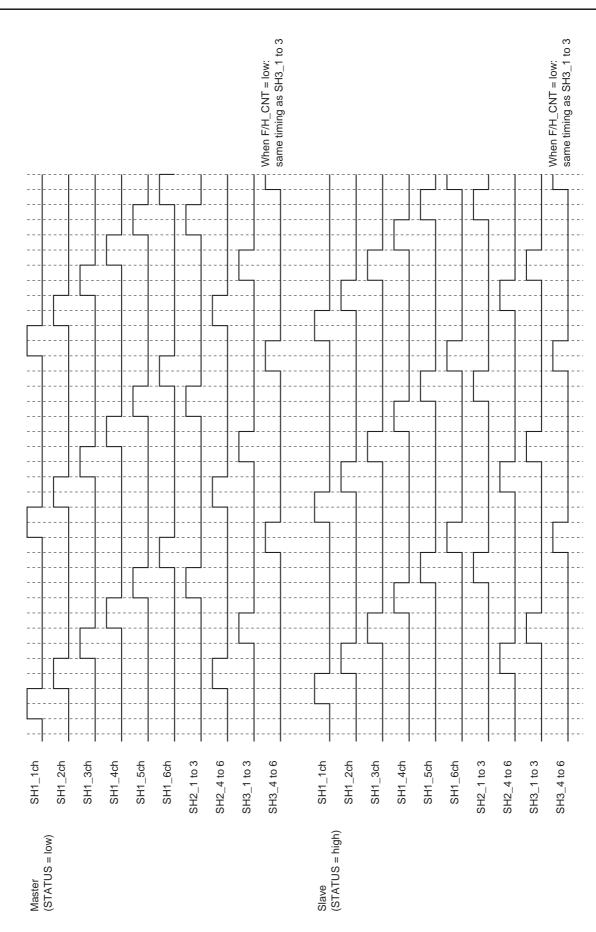

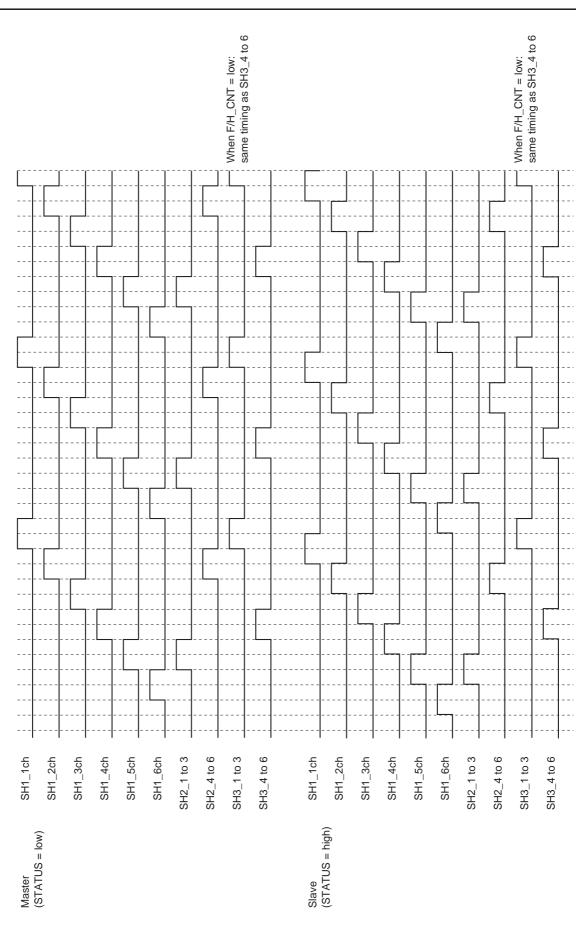

| 10         | STATUS             | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V<br>OPEN High | $\begin{array}{c} V_{DD} & V_{DD} & V_{DD} \\ \hline \\ 100k \\ 100k \\ 40k \\ 777 \\ 12\mu \\ 777 \\ 12\mu \\ 777 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Used in XGA and UXGA modes<br>(when using 2 ICs for a gamma-<br>corrected IC).<br>During forward scan, high: 2nd<br>device, low: 1st device<br>During reverse scan, high: 1st<br>device, low: 2nd device<br>See Table B.                                                                                                            |

| 11         | ENB                | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V              | VDD<br>50k<br>110<br>145<br>777<br>777<br>777<br>777                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ENB pulse input.<br>See the Timing Chart.                                                                                                                                                                                                                                                                                           |

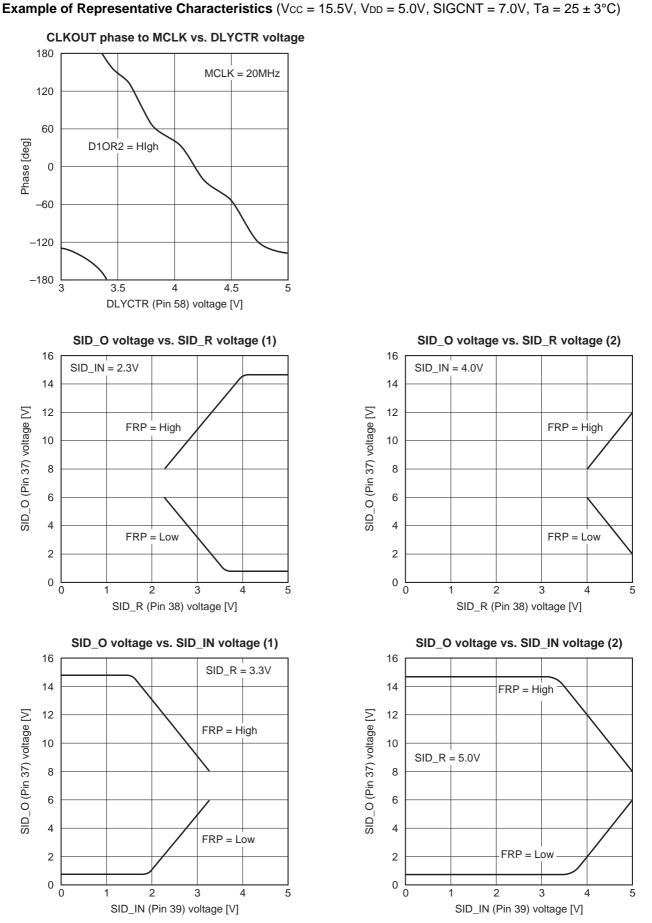

| 13         | D1OR2              | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V<br>OPEN High | $\begin{array}{c} V_{DD} & V_{DD} & V_{DD} \\ \hline \\ V_{DD} & V_{DD} & \downarrow \\ 100k \\ \hline \\ 100k \\ \hline \\ 40k \\ 12\mu \\ \hline \\ 777 \\ 12\mu \\ \hline \\ 777 \\ 12\mu \\ \hline \\ 777 \\ 777 \\ \hline \\ 777 \\ 777 \\ 777 \\ \hline \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 \\ 777 $ | CLKOUT pin frequency selection.<br>High: same frequency as MCLK<br>Low: double the MCLK frequency                                                                                                                                                                                                                                   |

| Pin<br>No.                       | Symbol                                                   | I/O | Standard voltage level                   | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                    |

|----------------------------------|----------------------------------------------------------|-----|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14                               | DIRCTR                                                   | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V<br>OPEN High | $\begin{array}{c} V_{DD} & V_{DD} & V_{DD} \\ \hline & & & \\ 100k \\ \hline & & & \\ 100k \\ \hline & & & \\ 40k \\ \hline & & & \\ 12\mu \\ \hline & & \\ \hline & & \\ \hline & & \\ \hline & & \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Scan direction setting.<br>Low: output as a time series in<br>descending order (reverse scan) of<br>output pin symbol (in order from<br>SHOUT6 to SHOUT1)<br>High: output in ascending order<br>(forward scan) |

| 16                               | DCFBSW                                                   | I   | OPEN High                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Offset cancel circuit on/off switch.<br>High: cancel circuit on<br>Use this pin at on (open).                                                                                                                  |

| 17<br>19<br>21<br>28<br>30<br>32 | SHOUT6<br>SHOUT5<br>SHOUT4<br>SHOUT3<br>SHOUT2<br>SHOUT1 | 0   | 1.5 to 13.5V                             | Vcc Vcc<br>1723<br>1930<br>2132<br>177<br>1930<br>1930<br>1930<br>1930<br>1930<br>1930<br>1930<br>1930<br>197<br>197<br>197<br>197<br>197<br>197<br>197<br>197                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Demultiplexer outputs.<br>Can be connected directly to the<br>LCD input pins.                                                                                                                                  |

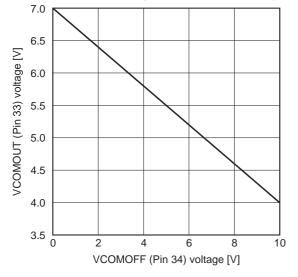

| 33                               | VCOMOUT                                                  | 0   | 3 to 7V                                  | Vcc<br>Vcc<br>70μ<br>33<br>145<br>60k<br>770μ<br>70μ<br>70μ<br>70μ<br>70μ<br>70μ<br>70μ<br>70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LCD common voltage of panel<br>output.<br>Can be set to Vsigcn⊤ to<br>(Vsigcn⊤ – 3V) by the Pin 34 input.                                                                                                      |

| 34                               | VCOMOFF                                                  | I   | 0 to 10V                                 | Vcc<br>4<br>34<br>↓<br>100k<br>100k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VCOMOUT (Pin 33) voltage setting.<br>VCOMOUT is the same potential as<br>SIGCNT for input of 0V, and<br>approximately 3V lower than that for<br>input of 10V.                                                  |

| 35                               | SIGCNT                                                   | I   | 7V                                       | $\begin{array}{c} & \\ & \\ \hline \\ & \\ \hline \\ & \\ \\ \hline \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ & \\ \\ \\ & \\ \\ \\ & \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$ | Signal center voltage (inversion<br>folded voltage) input.<br>Normally, set to 7V.                                                                                                                             |

| Pin<br>No. | Symbol  | I/O | Standard voltage level      | Equivalent circuit                                                                     | Description                                                                                                                                                                                                            |

|------------|---------|-----|-----------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

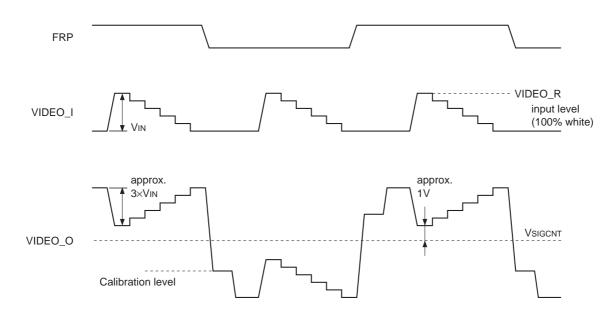

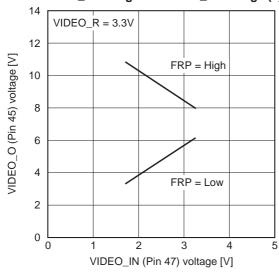

| 36         | FRP     | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V | VDD VDD VDD<br>36<br>100k<br>10k<br>50µ<br>777<br>777                                  | Invert pulse input.<br>High: inverse<br>Low: non-inverse<br>See the Timing Chart.                                                                                                                                      |

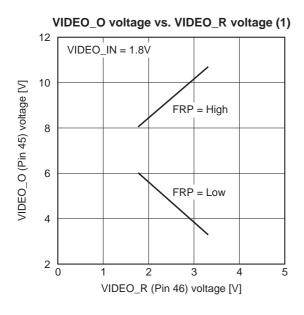

| 37         | SID_O   | 0   | 2 to 12V                    | 37<br>145<br>778k<br>0.2p<br>0.2p<br>778k<br>0.2p<br>778k<br>0.2p                      | SID block output.<br>Provide an external buffer for<br>precharge.                                                                                                                                                      |

| 38         | SID_R   | I   | 3.3V                        | $\begin{array}{c} Vcc \\ 10\mu \\ 38 \\ 30k \\ 777 \end{array}$                        | Precharge signal invert offset<br>adjustment.<br>When using the CXA2111R SID,<br>connect to the V33 output of the<br>CXA2111R.                                                                                         |

| 39         | SID_IN  | I   | 2.3 to 3.3V                 | $\begin{array}{c} V_{CC} \\ 40\mu \\ \hline \\ 39 \\ 145 \\ \hline \\ 777 \end{array}$ | Precharge waveform input.<br>Can be connected directly to the<br>CXA2111R SID output.<br>Connect to 5V when not using the<br>SID block.                                                                                |

| 44         | SH_IN   | I   | 2 to 10V                    | 44<br>44<br>200<br>200<br>44<br>                                                       | Analog demultiplexer input.<br>Connect to the VIDEO_O (Pin 45)<br>output.<br>Do not input 2V or less.                                                                                                                  |

| 45         | VIDEO_O | 0   | 2 to 10V                    | 45<br>777 777 600μ                                                                     | Invert amplifier output.<br>Connect directly to Pin 44.<br>When using two CXA3512R in<br>parallel in XGA or UXGA mode, use<br>the invert amplifier of only one IC,<br>and connect the output to Pin 44 of<br>both ICs. |

| Pin<br>No. | Symbol        | I/O | Standard voltage level                                                                       | Equivalent circuit                                                 | Description                                                                                                                                                                                                                                                                     |

|------------|---------------|-----|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46         | VIDEO_R       | I   | 3.3V                                                                                         |                                                                    | Input the 100% white level DC of the<br>signal input to VIDEO_I.<br>When using the CXA2111R,<br>connect to the V33 output of the<br>CXA2111R. When using bipolar<br>DAC output for VIDEO_I, connect to<br>the DAC supply voltage.                                               |

| 47         | VIDEO_I       | I   | 2 to 3.3V                                                                                    | 47<br>47<br>145<br>Vcc<br>420µ<br>420µ<br>145                      | Video input.<br>Connect a gamma-corrected<br>1.5Vp-p analog video output.<br>Can be connected directly to the<br>CXA2111R video output. Connect<br>to 5V when not using the invert<br>amplifier.                                                                                |

| 49         | CAL_R         | I   | 2.7V                                                                                         | 49<br>145<br>Vcc<br>50µ<br>Vcc<br>50µ<br>145                       | Calibration level input for offset<br>cancel.<br>Input the DC level during non-<br>inverse with the most highly visible<br>gradation. Normally, approximately<br>2.5 to 3V.                                                                                                     |

| 50         | CAL_O         | 0   | 3 to 11V                                                                                     | Vcc<br>Vcc<br>100µ<br>Vcc<br>700<br>145<br>700                     | Calibration amplifier output.<br>Connect directly to Pin 51.<br>When using two CXA3512R in<br>parallel in XGA or UXGA mode, use<br>the calibration amplifier of only one<br>IC, and connect the output to Pin 51<br>of both ICs.                                                |

| 51         | CAL_I         | I   | 3 to 11V                                                                                     | 51<br>30k<br>30k<br>30k                                            | Calibration level input for offset<br>cancel.<br>Connect to CAL_O.                                                                                                                                                                                                              |

| 54<br>55   | MCLK<br>MCLKX | I   | PECL<br>differential<br>(amplitude<br>0.4V or more<br>between VDD<br>and 2V) or<br>TTL input | VDD VDD<br>54<br>55<br>140k<br>140k<br>140k<br>140k<br>155<br>100μ | Dot clock inputs.<br>PECL differential input or TTL input.<br>For TTL input, input to MCLK and<br>connect MCLKX to GND via a<br>capacitor.<br>Always input the dot clock or<br>equivalent signal to these pins even<br>when not using CLKOUT.<br>(Otherwise, noise may result.) |

| Pin<br>No.                                                            | Symbol            | I/O | Standard voltage level                   | Equivalent circuit                                                                                                                                                                    | Description                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------|-------------------|-----|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 58                                                                    | DLYCTR            | I   | 3 to 5V                                  | 58<br>10k<br>777<br>777<br>25μ                                                                                                                                                        | Dot clock phase adjustment.<br>The CLKOUT phase relative to<br>MCLK can be changed by the<br>voltage of this pin.<br>Connection to the CXA2111R<br>DLY_CNT output allows digital<br>control using the I <sup>2</sup> C register of the<br>CXA2111R. |

| 59<br>60                                                              | CLKOUT<br>CLKOUTX | 0   | Vdd – 0.3V<br>to Vdd                     | 59<br>60<br>150<br>150<br>150<br>1m<br>1m<br>1m                                                                                                                                       | Phase-adjusted dot clock outputs.                                                                                                                                                                                                                   |

| 62<br>63                                                              | CLKIN<br>CLKINX   | I   | Vdd – 0.3V<br>to Vdd                     | $\begin{array}{c} V_{DD} & V_{DD} & V_{DD} \\ \downarrow & 2k \\ \hline 62 \\ \hline 63 \\ \hline 777 \\ 145 \\ \hline 100 \mu \\ \hline 777 \\ 100 \mu \\ \hline 777 \\ \end{array}$ | Dot clock inputs for timing<br>generation.<br>Connect the CLKOUT (CLKOUTX)<br>pin.<br>When not using the CLK phase<br>adjustment function, the dot clock<br>can also be input directly to these<br>pins by PECL differential input.                 |

| 64                                                                    | F/H_CNT           | I   | High: ≥ 2.5V<br>Low: ≤ 0.8V<br>OPEN High | $\begin{array}{c} V_{DD} & V_{DD} & V_{DD} & V_{DD} \\ \hline \\ 100k \\ \hline \\ 40k \\ 12\mu \\ \hline \\ 777 \\ 12\mu \\ \hline \\ 777 \\ 12\mu \\ \hline \\ 777 \\ \end{array}$  | SHOUT output timing selection.<br>High: SHOUT 1 to 3 and SHOUT 4<br>to 6 are output at different timing.<br>Low: SHOUT 1 to 6 are output at the<br>same timing.                                                                                     |

| 23                                                                    | PGND              |     | GND                                      |                                                                                                                                                                                       | Power GND.                                                                                                                                                                                                                                          |

| 26                                                                    | PVcc              |     | 15.5V                                    |                                                                                                                                                                                       | Power Vcc.<br>Connect directly to Vcc.                                                                                                                                                                                                              |

| 42                                                                    | Vcc               |     | 15.5V                                    |                                                                                                                                                                                       | 15V power supply.                                                                                                                                                                                                                                   |

| 52                                                                    | Vdd               |     | 5V                                       |                                                                                                                                                                                       | 5V power supply.                                                                                                                                                                                                                                    |

| 53                                                                    | DGND              |     | GND                                      |                                                                                                                                                                                       | Digital GND.                                                                                                                                                                                                                                        |

| 8, 9,<br>24, 25,<br>40, 41,<br>56, 57                                 |                   |     | GND                                      |                                                                                                                                                                                       | Analog GND.                                                                                                                                                                                                                                         |

| 3, 4,<br>7, 12,<br>15, 18,<br>20, 22,<br>27, 29,<br>31, 43,<br>48, 61 | NC                |     |                                          |                                                                                                                                                                                       | No connection.<br>Not connected to anything.                                                                                                                                                                                                        |

# SONY

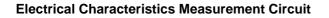

| No. | Item                                                     | Symbol | Measurement points       | Measurement contents                                                                                                                                                                                                          | Min.     | Тур. | Max. | Unit  |

|-----|----------------------------------------------------------|--------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|-------|

| 1   | VDD current consumption                                  | ldd    | Ivdd                     | IDD = IVDD                                                                                                                                                                                                                    | 20       | 28   | 42   | mA    |

| 2   | Vcc current consumption                                  | Icc    | lvcc1<br>lvcc2           | Icc = Ivcc1 + Ivcc2                                                                                                                                                                                                           | 30       | 45   | 65   | mA    |

| 3   | Input – output gain                                      | Ashout | Vshout<br>Vin            | Ashout = Vshout (AC)/Vin                                                                                                                                                                                                      | _        | 3    |      | times |

| 4   | Invert amplifier gain                                    | Ainv   | Vinv<br>Vin              | AINV = VINV (AC)/VIN                                                                                                                                                                                                          | _        | 2    |      | times |

| 5   | Invert amplifier<br>slew rate                            | SRINV  | Vinv                     | Input a square wave from VIN<br>so that the VINV output<br>amplitude is 3.0Vp-p.<br>Measure the slew rate at 10 to<br>90% of output waveform rise<br>or fall. (for inverse or non-<br>inverse)                                | _        | 700  |      | V/µs  |

| 6   | Invert amplifier<br>output band width                    | BWINV  | Vinv                     | Input 2.5V DC, 100mVp-p AC<br>from Pin 47 (VIDEO_IN) and<br>measure VINV. The frequency<br>that is –3dB to 100kHz. (for<br>inverse or non-inverse)                                                                            | _        | 90   |      | MHz   |

| 7   | Output delay<br>deviation for<br>inverse/non-<br>inverse | Tdiff  | Vinv                     | Invert amplifier delay time<br>difference for inverse and non-<br>inverse.                                                                                                                                                    | _        | 2    | 4    | ns    |

| 8   | SID output gain                                          | Asid   | Vsid<br>Vsid_in          | Asid = Vsid (AC)/Vsid_in                                                                                                                                                                                                      | —        | 4    | 4.4  | times |

| 9   | SID block output<br>slew rate                            | SRsid  | Vsid                     | Input an invert pulse to Pin 44<br>(FRP), load capacitance C7 =<br>47pF, and apply DC input<br>voltage to VsiD_IN so that VsiD<br>is 2.5V/11.5V.<br>Measure the slew rate at 10 to<br>90% of output waveform rise<br>or fall. | 30       | 50   |      | V/µs  |

| 10  | VCOM adjustable range                                    | Vсом   | Vсом                     | VCOM output voltage when<br>Pin 34 (VCOMOFF) is varied<br>from 0 to 10V.                                                                                                                                                      | Vsig – 2 | _    | Vsig | V     |

| 11  | First stage<br>SH_OUT<br>slew rate                       | SRsH1  | _                        | First stage sample-and-hold slew rate on Block Diagram.                                                                                                                                                                       | _        | 700  |      | V/µs  |

| 12  | SH_OUT<br>slew rate                                      | SRout  | Vout1 <b>to</b><br>Vout6 | Input a square wave from VIN<br>so that the Vout1 to Vout6<br>output amplitude is 3.5Vp-p.<br>Measure the slew rate at 10 to<br>90% of output waveform rise<br>or fall. (load 270pF, for inverse<br>or non-inverse)           |          | 150  |      | V/µs  |

# Electrical Characteristics (See Electrical Characteristics Measurement Circuit) $(V_{DD} = 5V, V_{CC} = 15.5V, V_{SIGCEN})$

| No. | ltem                                       | Symbol | Measurement points       | Measurement contents                                                                                                                                                                       | Min. | Тур. | Max. | Unit  |

|-----|--------------------------------------------|--------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| 13  | MCLK input<br>frequency range              | fмськ  |                          | D1OR2 = High<br>(CLKOUT = MCLK)                                                                                                                                                            | 14   | _    | 65   | MHz   |

| 14  | TG operating frequency range               | fтg    | _                        | Maximum frequency at which<br>the sample-and-hold timing<br>pulse is output properly.                                                                                                      | _    | _    | 120  | MHz   |

| 15  | VIDEO_I input<br>signal range              | Vinr   | —                        | VIDEO_I input voltage range when VIDEO_R is set to 3.3V.                                                                                                                                   | 1.5  | _    | 3.7  | V     |

| 16  | VIDEO_I input<br>signal amplitude<br>range | Vin    | _                        | Maximum signal amplitude range of VIDEO_I input signal                                                                                                                                     | _    | _    | 1.5  | V     |

| 17  | SHOUT minimum output voltage               | Vmin   | Vout1 to<br>Vout6        | Minimum voltage at which<br>sample-and-hold output<br>(SHOUT 1 to SHOUT 6) can<br>be output.                                                                                               | 1.5  | 2    |      | V     |

| 18  | SHOUT maximum output voltage               | Vmax   | Vout1 to<br>Vout6        | Maximum voltage at which<br>sample-and-hold output<br>(SHOUT 1 to SHOUT 6) can<br>be output.                                                                                               | _    | 13   | 13.5 | V     |

| 19  | Output deviation<br>between<br>channels 1  | Dout1  | Vout1 <b>to</b><br>Vout6 | Value obtained by subtracting minimum VouT1 to VouT6 value from maximum VouT1 to VouT6 value when CAL_R = $2.6V$ and VIDEO_I = $2.6V$ .                                                    | _    | 4    | 10   | mVp-p |

| 20  | Output deviation<br>between<br>channels 2  | Dout2  | Vout1 to<br>Vout6        | Value obtained by subtracting minimum Vout1 to Vout6 value from maximum Vout1 to Vout6 value when CAL_R = $2.6V$ and VIDEO_I = $3.3V$ or $1.9V$ .                                          | _    | 4    | 40   | mVp-p |

| 21  | Output deviation between ICs 1             | DIC1   | Vout1 to<br>Vout6        | Value obtained by subtracting<br>minimum Vout1 to Vout6 value<br>from maximum Vout1 to Vout6<br>value when CAL_R = $2.6V$<br>and VIDEO_I = $2.6V$ .<br>(when using two CXA3512R)           | _    | 10   | 20   | mVp-p |

| 22  | Output deviation between ICs 2             | DIC2   | Vout1 <b>to</b><br>Vout6 | Value obtained by subtracting<br>minimum VouT1 to VouT6 value<br>from maximum VouT1 to VouT6<br>value when CAL_R = $2.6V$<br>and VIDEO_I = $3.3V$ or $1.9V$ .<br>(when using two CXA3512R) |      | 10   | 60   | mVp-p |

Unless otherwise specified, pin setting conditions are as follows.

(46) VIDEO\_R = 3.3V, (47) VIDEO\_I = 2.0V, (39) SID\_IN = 2.3V, (38) SID\_R = 3.3V, (35) SIGCNT = 7.0V,

(34) VCOMOFF = 0V, (1) PRGPOL = 0V, (5) POSCTR1 = 0V, (6) POSCTR2 = 0V, (10) STATUS = 0V,

(13) D1OR2 = 5V, (14) DIRCTR = 5V, (49) CAL\_R = 2.6V, (58) DLYCTR = 4.0V, (64) F/H\_CNT = 0V,

(36) FRP = 0V, fclk32.5MHz

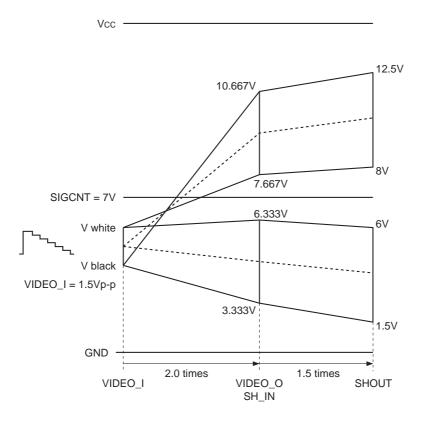

# Level Diagram

VIDEO\_I to SHOUT (SIGCNT = 7V, VIDEO\_R = input 100% white level)

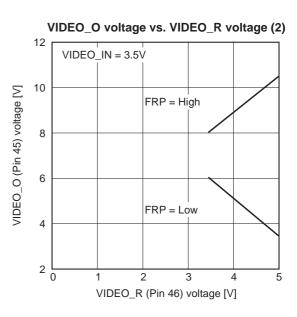

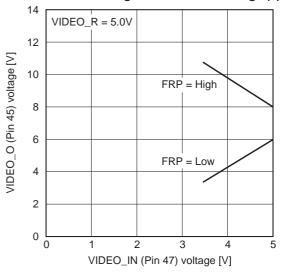

# VIDEO\_I to VIDEO\_O

The formulas for calculating the VIDEO\_I to SHOUT internal DC gain are as follows. For non-inverse:

$\begin{aligned} \text{VIDEO}_O &= 2.0 \times (\text{VIDEO}_I - \text{VIDEO}_R) + \text{SIGCNT} \times (1 - 1/10.5) \\ \text{SHOUT} &= 3.0 \times (\text{VIDEO}_I - \text{VIDEO}_R) + \text{SIGCNT} \times (1 - 1/7) \end{aligned}$

For inverse:

$VIDEO_O = -2.0 \times (VIDEO_I - VIDEO_R) + SIGCNT \times (1 + 1/10.5)$ SHOUT = -3.0 × (VIDEO\_I - VIDEO\_R) + SIGCNT × (1 + 1/7)

#### **Description of Operation**

#### **1. Invert Amplifier Block**

The CXA3512R is designed so that the optimal signal for the LCD panel is output from the SHOUT pins when a signal in the range from 1.8 to 3.3V is applied to the VIDEO\_I input. As shown in the figure above, when a  $\gamma$  corrected video signal is input to VIDEO\_I, the signal is inverse/non-inverse amplified according to the FRP input (TTL level) and output from VIDEO\_O. The DC level is determined by the VIDEO\_R input. Input a level equivalent to 100% white of input. Also, when not using the invert amplifier, connect VIDEO\_I to 5V.

# 2. Analog Demultiplexer Block

The SH\_IN analog input signal is converted from a time series signal to a 6-channel (or 12-channel) cyclic parallel signal by the sample-and-hold group which is appropriately controlled by the on-chip timing generator. These signals pass through a fixed-gain (= 1.5 times) buffer amplifier and are output to SHOUT. These outputs can directly drive the input load of the LCD panel.

When using a SVGA panel, connect the (6-channel output) VIDEO\_O output directly to the adjacent SH\_IN. XGA panels use 12-channel output, so short the SH\_IN of two CXA3512R and connect them to the VIDEO\_O output of one of the IC. The on-chip TG recognizes master/slave by the low/high STATUS (Pin 10) input. For forward scan, the output alternates between the ICs in the order of master SHOUT1  $\rightarrow$  slave SHOUT1  $\rightarrow$  master SHOUT2  $\rightarrow$  slave SHOUT2  $\rightarrow$  master SHOUT3 and so on. Connect the wiring to the LCD panel inputs in this order.

The sample-and-hold pulse generation timing is shown on the following pages. These pulses are not output and are used only inside the IC.

# 3. Timing Generator (TG) Block

The on-chip TG operates by one pair of differential clock inputs (CLK\_IN, CLK\_INX) and two horizontal sync signal inputs (PRG, ENB), and generates the timing pulses needed by the demultiplexer block and the output deviation cancel circuit. The various operation modes can be designated by the pin voltage settings.

# • Input timing signal conditions

Maintain the ENB, PRG and FRP phase relationship shown in the timing chart above, with the CLK\_IN input sync as 1 clk. In particular, when FRP changes between high and low, be sure to input ENB and PRG as shown above. Otherwise, the IC may suffer irrecoverable deterioration in the worst case.

# Operation mode setting

Table B.

|        | SVGA (6-channel mode)  | XGA/UXGA (12-channel/24-channel mode |       |  |  |

|--------|------------------------|--------------------------------------|-------|--|--|

|        | SXGA (12-channel mode) | Master                               | Slave |  |  |

| STATUS | H/L*1                  | L                                    | Н     |  |  |

| D1OR2  | L                      | Н                                    | Н     |  |  |

\*1 The output phase can be shifted by 1/2-dot clock in SVGA/SXGA mode by changing STATUS.

# Scan direction setting

The output scan direction can be changed by the DIRCTR (Pin 14) input.

| Pin 14 | Direction | Scan order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| н      | Forward   | $SHOUT1 \rightarrow SHOUT2 \rightarrow SHOUT3 \rightarrow SHOUT4 \rightarrow SHOUT5 \rightarrow SHOUT6 \rightarrow SHOUT1 \rightarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| L      | Reverse   | $SHOUT6 \rightarrow SHOUT5 \rightarrow SHOUT4 \rightarrow SHOUT3 \rightarrow SHOUT2 \rightarrow SHOUT1 \rightarrow SHOUT6 \rightarrow SHOUC6 \rightarrow SH$ |

The scan direction can be changed by the Pin 14 setting without changing other connections even when using two CXA3512R such as in XGA mode.

# Output phase setting

The phase of each SHOUT output relative to the analog input can be adjusted in CLK\_IN clock units by the Pins 5 and 6 input levels.

Each input pin has 4 setting values, for a total of 16 settings.

POSCTR1 is the lower bits setting, POSCTR2 is the upper bits setting, and the setting values are as shown in Table A-1.

| Setting value | Threshold     |

|---------------|---------------|

| 0             | to 0.75V      |

| 1             | 1.15 to 1.50V |

| 2             | 1.70 to 2.55V |

| 3             | 2.95V to      |

| Table A-1. Setting Voltage Range |  |

|----------------------------------|--|

| for Output Phase                 |  |

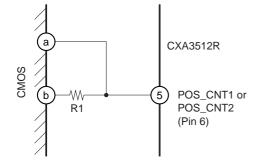

| Table A-2. CMOS Logic Connection Settin | g |

|-----------------------------------------|---|

| Value and CMOS Output Pins              |   |

| Setting value | а    | b |

|---------------|------|---|

| 0             | L    | L |

| 1             | Hi-Z | L |

| 2             | Hi-Z | Н |

| 3             | Н    | Н |

There are two ways to use these pins.

A. Connect directly to the CXA2111R

Connect to the corresponding CXA2111R pins POS\_CNT1 and POS\_CNT2. This allows bit setting via the CXA2111R I<sup>2</sup>C bus.

B. Connect to CMOS logic

Connect CMOS logic as shown in the figure. This allows digital control by tri-state control of Pin a. See Table A-2.

R1 is a threshold setting resistor that provides the voltage for setting values 1 and 2. The appropriate resistance value changes depending on the number of CXA3512R driven by one CMOS logic (1-channel or 3-channel RGB drive, or one CXA3512R (6-outputs/ch) or two CXA3512R (12-outputs/ch)). Recommended resistance values are given in Table A-3.

# **CMOS Logic Connection**

# CXA3512R Usage and Threshold Setting Resistor R1

# Table A-3.

|          | RGB 1-channel drive |            | RGB 3-cha | annel drive |

|----------|---------------------|------------|-----------|-------------|

|          | 6 outputs           | 12 outputs | 6 outputs | 12 outputs  |

| R1 value | 250kΩ               | 150kΩ      | 100kΩ     | 47kΩ        |

CMOS supply voltage = 3.3 to 5V

# 4. Dot Clock Phase Adjustment Block

The CXA3512R has a function for adjusting the phase between the analog video input and the dot clock input to achieve stable reproduction of high definition images. Images with no jitter and flicker can be reproduced by optimizing the setting.

The 1/2-dot clock input to MCLK and MCLKX (PECL level) is input to the phase comparator of the on-chip PLL clock generator. The output from CLKOUT and CLKOUTX becomes the internal VCO output. CLKOUT is the same frequency as MCLK when the D10R2 (Pin 13) input is high, and twice the MCLK frequency when the D10R2 input is low.

A large amplitude logic with a threshold value of 1.5V can also be connected directly to MCLK instead of PECL. In this case, connect MCLKX to GND via a capacitor of approximately 100pF. (PECL level input is recommended when the MCLK input is used around 50MHz.)

The CLKOUT phase can be adjusted up to  $\pm 180^{\circ}$  according to the DC level (3 to 5V) of the DLYCTR (Pin 58) input.

By connecting CLKOUT to the TG clock input, the analog video signal and first stage sample-and-hold phases can be finely adjusted using the DLYCTR DC level.

When using two CXA3512R in XGA mode, input the CLKOUT of one CXA3512R to the CLKIN of both in order to match the timing of both ICs. In this case, input the same clock to MLCK of both ICs.

# 5. Calibration Amplifier Block

The CXA3512R generates the deviation cancel circuit reference with a calibration amplifier in order to minimize the deviation between channels at the highest visibility level.

Input DC level equivalent to approximately 50% gray at VIDEO\_I to CAL\_R (Pin 49). In addition, directly connect the CAL\_O (Pin 50) output to the adjacent CAL\_I.

When using two CXA3512R in XGA mode, connect the CAL\_O of one IC to the CAL\_I of both ICs, and connect the unused CAL\_R to 5V.

# 6. SID Block

This block generates the precharge signal used by the LCD panel.

The signal input to SID\_IN (Pin 39) is folded at the SIGCNT potential by FRP in the same manner as the invert amplifier, and output to SID\_O (Pin 37). The gain is designed at approximately 4 times. The DC level is determined by SID\_R, and is normally approximately 3.3V.

SID\_O cannot directly drive the precharge signal input of the LCD panel. Therefore, connect SID\_O via a buffer having sufficient current supply capability.

SID\_O DC calculation formula

Pin 36: low = non-inverse  $SID_O = 4 \times (SID_IN - SID_R) + 6/7 (SIGCNT)$ Pin 36: high = inverse  $SID_O = 4 \times (SID_R - SID_IN) + 8/7 (SIGCNT)$

# 7. VCOM Block

This block sets the DC potential of the VCOM level.

The VCOMOFF (Pin 34) potential sets the deviation relative to the SIGCNT potential as follows.

VCOMOFF = 0V: VCOMOUT = SIGCNT VCOMOFF = 10V: VCOMOUT = SIGCNT - 3V

# Combination with the CXA2111R

Used together with the CXA2111R, the CXA3512R can achieve most of the analog signal processing ( $\gamma$  correction, precharge waveform generation) required by LCD panels.

In addition, I<sup>2</sup>C serial control of the following functions is possible using the I<sup>2</sup>C-controlled registers built into the CXA2111R.

- Output phase adjustment (POSCTR1, 2)

- Clock phase adjustment (DLYCTR)

- Scan direction (DIRCTR)

Connect the pins as shown in the table below to use the various functions. For details, see the CXA2111R specifications.

|                    | CXA2111R                             | CXA3512R                   |

|--------------------|--------------------------------------|----------------------------|

| Video signal       | ROUT (18), GOUT (16) or<br>BOUT (14) | VIDE_IN (47)               |

| Precharge waveform | SIDOUT (6)                           | SID_IN (39)                |

|                    | POS_CNT (1)                          | POSCTR1 (5)                |