## SONY

# CXA3562AR

## **LCD** Driver

#### Description

The CXA3562AR is a driver IC developed for use with Sony polycrystalline silicon TFT LCD panels. It supports digital 2-parallel and single input, and the input data is analog demultiplexed into 12 phases and output. The CXA3562AR can directly drive an LCD panel, and the VCOM setting circuit and precharge pulse waveform generator are also on-chip.

#### **Features**

- Supports 10-bit 2-parallel and single input

- Supports signals up to UXGA (1/2 clock when using UXGA signals)

- Low output deviation by on-chip output offset cancel circuit

- Supports both line inversion and dot and line inversion

- On-chip timing generator with ECL

- VCOM voltage generation circuit

- Precharge pulse waveform generation circuit

## **Applications**

LCD projectors and other video equipment

## **Absolute Maximum Ratings** (Vss = 0V)

| <ul> <li>Supply voltage</li> </ul>        | Vcc      | 16          | V  |  |

|-------------------------------------------|----------|-------------|----|--|

|                                           | $V_{DD}$ | 5.5         | V  |  |

| <ul> <li>Operating temperature</li> </ul> | Topr     | -20 to +70  | °C |  |

| Storage temperature                       | Tstg     | -65 to +150 | °C |  |

| Allowable power dissipation               | Po       | 2000        | mW |  |

## Recommended Operating Conditions

| <ul> <li>Supply voltage</li> </ul>        | Vcc      | 15.0 to 15.5 | V  |

|-------------------------------------------|----------|--------------|----|

|                                           | $V_{DD}$ | 4.75 to 5.25 | V  |

| <ul> <li>Operating temperature</li> </ul> | Topr     | -20 to +70   | °C |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

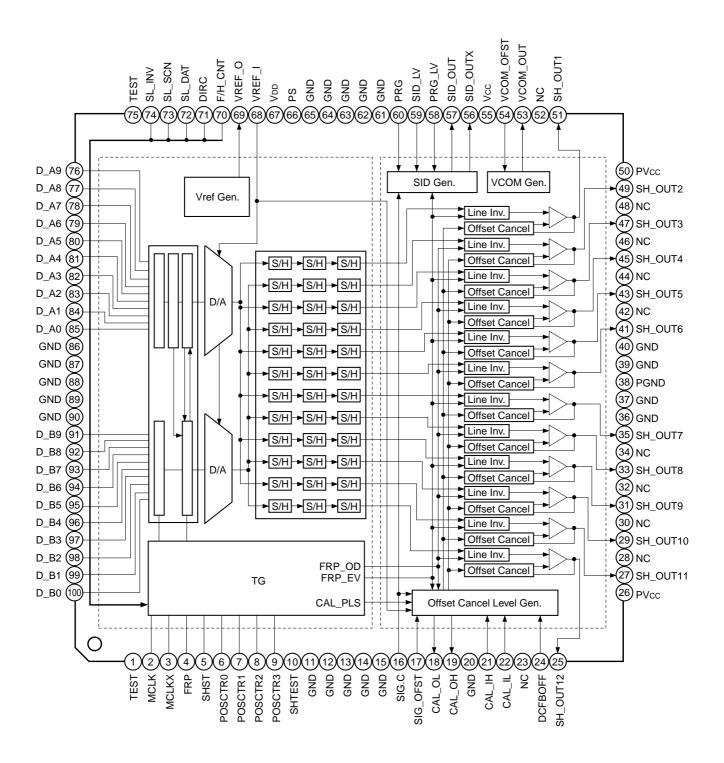

#### **Block Diagram and Pin Configuration**

## **Pin Description**

| Pin<br>No.       | Symbol                                   | I/O | Standard voltage level                                                                      | Equivalent circuit   | Description                                                                                                                                                                                                  |

|------------------|------------------------------------------|-----|---------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 3              | MCLK<br>MCLKX                            | I   | PECL<br>differential<br>(amplitude<br>0.4V or more<br>between<br>VDD to 2V)<br>or TTL input | VDD                  | Dot clock input. PECL differential input or TTL input. For TTL input, input to MCLK and connect MCLKX to GND through a capacitor.                                                                            |

| 4                | FRP                                      | I   | High: ≥2.0V<br>Low: ≤0.8V                                                                   | VDD \$50k            | LCD panel AC drive inversion timing input. High: inverted Low: non-inverted See the Timing Chart.                                                                                                            |

| 5                | SHST                                     | I   | High: ≥2.0V<br>Low: ≤0.8V                                                                   | 50k<br>5 192<br>6ND  | Internal sample-and-hold timing circuit reset pulse input. This pin is also used as the offset cancel level insertion timing input. A reset is applied to the internal timing generator at the falling edge. |

| 6<br>7<br>8<br>9 | POSCTR0<br>POSCTR1<br>POSCTR2<br>POSCTR3 | I   | High: ≥2.0V<br>Low: ≤0.8V                                                                   | VDD                  | Output phase adjustment. The output phase is adjusted in MCLK period units when SL_DAT (Pin 72) is high, and in 1/2 MCLK period units when SL_DAT is low.                                                    |

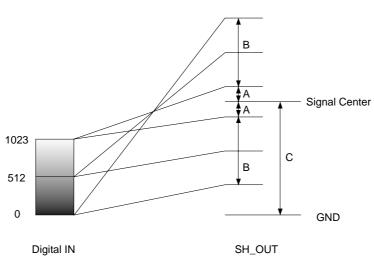

| 16               | SIG.C                                    | I   | 1 to 5.0V                                                                                   | VDD VCC 20µ  30k GND | Signal center voltage (inversion folded voltage) adjustment input. The SH_OUT output center voltage can be adjusted in the range from 7.0 to 8.0V.                                                           |

| 17               | SIG_OFST                                 | I   | 0 to 5.0V                                                                                   | VDD VCC 10μ SQND     | Output signal offset adjustment from signal center voltage. The SH_OUT output 100% white level (at 3FF input) voltage can be adjusted in the range from 0 to 1V from the center voltage.                     |

| Pin<br>No.                                                    | Symbol                    | I/O | Standard voltage level      | Equivalent circuit                          | Description                                                                                                                                                                                                                     |

|---------------------------------------------------------------|---------------------------|-----|-----------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18<br>19                                                      | CAL_OL<br>CAL_OH          | 0   | 3.0 to 6.0V<br>9.0 to 12.0V | Vcc 40µ \$1k 145 18 (19) GND                | Level output for canceling the offset between channels. Connect directly to CAL_IL and CAL_IH, respectively.                                                                                                                    |

| 21<br>22                                                      | CAL_IH<br>CAL_IL          | 0   | 9.0 to 12.0V<br>3.0 to 6.0V | Vcc                                         | Level input for canceling the offset between channels. Connect directly to CAL_OL and CAL_OH, respectively. When using two CXA3562R, connect the CAL_IL and CAL_IH of both chips to the CAL_OL and CAL_OH of only one CXA3562R. |

| 24                                                            | DCFBOFF                   | I   | GND                         | VDD                                         | Offset cancel function off. Normally connect to GND to use with the offset cancel function on. High (offset cancel function off) when open.                                                                                     |

| 25, 27,<br>29, 31,<br>33, 35,<br>41, 43,<br>45, 47,<br>49, 51 | SH_OUT12<br>to<br>SH_OUT1 | 0   | 1.5 to 13.5V                | 300<br>300<br>33335<br>4143<br>4547<br>4951 | Demultiplexed output of AC inverse driven video signals. Can be connected directly to the LCD panel.                                                                                                                            |

| 53                                                            | VCOM_OUT                  | 0   | 5.0 to 8.0V                 | Vcc 80µ 500 145 63                          | LCD panel common voltage output. Can be set in the range from the SH_OUT center potential Vsig.c to Vsig.c – 2V by VCOM_OFST.                                                                                                   |

| 54                                                            | VCOM_OFST                 | I   | 0 to 5.0V                   | VDD VCC<br>80μ<br>54 × 100<br>GND           | LCD panel common voltage adjustment. VCOM_OUT can be set in the range from the SH_OUT center potential Vsig.c to Vsig.c – 2V by inputting 0 to 5V.                                                                              |

| Pin<br>No. | Symbol              | I/O | Standard voltage level                 | Equivalent circuit                        | Description                                                                                                                                                                                                 |

|------------|---------------------|-----|----------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56<br>57   | SID_OUTX<br>SID_OUT | 0   | 1.5 to 13.5V                           | Vcc 100k 145 56 57 GND 6ND                | Precharge waveform output. SID_OUTX outputs the inverse of SID_OUT based on the output center voltage. These pins cannot directly drive the LCD panel, so input to the LCD panel with an external a buffer. |

| 58<br>59   | PRG_LV<br>SID_LV    | I   | 1.0 to 5.0V                            | VDD                                       | Precharge level setting. Adjusts the SID_OUT and SID_OUTX output potential. PRG_LV is reflected when the PRG input pin (Pin 60) is high, and SID_LV is reflected when PRG is low.                           |

| 60         | PRG                 | I   | High: ≥2.0V<br>Low: ≤0.8V              | V <sub>DD</sub> Vcc \$100k 10k 50μ GND    | Timing pulse input for switching the Pins 56 and 57 output levels. (See PRG_LV (Pin 58) and SID_LV (Pin 59).)                                                                                               |

| 68         | VREF_I              | I   | 3.2V                                   | 70µ 10µ 10µ 10µ 10µ 10µ 10µ 10µ 10µ 10µ 1 | Internal D/A converter reference voltage input. Normally connect directly to VREF_O.                                                                                                                        |

| 69         | VREF_O              | 0   | 3.2V                                   | VDD                                       | Reference voltage output. Normally connect directly to VREF_I, and connect to GND through a 0.5 to 1.0µF capacitor.                                                                                         |

| 70         | F/H_CNT             | I   | High: ≥2.0V<br>Low: ≤0.8V<br>Open: Low | VDD \$50k<br>192<br>70 W \$200k<br>GND    | SH_OUT output timing selection. High: SH_OUT1 to SH_OUT6 and SH_OUT7 to SH_OUT12 are output at different timing. Low: SH_OUT1 to SH_OUT12 are output at the same timing.                                    |

| Pin<br>No.                                                      | Symbol | I/O | Standard voltage level    | Equivalent circuit                                | Description                                                                                                                                                       |

|-----------------------------------------------------------------|--------|-----|---------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66                                                              | PS     | ı   | 5V                        | VDD<br>70k<br>66 W 30μ<br>GND                     | Test. Normally connect to VDD.                                                                                                                                    |

| 38                                                              | PGND   |     | GND                       |                                                   | Power GND.                                                                                                                                                        |

| 26, 50                                                          | PVcc   |     | 15.5V                     |                                                   | Power Vcc.                                                                                                                                                        |

| 55                                                              | Vcc    |     | 15.5V                     |                                                   | 15V power supply.                                                                                                                                                 |

| 67                                                              | VDD    |     | 5V                        |                                                   | 5V power supply.                                                                                                                                                  |

| 11 to 15,<br>20, 36,<br>37, 39,<br>40,<br>61 to 65,<br>86 to 90 | GND    |     | GND                       |                                                   | GND.                                                                                                                                                              |

| 23, 28,<br>30, 32,<br>34, 42,<br>44, 46,<br>48, 52              | NC     |     |                           |                                                   |                                                                                                                                                                   |

| 1, 75                                                           | TEST   | 0   | 1.7 to 3.2V               | VDD<br>1μ \$2k<br>192<br>W 175<br>GND             | DAC output monitor test. Normally connect to VDD.                                                                                                                 |

| 10                                                              | SHTEST | I   | 2.5V                      | VDD 20k ≥ 20k | Test.<br>Leave open.                                                                                                                                              |

| 71                                                              | DIRC   | I   | High: ≥2.0V<br>Low: ≤0.8V | VDD \$50k                                         | Scan direction setting. High: output as a time series in ascending order of output pin symbol (in order from SH_OUT1 to SH_OUT12) Low: output in descending order |

| Pin<br>No.      | Symbol             | I/O | Standard voltage level                  | Equivalent circuit                  | Description                                                                                                                                                                                               |

|-----------------|--------------------|-----|-----------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 72              | SL_DAT             | ı   | High: ≥2.0V<br>Low: ≤0.8V<br>Open: Low  | VDD \$50k  192 W \$200k  GND        | Digital input mode switch setting. High: single input from the A port Low: parallel input from both the A and B ports                                                                                     |

| 73              | SL_SCN             | ı   | High: ≥2.0V<br>Low: ≤0.8V<br>Open: High | VDD                                 | A and B port input switching interlocked/non-interlocked setting relative to scan direction setting during parallel input. High: A and B port switching interlocked to DIRC Low: fixed regardless of DIRC |

| 74              | SL_INV             | ı   | High: ≥2.0V<br>Low: ≤0.8V<br>Open: Low  | VDD \$50k<br>192<br>W \$200k<br>GND | SH_OUT odd-numbered and even-numbered output polarity inverted/non-inverted setting. High: odd-numbered and even-numbered outputs inverted Low: non-inverted                                              |

| 76<br>to<br>85  | D_A9<br>to<br>D_A0 | 1   | High: ≥2.0V<br>Low: ≤0.8V               | VDD                                 | A port digital data input.                                                                                                                                                                                |

| 91<br>to<br>100 | D_B9<br>to<br>D_B0 | ı   | High: ≥2.0V<br>Low: ≤0.8V               | 91) to (100) 192<br>GND             | B port digital data input.                                                                                                                                                                                |

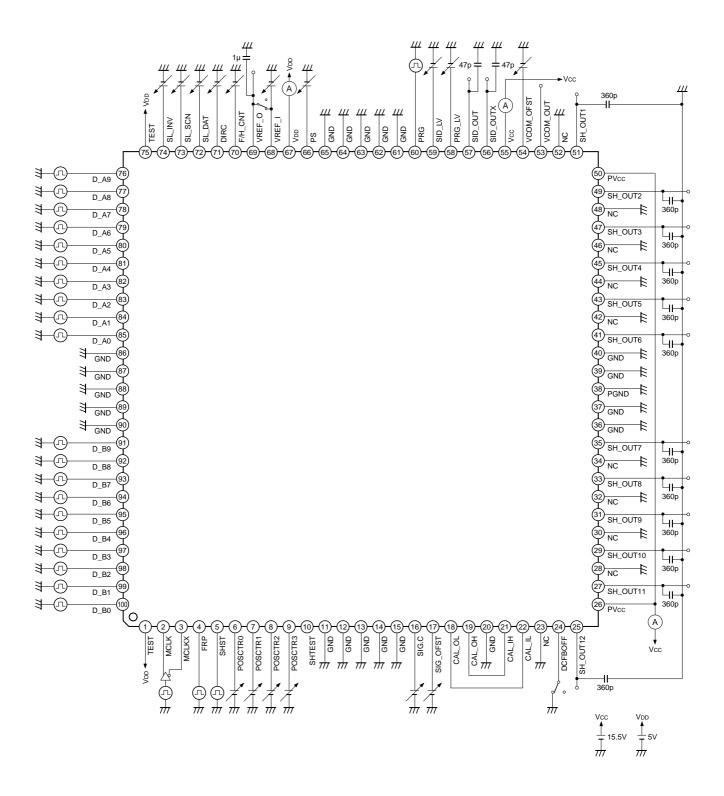

#### **Electrical Characteristics Measurement Circuit**

## **Electrical Characteristics**

| No. | Item                                | Symbol     | Measurement points | Measurement conditions                                                                                                                                         | Min. | Тур. | Max. | Unit     |

|-----|-------------------------------------|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| 1   | Digital input resolution            | n          |                    |                                                                                                                                                                | _    | 10   | _    | bit      |

| 2   | Digital input setup time            | Ts         |                    | SHST, D_A[9:0] and D_B[9:0] minimum setup time relative to MCLK input. (PELL)                                                                                  | 2    | _    | _    | ns       |

| 3   | Digital input hold time             | Тн         |                    | SHST, D_A[9:0] and D_B[9:0] minimum hold time relative to MCLK input. (PECL)                                                                                   | 3    | _    | _    | ns       |

| 4   | MCLK input frequency range 1        | fmcLK1     |                    | SL_DAT: 5V; maximum frequency at which the internal timing generator and D/A converter operate normally.                                                       | 30   | _    | 80   | MHz      |

| 5   | MCLK input frequency range 2        | fmcLK2     |                    | SL_DAT: 0V; maximum frequency at which the internal timing generator and D/A converter operate normally.                                                       | 60   |      | 100  | MHz      |

| 6   | VREF_O output voltage range         | Vvref_0    |                    | Measure the VREF_O (Pin 69) voltage.                                                                                                                           | 3.10 | 3.20 | 3.32 | ٧        |

| 7   | SH_OUT amplitude 1                  | VSHOUT1p-p | Vout1              | Measure the SH_OUT1 voltage difference at D_A[9:0]: 000h and 3FFh.                                                                                             | 4.44 | 4.50 | 4.83 | V        |

| 8   | SH_OUT amplitude 2                  | VSHOUT2p-p | Vout2              | Measure the SH_OUT2 voltage difference at D_B[9:0]: 000h and 3FFh.                                                                                             | 4.44 | 4.50 | 4.83 | V        |

| 9   | SH_OUT<br>minimum<br>amplitude      | Voutminp-p | Vout1              | Lower the VREF_I voltage and adjust the amplitude; minimum amplitude at which SH_OUT1 can be output at D_B[9:0]: 000h and 3FFh.                                | 4    | _    | _    | <b>V</b> |

| 10  | SH_OUT<br>slew rate                 | SRout      | Vout1 to<br>Vout12 | Load capacitance = 360pF; measure slew rate at 10 to 90% of output waveform rise and fall when D_A[9:0] is varied from 000h to 3FFh and from 3FFh to 000h.     | 160  | 300  | _    | V/µs     |

| 11  | SH_OUT<br>minimum<br>output voltage | Vmin       | Vout1 to<br>Vout12 | Minimum voltage at which sample-<br>and-hold outputs Vout1 to Vout12 can<br>be output.                                                                         | 1.5  | _    | _    | V        |

| 12  | SH_OUT<br>maximum<br>output voltage | VMAX       | Vout1 to<br>Vout12 | Maximum voltage at which sample-<br>and-hold outputs Vout1 to Vout12 can<br>be output.                                                                         | _    | _    | 13.6 | V        |

| 13  | Output deviation between channels 1 | Dout1      | Vout1 to<br>Vout12 | Value obtained by subtracting minimum Vout1 to Vout12 value from maximum Vout1 to Vout12 value at D_A[9:0]: 200h and D_B[9:0]: 200h.                           |      | 3    | 10   | mVp-p    |

| 14  | Output deviation between channels 2 | Dout2      | Vout1 to<br>Vout12 | Value obtained by subtracting minimum Vout1 to Vout12 value from maximum Vout1 to Vout12 value at D_A[9:0]: 000h or 3FFh and D_B[9:0]: 000h or 3FFh.           | _    | 10   | 40   | mVp-p    |

| 15  | Output deviation between ICs 1      | Dic1       | Vout1 to<br>Vout12 | Value obtained by subtracting minimum Vout1 to Vout12 value from maximum Vout1 to Vout12 value at D_A[9:0]: 200h and D_B[9:0]: 200h. (when using two CXA3562R) | _    | 10   | _    | mVp-p    |

| No. | Item                                     | Symbol   | Measurement points       | Measurement conditions                                                                                                                                                                                                | Min.        | Тур. | Max. | Unit  |

|-----|------------------------------------------|----------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|------|-------|

| 16  | Output deviation between ICs 2           | DIC2     | Vout1 to                 | Value obtained by subtracting minimum Vout1 to Vout12 value from maximum Vout1 to Vout12 value at D_A[9:0]: 000h or 3FFh and D_B[9:0]: 000h or 3FFh. (when using two CXA3562R)                                        | _           | 20   | _    | mVp-p |

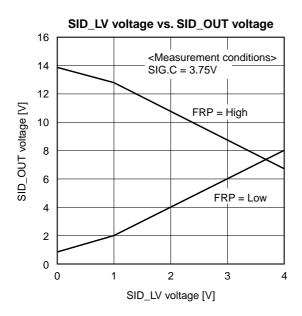

| 17  | SID output<br>gain 1                     | Asid1    | VSID_LV<br>VSID<br>VSIDX | PRG: 0V; measure Vsid_Lv and Vsid at FRP: 0V, and Vsid_Lv and Vsidx at FRP: 5V. Calculate as Asid1 = Vsid(x)/Vsid_Lv.                                                                                                 | 1.9         | 2.0  | 2.1  | times |

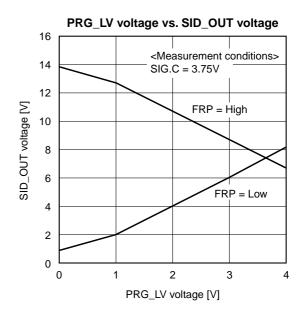

| 18  | SID output<br>gain 2                     | ASID2    | VPRG_LV<br>VSID<br>VSIDX | PRG: 5V; measure VPRG_LV and VSID at FRP: 0V, and VPRG_LV and VSIDX at FRP: 5V. Calculate as ASID2 = VSID(X)/VPRG_LV.                                                                                                 | 1.9         | 2.0  | 2.1  | times |

| 19  | SID output<br>slew rate                  | SRsid    | Vsid<br>Vsidx            | Load capacitance = 47pF, PRG: 0V; input a repeating high/low pulse to FRP (Pin 4), and apply DC input voltage so that VSID and VSIDX are 2.5V/11.5V. Measure slew rate at 10 to 90% of output waveform rise and fall. |             | 50   | _    | V/µs  |

| 20  | Signal center adjustable range           | Vsig     | Vout1                    | Vout center voltage when SIG.C (Pin 16) is varied from 1 to 5V.                                                                                                                                                       |             |      | 8    | V     |

| 21  | SH_OUT offset adjustable range           | Vsigofst | Vout1                    | D_A[9:0]: 3FFh, FRP: 0V, D_B[9:0]: 3FFh; value obtained by subtracting Vout1 from Vout1 center voltage when SIG_OFST (Pin 17) is varied from 1 to 5V.                                                                 | 0           | _    | 1    | V     |

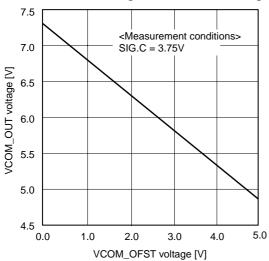

| 22  | VCOM adjustable range                    | Vсом     | Vсом                     | VCOM_OUT voltage when VCOM_OFST (Pin 54) is varied from 0 to 5V.                                                                                                                                                      | Vc –<br>2.5 | _    | Vc   | V     |

| 23  | V <sub>DD</sub> current consumption      | IDD      | Ivdd                     | IDD = IVDD                                                                                                                                                                                                            | 59          | 85   | 112  | mA    |

| 24  | Vcc current consumption                  | Icc      | Ivcc1<br>Ivcc2           | Icc = Ivcc1 + Ivcc2<br>(no digital data input)                                                                                                                                                                        | 21          | 40   | 59   | mA    |

| 25  | Current consumption in power saving mode | IPS      | IVDD<br>IVCC1<br>IVCC2   | GND (Pin 66),<br>Icc = Ivdd + Ivcc1 + Ivcc2                                                                                                                                                                           | 31          | 47   | 65   | mA    |

| 26  | Differential linearity error             | DLE      |                          | VVREF_I = 3.2V                                                                                                                                                                                                        | -0.7        |      | 0.7  | LSB   |

| 27  | Integral linearity error                 | ILE      | _                        | VVREF_I = 3.2V                                                                                                                                                                                                        | -1.2        |      | 1.2  | LSB   |

SONY

CXA3562AR

#### **Description of Operation**

The flow of internal operations is described below.

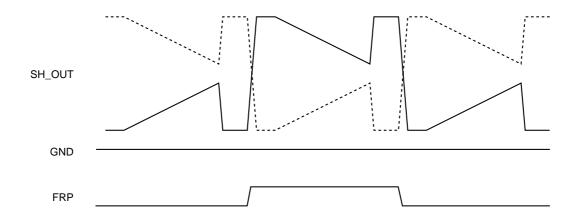

The digital signals input to D\_A9 to D\_A0 and D\_B9 to D\_B0 are internally D/A converted into approximately 1.5V (at VREF\_I: 3.2V) analog signals. After that, the signal that has been demultiplexed into 12 phases is amplified by a factor of three times, inverted at the signal center potential according to FRP, and output.

Vcc

The output level relative to the digital input changes according to the following settings.

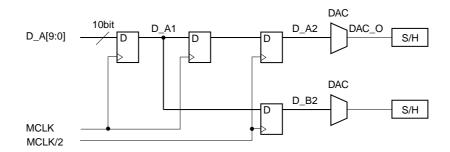

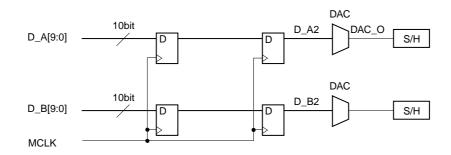

#### 1. Digital input block

The CXA3562AR can be set to single input from only the A port or parallel input from both the A and B ports, and port switching by right/left inversion is also possible in parallel input mode. This makes it possible to support various systems.

In single input mode, the signal is internally demultiplexed to 2-parallel format and input to the D/A converter.

#### 2. D/A converter block

The internal D/A converter has two systems for odd-numbered and even-numbered outputs. The voltage input from VREF\_I becomes the 100% white level potential of the analog converted signal, and this amplitude is a maximum 1.5Vp-p with respect to input data of 000h to 3FFh.

## 3. Sample-and-hold (S/H) block

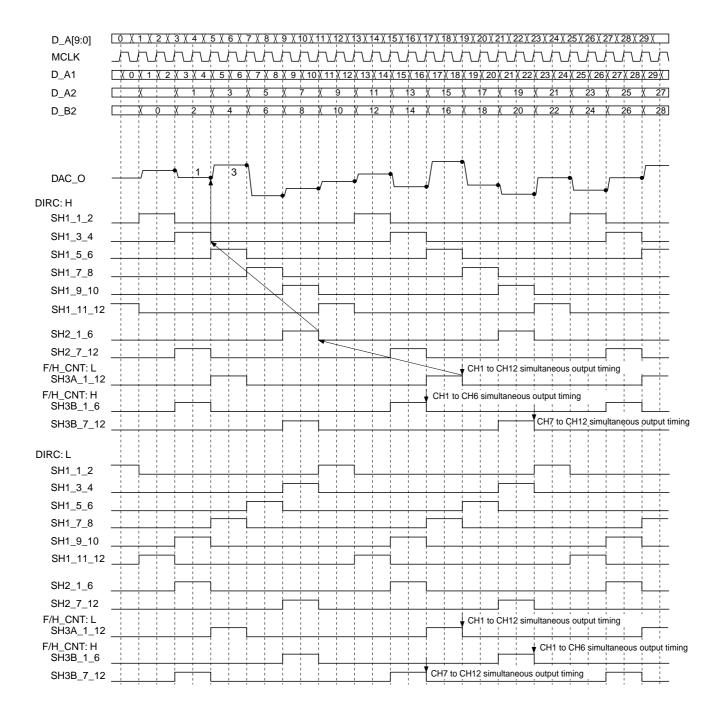

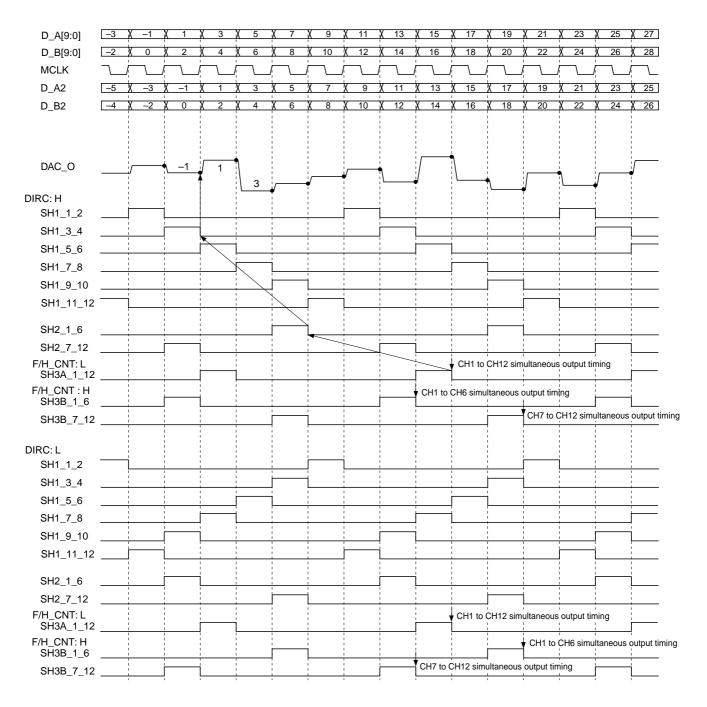

The odd-numbered and even-numbered D/A converter outputs are input to the odd-numbered and even-numbered sample-and-hold blocks, respectively. The signals are converted from time series signals into 6-phase cyclic parallel signals by the sample-and-hold group which is appropriately controlled by the internal timing generator. For forward scan, the signals are output in the ascending order of SH\_OUT1, SH\_OUT2, SH\_OUT3 ... SH\_OUT12. For reverse scan, this order is inverted and the signals are output in descending order. Connect the signals to the LCD panel according to the order used. The timing of each sample-and-hold pulse is shown on the following pages. These pulses are not output and are used only inside the IC.

## Single input mode

#### 2-parallel input mode

#### 4. Timing generator (TG) block

The internal timing generator operates by one pair of differential clock inputs (MCLK, MCLKX) and a horizontal sync signal input (SHST), and generates the timing pulses needed by the demultiplexer block, dot inversion control pulse and output deviation cancel circuit. The various operating modes can be designated by the pin settings.

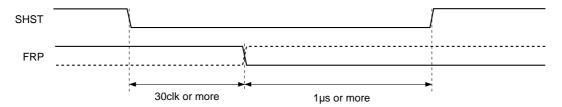

The SHST and FRP inputs should satisfy the relationship shown in the figure below with the MCLK and MCLKX input period as 1clk.

The CXA3562AR can select various operating modes according to the timing generator block settings. These settings are described below.

#### SL DAT (Pin 72)

Digital input selection. Single input from only the A port is selected when set to high level, and parallel input from both the A and B ports is selected when set to low level. When inputting a 2-parallel processed digital video signal in parallel input mode, input the earlier time series data to the A port and the later time series data to the B port. Input a master clock having the same period as the input data rate to MCLK in both modes. This pin is low level (2-parallel input mode) when left open.

### • DIRC (Pin 71), SL\_SCN (Pin 73)

Scan direction settings. Output is ascending order when DIRC is set to high level, and inverted to descending order (SH\_OUT1 to SH\_OUT12) when set to low level. At this time if SL\_SCN is set to high, the A and B port data can be switched by switching DIRC between high and low. When SL\_SCN is set to low, the A port data is output from the odd-numbered SH\_OUT and the B port data is output from the even-numbered SH\_OUT regardless of the DIRC setting.

Set SL\_SCN to high when SL\_DAT is high.

| D_A[9:0] | $\rangle$ | ( A1 | X A2 | X A3 | X A4 | ( A5 )   | ( A6 )   |   |

|----------|-----------|------|------|------|------|----------|----------|---|

| D B[9:0] |           | / R1 | Y B2 | Y B3 | X B4 | X B5 X   | / B6 \   | , |

| D[3.0]   | /         | \    | Λ υζ | V D2 | V D4 | <u> </u> | <u> </u> |   |

|           | DIRC: L                                                                                                                                                                      | DIRC: H                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SL_SCN: L | SH_OUT1: A6, SH_OUT2: B6,<br>SH_OUT3: A5, SH_OUT4: B5,<br>SH_OUT5: A4, SH_OUT6: B4,<br>SH_OUT7: A3, SH_OUT8: B3,<br>SH_OUT9: A2, SH_OUT10: B2,<br>SH_OUT11: A1, SH_OUT12: B1 | SH_OUT1: A1, SH_OUT2: B1,<br>SH_OUT3: A2, SH_OUT4: B2,<br>SH_OUT5: A3, SH_OUT6: B3,<br>SH_OUT7: A4, SH_OUT8: B4,<br>SH_OUT9: A5, SH_OUT10: B5,<br>SH_OUT11: A6, SH_OUT12: B6 |

| SL_SCN: H | SH_OUT1: B6, SH_OUT2: A6,<br>SH_OUT3: B5, SH_OUT4: A5,<br>SH_OUT5: B4, SH_OUT6: A4,<br>SH_OUT7: B3, SH_OUT8: A3,<br>SH_OUT9: B2, SH_OUT10: A2,<br>SH_OUT11: B1, SH_OUT12: A1 | SH_OUT1: A1, SH_OUT2: B1,<br>SH_OUT3: A2, SH_OUT4: B2,<br>SH_OUT5: A3, SH_OUT6: B3,<br>SH_OUT7: A4, SH_OUT8: B4,<br>SH_OUT9: A5, SH_OUT10: B5,<br>SH_OUT11: A6, SH_OUT12: B6 |

#### • SL\_INV (Pin 74)

Dot inversion and line inversion selection. When set to low level, all SH\_OUT channels are output at the same polarity as shown by the solid line in the figure below. When set to high level, the odd-numbered and even-numbered SH\_OUT outputs are output at inverse polarities. At this time the odd-numbered outputs are inverted when the FRP pulse is high, and non-inverted when the FRP pulse is low. Conversely, the even-numbered outputs are inverted when the FRP pulse is low, and non-inverted when the FRP pulse is high.

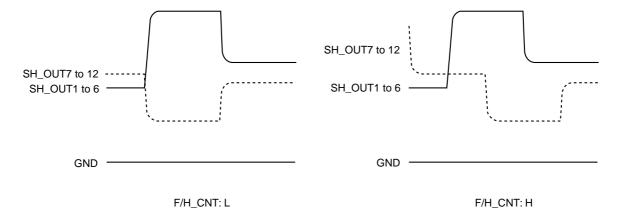

#### • F/H\_CNT (Pin 70)

SH\_OUT output timing phase setting. When set to low level, all SH\_OUT outputs are output at the same timing. When set to high level, SH\_OUT1 to SH\_OUT6 and SH\_OUT7 to SH\_OUT12 are output at phases offset by 1/2 clock period from each other.

#### · Output phase setting

The phase of each SH\_OUT output can be adjusted in MCLK period units when SL\_DAT is high or in 1/2 MCLK period units when SL\_DAT is low by POSCTR[3:0] (Pins 6 to 9). The phase can be set in 16 ways by 4-bit digital input. The output phase shifts backward by the above unit each time this setting is increased by one bit.

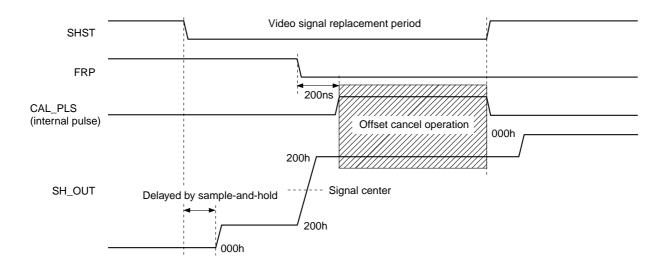

#### 5. Calibration level generator block

The CXA3562AR generates the offset cancel circuit reference with a calibration level generator in order to minimize the deviation between channels at the center level.

The 200h output level is generated at both the AC output high and low sides, and these levels are DC output from CAL\_OH and CAL\_OL, respectively. At the same time, 200h data is forcibly inserted into the video signal while the video blanking period SHST pulse is low level, and feedback is applied so that the output levels of all SH\_OUT channels conform to CAL\_IH and CAL\_IL during this period.

#### 6. SID signal generator block

This circuit generates the precharge signal waveform used by the LCD panel.

The voltage input from PRG\_LV (Pin 58) and SID\_LV (Pin 59) is switched by the PRG pulse (Pin 60). The PRG\_LV voltage is selected when PRG is high, and the SID\_LV voltage is selected when PRG is low. This signal is then further amplified by a factor of two times and folded by the FRP pulse. The folded center voltage is the SH\_OUT center voltage (voltage set by the SIG.C pin). SID\_OUT (Pin 57) is inverted when FRP is low, and non-inverted when FRP is low. Conversely, SID\_OUTX (Pin 56) is inverted when FRP is low, and non-inverted when FRP is high.

SID\_OUT and SID\_OUTX cannot directly drive the precharge signal input of the LCD panel, so they should be connected via a buffer having sufficient current supply capability.

#### 7. VCOM potential generator block

This block sets the DC common potential for the LCD panel.

VCOM\_OFST (Pin 54) sets the deviation relative to the SH\_OUT center potential, which is set by SIG.C.

## **Example of Representative Characteristics** (Vcc = 15.5V, Vdd = 5.0V, Ta = 25°C)

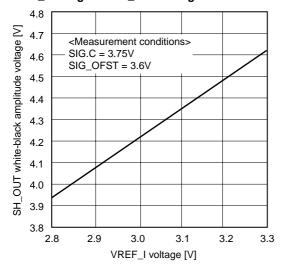

VREF\_I voltage vs. SH\_OUT voltage white-black amplitude

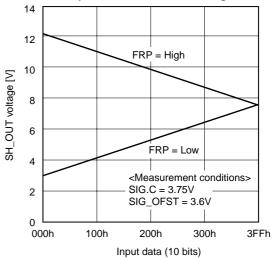

Input data vs. SH\_OUT voltage

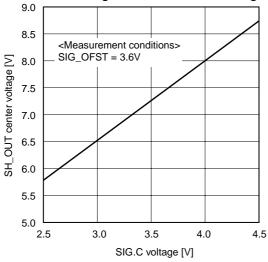

SIG.C voltage vs. SH\_OUT center voltage

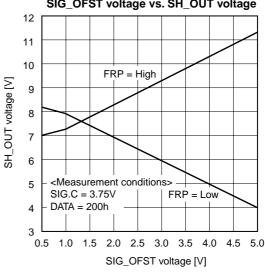

SIG\_OFST voltage vs. SH\_OUT voltage

VCOM\_OFST voltage vs. VCOM\_OUT voltage

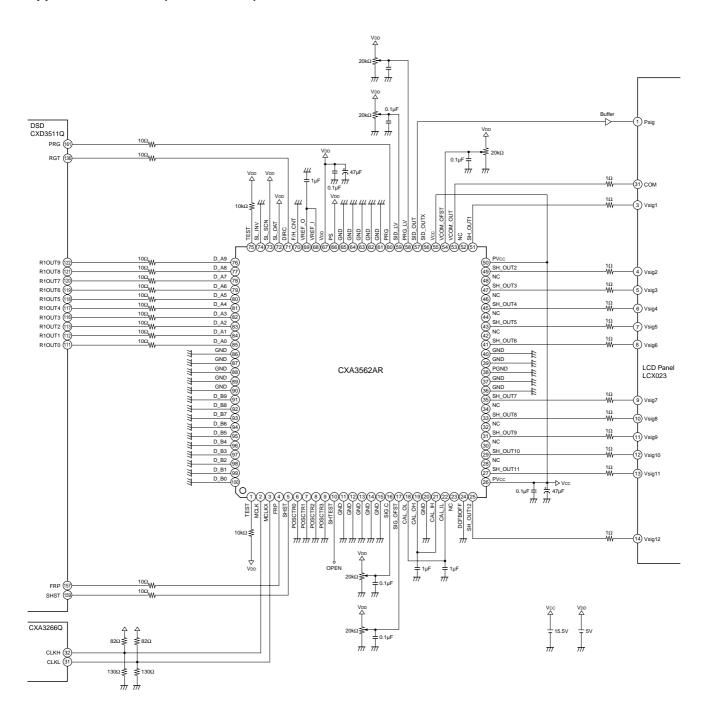

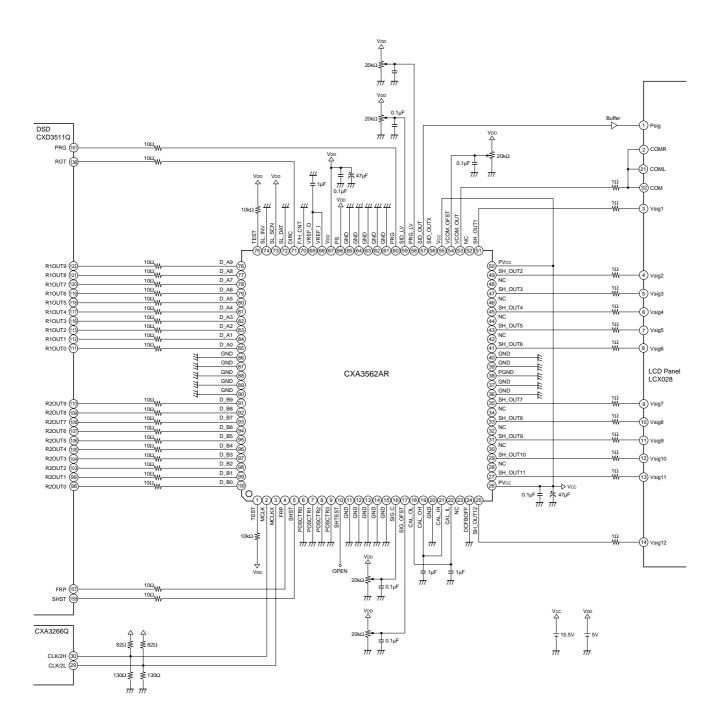

## **Application Circuit 1 (to XGA Panel)**

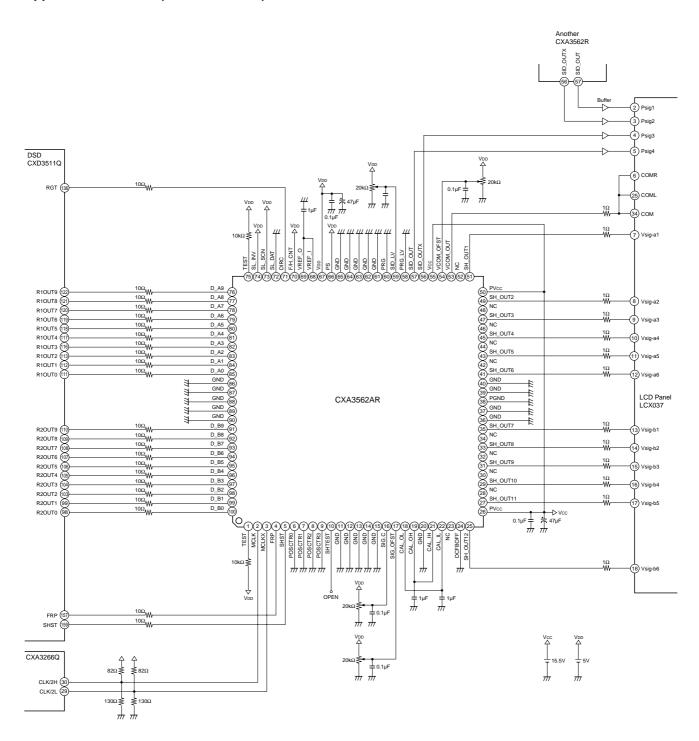

## **Application Circuit 2 (to SXGA Panel)**

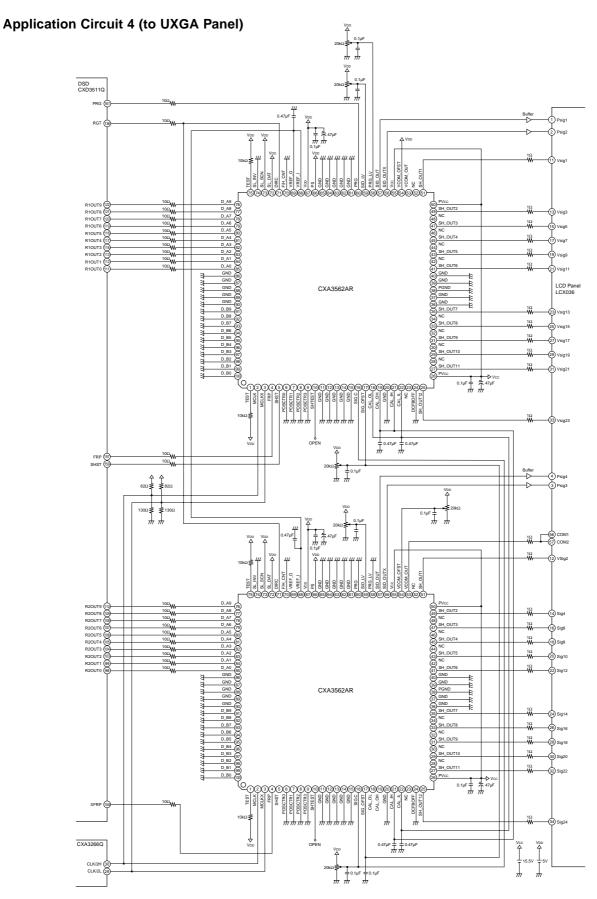

## **Application Circuit 3 (to WXGA Panel)**

SONY

CXA3562AR

## **Notes on Operation**

The CXA3562AR has high power consumption, so be sure to take the following radiation measures.

- Use four-layer substrate.

- GND lines connected between Pins 11 to 15, Pins 36 to 40, Pins 61 to 65 and Pins 86 to 90 should be as thick as possible.

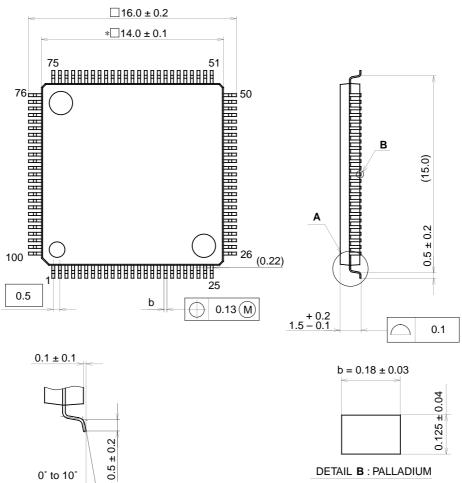

## Package Outline Unit: mm

# 100PIN LQFP (PLASTIC)

NOTE: Dimension "\*" does not include mold protrusion.

DETAIL A

## PACKAGE STRUCTURE

|            |                     | PACKAGE MATERIAL | EPOXY RESIN       |

|------------|---------------------|------------------|-------------------|

| SONY CODE  | LQFP-100P-L01       | LEAD TREATMENT   | PALLADIUM PLATING |

| EIAJ CODE  | P-LQFP100-14x14-0.5 | LEAD MATERIAL    | COPPER ALLOY      |

| JEDEC CODE |                     | PACKAGE MASS     | 0.7g              |