Technical Data

XC5200 Logic Cell Array Family

Preliminary (v1.0) • April 1995

XILINX® and XACT are registered trademarks of Xilinx. All XC-prefix product designations, XACT-Performance, X-BLOX, XChecker, XDM, LCA, Logic Cell, Express, VersaBlock, and VersaRing are trademarks of Xilinx. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx.

Mentor is a registered trademark and NETED, Design Architect, QuickSim, and QuickSim II are trademarks of Mentor Graphics, Inc. OrCAD is a registered trademark of OrCAD Systems Corporation Viewlogic, Viewsim, and Viewdraw are registered trademarks of Viewlogic Systems, Inc. Synopsys is a registered trademark of Synopsys, Inc. Xilinx does not assume any liability arising out of the application or use of any product described herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others.

Xilinx reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx devices and products are protected under one or more of the

```

following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557;

4,746,822; 4,750,155; 4,758,985; 4,783,607; 4,820,937; 4,821,233;

4,835,418; 4,853,626; 4,855,619; 4,855,669; 4,902,910; 4,940,909;

4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603;

5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238;

5,267,187; 5,224,056; 5,245,277; 5,291,079; 5,295,090; 5,302,866;

5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220;

5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249;

5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999;

5,365,125; 5,367,207; 5,386,154; RE 34,363; RE 34,444; and

RE 34,808. Xilinx, Inc. does not represent that devices shown or

products described herein are free from patent infringement or from any

other third-party right. Xilinx assumes no obligation to correct any errors

contained herein or to advise any user of this text of any correction if

such be made. Xilinx will not assume any liability for the accuracy or

correctness of any engineering or software support or assistance

provided to a user.

```

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

# TABLE OF CONTENTS

| Features                                | 1  |

|-----------------------------------------|----|

| Description                             | 1  |

| XC5200 Family Compared to XC4000 Family | 2  |

| Architectural Overview                  | 3  |

| Development System                      | 6  |

| Detailed Functional Description         | 8  |

| VersaBlock Routing                      | 12 |

| General Routing Matrix                  | 14 |

| Configuration                           | 17 |

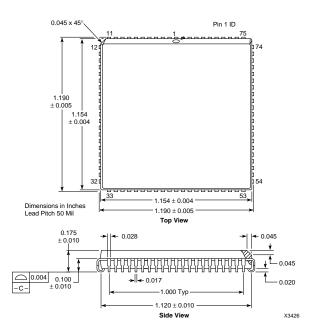

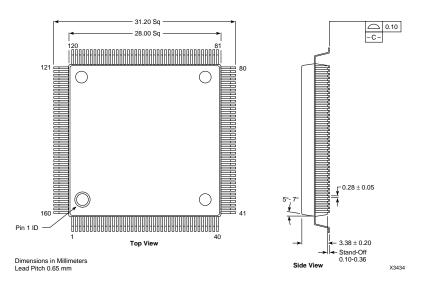

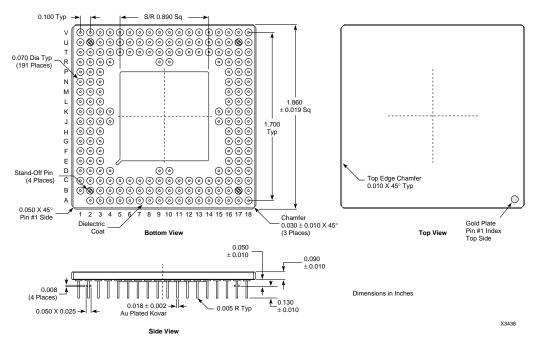

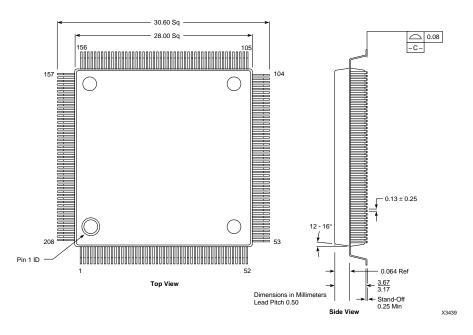

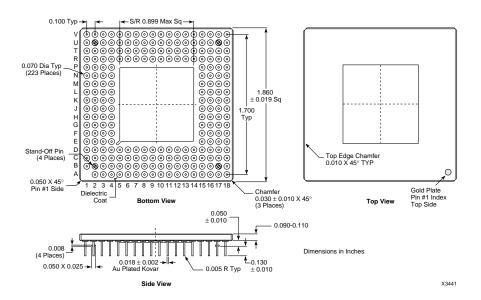

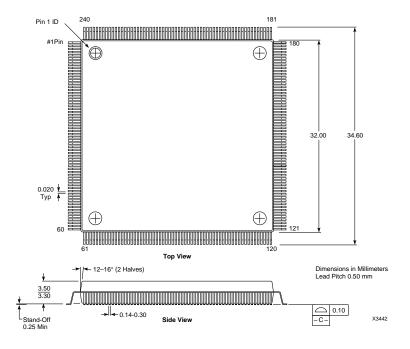

| Physical Dimensions                     | 40 |

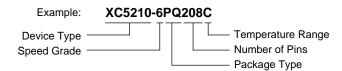

| Ordering Information                    | 43 |

# XC5200 Logic Cell Array Family

# Preliminary (v1.0)

# **Features**

- High-density family of Field-Programmable Gate Arrays (FPGAs)

- Design- and process-optimized for low cost

0.6-µm three-layer metal (TLM) process

- System performance up to 50 MHz

- · SRAM-based, in-system reprogrammable architecture

- · Flexible architecture with abundant routing resources

- VersaBlock™ logic module

- VersaRing™ I/O interface

- Dedicated cell-feedthrough path

- Hierarchical interconnect structure

- Extensive registers/latches

- Dedicated carry logic for arithmetic functions

- Cascade chain for wide input functions

- Dedicated IEEE 1149.1 boundary-scan logic

- Internal 3-state bussing capability

- Four global low-skew clock or signal distribution nets

- Globally selectable CMOS or TTL input thresholds

- Output slew-rate control

- 8-mA sink current per output

- Configured by loading binary file

- Unlimited reprogrammability

- Six programming modes, including high-speed Express™ mode

- 100% factory tested

- 100% footprint compatibility for common packages

# **Product Description**

- Fully supported by XACT<sup>®</sup> Development System

- Includes complete support for XACT-Performance™, X-BLOX™, Unified Libraries, Relationally Placed Macros (RPMs), XDelay, and XChecker™

- Wide selection of PC and workstation platforms

- Interfaces to more than 100 third-party CAE tools

# Description

The XC5200 Field-Programmable Gate Array Family is engineered to deliver the lowest cost of any FPGA family. By optimizing the new XC5200 architecture for TLM technology and 0.6-µm CMOS SRAM process, dramatic advances have been made in silicon efficiency. These advances position the XC5200 family as a cost-effective, high-volume alternative to gate arrays.

Building on experiences gained with three previous successful SRAM FPGA families, the XC5200 family brings a robust feature set to high-density programmable logic design. The VersaBlock logic module, the VersaRing I/O interface, and a rich hierarchy of interconnect resources combine to enhance design flexibility and reduce time-to-market.

Complete support for the XC5200 family is delivered through the familiar XACT software environment. The XC5200 family is fully supported on popular workstation and PC platforms. Popular design entry methods are fully supported, including ABEL, schematic capture, and synthesis. Designers utilizing logic synthesis can use their existing Synopsys, Viewlogic, Mentor, and Exemplar tools to design with the XC5200 devices.

Table 1. Initial XC5200 Field-Programmable Gate Array Family Members

| Device                        | XC5202           | XC5204           | XC5206           | XC5210             | XC5215             |

|-------------------------------|------------------|------------------|------------------|--------------------|--------------------|

| Typical Gate Range            | 2,200 -<br>2,700 | 3,900 -<br>4,800 | 6,000 -<br>7,500 | 10,000 -<br>12,000 | 14,000 -<br>18,000 |

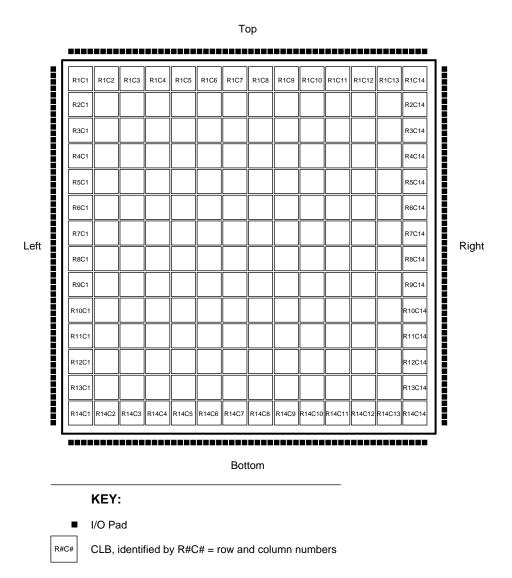

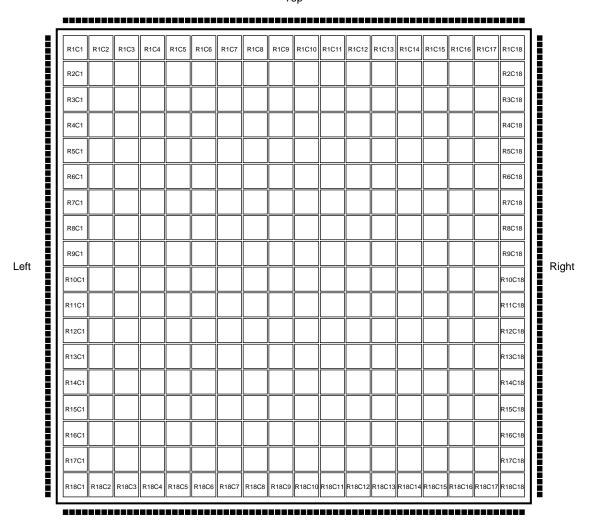

| VersaBlock Array              | 8 x 8            | 10 x 12          | 14 x 14          | 18 x 18            | 22 x 22            |

| Number of CLBs                | 64               | 120              | 196              | 324                | 484                |

| Number of Flip-Flops          | 256              | 480              | 784              | 1,296              | 1,936              |

| Number of I/Os                | 84               | 124              | 148              | 196                | 244                |

| TBUFs per Horizontal Longline | 10               | 14               | 16               | 20                 | 24                 |

|                               |                  |                  |                  |                    |                    |

# XC5200 Family Compared to XC4000 Family

For those readers already familiar with the XC4000 family of Xilinx Field-Programmable Gate Arrays, here is a concise description of the similarities and differences between the XC4000 and XC5200 families.

Superficially, the XC5200 family is quite similar to the XC4000 family. Both use CMOS SRAM technology. Both use 4-input lookup tables with unshared inputs. Both have a dedicated fast carry track, and dedicated boundary-scan logic in the input/output blocks (IOBs).

XC5200 and XC4000 devices are footprint and pin-out compatible; their pin names and pin locations are identical. XC5200 devices offer the same configuration options as XC4000 devices, and they can be intermixed with XC4000 devices in a configuration daisy chain.

There are also, however, significant differences between the two families:

- XC5200 lookup tables cannot be used as RAM.

- The XC5200 family offers dedicated carry logic, but differs from the XC4000 family in that the sum is generated in an additional function generator in the adjacent column. An XC5200 device thus uses twice as many function generators for adders, subtracters, accumulators, and some counters. Note, however, that a loadable up/down counter requires the same number of function generators in both families.

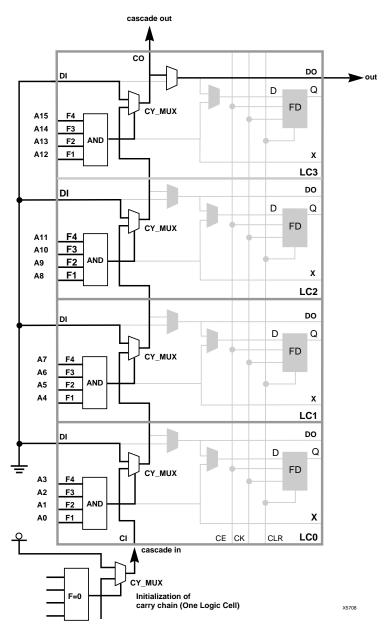

- XC5200 devices have no dedicated wide edge decoders. The XC5200 carry logic, unlike the XC4000 architecture, can be used to cascade function generators to implement wide AND and OR functions, for example.

- The XC5200 family contains a flexible coupling of logic and local routing resources called the VersaBlock. The XC5200 VersaBlock element includes the Configurable Logic Block (CLB), a Local Interconnect Matrix (LIM), and direct connects to neighboring VersaBlocks.

- XC5200 CLBs are roughly equivalent to two XC4000 CLBs. Each XC5200 CLB contains four 4-input function generators and four registers, which are configured as four independent Logic Cells™ (LCs). The output from each function generator can be brought out as a CLB output and/or drive the D input of a flip-flop. Pairs of logic cells can be combined to form a 5-input function generator.

- There are four direct feedthrough paths per CLB, one per LC. These paths can provide extra data input lines or serve as local routes without consuming any logic resources.

- The XC5200 family has a global reset, whereas the XC4000 family has both a global set and a global reset.

- Unlike the XC4000 family, each register can be configured as either an edge-triggered D flip-flop or a transparent, level-sensitive latch.

- There are no dedicated IOB flip-flops, but there are fast direct connects to adjacent CLBs.

Table 2. Four Generations of Xilinx Field-Programmable Gate Array Families

| Parameter                   | XC5200 | XC4000 | XC3000A/XC3100A | XC2000 |

|-----------------------------|--------|--------|-----------------|--------|

| Function generators per CLB | 4      | 3      | 2               | 2      |

| Logic inputs per CLB        | 20     | 9      | 5               | 4      |

| Logic outputs per CLB       | 12     | 4      | 2               | 2      |

| Low-skew global buffers     | 4      | 8      | 2               | 2      |

| User RAM                    | no     | yes    | no              | no     |

| Dedicated decoders          | no     | yes    | no              | no     |

| Cascade chain               | yes    | no     | no              | no     |

| Fast carry logic            | yes    | yes    | no              | no     |

| Internal 3-state drivers    | yes    | yes    | yes             | no     |

| IEEE boundary scan          | yes    | yes    | no              | no     |

| Output slew-rate control    | yes    | yes    | yes             | no     |

| Power-down option           | no     | no     | yes             | yes    |

| Crystal oscillator circuit  | no     | no     | yes             | yes    |

Table 3. Routing Resource Comparison

| Resource               | XC5200 | XC4000 |

|------------------------|--------|--------|

| Single-length Lines    | 10     | 8      |

| Double-length Lines    | 4      | 4      |

| Longlines              | 8      | 6      |

| <b>Direct Connects</b> | 8      | 0      |

| VersaRing              | yes    | no     |

- The TLM process allows significant improvements in the routing structure. Each XC5200 VersaBlock element has complete intra-CLB routing, the LIM, and offers four direct routing connections to each of the four neighboring CLBs (North, South, East, and West). Any function generator or flip-flop thus has unrestricted connectivity to 19 other function generators or flip-flops: three in its own CLB, and 16 in the adjacent CLBs. These direct connects do not compete with the general routing resources (see Table 3).

- Each XC5200 3-state buffer (TBUF) can drive up to two horizontal Longlines; each XC4000 TBUF accesses only one horizontal Longline.

- There is a special racetrack, the VersaRing, between the outer edge of the core CLB array and the ring of IOBs, providing significant help in overcoming the problems caused by early locking of I/O pins.

- There are no internal pull-ups for XC5200 Longlines.

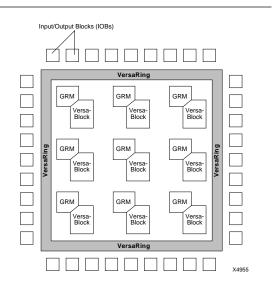

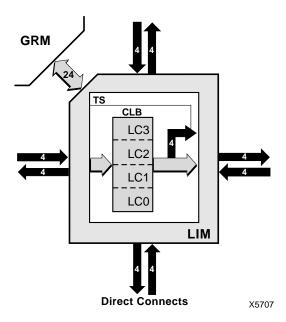

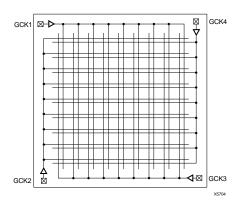

Figure 1. XC5200 Architectural Overview

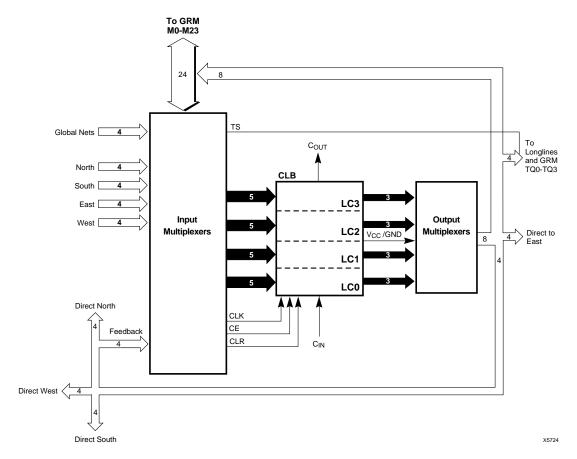

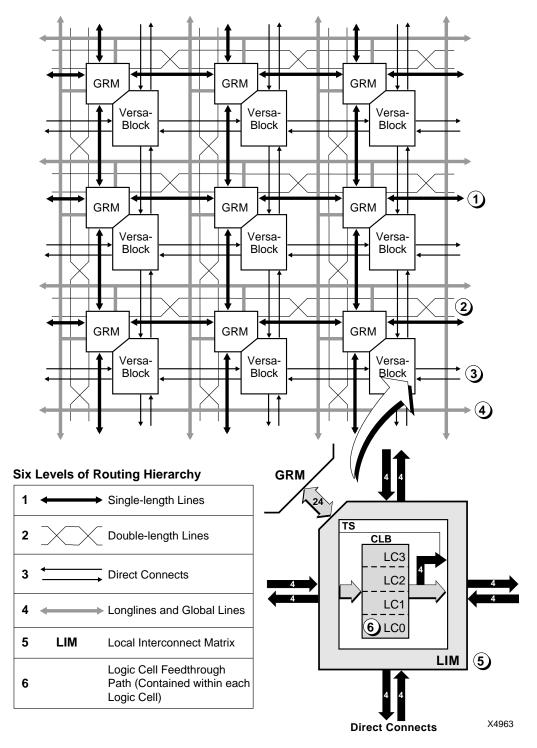

#### **Architectural Overview**

Figure 1 presents a simplified, conceptual overview of the XC5200 architecture. Similar to conventional FPGAs, the XC5200 family consists of programmable IOBs, programmable logic blocks, and programmable interconnect. Unlike other FPGAs, however, the logic and local routing resources of the XC5200 family are combined in flexible VersaBlocks. General-purpose routing connects to the VersaBlock through the General Routing Matrix (GRM).

# VersaBlock: Abundant Local Routing Plus Versatile Logic

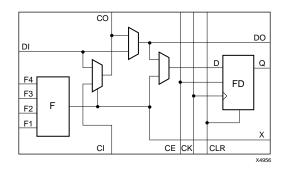

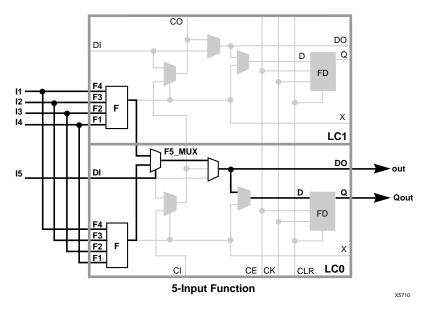

The basic logic element in each VersaBlock structure is the Logic Cell, shown in Figure 2. Each LC contains a 4-input function generator (F), a storage device (FD), and control logic. There are five independent inputs and three outputs to each LC. The independence of the inputs and outputs allows the software to maximize the resource utilization within each LC. Each Logic Cell also contains a direct feedthrough path that does not sacrifice the use of either the function generator or the register; this feature is a first for FPGAs. The storage device is configurable as either a D flip-flop or a latch. The control logic consists of carry logic for fast implementation of arithmetic functions, which can also be configured as a cascade chain allowing decode of very wide input functions.

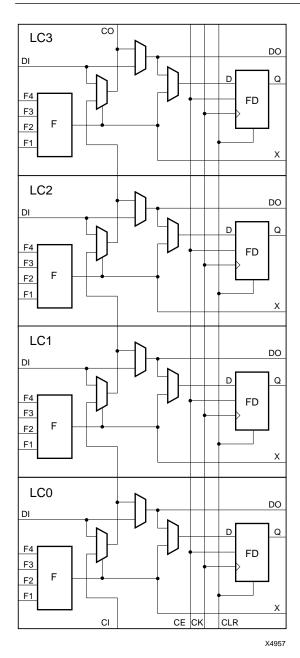

The XC5200 CLB consists of four LCs, as shown in Figure 3. Each CLB has 20 independent inputs and 12 independent outputs. The top and bottom pairs of LCs can be configured to implement 5-input functions. The challenge of FPGA implementation software has always been to maximize the usage of logic resources. The XC5200 family addresses this issue by surrounding each CLB with two types of local interconnect — the LIM and direct connects. These two interconnect resources, combined with the CLB, form the VersaBlock, represented in Figure 4.

Figure 2. XC5200 Logic Cell (Four LCs per CLB)

Figure 3. Configurable Logic Block

Figure 4. VersaBlock

The LIM provides 100% connectivity of the inputs and outputs of each LC in a given CLB. The benefit of the LIM is that no general routing resources are required to connect feedback paths within a CLB. The LIM connects to the GRM via 24 bidirectional nodes.

The direct connects allow immediate connections to neighboring CLBs, once again without using any of the general interconnect. These two layers of local routing resource improve the granularity of the architecture, effectively making the XC5200 family a "sea of logic cells." Each VersaBlock has four 3-state buffers that share a common enable line and directly drive horizontal Longlines, creating robust on-chip bussing capability. The VersaBlock allows fast, local implementation of logic functions, effectively implementing user designs in a hierarchical fashion. These resources also minimize local routing congestion and improve the efficiency of the general interconnect, which is used for connecting larger groups of logic. It is this combination of both fine-grain and coarse-grain architecture attributes that maximize logic utilization in the XC5200 family. This symmetrical structure takes full advantage of the third metal layer, freeing the placement software to pack user logic optimally with minimal routing restrictions.

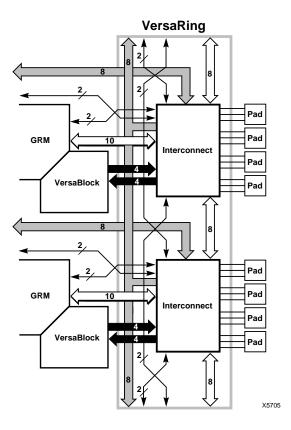

#### VersaRing I/O Interface

The interface between the IOBs and core logic has been redesigned in the XC5200 family. The IOBs are completely decoupled from the core logic. The XC5200 IOBs contain dedicated boundary-scan logic for added board-level testability, but do not include input or output registers. This approach allows a maximum number of IOBs to be placed around the device, improving the I/O-togate ratio and decreasing the cost per I/O. A "freeway" of interconnect cells surrounding the device forms the VersaRing, which provides connections from the IOBs to the internal logic These incremental routing resources provide abundant connections from each IOB to the nearest VersaBlock, in addition to Longline connections surrounding the device. The VersaRing eliminates the historic trade-off between high logic utilization and pin placement flexibility. These incremental edge resources give users increased flexibility in preassigning (i.e., locking) I/O pins before completing their logic designs. This ability accelerates time-to-market, since PCBs and other system components can be manufactured concurrent with the logic design.

# **General Routing Matrix**

The GRM is functionally similar to the switch matrices found in other architectures, but it is novel in its tight coupling to the logic resources contained in the VersaBlocks. Advanced simulation tools were used during the development of the XC5200 architecture to determine the optimal level of routing resources required. The XC5200 family contains six levels of interconnect hierarchy — a series of single-length lines, double-length lines, and Longlines all routed through the GRM. The direct connects, LIM, and logic-cell feedthrough are

contained within each VersaBlock. Throughout the XC5200 interconnect, an efficient multiplexing scheme, in combination with TLM, was used to improve the overall efficiency of silicon usage.

#### **Performance Overview**

The XC5200 family has been benchmarked with many designs running synchronous clock rates up to 40 MHz. The performance of any design depends on the circuit to be implemented, and the delay through the combinatorial and sequential logic elements, plus the delay in the interconnect routing. Table 4 shows some performance numbers for representative circuits, using worst-case timing parameters for the Engineering Sample (ES) speed grade. A rough estimate of timing can be made by assuming 6 ns per logic level, which includes direct-connect routing delays. More accurate estimations can be made using the information in the Switching Characteristic Guideline section.

Table 4. Performance for Several Common Circuit Functions

| Function                               | XC5200 Speed Grade |        |    |

|----------------------------------------|--------------------|--------|----|

| Function                               | -6                 | -5     | -4 |

| 16-bit Decoder from Input Pad          | 9 ns               | 8 ns   |    |

| 24-bit Accumulator                     | 32 MHz             | 39 MHz |    |

| 16-to-1 Multiplexer                    | 16 ns              | 13 ns  |    |

| 16-bit Unidirectional Loadable Counter | 40 MHz             | 50 MHz |    |

| 16-bit U/D Counter                     | 40 MHz             | 50 MHz |    |

| 16-bit Adder                           | 24 ns              | 20 ns  |    |

| 24-bit Loadable U/D Counter            | 36 MHz             | 42 MHz |    |

# **Development System**

The powerful features of the XC5200 device family require an equally powerful, yet easy-to-use, set of development tools. Xilinx provides an enhanced version of the Xilinx Automatic CAE Tools (XACT), optimized for the XC5200 family.

As with other logic technologies, the basic methodology for XC5200 FPGA design consists of three interrelated steps: design entry, implementation, and verification. Popular generic tools are used for entry and simulation (for example, Viewlogic Systems's Viewdraw schematic editor and Viewsim simulator), but architecture-specific tools are needed for implementation.

All Xilinx development system software is integrated under the Xilinx Design Manager (XDM™), providing designers with a common user interface regardless of their choices of entry and verification tools. XDM simplifies the selection of command-line options with pull-down menus and online help text. Application programs ranging from schematic capture to Partitioning, Placement, and Routing (PPR) can be accessed from XDM, while the program-command sequence is generated and stored for documentation prior to execution. The XMAKE command, a design compilation utility, automates the entire implementation process, automatically retrieving the design's input files and performing all the steps needed to create configuration and report files.

Several advanced features of the XACT system facilitate XC5200 FPGA design. RPMs — schematic-based macros with relative location constraints to guide their placement within the FPGA — help to ensure an optimized implementation for common logic functions. An abundance of local routing permits RPMs to be contained within a single VersaBlock or to span across multiple VersaBlocks. XACT-Performance allows designers to enter the exact performance requirements during design entry, at the schematic level, to guide PPR.

# **Design Entry**

Designs can be entered graphically, using schematic-capture software, or in any of several text-based formats (such as Boolean equations, state-machine descriptions, and high-level design languages).

Xilinx and third-party CAE vendors have developed library and interface products compatible with a wide variety of design-entry and simulation environments. A standard interface-file specification, Xilinx Netlist File (XNF), is provided to simplify file transfers into and out of the XACT development system.

Xilinx offers XACT development system interfaces to the following design environments:

- · Viewlogic Systems (Viewdraw, Viewsim)

- Mentor Graphics V8 (NETED, QuickSim, Design Architect, QuickSim II)

- OrCAD (SDT, VST)

- Synopsys (Design Compiler, FPGA Compiler)

- Xilinx-ABEL (State Machine module generator)

- X-BLOX (Graphical Mode Generator)

Many other environments are supported by third-party vendors. Currently, more than 100 packages are supported.

The unified schematic library for the XC5200 FPGA reflects the wide variety of logic functions that can be implemented in these versatile devices. The library contains over 400 primitives and macros, ranging from 2-input AND gates to 16-bit accumulators, and includes arithmetic functions, comparators, counters, data registers, decoders, encoders, I/O functions, latches, Boolean functions, multiplexers, shift registers, and barrel shifters.

Designing with macros is as easy as designing with standard SSI/MSI functions. The "soft macro" library contains detailed descriptions of common logic functions, but does not contain any partitioning or routing information. The performance of these macros depends, therefore, on how the PPR software processes the design. RPMs, on the other hand, do contain predetermined partitioning and relative placement information, resulting in an optimized implementation for these functions. Users can create their own library elements — either soft macros or RPMs — based on the macros and primitives of the standard library.

The X-BLOX design language is a graphics-based highlevel description language (HDL) that allows designers to use a schematic editor to enter designs as a set of generic modules. The X-BLOX compiler synthesizes and optimizes the modules for the target device architecture, automatically choosing the appropriate architectural resources for each function.

The XACT design environment supports hierarchical design entry, with top-level drawings defining the major functional blocks, and lower-level descriptions defining the logic in each block. The implementation tools automatically combine the hierarchical elements of a design. Different hierarchical elements can be specified with different design entry tools, allowing the use of the most convenient entry method for each portion of the design.

#### **Design Implementation**

The design implementation tools satisfy the requirements for an automated design process. Logic partitioning, block placement, and signal routing are performed by the PPR program. The partitioner takes the logic from the entered design and maps the logic into the architectural resources of the FPGA (such as the logic blocks, I/O blocks, and 3-state buffers). The placer then determines the best locations for the blocks, depending on their connectivity and the required performance. The router finally connects the placed blocks together.

The PPR algorithms support fully automatic implementation of most designs. However, for demanding applications, the user may exercise various degrees of control over the automated implementation process. Optionally, user-designated partitioning, placement, and routing information can be specified as part of the designentry process. The implementation of highly structured designs can benefit greatly from the basic floorplanning techniques familiar to designers of large gate arrays.

The PPR program includes XACT-Performance, a feature that allows designers to specify the timing requirements along entire paths during design entry. Timing path analysis routines in PPR then recognize and accommodate the user-specified requirements. Timing requirements can be entered on the schematic in a form directly relating to the system requirements (such as the targeted minimum clock frequency, or the maximum allowable delay on the data path between two registers). So, while the timing of each individual net is not predictable, the overall performance of the system along entire signal paths is automatically tailored to match user-generated specifications.

# **Design Verification**

The high development cost associated with common mask-programmed gate arrays necessitates extensive simulation to verify a design. Due to the custom nature of masked gate arrays, mistakes or last-minute design changes cannot be tolerated. A gate-array designer must simulate and test all logic using simulation software. Simulation describes what happens in a system under worst-case situations. However, simulation can be tedious and slow, and simulation vectors must be generated. A few seconds of system time can take weeks to simulate.

Programmable-gate-array users, however, can use incircuit debugging techniques in addition to simulation. Because Xilinx devices are reprogrammable, designs can be verified in real time without the need for extensive simulation vectors.

The XACT development system supports both simulation and in-circuit debugging techniques. For simulation, the system extracts the post-layout timing information from the design database. This data can then be sent to the simulator to verify timing-critical portions of the design database using XDELAY, the Xilinx static timing analyzer tool. Back-annotation — the process of mapping the timing information back into the signal names and symbols of the schematic — eases the debugging effort.

For in-circuit debugging, the XACT development system includes a serial download and readback cable (XChecker) that connects the FPGA in the system to the PC or workstation through an RS232 serial port. The engineer can download a design or a design revision into the system for testing. The designer can also single-step the logic, read the contents of the numerous flip-flops on the device, and observe internal logic levels. Simple modifications can be downloaded into the system in a matter of minutes.

# **Detailed Functional Description**

# **CLB Logic**

Figure 3 shows the logic in the XC5200 CLB, which consists of four Logic Cells (LC[3:0]). Each Logic Cell consists of an independent 4-input Lookup Table (LUT), and a D-Type flip-flop or latch with common clock, clock enable, and clear, but individually selectable clock polarity. Additional logic features provided in the CLB are:

- High-speed carry propagate logic.

- · High-speed pattern decoding.

- High-speed direct connection to flip-flop D-inputs.

- Each flip-flop can be programmed individually as either a transparent, level-sensitive latch or a D flip-flop.

- Four 3-state buffers with a shared Output Enable.

- Two 4-input LUTs can be combined to form an independent 5-input LUT.

# 5-Input Functions

Figure 5 illustrates how the outputs from the LUTs from LC0 and LC1 can be combined with a 2:1 multiplexer (F5\_MUX) to provide a 5-input function. The outputs from the LUTs of LC2 and LC3 can be similarly combined.

Figure 5. Two LUTs in Parallel Combined to Create a 5-input Function

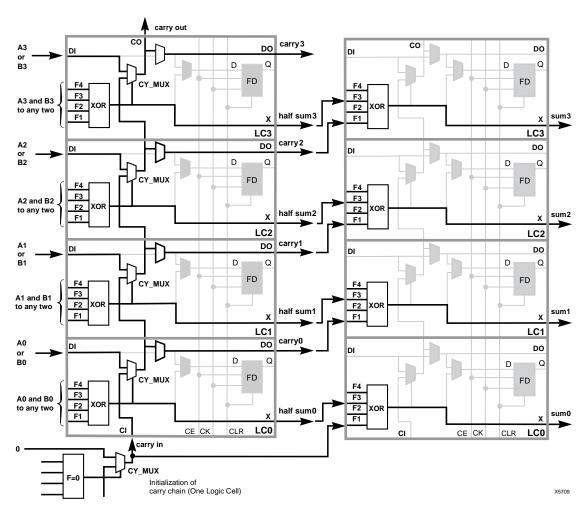

# **Carry Function**

The XC5200 family supports a carry-logic feature that enhances the performance of arithmetic functions such as counters, adders, etc. A carry multiplexer (CY\_MUX) symbol on a schematic is used to indicate the XC5200 carry logic. This symbol represents the dedicated 2:1 multiplexer in each LC that performs the one-bit high-speed carry propagate per logic cell (four bits per CLB).

While the carry propagate is performed inside the LC, an adjacent LC must be used to complete the arithmetic function. Figure 6 represents an example of an adder function. The carry propagate is performed on the CLB

shown, which also generates the half-sum for the four-bit adder. An adjacent CLB is responsible for XORing the half-sum with the corresponding carry-out. Thus an adder or counter requires two LCs per bit. Notice that the carry chain requires an initialization stage, which the XC5200 family accomplishes using the carry initialize (CY\_INIT) macro and one additional LC.

The XC5200 library contains a set of RPMs and arithmetic functions designed to take advantage of the dedicated carry logic. Using and modifying these macros makes it much easier to implement customized RPMs, freeing the designer from the need to become an expert on architectures.

Figure 6. XC5200 CY\_MUX Used for Adder Carry Propagate

# **Cascade Function**

Each CY\_MUX can be connected to the CY\_MUX in the adjacent LC to provide cascadable decode logic. Figure 7 illustrates how the 4-input function generators can be configured to take advantage of these four cascaded

CY\_MUXes. Note that AND and OR cascading are specific cases of a general decode. In AND cascading all bits are decoded equal to logic one, while in OR cascading all bits are decoded equal to logic zero. The flexibility of the LUT achieves this result.

Figure 7. XC5200 CY\_MUX Used for Decoder Cascade Logic

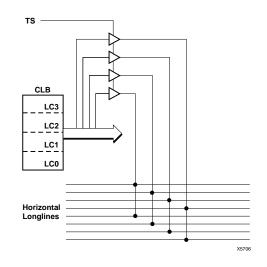

#### 3-State Buffers

The XC5200 family has four dedicated TBUFs per CLB. The four buffers are individually configurable through four configuration bits to operate as simple non-inverting buffers or in 3-state mode. When in 3-state mode the CLB's output enable (TS) control signal drives the enable to all four buffers (see Figure 8). Each TBUF can drive up to two horizontal Longlines

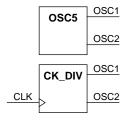

#### Oscillator

The XC5200 oscillator (OSC52) divides the internal 16-MHz clock or a user clock that is connected to the "C" pin. The user then has the choice of dividing by 4, 16, 64, or 256 for the "OSC1" output and dividing by 2, 8, 32, 128, 1024, 4096, 16384, or 65536 for the "OSC2" output. The division is specified via a "DIVIDEn\_BY=x" attribute on the symbol, where n=1 for OSC1, or n=2 for OSC2. The OSC5 macro is used where an internal oscillator is required. The CK\_DIV macro is applicable when a user clock input is specified (see Figure 9).

Figure 8. XC5200 3-State Buffer

Figure 9. XC5200 Oscillator Macros

#### Start-Up

On start-up, all XC5200 internal flip-flops are reset. The XC5200 devices do not support the "INIT=" attribute. Thus, the XC5200 family has only a global reset (GR) signal. The user can assign the pin location for the GR signal and use it to reset asynchronously all of the flip-flops in the design without using general routing resources. The user can also assign a positive or negative polarity to GR.

#### **Boundary Scan**

XC5200 devices support all the mandatory boundary-scan instructions specified in the IEEE standard 1149.1. A Test Access Port (TAP) and registers are provided that implement the EXTEST, SAMPLE/PRELOAD, and BYPASS instructions. The TAP can also support two USERCODE instructions.

Boundary-scan operation is independent of individual IOB configuration and package type. All IOBs are treated as independently controlled bidirectional pins, including any unbonded IOBs. Retaining the bidirectional test capability after configuration provides flexibility for interconnect testing.

Also, internal signals can be captured during EXTEST by connecting them to unbonded IOBs, or to the unused outputs in IOBs used as unidirectional input pins. This technique partially compensates for the lack of INTEST support.

The public boundary-scan instructions are always available prior to configuration. After configuration, the public instructions and any USERCODE instructions are only available if specified in the design. While SAMPLE and BYPASS are available during configuration, it is recommended that boundary-scan operations not be performed during this transitory period.

In addition to the test instructions outlined above, the boundary-scan circuitry can be used to configure the Logic Cell Array (LCA $^{\text{TM}}$ ) device, and to read back the configuration data.

All of the XC4000 boundary-scan modes are supported in the XC5200 family. Three additional outputs for the User Register are provided (Reset, Update, and Shift), representing the decoding of the corresponding state of the boundary-scan internal state machine. For details on boundary scan, refer to "Boundary Scan in XC4000 Devices — Application Note" on pages 8-45 through 8-42 of the 1994 Xilinx Programmable Logic Data Book.

# **VersaBlock Routing**

#### **Local Interconnect Matrix**

The GRM connects to the VersaBlock via 24 bidirectional ports (M0-M23). Excluding direct connections, global nets, and 3-statable Longlines, all VersaBlock inputs and outputs connect to the GRM via these 24 ports. Four 3-statable unidirectional signals (TQ0-TQ3) drive out of the VersaBlock directly onto the horizontal Longlines. Two horizontal global nets (GH0 and GH1) and two vertical global nets (GV0 and GV1) connect directly to every CLB clock pin; they can connect to other CLB inputs via the GRM. Each CLB also has four unidirectional direct connects to each of its four neighboring CLBs. These direct connects can also feed directly back to the CLB (see Figure 10).

In addition, each CLB has 16 direct inputs, four direct connections from each of the neighboring CLBs. These direct connections provide high-speed local routing that bypasses the GRM.

The 13 CLB outputs (12 LC outputs plus a  $V_{cc}/GND$  signal) connect to the eight VersaBlock outputs via the output multiplexers, which consist of eight fully populated 13-to-1 multiplexers. Of the eight VersaBlock outputs, four signals drive each neighboring CLB directly, and provide a direct feedback path to the input multiplexers. The four remaining multiplexer outputs can drive the GRM through four TBUFs (TQ0-TQ3). All eight multiplexer outputs can connect to the GRM through the bidirectional M0-M23 signals. All eight signals also connect to the input multiplexers and are potential inputs to that CLB.

CLB inputs have several possible sources: the 24 signals from the GRM, 16 direct connections from neighboring VersaBlocks, four signals from global, low-skew buffers (GH0, GH1, GV0, and GV1), and the four signals from the CLB output multiplexers. Unlike the output multiplexers, the input multiplexers are not fully populated; i.e., only a subset of the available signals can be connected to a given CLB input. The flexibility of LUT input swapping and LUT mapping compensates for this limitation. For example, if a 2-input NAND gate is required, it can be mapped into any of the four LUTs, and use any two of the four inputs to the LUT.

# **Direct Connects**

The unidirectional direct-connect segments are connected to the logic input/output pins through the CLB's input and output multiplexer array, and thus bypass the programmable routing matrix altogether. These lines are intended to increase the routing channel utilization where possible, while simultaneously reducing the delay incurred in speed-critical connections.

The direct connects also provide a high-speed path from the edge CLBs to the VersaRing input/output buffers, and thus reduce set-up time, clock-to-out, and combinational propagation delay.

The direct connects are ideal for developing customized RPM cells. Using direct connects improves the macro performance, and leaves the other routing channels intact for improved routing. Direct connects can also route through a CLB using one of the four cell-feedthrough paths.

Figure 10. VersaBlock Details

# **General Routing Matrix**

The General Routing Matrix, shown in Figure 11, provides flexible bidirectional connections to the Local Interconnect Matrix through a hierarchy of different-length metal segments in both the horizontal and vertical directions. A programmable interconnect point (PIP) establishes an electrical connection between two wire segments. The PIP, consisting of a pass transistor switch controlled by a memory element, provides bidirectional (in some cases, unidirectional) connection between two adjoining wires. A collection of PIPs inside the General Routing Matrix and in the Local Interconnect Matrix provides connectivity between various types of metal segments. A hierarchy of PIPs and associated routing segments combine to provide a powerful interconnect hierarchy:

- Forty bidirectional single-length segments per CLB provide ten routing channels to each of the four neighboring CLBs in four directions.

- Sixteen bidirectional double-length segments per CLB provide four routing channels to each of four other (nonneighboring) CLBs in four directions.

- Eight horizontal and eight vertical bidirectional Longline segments span the width and height of the chip, respectively.

- Two low-skew horizontal and vertical unidirectional global-line segments span each row and column of the chip, respectively.

# Single- and Double-Length Lines

The single- and double-length bidirectional line segments make up the bulk of the routing channels. The double-length lines hop across every other CLB to reduce the propagation delays in speed-critical nets. Regenerating the signal strength is recommended after traversing three or four such segments. XACT place-and-route software automatically connects buffers in the path of the signal as necessary. Single- and double-length lines cannot drive onto Longlines and global lines; Longlines and global lines can, however, drive onto single- and double-length lines. As a general rule, Longline and global-line connections to the programmable routing matrix are unidirectional, with the signal direction from these lines toward the routing matrix.

# Longlines

Longlines are used for high-fan-out signals, 3-state busses, low-skew nets, and faraway destinations. Row and column splitter PIPs in the middle of the array effectively double the total number of Longlines by electrically dividing them into two separated half-lines. The horizontal Longlines are driven by the 3-state buffers in

each CLB, and are driven by similar buffers at the periphery of the array from the VersaRing I/O Interface.

Bus-oriented microprocessor designs are accommodated by using horizontal Longlines in conjunction with the 3state buffers in the CLB and in the VersaRing. Additionally, programmable keeper cells at the periphery can be enabled to retain the last valid logic level on the Longlines when all buffers are in 3-state mode.

Longlines connect to the single-length or double-length lines, or to the logic inside the CLB, through the General Routing Matrix. The only manner in which a Longline can be driven is through the four 3-state buffers; therefore, a Longline-to-Longline or single-line-to-Longline connection through PIPs in the General Routing Matrix is not possible. Again, as a general rule, long- and global-line connections to the General Routing Matrix are unidirectional, with the signal direction from these lines toward the routing matrix.

The XC5200 family has no pull-ups on the ends of the Longlines sourced by TBUFs. Consequently, wired functions (i.e., WAND and WORAND) and wide multiplexing functions requiring pull-ups for undefined states (i.e., bus applications) must be implemented in a different way. In the case of the wired functions, the same functionality can be achieved by taking advantage of the carry/cascade logic described above, implementing a wide logic function in place of the wired function. In the case of 3-state bus applications, the user must insure that all states of the multiplexing function are defined. This process is as simple as adding an additional TBUF to drive the bus High when the previously undefined states are activated.

# Global Clock Buffers

Global buffers in Xilinx FPGAs are special buffers that drive a dedicated routing network called Global Lines, as shown in Figure 12. This network is intended for high-fanout clocks or other control signals, to maximize speed and minimize skewing while distributing the signal to many leads

The XC5200 family has a total of four global buffers (BUFG symbol in the library), each with its own dedicated routing channel. Two are distributed vertically and two horizontally throughout the LCA.

Figure 11. XC5200 Interconnect Structure

# **Global Lines**

Two pairs of horizontal and vertical global lines provide low-skew clock signals to the CLBs. Global lines are driven by low-skew buffers inside the VersaRing. The global lines provide direct input only to the CLB clock pins. The global lines also connect to the General Routing Matrix to provide access from these lines to the function generators and other control signals.

Four clock input pads at the corners of the chip, as shown in Figure 12, provide a high-speed, low-skew clock network to each of the four global-line buffers. In addition to the dedicated pad, the global lines can be sourced by internal logic. PIPs from several routing channels within the VersaRing, inside the IOI cell, can also be configured to drive the global-line buffers.

# VersaRing Input/Output Interface

The VersaRing, shown in Figure 13, is positioned between the core logic and the pad ring; it has all the routing resources of a VersaBlock without the CLB logic. The VersaRing decouples the pad ring's pitch from the core's pitch. Each VersaRing Cell provides up to four pad-cell connections on one side, and connects directly to the CLB ports on the other side. Depending on placement and pad-cell pitch, any number of pad cells to a maximum of four can be connected to a VersaRing cell. Note: there are no direct connects from the Pads on top and bottom edges.

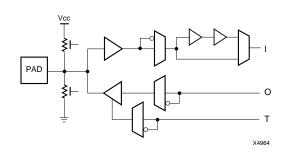

#### Input/Output Pad

The I/O pad, shown in Figure 14, consists of an input buffer and an output buffer. The output driver is an 8-mA full-rail CMOS buffer with 3-state control. Two slew-rate control modes are supported to minimize bus transients. Both the output buffer and the 3-state control are invertible.

Figure 12. Global Lines

The input buffer has globally selected CMOS and TTL input thresholds. The input buffer is invertible and also provides a programmable delay line to assure reliable chip-to-chip set-up and hold times. Minimum ESD protection is 5 KV using the Human Body Model.

Figure 13. VersaRing I/O Interface

Figure 14. XC5200 I/O Block

# Configuration

Configuration is the process of loading design-specific programming data into one or more LCA devices to define the functional operation of the internal blocks and their interconnections. This is somewhat like loading the command registers of a programmable peripheral chip. Each configuration bit defines the state of a static memory cell that controls either a function LUT bit, a multiplexer input, or an interconnect pass transistor. The XACT development system translates the design into a netlist file. It automatically partitions, places, and routes the logic and generates the configuration data in PROM format.

#### Modes

The XC5200 family has seven modes of configuration, selected by a 3-bit input code applied to the LCA mode pins (M0, M1, and M2). There are three self-clocking Master modes, two Peripheral modes, a Slave serial mode, and a new high-speed Slave parallel mode called the Express. See Table 5.

Brief descriptions of the seven modes are provided below. For details on all modes except Express, see pages 2-32 through 2-41 of the 1994 Xilinx Programmable Logic Data Book.

#### Master Modes

The Master modes use an internal oscillator to generate CCLK for driving potential slave devices, and to generate address and timing for external PROM(s) containing the configuration data. Master Parallel (up or down) modes generate the CCLK signal and PROM addresses, and receive byte parallel data, which is internally serialized

into the LCA data-frame format. The up and down selection generates starting addresses at either zero or 3FFFF, to be compatible with different microprocessor addressing conventions. The Master Serial Mode generates CCLK and receives the configuration data in serial form from configuration data in serial form from a Xilinx serial-configuration PROM.

#### Peripheral Modes

The two Peripheral modes accept byte-wide data from a bus. A READY/BUSY status is available as a handshake signal. In the asynchronous mode, the internal oscillator generates a CCLK burst signal that serializes the byte-wide data. In the synchronous mode, an externally supplied clock input to CCLK serializes the data.

#### Slave Serial Mode

In the Slave Serial mode, the LCA device receives serial-configuration data on the rising edge of CCLK and, after loading its configuration, passes additional data out, resynchronized on the next falling edge of CCLK. Multiple slave devices with identical configurations can be wired with parallel DIN inputs so that the devices can be configured simultaneously.

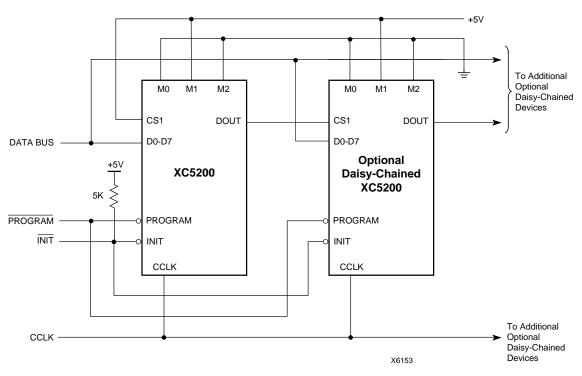

# Daisy Chaining

Multiple devices may be daisy-chained together so that they may be programmed using a single bitstream. The first device in the chain may be set to operate in any mode. All devices except the first device in the chain must be set to operate in Slave Serial mode.

All CCLK pins are tied together and the data chain passes from DOUT to DIN of successive devices along the chain.

Table 5. Configuration Modes

| Mode                     | M2 | M1 | МО | CCLK   | Data                          |

|--------------------------|----|----|----|--------|-------------------------------|

| Master Serial            | 0  | 0  | 0  | output | Bit-Serial                    |

| Slave Serial             | 1  | 1  | 1  | input  | Bit-Serial                    |

| Master Parallel up       | 1  | 0  | 0  | output | Byte-Wide, 00000 ↑            |

| Master Parallel down     | 1  | 1  | 0  | output | Byte-Wide, 3FFFF $\downarrow$ |

| Peripheral Synchronous * | 0  | 1  | 1  | input  | Byte-Wide                     |

| Peripheral Asynchronous  | 1  | 0  | 1  | output | Byte-Wide                     |

| Express                  | 0  | 1  | 0  | input  | Byte-Wide                     |

| Reserved                 | 0  | 0  | 1  | _      | _                             |

<sup>\*</sup> Peripheral Synchronous can be considered byte-wide Slave Parallel

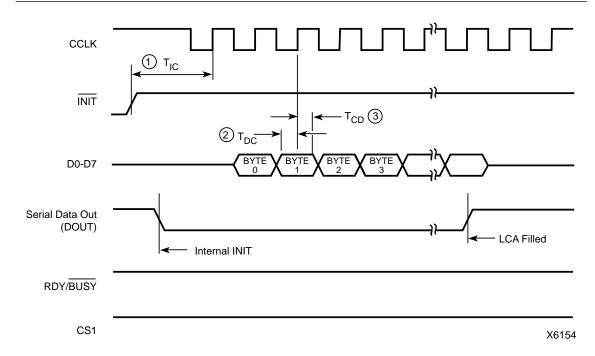

Figure 15. Express Mode

#### Express Mode

The Express mode (see Figure 15) is similar to the Slave serial mode, except that data is processed one byte per CCLK cycle instead of one bit per CCLK cycle. An external source is used to drive CCLK while byte-wide data is loaded directly into the configuration data shift registers. In this mode the XC5200 family is capable of supporting a CCLK frequency of 10 MHz, which is equivalent to an 80-MHz serial rate, because eight bits of configuration data are being loaded per CCLK cycle. An XC5210 in the Express mode, for instance, can be configured in about 2 ms. The Express mode does not support CRC error checking, but does support constant-field error checking.

In the Express configuration mode, an external signal drives the CCLK input(s) of the LCA device(s). The first bytes of parallel configuration data must be available at the D inputs of the LCA devices a short set-up time before each rising CCLK edge. Subsequent data bytes are clocked in on each consecutive rising CCLK edge. See Figure 16.

The Express mode is only supported by the XC5200 family. It may not be used, therefore, when an XC5200

device is daisy-chained with devices from other Xilinx families.

If the first device is configured in the Express mode, additional devices may be daisy-chained only if every device in the chain is also configured in the Express mode. CCLK pins are tied together and D7-D0 pins are tied together for all devices along the chain. A status signal is passed from DOUT to CS1 of successive devices along the chain. The lead device in the chain has its CS1 input tied High (or floating, since there is an internal pullup). All devices receive and recognize the preamble and length count, but frame data is accepted only when CS1 is High and the device's configuration memory is not already full. The status pin DOUT is pulled LOW two internaloscillator cycles (nominally 1 MHz per cycle) after INIT is recognized as High, and remains Low until the device's configuration memory is full. Then DOUT is pulled High to signal the next device in the chain to accept the configuration data on the D7-D0 bus.

# How to Delay Configuration After Power-Up

For details on how to delay configuration after power-up, refer to page 2-32 of the 1994 Xilinx Programmable Logic Data Book.

|      | Description                     | ption Symbol Min Max |                  | Units  |        |     |

|------|---------------------------------|----------------------|------------------|--------|--------|-----|

| CCLK | INIT (High) Setup time required | 1                    | T <sub>IC</sub>  | 5      |        | μs  |

|      | DIN Setup time required         | 2                    | T <sub>DC</sub>  | 50     |        | ns  |

|      | DIN Hold time required          | 3                    | T <sub>CD</sub>  | 0      |        | ns  |

|      | CCLK High time                  |                      | T <sub>CCH</sub> | 50     |        | ns  |

|      | CCLK Low time                   |                      | T <sub>CCL</sub> | 50     |        | ns  |

|      | CCLK Frequency                  |                      | F <sub>cc</sub>  |        | 10     | MHz |

|      |                                 |                      |                  | Prelin | ninary |     |

Figure 16. Express Mode Programming Switching Characteristics

# **Format**

Table 6 describes the XC5200 configuration data stream. Table 7 provides details of the internal configuration data structure.

# **Configuration Sequence**

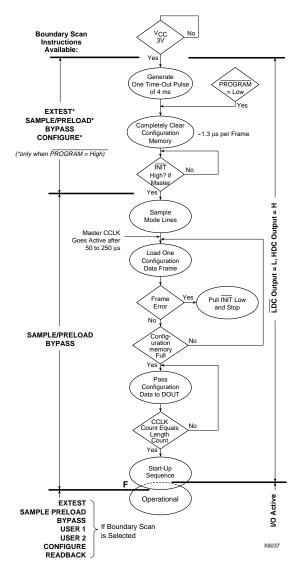

Figure 17 illustrates the XC5200 start-up sequence. It is described in detail in the sections below.

# Clear Internal Logic

When reprogramming the XC5200 chip, a contention-free state must be reached before memory initialization can begin. In this state internal control lines sequence activities in the following order: long lines are disabled, output drivers are forced Low, and interconnect lines are discharged. Each of these operations requires one cycle of the 1-MHz Initialization clock. This sequencing is important only when reprogramming, because the contention-free state is immediately entered when configuring from a power-on state.

Table 6. Unified XC5200 Bitstream Format

| Data Type                                          | Value               |

|----------------------------------------------------|---------------------|

| Fill Byte                                          | 11111111            |

| Preamble                                           | 11110010            |

| Length Counter                                     | COUNT(23:0)         |

| Fill Byte                                          | 11111111            |

| Start Byte                                         | 11111110            |

| Data Frame *                                       | DATA(N-1:0)         |

| Cyclic Redundancy Check or<br>Constant Field Check | CRC(3:0) or<br>0110 |

| Fill Nibble                                        | 1111                |

| Extend Write Cycle                                 | FFFFFF              |

| Postamble                                          | 11111110            |

| Fill Bytes (30)                                    | FFFFFF              |

# Legend:

| (unshaded) | Only once per bitstream |

|------------|-------------------------|

| (light)    | Once per data frame     |

| (dark)     | Once per device         |

Table 7. Internal Configuration Data Structure

| Device | VersaBlock<br>Array | PROM<br>Size<br>(bits) | Xilinx<br>Serial Prom<br>Needed |

|--------|---------------------|------------------------|---------------------------------|

| XC5202 | 8 x 8               | 42,448                 | XC1765                          |

| XC5204 | 10 x 12             | 70,736                 | XC1728                          |

| XC5206 | 14 x 14             | 106,320                | XC17128                         |

| XC5210 | 18 x 18             | 165,520                | XC17256                         |

| XC5215 | 22 x 22             | 237,776                | XC17256                         |

Bits per Frame = (34 x number of Rows) + 28 for the top + 28 for the bottom + 4 splitter bits + 8 start bits + 8 error check bits + 4 fill bits + 4 extended write bits

Number of Frames = (12 x number of Columns) + 7 for the left edge + 8 for the right edge + 1 splitter bit

Program Data = (Bits per Frame x Number of Frames) + 48 header bits + 8 postamble bits + 280 fill bits

PROM Size = Program Data

Figure 17. Start-up Sequence

#### Clear Address Registers

During this phase the configuration address registers are cleared to ensure that they will contain at most a single token at all times. Prior to memory initialization, the XC5200 device eliminates the possibility of multiple tokens within the address register, as is typically the case when powering on.

# Power-On Time-Out

An internal power-on reset circuit is triggered when power is applied. When  $\rm V_{CC}$  reaches the voltage at which portions of the LCA begin to operate (i.e., performs a write-and-read test of a sample pair of configuration memory bits), the programmable I/O buffers are 3-stated with active high-impedance pull-up resistors. A time-out delay — nominally 4 ms — is initiated to allow the power-supply voltage to stabilize. For correct operation the power supply must reach  $\rm V_{CC}(min)$  by the end of the time-out, and must not dip below it thereafter.

There is no distinction between master and slave modes with regard to the time-out delay. Instead, the  $\overline{\text{INIT}}$  line is used to ensure that all daisy-chained devices have completed initialization. Since XC2000 devices do not have this signal, extra care must be taken to guarantee proper operation when daisy-chaining them with XC5200 devices. For proper operation with XC3000 devices, the  $\overline{\text{RESET}}$  signal, which is used in XC3000 to delay configuration, should be connected to  $\overline{\text{INIT}}$ .

If the time-out delay is insufficient, configuration should be delayed by holding the INIT pin Low until the power supply has reached operating levels.

During all three phases — Power-on, Initialization, and Configuration — DONE is held Low; HDC, LDC, and INIT are active; DOUT is driven; and all I/O buffers are disabled.

# Initialization

This phase clears the configuration memory and establishes the configuration mode.

The configuration memory is cleared at the rate of one frame per internal clock cycle (nominally 1 MHz). An opendrain bidirectional signal,  $\overline{\text{INIT}}$ , is released when the configuration memory is completely cleared. The device then tests for the absence of an external active-low level on  $\overline{\text{INIT}}$ . The mode lines are sampled two internal clock cycles later (nominally 2  $\mu s$ ).

The master device waits an additional 32  $\mu s$  to 256  $\mu s$  (nominally 64-128  $\mu s$ ) to provide adequate time for all of the slave devices to recognize the release of  $\overline{\text{INIT}}$  as well. Then the master device enters the Configuration phase.

#### Configuration

The length counter begins counting immediately upon entry into the configuration state. In slave-mode operation it is important to wait at least two cycles of the internal 1-MHz clock oscillator after  $\overline{\text{INIT}}$  is recognized before toggling CCLK and feeding the serial bitstream. Configuration will not begin until the internal configuration logic reset is released, which happens two cycles after  $\overline{\text{INIT}}$  goes High. A master device's configuration is delayed from 32 to 256  $\mu s$  to ensure proper operation with any slave devices driven by the master device.

A preamble field at the beginning of the configuration data stream indicates that the next 24 bits represent the length count. The length count equals the total number of configuration bits needed to load the complete configuration data to all daisy-chained devices. Once the preamble and length-count values have been passed through to the next device in the daisy-chain, DOUT is held High to prevent start bits from reaching any daisy-chained devices. After fully configuring itself, the device passes serial data to downstream daisy-chained devices via DOUT until the full length count is reached.

Errors in the configuration bitstream are checked at the end of a frame of data. The device does not check the preamble or length count for errors. In a daisy-chained configuration, configuration data for downstream devices are not checked for errors. If an error is detected after reading a frame, the ERR pin (also known as INIT) is immediately pulled Low and all configuration activity ceases. However, a master or Peripheral Asynchronous device will continue outputting a configuration clock and incrementing the PROM address indefinitely even though it will never complete configuration. A reprogram or power-on must be applied to remove the device from this state.

# Start-Up and Operation

The XC5200 start-up sequence is identical to that of the XC4000 family. Each of these events may occur in any order: (a) DONE is pulled High; and/or (b) user I/Os become active; and/or (c) Internal Reset is deactivated. As a configuration option, the three events may be triggered by a user clock rather than by CCLK, or the start-up sequence may be delayed by externally holding the DONE pin Low.

In any mode, the clock cycles of the start-up sequence hare not included in the length count. The length of the bitstream is greater than the length count.

# **Pin Functions During Configuration**

| USER      | MASTER-LOW    | MASTER-HIGH   | ASYN.PERIPH   | SYN.PERIPH      | MASTER-SER   | SLAVE          |

|-----------|---------------|---------------|---------------|-----------------|--------------|----------------|

| OPERATIO  | <1:0:0>       | <1:1:0>       | <1:0:1>       | <0:1:1>         | <0:0:0>      | <1:1:1>        |

| GCK1-I/O  | A16           | A16           |               |                 |              |                |

| I/O       | A17           | A17           |               |                 |              |                |

| TDI-I/O   | TDI           | TDI           | TDI           | TDI             | TDI          | TDI            |

| TCK-I/O   | TCK           | TCK           | TCK           | TCK             | TCK          | TCK            |

| TMS-I/O   | TMS           | TMS           | TMS           | TMS             | TMS          | TMS            |

| I/O       |               |               |               |                 |              |                |

| I/O       | M1 (LOW) (I)  | M1 (HIGH) (I) | M1 (LOW) (I)  | M1 (HIGH) (I)   | M1 (LOW) (I) | VI1 (HIGH) (I) |

| I/O       | M0 (LOW) (I)  | M0 (LOW) (I)  | M0 (HIGH) (I) | M0 (HIGH) (I)   | M0 (LOW) (I) | M0 (HIGH) (I)  |

| I/O       | M2 (HIGH) (I) | M2 (HIGH) (I) | M2 (HIGH) (I) | M2 (LOW) (I)    | M2 (LOW) (I) | M2 (HIGH) (I)  |

| GCK2-I/O  |               |               |               |                 |              |                |

| I/O       | HDC (HIGH)    | HDC (HIGH)    | HDC (HIGH)    | HDC (HIGH)      | HDC (HIGH)   | HDC (HIGH)     |

| I/O       | LDC (LOW)     | LDC (LOW)     | LDC (LOW)     | LDC (LOW)       | LDC (LOW)    | LDC (LOW)      |

| I/O       | INIT-ERROR    | INIT-ERROR    | INIT-ERROR    | INIT-ERROR      | INIT-ERROR   | NIT-ERROR      |

| I/O       |               |               |               |                 |              |                |

| DONE      | DONE          | DONE          | DONE          | DONE            | DONE         | DONE           |

| PROGRAM   | PROGRAM (I)   | PROGRAM (I)   | PROGRAM (I)   | PROGRAM (I)     | PROGRAM (I)  | PROGRAM (I)    |

| I/O       | DATA 7 (I)    | DATA 7 (I)    | DATA 7 (I)    | DATA 7 (I)      |              | ( )            |

| GCK3-I/O  | ( )           | (,            | ( )           | ( )             |              |                |

| I/O       | DATA 6 (I)    | DATA 6 (I)    | DATA 6 (I)    | DATA 6 (I)      |              |                |

| I/O       | DATA 5 (I)    | DATA 5 (I)    | DATA 5 (I)    | DATA 5 (I)      |              |                |

| I/O       | =::::: (.)    |               | CSO (I)       | = : : : : : (:) |              |                |

| I/O       | DATA 4 (I)    | DATA 4 (I)    | DATA 4 (I)    | DATA 4 (I)      |              |                |

| I/O       | DATA 3 (I)    | DATA 3 (I)    | DATA 3 (I)    | DATA 3 (I)      |              |                |

| I/O       | Ditiit o (i)  | Ditiit o (i)  | RS (I)        | Ditiit (i)      |              |                |

| I/O       | DATA 2 (I)    | DATA 2 (I)    | DATA 2 (I)    | DATA 2 (I)      |              |                |

| I/O       | DATA 1 (I)    | DATA 1 (I)    | DATA 1 (I)    | DATA 1 (I)      |              |                |

| I/O       | RCLK          | RCLK          | RDY/BUSY      | RDY/BUSY        |              |                |

| I/O       | DATA 0 (I)    | DATA 0 (I)    | DATA 0 (I)    | DATA 0 (I)      | DIN (I)      | DIN (I)        |

| I/O       | DOUT          | DOUT          | DOUT          | DOUT            | DOUT         | DOUT           |

| CCLK (I)  | CCLK (O)      | CCLK (O)      | CCLK (O)      | CCLK (I)        | CCLK (O)     | CCLK (I)       |

| TDO-I/O   | TDO           | TDO           | TDO           | TDO             | TDO          | TDO            |

| 1/0       | A0            | A0            | WS (I)        | 150             | 100          | 100            |

| GCK4-I/O  | A1            | A1            | WO (I)        |                 |              |                |

| 1/0       | A2            | A2            | CS1 (I)       |                 |              |                |

| I/O       | A3            | A3            | 031 (1)       |                 |              |                |

| 1/0       | A3<br>A4      | A3<br>A4      |               |                 |              |                |

| 1/0       | A5            | A4<br>A5      |               |                 |              |                |

| I/O       | A6            | A5<br>A6      |               |                 |              |                |

| 1/0       | A6<br>A7      | A6<br>A7      |               |                 |              |                |

| I/O       | A7<br>A8      | A7<br>A8      |               |                 |              |                |

|           |               |               |               |                 |              |                |

| 1/0       | A9            | A9            |               |                 |              |                |

| I/O       | A10           | A10           |               |                 |              |                |

| I/O       | A11           | A11           |               |                 |              |                |

| I/O       | A12           | A12           |               |                 |              |                |

| I/O       | A13           | A13           |               |                 |              |                |

| I/O       | A14           | A14           |               |                 |              |                |

| I/O       | A15           | A15           |               |                 |              |                |

| ALL OTHER |               |               |               |                 |              |                |

Before and during configuration, all outputs that are not used for the configuration process are 3-stated with a .50-k $\Omega$  to 100-k $\Omega$  pull-up resistor.

<sup>(</sup>O) Represents an output

# **Pin Descriptions**

# **Permanently Dedicated Pins**

#### $V_{cc}$

Eight or more (depending on package type) connections to the nominal +5-V supply voltage. All must be connected.

#### **GND**

Eight or more (depending on package type) connections to ground. All must be connected.

#### **CCLK**

During configuration, Configuration Clock is an output of the LCA in master modes or Asynchronous Peripheral mode, but is an input to the LCA in Slave Serial mode and Synchronous Peripheral mode.

After configuration, CCLK has a weak pull-up resistor and can be selected as Readback Clock.

# **DONE**

This is a bidirectional signal with optional pull-up resistor.

As an output, it indicates the completion of the configuration process. The configuration program determines the exact timing, the clock source for the Low-to-High transition, and enable of the pull-up resistor.

As an input, a Low level on DONE can be configured to delay the global logic initialization or the enabling of outputs.

# **PROGRAM**

This is an active-Low input, held Low during configuration, that forces the LCA to clear its configuration memory.

When PROGRAM goes High, the LCA executes a complete clear cycle, before it goes into a WAIT state and releases INIT. After configuration, it has an optional pull-up resistor.

# User I/O Pins That Can Have Special Functions

#### RDY/BUSY

During peripheral modes, this pin indicates when it is appropriate to write another byte of data into the LCA device. The same status is also available on D7 in Asynchronous Peripheral mode, if a read operation is performed when the device is selected. After configuration, this is a user-programmable I/O pin.

# **RCLK**

During Master Parallel configuration, each change on the A0-15 outputs is preceded by a rising edge on RCLK, a redundant output signal. After configuration, this is a user-programmable I/O pin.

# M0, M1, M2

As mode inputs, these pins are sampled before the start of configuration to determine the configuration mode to be used.

After configuration, M0, M1, and M2 become user-programmable I/O.

### **TDO**

If boundary scan is used, this is the Test Data Output.

If boundary scan is not used, this pin becomes user-programmable I/O.

# TDI, TCK, TMS

If boundary scan is used, these pins are Test Data In, Test Clock, and Test Mode Select inputs, respectively, coming directly from the pads, bypassing the IOBs. These pins can also be used as inputs to the CLB logic after configuration is completed.

If the boundary scan option is not selected, all boundary scan functions are inhibited once configuration is completed. These pins become user-programmable I/O.

# **HDC**

High During Configuration is driven High until configuration is completed. It is available as a control output indicating that configuration is not yet completed. After configuration, this is a user-programmable I/O pin.

# **Pin Descriptions**

#### LDC

Low During Configuration is driven Low until configuration completes. It is available as a control output indicating that configuration is not yet completed. After configuration, this is a user-programmable I/O pin.

#### **INIT**

Before and during configuration, this is a bidirectional signal. An external pull-up resistor is recommended.

As an active-Low open-drain output,  $\overline{\text{INIT}}$  is held Low during the power stabilization and internal clearing of the configuration memory. As an active-Low input, it can be used to hold the LCA device in the internal WAIT state before the start of configuration. Master-mode devices stay in a WAIT state an additional 30 to 300  $\mu\text{s}$  after  $\overline{\text{INIT}}$  has gone High.

During configuration, a Low on this output indicates that a configuration data error has occurred. After configuration, this is a user-programmable I/O pin.

# GCK1 - GCK4

Four Global Inputs each drive a dedicated internal global net with short delay and minimal skew. If not used for this purpose, any of these pins is a user-programmable I/O pin.

# CS0, CS1, WS, RS

These four inputs are used in peripheral modes. The chip is selected when  $\overline{CSO}$  is Low and CS1 is High. While the chip is selected, a Low on Write Strobe ( $\overline{WS}$ ) loads the data present on the D0 - D7 inputs into the internal data buffer; a Low on Read Strobe ( $\overline{RS}$ ) changes D7 into a status output: High if Ready, Low if Busy, and D0...D6 are active Low.  $\overline{WS}$  and  $\overline{RS}$  should be mutually exclusive, but if both are Low simultaneously, the Write Strobe overrides. After configuration, these are user-programmable I/O pins.

# A0 - A17

During Master Parallel mode, these 18 output pins address the configuration EPROM. After configuration, these are user-programmable I/O pins.

# D0 - D7

During Master Parallel and peripheral configuration modes, these eight input pins receive configuration data. After configuration, they are user-programmable I/O pins.

#### DIN

During Slave Serial or Master Serial configuration modes, this is the serial configuration data input receiving data on the rising edge of CCLK.

During parallel configuration modes, this is the D0 input. After configuration, DIN is a user-programmable I/O pin.

#### **DOUT**

During configuration in any mode, this is the serial configuration data output that can drive the DIN of daisy-chained slave LCA devices. DOUT data changes on the falling edge of CCLK, 1.5 CCLK periods after it was received at the DIN input. After configuration, DOUT is a user-programmable I/O pins.

# Unrestricted User-Programmable I/O Pins

### I/O

A pin that can be configured to be input and/or output after configuration is completed. Before configuration is completed, these pins have an internal high-value pull-up resistor that defines the logical level as High.

Before and during configuration, all outputs that are not used for the configuration process are 3-stated with a 50-k $\Omega$  to 100-k $\Omega$  pull-up resistor.

# **Absolute Maximum Ratings**

| Symbol           | Description                                              |                              | Units |

|------------------|----------------------------------------------------------|------------------------------|-------|

| V <sub>cc</sub>  | Supply voltage relative to GND                           | -0.5 to +7.0                 | V     |

| V <sub>IN</sub>  | Input voltage with respect to GND                        | -0.5 to V <sub>CC</sub> +0.5 | V     |

| V <sub>TS</sub>  | Voltage applied to 3-state output                        | -0.5 to V <sub>CC</sub> +0.5 | V     |

| T <sub>STG</sub> | Storage temperature (ambient)                            | -65 to +150                  | °C    |

| T <sub>SOL</sub> | Maximum soldering temperature (10 s @ 1/16 in. = 1.5 mm) | +260                         | °C    |

| T,               | Junction temperature in plastic packages                 | +125                         | °C    |

| .1               | Junction temperature in ceramic packages                 | +150                         | °C    |

Note: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

# **Operating Conditions**

| Symbol           | Description                                              | Min  | Max             | Units           |

|------------------|----------------------------------------------------------|------|-----------------|-----------------|

|                  | Supply voltage relative to GND Commercial: 0°C to 70°C   | 4.75 | 5.25            | V               |

| V <sub>cc</sub>  | Supply voltage relative to GND Industrial: -40°C to 85°C | 4.5  | 5.5             | V               |

|                  | Supply voltage relative to GND Military: -55°C to 125°C  | 4.5  | 5.5             | V               |

| V <sub>IHT</sub> | High-level input voltage — TTL configuration             | 2.0  | V <sub>CC</sub> | V               |

| V <sub>ILT</sub> | Low-level input voltage — TTL configuration              | 0    | 0.8             | V               |

| V <sub>IHC</sub> | High-level input voltage — CMOS configuration            | 70%  | 100%            | V <sub>cc</sub> |

| V <sub>ILC</sub> | Low-level input voltage — CMOS configuration             | 0    | 20%             | V <sub>cc</sub> |

| T <sub>IN</sub>  | Input signal transition time                             |      | 250             | ns              |

# **DC Characteristics Over Operating Conditions**

| Symbol           | Description                                                                       | Min  | Max  | Units |

|------------------|-----------------------------------------------------------------------------------|------|------|-------|

| V <sub>OH</sub>  | High-level output voltage @ I <sub>OH</sub> = -8.0 mA, V <sub>CC</sub> min        | 3.86 |      | ٧     |

| V <sub>OL</sub>  | Low-level output voltage @ I <sub>OL</sub> = 8.0 mA, V <sub>CC</sub> max (Note 1) |      | 0.4  | ٧     |

| I <sub>cco</sub> | Quiescent LCA supply current (Note 1)                                             |      | 15   | mA    |

| I <sub>IL</sub>  | Leakage current                                                                   | -10  | +10  | μА    |

| C <sub>IN</sub>  | Input capacitance (sample tested)                                                 |      | 15   | pF    |

| I <sub>RIN</sub> | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V (sample tested)                | 0.02 | 0.25 | mA    |

Note: 1. With no output current loads, all package pins at  $V_{CC}$  or GND, and the LCA configured with a MakeBits tie option.

# **Global Buffer Switching Characteristic Guidelines**

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more detailed, more precise, and more up-to-date timing information, use the values provided by the XACT timing calculator and used in the simulator.

|                                                            | Spe                | Speed Grade |             | Speed Grade |             | -5 | -4 |

|------------------------------------------------------------|--------------------|-------------|-------------|-------------|-------------|----|----|

| Description                                                | Symbol             | Device      | Max<br>(ns) | Max<br>(ns) | Max<br>(ns) |    |    |

| Global Signal Distribution                                 |                    |             |             |             |             |    |    |

| From pad through global buffer, to any clock (CK)          | T <sub>BUFG</sub>  | XC5202      |             |             |             |    |    |

|                                                            | Boro               | XC5204      |             |             |             |    |    |

|                                                            |                    | XC5206      | 9.4         | 8.8         |             |    |    |

|                                                            |                    | XC5210      | 9.4         | 8.8         |             |    |    |

|                                                            |                    | XC5215      |             |             |             |    |    |

| Internal Clock to Output Pad Delay                         |                    |             |             |             |             |    |    |

| From clock (CK) to output pad (fast), using direct connect | T <sub>OKPOF</sub> | XC5202      |             |             |             |    |    |

| between Q and output (O)                                   | Old Ol             | XC5204      |             |             |             |    |    |