# QPRO XQ4000E/EX QML High-Reliability FPGAs

DS021 (v2.2) June 25, 2000

#### **Product Specification**

### **Product Features**

- Certified to MIL-PRF-38535, appendix A QML (Qualified Manufacturers Listing)

- Also available under the following Standard Microcircuit Drawings (SMD)

XC4005E 5962-97522 XC4010E 5962-97523 5962-97524 XC4013E XC4025E 5962-97525 XC4028EX 5962-98509

- For more information contact the Defense Supply Center Columbus (DSCC)

- http://www.dscc.dla.mis/v/va/smd/smdsrch.html

- System featured Field-Programmable Gate Arrays

- Select-RAM™ memory: on-chip ultra-fast RAM with

- Synchronous write option WW.DZSG.COM

- **Dual-port RAM option**

- Abundant flip-flops

- Flexible function generators

- Dedicated high-speed carry logic

- Wide edge decoders on each edge

- Hierarchy of interconnect lines

- Internal 3-state bus capability

- Eight global low-skew clock or signal distribution networks

- System Performance beyond 60 MHz

- Flexible Array Architecture

- Low Power Segmented Routing Architecture

- Systems-Oriented Features

- IEEE 1149.1-compatible boundary scan logic

- Individually programmable output slew rate

- Programmable input pull-up or pull-down resistors

- 12 mA sink current per XQ4000E/EX output

- Configured by Loading Binary File

- Unlimited reprogrammability

- Readback Capability

- Program verification

- Internal node observability

- Backward Compatible with XC4000 Devices

- Development System runs on most common computer platforms

- Interfaces to popular design environments

- Fully automatic mapping, placement and routing

- Interactive design editor for design optimization

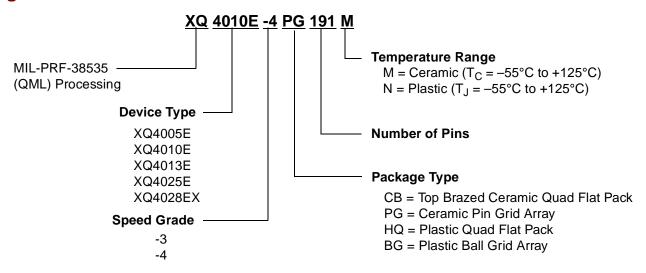

- Available Speed Grades:

- XQ4000E -3 for plastic packages only

- -4 for ceramic packages only

- XQ4028EX -4 for all packages

### **More Information**

For more information refer to Xilinx XC4000E and XC4000X series Field Programmable Gate Arrays product specification. This data sheet contains pinout tables for XQ4010E only. Refer to Xilinx web site for pinout tables for other devices. (Pinouts for XQ4000E/EX are identical to XC4000E/EX.)

(http://www.xilinx.com/partinfo/databook.htm)

Table 1: XQ4000E/EX Field Programmable Gate Arrays

| Device   | Max.<br>Logic<br>Gates<br>(No RAM) | Max.<br>RAM Bits<br>(No<br>Logic) | Typical<br>Gate Range<br>(Logic and<br>RAM) <sup>(1)</sup> | CLB<br>Matrix | Total<br>CLBs | Number<br>of<br>Flip-Flops | Max. Decode Inputs per Side | Max.<br>User<br>I/O | Packages                            |

|----------|------------------------------------|-----------------------------------|------------------------------------------------------------|---------------|---------------|----------------------------|-----------------------------|---------------------|-------------------------------------|

| XQ4005E  | 5,000                              | 6,272                             | 3,000 - 9,000                                              | 14 x 14       | 196           | 616                        | 42                          | 112                 | PG156,<br>CB164                     |

| XQ4010E  | 10,000                             | 12,800                            | 7,000 - 20,000                                             | 20 x 20       | 400           | 1,120                      | 60                          | 160                 | PG191,<br>CB196,<br>HQ208           |

| XQ4013E  | 13,000                             | 18,432                            | 10,000 - 30,000                                            | 24 x 24       | 576           | 1,536                      | 72                          | 192                 | PG223,<br>CB228,<br>HQ240           |

| XQ4025E  | 25,000                             | 32,768                            | 15,000 - 45,000                                            | 32 x 32       | 1,024         | 2,560                      | 96                          | 256                 | PG299,<br>CB228                     |

| XQ4028EX | 28,000                             | 32,768                            | 18,000 - 50,000                                            | 32 x 32       | 1,024         | 2,560                      | 96                          | 256                 | PG299,<br>CB228,<br>HQ240,<br>BG352 |

#### Notes:

# **XQ4000E Switching Characteristics**

# XQ4000E Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Description                                        |                 |                          | Units |

|------------------|----------------------------------------------------|-----------------|--------------------------|-------|

| V <sub>CC</sub>  | Supply voltage relative to GND                     |                 | -0.5 to +7.0             | V     |

| V <sub>IN</sub>  | Input voltage relative to GND <sup>(2)</sup>       |                 | $-0.5$ to $V_{CC}$ + 0.5 | V     |

| V <sub>TS</sub>  | Voltage applied to High-Z output <sup>(2)</sup>    |                 | $-0.5$ to $V_{CC}$ + 0.5 | V     |

| T <sub>STG</sub> | Storage temperature (ambient)                      |                 | -65 to +150              | °C    |

| T <sub>SOL</sub> | Maximum soldering temperature (10s @ 1/16 in. = 1. | 5 mm)           | +260                     | °C    |

| TJ               | Junction temperature                               | Ceramic package | +150                     | °C    |

|                  |                                                    | Plastic package | +125                     | °C    |

- Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions

is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

- Maximum DC excursion above V<sub>CC</sub> or below Ground must be limited to either 0.5V or 10 mA, whichever is easier to achieve. During transitions, the device pins may undershoot to –2.0V or overshoot to V<sub>CC</sub> + 2.0V, provided this over or undershoot lasts less than 10 ns and with the forcing current being limited to 200 mA.

<sup>1.</sup> Max values of Typical Gate Range include 20-30% of CLBs used as RAM.

# **XQ4000E** Recommended Operating Conditions<sup>(1,2)</sup>

| Symbol          | Description                                                      |             | Min | Max             | Units           |

|-----------------|------------------------------------------------------------------|-------------|-----|-----------------|-----------------|

| V <sub>CC</sub> | Supply voltage relative to GND, $T_J = -55^{\circ}C$ to +125°C   | Plastic     | 4.5 | 5.5             | V               |

|                 | Supply voltage relative to GND, T <sub>C</sub> = −55°C to +125°C | Ceramic     | 4.5 | 5.5             | V               |

| V <sub>IH</sub> | High-Level Input Voltage                                         | TTL inputs  | 2.0 | V <sub>CC</sub> | V               |

|                 |                                                                  | CMOS inputs | 70% | 100%            | V <sub>CC</sub> |

| V <sub>IL</sub> | Low-Level Input Voltage                                          | TTL inputs  | 0   | 0.8             | V               |

|                 |                                                                  | CMOS inputs | 0   | 20%             | V <sub>CC</sub> |

| T <sub>IN</sub> | Input signal transition time                                     |             | -   | 250             | ns              |

#### Notes:

- 1. At junction temperatures above those listed as Operating Conditions, all delay parameters increase by 0.35% per °C.

- 2. Input and output measurement threshold are 1.5V for TTL and 2.5V for CMOS.

# **XQ4000E DC Characteristics Over Recommended Operating Conditions**

| Symbol           | Description                                                                              |              | Min                   | Max   | Units |

|------------------|------------------------------------------------------------------------------------------|--------------|-----------------------|-------|-------|

| V <sub>OH</sub>  | High-level output voltage @ I <sub>OH</sub> = -4.0 mA, V <sub>CC</sub> min               | TTL outputs  | 2.4                   | -     | V     |

|                  | High-level output voltage @ I <sub>OH</sub> = −1.0 mA, V <sub>CC</sub> min               | CMOS outputs | V <sub>CC</sub> - 0.5 | -     | V     |

| V <sub>OL</sub>  | Low-level output voltage @ I <sub>OL</sub> = 12.0 mA, V <sub>CC</sub> min <sup>(1)</sup> | TTL outputs  | -                     | 0.4   | V     |

|                  |                                                                                          | CMOS outputs | -                     | 0.4   | V     |

| I <sub>cco</sub> | Quiescent FPGA supply current <sup>(2)</sup>                                             |              | -                     | 50    | mA    |

| Ι <sub>L</sub>   | Input or output leakage current                                                          |              | -10                   | +10   | μΑ    |

| C <sub>IN</sub>  | Input capacitance (sample tested)                                                        |              | -                     | 16    | pF    |

| I <sub>RIN</sub> | ad pull-up (when selected) at V <sub>IN</sub> = 0V (sample tested) <sup>(3)</sup>        |              | -0.02                 | -0.25 | mA    |

| I <sub>RLL</sub> | Horizontal longline pull-up (when selected) at logic Low                                 | 3)           | 0.2                   | 2.5   | mA    |

- 1. With 50% of the outputs simultaneously sinking 12 mA, up to a maximum of 64 pins.

- 2. With no output current loads, no active input or Longline pull-up resistors, all package pins at V<sub>CC</sub> or GND, and the FPGA configured with the development system Tie option.

- 3. Characterized Only.

# XQ4000E Switching Characteristic Guidelines

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

When fewer vertical clock lines are connected, the clock distribution is faster; when multiple clock lines per column are driven from the same global clock, the delay is longer. For more specific, more precise, and worst-case guaranteed

data, reflecting the actual routing structure, use the values provided by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature).

Note: -3 Speed Grade only applies to XQ4010E and XQ4013E Plastic Package options only. -4 Speed Grade applies to all XQ devices and is only available in Ceramic Packages only.

### **XQ4000E Global Buffer Switching Characteristics**

|                 |                                                   |         | -3(1) | -4(2) |       |

|-----------------|---------------------------------------------------|---------|-------|-------|-------|

| Symbol          | Description                                       | Device  | Max   | Max   | Units |

| T <sub>PG</sub> | From pad through primary buffer, to any clock K   | XQ4005E | -     | 7.0   | ns    |

|                 |                                                   | XQ4010E | 6.3   | 11.0  | ns    |

|                 |                                                   | XQ4013E | 6.8   | 11.5  | ns    |

|                 |                                                   | XQ4025E | -     | 12.5  | ns    |

| T <sub>SG</sub> | From pad through secondary buffer, to any clock K | XQ4005E | -     | 7.5   | ns    |

|                 |                                                   | XQ4010E | 6.8   | 11.5  | ns    |

|                 |                                                   | XQ4013E | 7.3   | 12.0  | ns    |

|                 |                                                   | XQ4025E | -     | 13.0  | ns    |

- 1. For plastic package options only.

- 2. For ceramic package options only.

## **XQ4000E Horizontal Longline Switching Characteristic Guidelines**

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist.

These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all XQ4000E devices unless otherwise noted.

The following guidelines reflect worst-case values over the recommended operating conditions.

|                  |                                                                                         |         | -3   | -4   |       |

|------------------|-----------------------------------------------------------------------------------------|---------|------|------|-------|

| Symbol           | Description                                                                             | Device  | Max  | Max  | Units |

| TBUF Driv        | ing a Horizontal Longline (LL):                                                         |         | :    |      | :     |

| T <sub>IO1</sub> | I going High or Low to LL going High or Low, while T is Low.                            | XQ4005E | -    | 5.0  | ns    |

|                  | Buffer is constantly active. <sup>(1)</sup>                                             | XQ4010E | 6.4  | 8.0  | ns    |

|                  |                                                                                         | XQ4013E | 7.2  | 9.0  | ns    |

|                  |                                                                                         | XQ4025E | -    | 11.0 | ns    |

| T <sub>IO2</sub> | I going Low to LL going from resistive pull-up High to active Low.                      | XQ4005E | -    | 6.0  | ns    |

|                  | TBUF configured as open-drain. <sup>(1)</sup>                                           | XQ4010E | 6.9  | 10.5 | ns    |

|                  |                                                                                         | XQ4013E | 7.7  | 11.0 | ns    |

|                  | Tour T going Low to LL going from resistive pull-up or fleeting High to                 | XQ4025E | -    | 12.0 | ns    |

| T <sub>ON</sub>  | T going Low to LL going from resistive pull-up or floating High to                      | XQ4005E | -    | 7.0  | ns    |

|                  | active Low. TBUF configured as open-drain or active buffer with I = Low. <sup>(1)</sup> | XQ4010E | 7.3  | 8.5  | ns    |

|                  | I = LOW.                                                                                | XQ4013E | 7.5  | 8.7  | ns    |

|                  |                                                                                         | XQ4025E | -    | 11.0 | ns    |

| T <sub>OFF</sub> | T going High to TBUF going inactive, not driving LL.                                    | XQ4005E | -    | 1.8  | ns    |

|                  |                                                                                         | XQ4010E | 1.5  | 1.8  | ns    |

|                  |                                                                                         | XQ4013E | 1.5  | 1.8  | ns    |

|                  |                                                                                         | XQ4025E | -    | 1.8  | ns    |

| T <sub>PUS</sub> | T going High to LL going from Low to High, pulled up by a single                        | XQ4005E | -    | 23.0 | ns    |

|                  | resistor. <sup>(1)</sup>                                                                | XQ4010E | 22.0 | 29.0 | ns    |

|                  |                                                                                         | XQ4013E | 26.0 | 32.0 | ns    |

|                  |                                                                                         | XQ4025E | -    | 42.0 | ns    |

| T <sub>PUF</sub> | T going High to LL going from Low to High, pulled up by two                             | XQ4005E | -    | 10.0 | ns    |

|                  | resistors. <sup>(1)</sup>                                                               | XQ4010E | 11.0 | 13.5 | ns    |

|                  |                                                                                         | XQ4013E | 13.0 | 15.0 | ns    |

|                  |                                                                                         | XQ4025E | -    | 18.0 | ns    |

#### Notes:

1. These values include a minimum load. Use the static timing analyzer to determine the delay for each destination.

## **XQ4000E Wide Decoder Switching Characteristic Guidelines**

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist.

These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all XQ4000E devices unless otherwise noted.

The following guidelines reflect worst-case values over the recommended operating conditions.

|                   |                                                        |         | -3   | -4   |       |

|-------------------|--------------------------------------------------------|---------|------|------|-------|

| Symbol            | Description <sup>(1,2)</sup>                           | Device  | Max  | Max  | Units |

| T <sub>WAF</sub>  | Full length, both pull-ups, inputs from IOB I-pins     | XQ4005E | -    | 9.5  | ns    |

|                   |                                                        | XQ4010E | 9.0  | 15.0 | ns    |

|                   |                                                        | XQ4013E | 11.0 | 16.0 | ns    |

|                   |                                                        | XQ4025E | -    | 18.0 | ns    |

| T <sub>WAFL</sub> | Full length, both pull-ups, inputs from internal logic | XQ4005E | -    | 12.5 | ns    |

|                   |                                                        | XQ4010E | 11.0 | 18.0 | ns    |

|                   |                                                        | XQ4013E | 13.0 | 19.0 | ns    |

|                   |                                                        | XQ4025E | -    | 21.0 | ns    |

| T <sub>WAO</sub>  | Half length, one pull-up, inputs from IOB I-pins       | XQ4005E | -    | 10.5 | ns    |

|                   |                                                        | XQ4010E | 10.0 | 16.0 | ns    |

|                   |                                                        | XQ4013E | 12.0 | 17.0 | ns    |

|                   |                                                        | XQ4025E | -    | 19.0 | ns    |

| T <sub>WAOL</sub> | Half length, one pull-up, inputs from internal logic   | XQ4005E | -    | 12.5 | ns    |

|                   |                                                        | XQ4010E | 12.0 | 18.0 | ns    |

|                   |                                                        | XQ4013E | 14.0 | 19.0 | ns    |

|                   |                                                        | XQ4025E | -    | 21.0 | ns    |

- 1. These delays are specified from the decoder input to the decoder output.

- 2. Fewer than the specified number of pull-up resistors can be used, if desired. Using fewer pull-ups reduces power consumption but increases delays. Use the static timing analyzer to determine delays if fewer pull-ups are used.

## **XQ4000E CLB Switching Characteristic Guidelines**

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist.

These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all XQ4000E devices unless otherwise noted.

|                    |                                                                  |     | -3   | -4  |     |              |

|--------------------|------------------------------------------------------------------|-----|------|-----|-----|--------------|

| Symbol             | Description                                                      | Min | Max  | Min | Max | Units        |

| Combinator         | ial Delays                                                       |     |      |     | !   | <del>'</del> |

| T <sub>ILO</sub>   | F/G inputs to X/Y outputs                                        | -   | 2.01 | -   | 2.7 | ns           |

| T <sub>IHO</sub>   | F/G inputs via H to X/Y outputs                                  | -   | 4.3  | -   | 4.7 | ns           |

| T <sub>HH0O</sub>  | C inputs via SR through H to X/Y outputs                         | -   | 3.3  | -   | 4.1 | ns           |

| T <sub>HH1O</sub>  | C inputs via H to X/Y outputs                                    | -   | 3.6  | -   | 3.7 | ns           |

| T <sub>HH2O</sub>  | C inputs via D <sub>IN</sub> through H to X/Y outputs            | -   | 3.6  | -   | 4.5 | ns           |

| CLB Fast Ca        | arry Logic                                                       |     |      |     |     |              |

| T <sub>OPCY</sub>  | Operand inputs (F1, F2, G1, G4) to C <sub>OUT</sub>              | -   | 2.6  | -   | 3.2 | ns           |

| T <sub>ASCY</sub>  | Add/Subtract input (F3) to C <sub>OUT</sub>                      | -   | 4.4  | -   | 5.5 | ns           |

| T <sub>INCY</sub>  | Initialization inputs (F1, F3) to C <sub>OUT</sub>               | -   | 1.7  | -   | 1.7 | ns           |

| T <sub>SUM</sub>   | C <sub>IN</sub> through function generators to X/Y outputs       | -   | 3.3  | -   | 3.8 | ns           |

| T <sub>BYP</sub>   | C <sub>IN</sub> to C <sub>OUT</sub> , bypass function generators | -   | 0.7  | -   | 1.0 | ns           |

| Sequential I       | Delays                                                           |     | -    | 1   | -   |              |

| T <sub>CKO</sub>   | Clock K to outputs Q                                             | -   | 2.8  | -   | 3.7 | ns           |

| Setup Time         | before Clock K                                                   |     | 1    |     | 1   | <b>"</b>     |

| T <sub>ICK</sub>   | F/G inputs                                                       | 3.0 | -    | 4.0 | -   | ns           |

| T <sub>IHCK</sub>  | F/G inputs via H                                                 | 4.6 | -    | 6.1 | -   | ns           |

| T <sub>HH0CK</sub> | C inputs via H0 through H                                        | 3.6 | -    | 4.5 | -   | ns           |

| T <sub>HH1CK</sub> | C inputs via H1 through H                                        | 4.1 | -    | 5.0 | -   | ns           |

| T <sub>HH2CK</sub> | C inputs via H2 through H                                        | 3.8 | -    | 4.8 | -   | ns           |

| T <sub>DICK</sub>  | C inputs via D <sub>IN</sub>                                     | 2.4 | -    | 3.0 | -   | ns           |

| T <sub>ECCK</sub>  | C inputs via EC                                                  | 3.0 | -    | 4.0 | -   | ns           |

| T <sub>RCK</sub>   | C inputs via S/R, going Low (inactive)                           | 4.0 | -    | 4.2 | -   | ns           |

| T <sub>CCK</sub>   | C <sub>IN</sub> input via F/G                                    | 2.1 | -    | 2.5 | -   | ns           |

| T <sub>CHCK</sub>  | C <sub>IN</sub> input via F/G and H                              | 3.5 | -    | 4.2 | -   | ns           |

# **XQ4000E CLB Switching Characteristic Guidelines** (continued)

|                       |                                                               | -           | 3    | -4   |      |       |

|-----------------------|---------------------------------------------------------------|-------------|------|------|------|-------|

| Symbol                | Description                                                   | Min         | Max  | Min  | Max  | Units |

| Hold Time a           | fter Clock K                                                  |             | '    |      |      |       |

| T <sub>CKI</sub>      | F/G inputs                                                    | 0           | -    | 0    | -    | ns    |

| T <sub>CKIH</sub>     | F/G inputs via H                                              | 0           | -    | 0    | -    | ns    |

| T <sub>CKHH0</sub>    | C inputs via H0 through H                                     | 0           | -    | 0    | -    | ns    |

| T <sub>CKHH1</sub>    | C inputs via H1 through H                                     | 0           | -    | 0    | -    | ns    |

| T <sub>CKHH2</sub>    | C inputs via H2 through H                                     | 0           | -    | 0    | -    | ns    |

| T <sub>CKDI</sub>     | C inputs via DIN/H2                                           | 0           | -    | 0    | -    | ns    |

| T <sub>CKEC</sub>     | C inputs via EC                                               | 0           | -    | 0    | -    | ns    |

| T <sub>CKR</sub>      | C inputs via SR, going Low (inactive)                         | 0           | -    | 0    | -    | ns    |

| Clock                 |                                                               |             |      | 1    |      |       |

| T <sub>CH</sub>       | Clock High time                                               | 4.0         | -    | 4.5  | -    | ns    |

| T <sub>CL</sub>       | Clock Low time                                                | 4.0         | -    | 4.5  | -    | ns    |

| Set/Reset D           | irect                                                         |             | -    |      |      |       |

| T <sub>RPW</sub>      | Width (High)                                                  | 4.0         | -    | 5.5  | -    | ns    |

| T <sub>RIO</sub>      | Delay from C inputs via S/R, going High to Q                  | -           | 4.0  | -    | 6.5  | ns    |

| /laster Set/l         | Reset <sup>(1)</sup>                                          |             |      |      |      |       |

| $T_{MRW}$             | Width (High or Low)                                           | 11.5        | -    | 13.0 | -    | ns    |

| T <sub>MRQ</sub>      | Delay from Global Set/Reset net to Q                          | -           | 18.7 | -    | 23.0 | ns    |

| T <sub>MRK</sub>      | Global Set/Reset inactive to first active clock K edge        | -           | 18.7 | -    | 23.0 | ns    |

| F <sub>TOG</sub>      | Toggle Frequency <sup>(2)</sup>                               | -           | 125  | -    | 111  | MHz   |

| lotes:<br>. Timing is | based on the XC4005E. For other devices see the static timing | g analyzer. |      |      | •    |       |

<sup>2.</sup> Export Control Max. flip-flop toggle rate.

### XQ4000E CLB Edge-Triggered (Synchronous) RAM Switching Characteristic Guidelines

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported

by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all XQ4000E/EX devices unless otherwise noted.

### Single-Port RAM Synchronous (Edge-Triggered) Write Operation Characteristics

|                   |                                           |      | -    | -3   |      | -4   |       |

|-------------------|-------------------------------------------|------|------|------|------|------|-------|

| Symbol            | Write Operation Description               | Size | Min  | Max  | Min  | Max  | Units |

| T <sub>WCS</sub>  | Address write cycle time (clock K period) | 16x2 | 14.4 | -    | 15.0 | -    | ns    |

| T <sub>WCTS</sub> |                                           | 32x1 | 14.4 | -    | 15.0 | -    | ns    |

| T <sub>WPS</sub>  | Clock K pulse width (active edge)         | 16x2 | 7.2  | 1 ms | 7.5  | 1 ms | ns    |

| T <sub>WPTS</sub> |                                           | 32x1 | 7.2  | 1 ms | 7.5  | 1 ms | ns    |

| T <sub>ASS</sub>  | Address setup time before clock K         | 16x2 | 2.4  | -    | 2.8  | -    | ns    |

| T <sub>ASTS</sub> |                                           | 32x1 | 2.4  | -    | 2.8  | -    | ns    |

| T <sub>AHS</sub>  | Address hold time after clock K           | 16x2 | 0    | -    | 0    | -    | ns    |

| T <sub>AHTS</sub> |                                           | 32x1 | 0    | -    | 0    | -    | ns    |

| T <sub>DSS</sub>  | D <sub>IN</sub> setup time before clock K | 16x2 | 3.2  | -    | 3.5  | -    | ns    |

| T <sub>DSTS</sub> |                                           | 32x1 | 1.9  | -    | 2.5  | -    | ns    |

| T <sub>DHS</sub>  | D <sub>IN</sub> hold time after clock K   | 16x2 | 0    | -    | 0    | -    | ns    |

| T <sub>DHTS</sub> |                                           | 32x1 | 0    | -    | 0    | -    | ns    |

| T <sub>WSS</sub>  | WE setup time before clock K              | 16x2 | 2.0  | -    | 2.2  | -    | ns    |

| T <sub>WSTS</sub> |                                           | 32x1 | 2.0  | -    | 2.2  | -    | ns    |

| T <sub>WHS</sub>  | WE hold time after clock K                | 16x2 | 0    | -    | 0    | -    | ns    |

| T <sub>WHTS</sub> |                                           | 32x1 | 0    | -    | 0    | -    | ns    |

| T <sub>WOS</sub>  | Data valid after clock K                  | 16x2 | 8.8  | -    | -    | 10.3 | ns    |

| T <sub>WOTS</sub> |                                           | 32x1 | 10.3 | -    | -    | 11.6 | ns    |

#### Notes:

- 1. Timing for the 16x1 RAM option is identical to 16x2 RAM timing.

- 2. Applicable Read timing specifications are identical to Level-Sensitive Read timing.

## **Dual-Port RAM Synchronous (Edge-Triggered) Write Operation Characteristics**

|                   |                                           |                     | -    | 3    | -    | 4    |       |

|-------------------|-------------------------------------------|---------------------|------|------|------|------|-------|

| Symbol            | Write Operation Description               | Size <sup>(1)</sup> | Min  | Max  | Min  | Max  | Units |

| T <sub>WCDS</sub> | Address write cycle time (clock K period) | 16x1                | 14.4 |      | 15.0 |      | ns    |

| T <sub>WPDS</sub> | Clock K pulse width (active edge)         | 16x1                | 7.2  | 1 ms | 7.5  | 1 ms | ns    |

| T <sub>ASDS</sub> | Address setup time before clock K         | 16x1                | 2.5  | -    | 2.8  | -    | ns    |

| T <sub>AHDS</sub> | Address hold time after clock K           | 16x1                | 0    | -    | 0    | -    | ns    |

| T <sub>DSDS</sub> | D <sub>IN</sub> setup time before clock K | 16x1                | 2.5  | -    | 2.2  | -    | ns    |

| T <sub>DHDS</sub> | D <sub>IN</sub> hold time after clock K   | 16x1                | 0    | -    | 0    | -    | ns    |

| T <sub>WSDS</sub> | WE setup time before clock K              | 16x1                | 1.8  | -    | 2.2  | -    | ns    |

| T <sub>WHDS</sub> | WE hold time after clock K                | 16x1                | 0    | -    | 0.3  | -    | ns    |

| T <sub>WODS</sub> | Data valid after clock K                  | 16x1                | -    | 7.8  | -    | 10.0 | ns    |

#### Notes:

1. Applicable Read timing specifications are identical to Level-Sensitive Read timing.

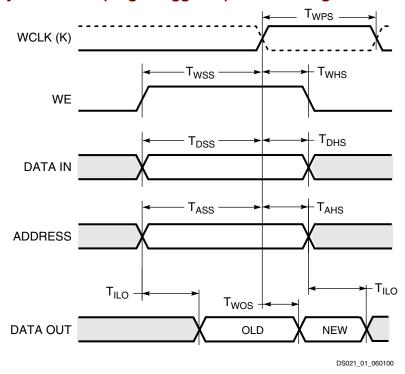

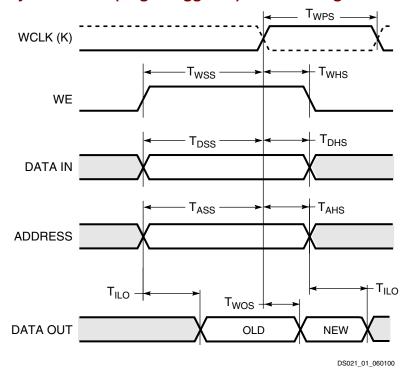

# XQ4000E CLB RAM Synchronous (Edge-Triggered) Write Timing Waveform

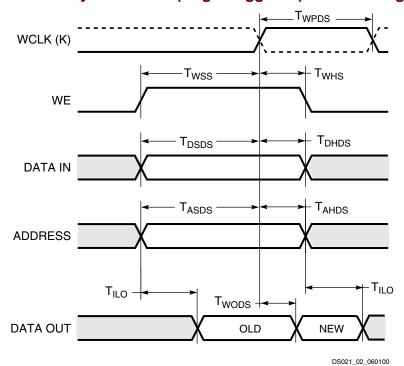

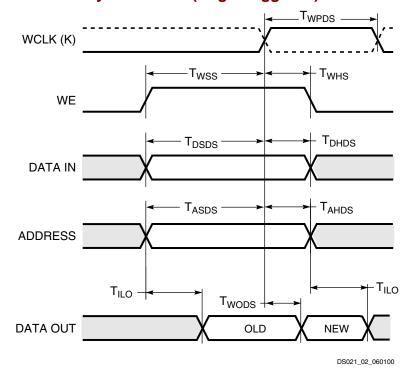

# XQ4000E CLB Dual-Port RAM Synchronous (Edge-Triggered) Write Timing Waveform

## **XQ4000E CLB Level-Sensitive RAM Switching Characteristic Guidelines**

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported

by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all XQ4000E devices unless otherwise noted.

|                   |                                                                      |      | -   | 3   | -   | -4   |       |

|-------------------|----------------------------------------------------------------------|------|-----|-----|-----|------|-------|

| Symbol            | Single Port RAM                                                      | Size | Min | Max | Min | Max  | Units |

| Write Ope         | ration                                                               | -    |     | !   | !   |      |       |

| $T_WC$            | Address write cycle time                                             | 16x2 | 8.0 | -   | 8.0 | -    | ns    |

| T <sub>WCT</sub>  |                                                                      | 32x1 | 8.0 | -   | 8.0 | -    | ns    |

| $T_WP$            | Write Enable pulse width (High)                                      | 16x2 | 4.0 | -   | 4.0 | -    | ns    |

| T <sub>WPT</sub>  |                                                                      | 32x1 | 4.0 | -   | 4.0 | -    | ns    |

| T <sub>AS</sub>   | Address setup time before WE                                         | 16x2 | 2.0 | -   | 2.0 | -    | ns    |

| T <sub>AST</sub>  |                                                                      | 32x1 | 2.0 | -   | 2.0 | -    | ns    |

| T <sub>AH</sub>   | Address hold time after end of WE                                    | 16x2 | 2.0 | -   | 2.5 | -    | ns    |

| T <sub>AHT</sub>  |                                                                      | 32x1 | 2.0 | -   | 2.0 | -    | ns    |

| T <sub>DS</sub>   | D <sub>IN</sub> setup time before end of WE                          | 16x2 | 2.2 | -   | 4.0 | -    | ns    |

| T <sub>DST</sub>  |                                                                      | 32x1 | 2.2 | -   | 5.0 | -    | ns    |

| T <sub>DH</sub>   | D <sub>IN</sub> hold time after end of WE                            | 16x2 | 2.0 | -   | 2.0 | -    | ns    |

| T <sub>DHT</sub>  |                                                                      | 32x1 | 2.0 | -   | 2.0 | -    | ns    |

| Read Oper         | ration                                                               |      | 1   |     |     | '    |       |

| T <sub>RC</sub>   | Address read cycle time                                              | 16x2 | 3.1 | -   | 4.5 | -    | ns    |

| T <sub>RCT</sub>  |                                                                      | 32x1 | 5.5 | -   | 6.5 | -    | ns    |

| T <sub>ILO</sub>  | Data valid after address change (no Write Enable)                    | 16x2 | -   | 1.8 | -   | 2.7  | ns    |

| T <sub>IHO</sub>  |                                                                      | 32x1 | -   | 3.2 | -   | 4.7  | ns    |

| Read Oper         | ration, Clocking Data into Flip-Flop                                 |      |     | •   | •   |      |       |

| T <sub>ICK</sub>  | Address setup time before clock K                                    | 16x2 | 3.0 | -   | 4.0 | -    | ns    |

| T <sub>IHCK</sub> |                                                                      | 32x1 | 4.6 | -   | 6.1 | -    | ns    |

| Read Duri         | ng Write                                                             |      |     | •   | •   |      |       |

| T <sub>WO</sub>   | Data valid after WE goes active (D <sub>IN</sub> stable before WE)   | 16x2 | -   | 6.0 | -   | 10.0 | ns    |

| T <sub>WOT</sub>  |                                                                      | 32x1 | -   | 7.3 | -   | 12.0 | ns    |

| T <sub>DO</sub>   | Data valid after D <sub>IN</sub> (D <sub>IN</sub> changes during WE) | 16x2 | -   | 6.6 | -   | 9.0  | ns    |

| T <sub>DOT</sub>  |                                                                      | 32x1 | -   | 7.6 | -   | 11.0 | ns    |

| Read Duri         | ng Write, Clocking Data into Flip-Flop                               |      |     |     |     |      |       |

| T <sub>WCK</sub>  | WE setup time before clock K                                         | 16x2 | 6.0 | -   | 8.0 | -    | ns    |

| T <sub>WCKT</sub> |                                                                      | 32x1 | 6.8 | -   | 9.6 | -    | ns    |

| T <sub>DCK</sub>  | Data setup time before clock K                                       | 16x2 | 5.2 | -   | 7.0 | -    | ns    |

| T <sub>DOCK</sub> |                                                                      | 32x1 | 6.2 | -   | 8.0 | -    | ns    |

<sup>1.</sup> Timing for the 16x1 RAM option is identical to 16x2 RAM timing.

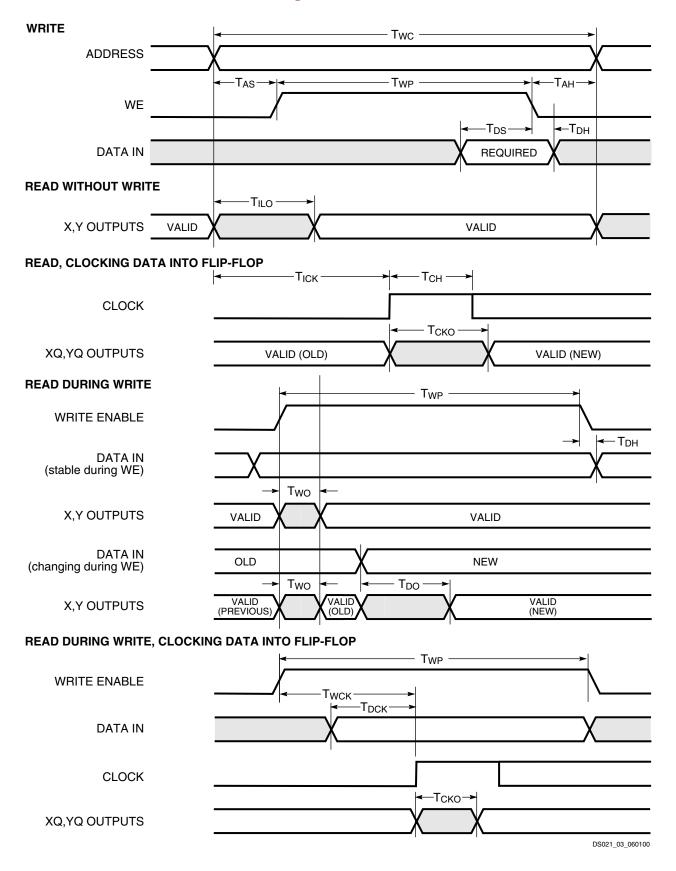

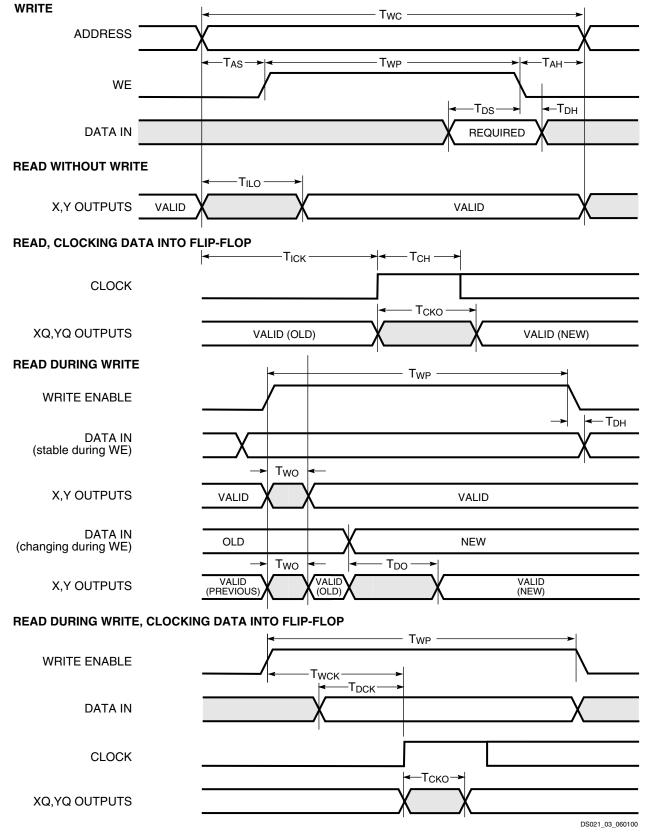

# **XQ4000E CLB Level-Sensitive RAM Timing Characteristics**

## XQ4000E Guaranteed Input and Output Parameters (Pin-to-Pin, TTL I/O)

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Pin-to-pin timing parameters are derived from measuring external and internal test patterns and are guaranteed over worst-case operating conditions (supply voltage and junction temperature). Listed below are representative values for typical pin locations and normal clock loading. For more specific, more precise, and

worst-case guaranteed data, reflecting the actual routing structure, use the values provided by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report. Values apply to all XQ4000E devices unless otherwise noted.

| TICKOF (Max)  Global clock to output (fast) us  Global Clock-to-Output De  Global Clock-to-Output De  Global Clock-to-Output De  TPG  Global Clock-to-Output De  TPSUF  Input setup time, using IFF (not                                       | DS021_04_060100 mited) using OFF           | XQ4005E<br>XQ4010E<br>XQ4013E<br>XQ4025E<br>XQ4005E<br>XQ4010E<br>XQ4013E<br>XQ4025E | -<br>10.9<br>11.0<br>-<br>-<br>14.9<br>15.0 | 14.0<br>16.0<br>16.5<br>17.0<br>18.0<br>20.0<br>20.5 | ns<br>ns<br>ns<br>ns |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------|----------------------|

| T <sub>ICKO</sub> Global clock to output (slew-ling)  (Max)  T <sub>PG</sub> OF Global Clock-to-Output Description  Global Clock-to-Output Description  Global Clock-to-Output Description  T <sub>PSUF</sub> Input setup time, using IFF (not | DS021_04_060100 mited) using OFF  FF       | XQ4013E<br>XQ4025E<br>XQ4005E<br>XQ4010E<br>XQ4013E                                  | 11.0<br>-<br>-<br>14.9                      | 16.5<br>17.0<br>18.0<br>20.0<br>20.5                 | ns<br>ns             |

| T <sub>ICKO</sub> Global clock to output (slew-ling)  (Max)  T <sub>PG</sub> OF Global Clock-to-Output Description  Global Clock-to-Output Description  Global Clock-to-Output Description  T <sub>PSUF</sub> Input setup time, using IFF (not | DS021_04_060100 mited) using OFF  FF       | XQ4025E<br>XQ4005E<br>XQ4010E<br>XQ4013E                                             | -<br>14.9                                   | 17.0<br>18.0<br>20.0<br>20.5                         | ns                   |

| T <sub>ICKO</sub> Global clock to output (slew-ling) (Max)  T <sub>PG</sub> OF Global Clock-to-Output December 1                                                                                                                               | DS021_04_060100 mited) using OFF  FF  elay | XQ4005E<br>XQ4010E<br>XQ4013E                                                        | 14.9                                        | 18.0<br>20.0<br>20.5                                 | ns                   |

| T <sub>ICKO</sub> Global clock to output (slew-ling) (Max)  T <sub>PG</sub> OF Global Clock-to-Output December 1                                                                                                                               | DS021_04_060100 mited) using OFF  FF  elay | XQ4010E<br>XQ4013E                                                                   | 14.9                                        | 20.0<br>20.5                                         |                      |

| (Max)  TPG OF Global Clock-to-Output De  TPSUF Input setup time, using IFF (no                                                                                                                                                                 | mited) using OFF                           | XQ4010E<br>XQ4013E                                                                   | 14.9                                        | 20.0<br>20.5                                         |                      |

| (Max)  TPG OF Global Clock-to-Output De  TPSUF Input setup time, using IFF (no                                                                                                                                                                 | =F :                                       | XQ4010E<br>XQ4013E                                                                   | 14.9                                        | 20.0<br>20.5                                         |                      |

| T <sub>PSUF</sub> Input setup time, using IFF (no                                                                                                                                                                                              | əlay                                       | XQ4013E                                                                              |                                             | 20.5                                                 | ns                   |

| T <sub>PSUF</sub> Input setup time, using IFF (no                                                                                                                                                                                              | əlay                                       |                                                                                      | 15.0                                        |                                                      |                      |

| T <sub>PSUF</sub> Input setup time, using IFF (no                                                                                                                                                                                              | · • • • • • • • • • • • • • • • • • • •    | XQ4025E                                                                              | -                                           |                                                      | ns                   |

| T <sub>PSUF</sub> Input setup time, using IFF (no                                                                                                                                                                                              | · • • • • • • • • • • • • • • • • • • •    |                                                                                      |                                             | 21.0                                                 | ns                   |

|                                                                                                                                                                                                                                                | DS021_04_060100                            |                                                                                      | I                                           |                                                      |                      |

|                                                                                                                                                                                                                                                |                                            |                                                                                      |                                             |                                                      |                      |

|                                                                                                                                                                                                                                                | o delay)                                   | XQ4005E                                                                              | -                                           | 2.0                                                  | ns                   |

| (Min)                                                                                                                                                                                                                                          |                                            | XQ4010E                                                                              | 0.2                                         | 1.0                                                  | ns                   |

| Input A                                                                                                                                                                                                                                        | D                                          | XQ4013E                                                                              | 0                                           | 0.5                                                  | ns                   |

| and Hold                                                                                                                                                                                                                                       | g FF                                       | XQ4025E                                                                              | -                                           | 0                                                    | ns                   |

| Time                                                                                                                                                                                                                                           |                                            |                                                                                      |                                             |                                                      |                      |

|                                                                                                                                                                                                                                                | DS021_05_060100                            |                                                                                      |                                             |                                                      |                      |

| T <sub>PHF</sub> Input hold time, using IFF (no                                                                                                                                                                                                | delay)                                     | XQ4005E                                                                              | -                                           | 4.6                                                  | ns                   |

| (Min)                                                                                                                                                                                                                                          | D                                          | XQ4010E                                                                              | 5.5                                         | 6.0                                                  | ns                   |

| Input A                                                                                                                                                                                                                                        |                                            | XQ4013E                                                                              | 6.5                                         | 7.0                                                  | ns                   |

| Setup T <sub>PC</sub><br>and Hold<br>Time                                                                                                                                                                                                      | 3 IFF                                      | XQ4025E                                                                              | -                                           | 8.0                                                  | ns                   |

| Time                                                                                                                                                                                                                                           |                                            |                                                                                      |                                             |                                                      |                      |

|                                                                                                                                                                                                                                                | DS021_05_060100                            |                                                                                      |                                             |                                                      |                      |

| T <sub>PSU</sub> Input setup time, using IFF (w                                                                                                                                                                                                | ith delay)                                 | XQ4005E                                                                              | -                                           | 8.5                                                  | ns                   |

| (Min)                                                                                                                                                                                                                                          | D                                          | XQ4010E                                                                              | 7.0                                         | 8.5                                                  | ns                   |

| Input A                                                                                                                                                                                                                                        |                                            | XQ4013E                                                                              | 7.0                                         | 8.5                                                  | ns                   |

| Setup T <sub>PC</sub><br>and Hold<br>Time                                                                                                                                                                                                      | 3 IFF                                      | XQ4025E                                                                              | -                                           | 9.5                                                  | ns                   |

|                                                                                                                                                                                                                                                |                                            |                                                                                      |                                             |                                                      |                      |

|                                                                                                                                                                                                                                                | DS021_05_060100                            |                                                                                      |                                             |                                                      |                      |

| T <sub>PH</sub> Input hold time, using IFF (with                                                                                                                                                                                               | h delay)                                   | XQ4005E                                                                              | -                                           | 0                                                    | ns                   |

| (Min)                                                                                                                                                                                                                                          | D                                          | XQ4010E                                                                              | 0                                           | 0                                                    | ns                   |

| Input                                                                                                                                                                                                                                          |                                            | XQ4013E                                                                              | 0                                           | 0                                                    | ns                   |

| Setup<br>and Hold<br>Time                                                                                                                                                                                                                      | 3 IFF                                      | XQ4025E                                                                              | -                                           | 0                                                    | ns                   |

| Tille                                                                                                                                                                                                                                          |                                            |                                                                                      |                                             |                                                      |                      |

|                                                                                                                                                                                                                                                |                                            |                                                                                      |                                             | 1                                                    | 1                    |

- 1. OFF = Output Flip-Flop

- 2. IFF = Input Flip-Flop or Latch

## **XQ4000E IOB Input Switching Characteristic Guidelines**

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Pin-to-pin timing parameters are derived from measuring external and internal test patterns and are guaranteed over worst-case operating conditions (supply voltage and junction temperature). Listed below are representative values for typical pin locations and normal clock loading. For more specific, more precise, and

worst-case guaranteed data, reflecting the actual routing structure, use the values provided by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report. Values apply to all XQ4000E devices unless otherwise noted.

|                    |                                                     | -3          |     | -3 -4 | -:  | 4    |       |

|--------------------|-----------------------------------------------------|-------------|-----|-------|-----|------|-------|

| Symbol             | Description                                         | Device      | Min | Max   | Min | Max  | Units |

| Propagat           | ion Delays (TTL Inputs) <sup>(1)</sup>              | · ·         |     |       |     |      |       |

| T <sub>PID</sub>   | Pad to I1, I2                                       | All devices | -   | 2.5   | -   | 3.0  | ns    |

| T <sub>PLI</sub>   | Pad to I1, I2 via transparent input latch, no delay | All devices | -   | 3.6   | -   | 4.8  | ns    |

| T <sub>PDLI</sub>  | Pad to I1, I2 via transparent FCL and input latch,  | XQ4005E     | -   | -     | -   | 10.8 | ns    |

|                    | with delay                                          | XQ4010E     | -   | 10.8  | -   | 11.0 | ns    |

|                    |                                                     | XQ4013E     | -   | 11.2  | -   | 11.4 | ns    |

|                    |                                                     | XQ4025E     | -   | -     | -   | 13.8 | ns    |

| Propagat           | ion Delays (CMOS Inputs) <sup>(1)</sup>             |             |     | 1     | 1   | 1    | 1     |

| T <sub>PIDC</sub>  | Pad to I1, I2                                       | All devices | -   | 4.1   | -   | 5.5  | ns    |

| T <sub>PLIC</sub>  | Pad to I1, I2 via transparent input latch, no delay | All devices | -   | 8.8   | -   | 6.8  | ns    |

| T <sub>PDLIC</sub> | Pad to I1, I2 via transparent FCL and input latch,  | XQ4005E     | -   | -     | -   | 16.5 | ns    |

|                    | with delay                                          | XQ4010E     | -   | 14.0  | -   | 17.5 | ns    |

|                    |                                                     | XQ4013E     | -   | 14.4  | -   | 18.0 | ns    |

|                    |                                                     | XQ4025E     | -   | -     | -   | 20.8 | ns    |

| Propagat           | ion Delays (TTL Inputs)                             |             |     | 1     | '   | 1    | 1     |

| T <sub>IKRI</sub>  | Clock (IK) to I1, I2 (flip-flop)                    | All devices | -   | 2.8   | -   | 5.6  | ns    |

| T <sub>IKLI</sub>  | Clock (IK) to I1, I2 (latch enable, active Low)     | All devices | -   | 4.0   | -   | 6.2  | ns    |

| Hold Tim           | es <sup>(2)</sup>                                   |             |     | 1     |     |      |       |

| T <sub>IKPI</sub>  | Pad to clock (IK), no delay                         | All devices | 0   | -     | 0   | -    | ns    |

| T <sub>IKPID</sub> | Pad to clock (IK), with delay                       | All devices | 0   | -     | 0   | -    | ns    |

| T <sub>IKEC</sub>  | Clock enable (EC) to clock (K), no delay            | All devices | 1.5 | -     | 1.5 | -    | ns    |

| T <sub>IKECD</sub> | Clock enable (EC) to clock (K), with delay          | All devices | 0   | -     | 0   | -    | ns    |

- 1. Input pad setup and hold times are specified with respect to the internal clock (IK). For setup and hold times with respect to the clock input pin, see the pin-to-pin parameters in the Guaranteed Input and Output Parameters table.

- 2. Voltage levels of unused pads, bonded or unbonded, must be valid logic levels. Each can be configured with the internal pull-up (default) or pull-down resistor, or configured as a driven output, or can be driven from an external source.

# **XQ4000E IOB Input Switching Characteristic Guidelines (continued)**

|                     |                                              |             | -3   |     | -4   |      |          |

|---------------------|----------------------------------------------|-------------|------|-----|------|------|----------|

| Symbol              | Description                                  | Device      | Min  | Max | Min  | Max  | Units    |

| Setup Tir           | nes (TTL Inputs) <sup>(1,2)</sup>            |             |      |     |      |      | <u>'</u> |

| T <sub>PICK</sub>   | Pad to clock (IK), no delay                  | All devices | 2.6  | -   | 4.0  | -    | ns       |

| T <sub>PICKD</sub>  | Pad to clock (IK), with delay                | XQ4005E     | -    | -   | 10.9 | -    | ns       |

|                     |                                              | XQ4010E     | 9.8  | -   | 11.3 | -    | ns       |

|                     |                                              | XQ4013E     | 10.2 | -   | 11.8 | -    | ns       |

|                     |                                              | XQ4025E     | -    | -   | 14.0 | -    | ns       |

| Setup Tir           | nes (CMOS Inputs) <sup>(1,2)</sup>           |             |      |     |      |      |          |

| T <sub>PICKC</sub>  | Pad to clock (IK), no delay                  | All devices | 3.3  | -   | 6.0  | -    | ns       |

| T <sub>PICKDC</sub> | Pad to clock (IK), with delay                | XQ4005E     | -    | -   | 12.0 | -    | ns       |

|                     |                                              | XQ4010E     | 10.5 | -   | 13.0 | -    | ns       |

|                     |                                              | XQ4013E     | 10.9 | -   | 13.5 | -    | ns       |

|                     |                                              | XQ4025E     | -    | -   | 16.0 | -    | ns       |

| (TTL or C           | MOS)                                         |             |      | -   |      |      |          |

| T <sub>ECIK</sub>   | Clock enable (EC) to clock (IK), no delay    | All devices | 2.5  | -   | 3.5  | -    | ns       |

| T <sub>ECIKD</sub>  | Clock enable (EC) to clock (IK), with delay  | XQ4005E     | -    | -   | 10.4 | -    | ns       |

|                     |                                              | XQ4010E     | 9.7  | -   | 10.7 | -    | ns       |

|                     |                                              | XQ4013E     | 10.1 | -   | 11.1 | -    | ns       |

|                     |                                              | XQ4025E     | -    | -   | 14.0 | -    | ns       |

| Global Se           | et/Reset <sup>(3)</sup>                      |             |      |     | -    | 1    | -        |

| T <sub>RRI</sub>    | Delay from GSR net through Q to I1, I2       | All devices | -    | 7.8 | -    | 12.0 | ns       |

| T <sub>MRW</sub>    | GSR width                                    | All devices | 11.5 | -   | 13.0 | -    | ns       |

| T <sub>MRI</sub>    | GSR inactive to first active clock (IK) edge | All devices | 11.5 | -   | 13.0 | -    | ns       |

- Input pad setup and hold times are specified with respect to the internal clock (IK). For setup and hold times with respect to the clock input pin, see the pin-to-pin parameters in the Guaranteed Input and Output Parameters table.

- 2. Voltage levels of unused pads, bonded or unbonded, must be valid logic levels. Each can be configured with the internal pull-up (default) or pull-down resistor, or configured as a driven output, or can be driven from an external source.

- 3. Timing is based on the XC4005E. For other devices see the XACT timing calculator.

### XQ4000E IOB Output Switching Characteristic Guidelines

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE in the Xilinx Develop-

ment System) and back-annotated to the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). For Propagation Delays, slew-rate = fast unless otherwise noted. Values apply to all XQ4000E devices unless otherwise noted.

|                     |                                                    |      | 3        | -4   |      |       |  |

|---------------------|----------------------------------------------------|------|----------|------|------|-------|--|

| Symbol              | Description                                        | Min  | Max      | Min  | Max  | Units |  |

| Propagation         | on Delays (TTL Output Levels)                      | '    | <u>'</u> |      |      |       |  |

| T <sub>OKPOF</sub>  | Clock (OK) to pad, fast                            | -    | 6.5      | -    | 7.5  | ns    |  |

| T <sub>OKPOS</sub>  | Clock (OK) to pad, slew-rate limited               | -    | 9.5      | -    | 11.5 | ns    |  |

| T <sub>OPF</sub>    | Output (O) to pad, fast                            | -    | 5.5      | -    | 8.0  | ns    |  |

| T <sub>OPS</sub>    | Output (O) to pad, slew-rate limited               | -    | 8.6      | -    | 12.0 | ns    |  |

| T <sub>TSHZ</sub>   | 3-state to pad High-Z, slew-rate independent       | -    | 4.2      | -    | 10.0 | ns    |  |

| T <sub>TSONF</sub>  | 3-state to pad active and valid, fast              | -    | 8.1      | -    | 10.0 | ns    |  |

| T <sub>TSONS</sub>  | 3-state to pad active and valid, slew-rate limited | -    | 11.1     | -    | 13.7 | ns    |  |

| Propagation         | on Delays (CMOS Output Levels)                     | -    | 1        |      | 1    | •     |  |

| T <sub>OKPOFC</sub> | Clock (OK) to pad, fast                            | -    | 7.8      | -    | 9.5  | ns    |  |

| T <sub>OKPOSC</sub> | Clock (OK) to pad, slew-rate limited               | -    | 11.6     | -    | 13.5 | ns    |  |

| T <sub>OPFC</sub>   | Output (O) to pad, fast                            | -    | 9.7      | -    | 10.0 | ns    |  |

| T <sub>OPSC</sub>   | Output (O) to pad, slew-rate limited               | -    | 13.4     | -    | 14.0 | ns    |  |

| T <sub>TSHZC</sub>  | 3-state to pad High-Z, slew-rate independent       | -    | 4.3      | -    | 5.2  | ns    |  |

| T <sub>TSONFC</sub> | 3-state to pad active and valid, fast              | -    | 7.6      | -    | 9.1  | ns    |  |

| T <sub>TSONSC</sub> | 3-state to pad active and valid, slew-rate limited | -    | 11.4     | -    | 13.1 | ns    |  |

| Setup and           | Hold Times                                         | '    |          |      | I    |       |  |

| T <sub>OOK</sub>    | Output (O) to clock (OK) setup time                | 4.6  | -        | 5.0  | -    | ns    |  |

| T <sub>OKO</sub>    | Output (O) to clock (OK) hold time                 | 0    | -        | 0    | -    | ns    |  |

| T <sub>ECOK</sub>   | Clock enable (EC) to clock (OK) setup              | 3.5  | -        | 4.8  | -    | ns    |  |

| T <sub>OKEC</sub>   | Clock enable (EC) to clock (OK) hold               | 1.2  | -        | 1.2  | -    | ns    |  |

| Clock               |                                                    | -    |          |      | 1    | •     |  |

| T <sub>CH</sub>     | Clock High                                         | 4.0  | -        | 4.5  | -    | ns    |  |

| T <sub>CL</sub>     | Clock Low                                          | 4.0  | -        | 4.5  | -    | ns    |  |

| Global Set          | /Reset <sup>(3)</sup>                              |      |          |      | 1    |       |  |

| T <sub>RRO</sub>    | Delay from GSR net to pad                          | -    | 11.8     | -    | 15.0 | ns    |  |

| T <sub>MRW</sub>    | GSR width                                          | 11.5 | -        | 13.0 | -    | ns    |  |

| T <sub>MRO</sub>    | GSR inactive to first active clock (OK) edge       | 11.5 | -        | 13.0 | -    | ns    |  |

- 1. Output timing is measured at pin threshold, with 50 pF external capacitive loads (incl. test fixture). Slew-rate limited output rise/fall times are approximately two times longer than fast output rise/fall times. For the effect of capacitive loads on ground bounce, see the "Additional XC4000 Data" section on the Xilinx web site, <a href="https://www.xilinx.com/partinfo/databook.htm">www.xilinx.com/partinfo/databook.htm</a>.

- 2. Voltage levels of unused pads, bonded or unbonded, must be valid logic levels. Each can be configured with the internal pull-up (default) or pull-down resistor, or configured as a driven output, or can be driven from an external source.

- Timing is based on the XC4005E. For other devices see the XACT timing calculator.

# XC4000E Boundary Scan (JTAG) Switching Characteristic Guidelines

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are not measured directly. They are derived from benchmark timing patterns that are taken at device introduction, prior to any process improvements. For more detailed, more precise, and more up-to-date information, use the values provided by the XACT timing calculator and used in the simulator.

These values can be printed in tabular format by running LCA2XNF-S.

The following guidelines reflect worst-case values over the recommended operating conditions. They are expressed in units of nanoseconds and apply to all XC4000E devices unless otherwise noted.

|                     |                            | -        | 3    | -    | 4    |       |

|---------------------|----------------------------|----------|------|------|------|-------|

| Symbol              | Description                | Min      | Max  | Min  | Max  | Units |

| Setup Times         |                            | '        | !    |      |      |       |

| T <sub>TDITCK</sub> | Input (TDI) to clock (TCK) | 30.0     |      | 30.0 |      | ns    |

| T <sub>TMSTCK</sub> | Input (TMS) to clock (TCK) | 15.0     |      | 15.0 |      | ns    |

| Hold Times          |                            | <u>'</u> |      |      |      |       |

| T <sub>TCKTDI</sub> | Input (TDI) to clock (TCK) | 0        |      | 0    |      | ns    |

| T <sub>TCKTMS</sub> | Input (TMS) to clock (TCK) | 0        |      | 0    |      | ns    |

| Propagation De      | lay                        | -        |      |      |      |       |

| T <sub>TCKPO</sub>  | Clock (TCK) to pad (TDO)   |          | 30.0 |      | 30.0 | ns    |

| Clock               |                            | <u>'</u> |      |      |      | ,     |

| T <sub>TCKH</sub>   | Clock (TCK) High           | 5.0      |      | 5.0  |      | ns    |

| T <sub>TCKL</sub>   | Clock (TCK) Low            | 5.0      |      | 5.0  |      | ns    |

| F <sub>MAX</sub>    | Frequency                  |          | 15.0 |      | 15.0 | MHz   |

- 1. Input setup and hold times and clock-to-pad times are specified with respect to external signal pins.

- 2. Output timing is measured at pin threshold, with 50pF external capacitive loads (incl. test fixture). Slew-rate limited output rise/fall times are approximately two times longer than fast output rise/fall times. For the effect of capacitive loads on ground bounce, see the "Additional XC4000 Data" section of the Programmable Logic Data Book.

- 3. Voltage levels of unused pads, bonded or unbonded, must be valid logic levels. Each can be configured with the internal pull-up (default) or pull-down resistor, or configured as a driven output, or can be driven from an external source.

# **XQ4028EX Switching Characteristics**

#### **Definition of Terms**

In the following tables, some specifications may be designated as Advance or Preliminary. These terms are defined as follows:

**Advance:** Initial estimates based on simulation and/or extrapolation from other speed grades, devices, or device families. Values are subject to change. Use as estimates, not for production.

Preliminary: Based on preliminary characterization. Further changes are not expected.

**Unmarked:** Specifications not identified as either Advance or Preliminary are to be considered Final.

Except for pin-to-pin input and output parameters, the A.C. parameter delay specifications included in this document are derived from measuring internal test patterns. All specifications are representative of worst-case supply voltage and junction temperature conditions.

All specifications subject to change without notice.

## XQ4028EX Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Description                                        |                                |                               | Units |

|------------------|----------------------------------------------------|--------------------------------|-------------------------------|-------|

| V <sub>CC</sub>  | Supply voltage relative to GND                     | Supply voltage relative to GND |                               | V     |

| V <sub>IN</sub>  | Input voltage relative to GND <sup>(2)</sup>       | -0.5 to V <sub>CC</sub> + 0.5  | V                             |       |