CY23FS04

# Failsafe™ 2.5V/ 3.3V Zero Delay Buffer

### **Features**

- Internal DCXO for continuous glitch-free operation

- · Zero input-output propagation delay

- Low-jitter (< 35 ps RMS) outputs</li>

- Low Output-to-Output skew (< 200 ps)</li>

- 4.17 MHz-170 MHz reference input

- Supports industry standard input crystals

- 170 MHz outputs

- · 5V-tolerant inputs

- · Phase-locked loop (PLL) Bypass Mode

- Dual Reference Inputs

- 16-pin TSSOP

- · 2.5V or 3.3V output power supplies

- · 3.3V core power supply

- Industrial temperature available

## Functional Description

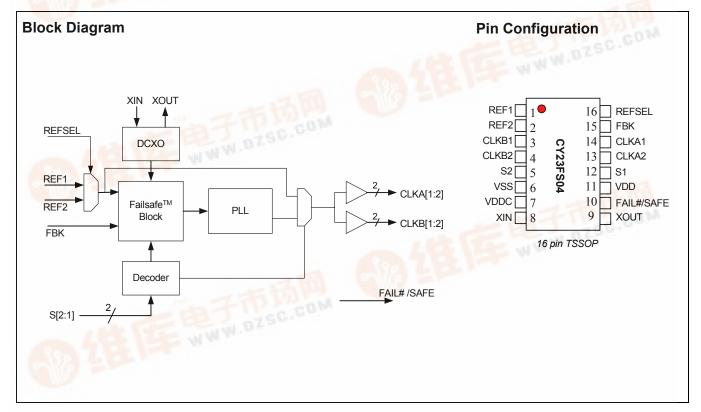

The CY23FS04 is a FailSafe™ zero delay buffer with two reference clock inputs and four phase-aligned outputs. The device provides an optimum solution for applications where continuous operation is required in the event of a primary clock failure.

The continuous, glitch-free operation is achieved by using a DCXO, which serves as a redundant clock source in the event of a reference clock failure by maintaining the last frequency and phase information of the reference clock.

The unique feature of the CY23FS04 is that the DCXO is in fact the primary clocking source, which is synchronized (phase-aligned) to the external reference clock. When this external clock is restored, the DCXO automatically resynchronizes to the external clock.

The frequency of the crystal, which will be connected to the DCXO must be chosen to be an integer factor of the frequency of the reference clock. This factor is set by two select lines: S[2:1], please see *Table 1*. Output power supply, VDD can be connected to either 2.5V or 3.3V. VDDC is the power supply pin for internal circuits and must be connected to 3.3V.

### **Pin Definition**

| Pin Number | Pin Name   | Description                                                                                                                                        |  |

|------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1,2        | REF[1:2]   | Reference clock inputs. 5V-tolerant <sup>[4]</sup> .                                                                                               |  |

| 3,4        | CLKB[1:2]  | Bank B clock outputs. <sup>[1,2]</sup>                                                                                                             |  |

| 14,13      | CLKA[1:2]  | nk A clock outputs. <sup>[1,2]</sup>                                                                                                               |  |

| 15         | FBK        | Feedback input to the PLL.[1,4]                                                                                                                    |  |

| 12,5       | S[1:2]     | Frequency select pins and PLL and DCXO bypass mode. [3]                                                                                            |  |

| 8          | XIN        | Reference crystal input.                                                                                                                           |  |

| 9          | XOUT       | Reference crystal output.                                                                                                                          |  |

| 10         | FAIL#/SAFE | Valid reference indicator. A high level indicates a valid reference input.                                                                         |  |

| 11         | VDD        | 2.5V or 3.3V power supply.                                                                                                                         |  |

| 7          | VDDC       | 3.3V power supply.                                                                                                                                 |  |

| 6          | VSS        | Ground.                                                                                                                                            |  |

| 16         | REFSEL     | <b>Reference select</b> . Selects the active reference clock from either REF1 or REF2. REFSEL = 1, REF1 is selected, REFSEL = 0, REF2 is selected. |  |

**Table 1. Configuration Table**

|        | XTAL (MHz) |       | REF (MHz) |                          | OUT (MHz) |        |               | REF:XTAL | Out:XTAL |

|--------|------------|-------|-----------|--------------------------|-----------|--------|---------------|----------|----------|

| S[2:1] | Min.       | Max.  | Min.      | Max.                     | Min.      | Max.   | REF:OUT ratio |          | ratio    |

| 00     |            |       |           | PLL and DCXO Bypass Mode |           |        |               |          |          |

| 01     | 8.33       | 30.00 | 4.17      | 15.00                    | 4.17      | 15.00  | x1            | 1/2      | 1/2      |

| 10     | 8.00       | 25.00 | 16.00     | 50.00                    | 16.00     | 50.00  | x1            | 2        | 2        |

| 11     | 8.33       | 28.33 | 50.00     | 170.00                   | 50.00     | 170.00 | x1            | 6        | 6        |

## **FailSafe Function**

The CY23FS04 is targeted at clock distribution applications that could or which currently require continued operation should the main reference clock fail. Existing approaches to this requirement have utilized multiple reference clocks with either internal or external methods for switching between references. The problem with this technique is that it leads to interruptions (or glitches) when transitioning from one reference to another, often requiring complex external circuitry or software to maintain system stability. The technique imple-

mented in this design completely eliminates any switching of references to the PLL, greatly simplifying system design.

The CY23FS04 PLL is driven by the crystal oscillator, which is phase-aligned to an external reference clock so that the output of the device is effectively phase-aligned to reference via the external feedback loop. This is accomplished by utilizing a digitally controlled capacitor array to pull the crystal frequency over an approximate range of  $\pm 300$  ppm from its nominal frequency.

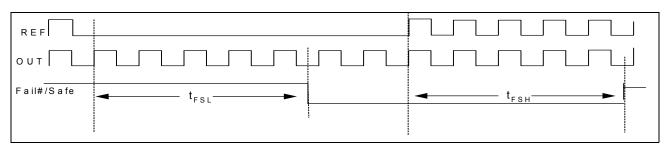

Figure 1. Fail#/Safe Timing for Input Reference Failing Catastrophically

#### Notes

- 1. For normal operation, connect either one of the four clock outputs to the FBK input.

- 2. Weak pull-downs on all outputs

- 3. Weak pull-ups on these inputs.

- 4. Weak pull-down on these inputs.

$$t_{FSL(max)} = 2 \left( t_{REF} \mathbf{x} \, n \right) + 25 \, \text{ns}$$

$$n = \frac{F_{REF}}{F_{XTAL}} = 4 \, (\text{in above example})$$

$$t_{FSH(min)} = 12 \left( t_{REF} \mathbf{x} \, n \right) + 25 \, \text{ns}$$

Figure 2. Fail#/Safe Timing Formula

Table 2. FailSafe Timing Table

| Parameter        | Description                | Conditions                           | Min.         | Max.         | Unit |

|------------------|----------------------------|--------------------------------------|--------------|--------------|------|

| t <sub>FSL</sub> | Fail#/Safe Assert Delay    | Measured at 80% to 20%, Load = 15 pF |              | See Figure 2 | ns   |

| t <sub>FSH</sub> | Fail#/Safe De-assert Delay | Measured at 80% to 20%, Load = 15 pF | See Figure 2 |              | ns   |

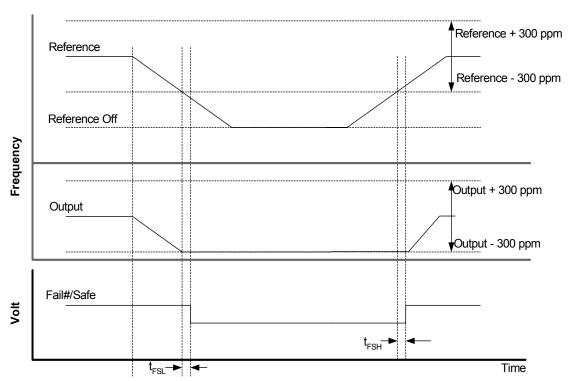

In this mode, should the reference frequency fail (i.e. stop or disappear), the DCXO maintains its last setting and a flag signal (FAIL#/SAFE) is set to indicate failure of the reference clock.

The CY23FS04 provides 2 select bits, S1 through S2 to control the reference to crystal frequency ratio. The DCXO is internally tuned to the phase and frequency of the external reference

only when the reference frequency divided by this ratio is within the DCXO capture range. If the frequency is out of range, a flag will be set on the FAIL#/SAFE pin notifying the system that the selected reference is not valid. If the reference moves in range, then the flag will be cleared, indicating to the system that the selected reference is valid.

Figure 3. FailSafe Timing Diagram: Input Reference Slowly Drifting Out of FailSafe Capture Range

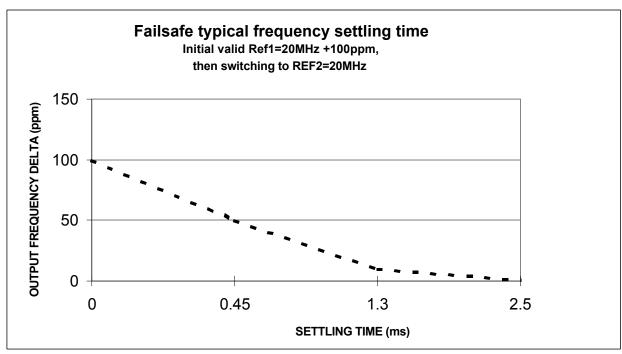

Figure 4. FailSafe Reference Switching Behavior

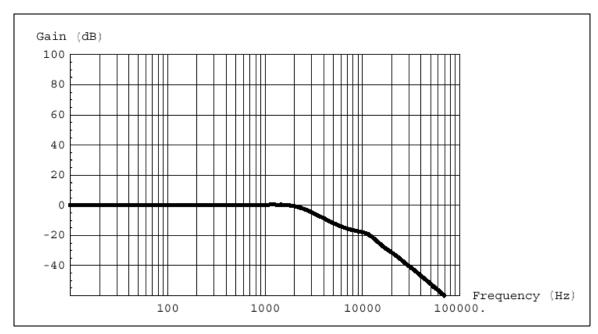

Figure 5. FailSafe Effective Loop Bandwidth (min)

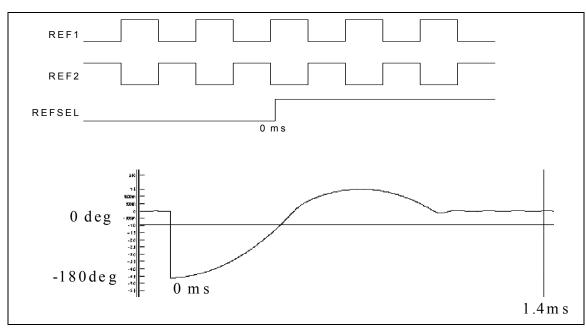

Figure 6. Sample Timing of Muxing Between Two Reference Clocks 180°C Out of Phase and Resulting Output Phase Offset Typical Settling Time (105 MHz)

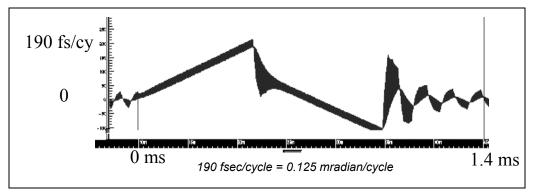

Figure 7. Resulting Output dphase/Cycle Typical Rate of Change (105 MHz)

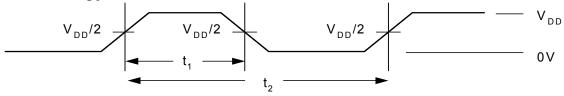

# Duty Cycle - t<sub>DC</sub>

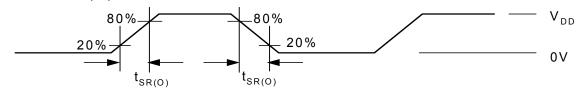

# Slew Rate - $t_{(SR)}$

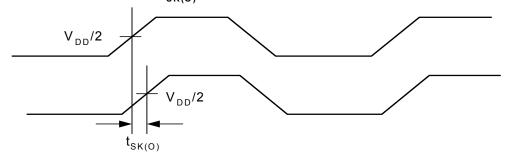

# Output-Output Skew - $t_{SK(O)}$

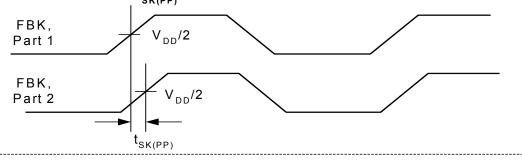

# Part to Part Skew - t<sub>SK(PP)</sub>

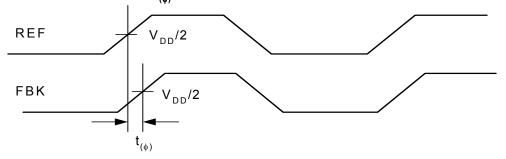

# Static Phase Offset - $t_{(\phi)}$

### **XTAL Selection Criteria and Application Example**

Choosing the appropriate XTAL will ensure the FailSafe device will be able to span an appropriate frequency of operation. Also, the XTAL parameters will determine the holdover frequency stability. Critical parameters are as follows. Our recommendation is to choose:

- Low C0/C1 ratio (240 or less) so that the XTAL has enough range of pullability.

- · Low temperature frequency variation

- · Low manufacturing frequency tolerance

- · Low aging.

C0 is the XTAL shunt capacitance (3 pF - 7 pF typ).

C1 is the XTAL motional capacitance (10 fF – 30 fF typ).

The capacitive load as "seen" by the XTAL is across its terminals. It is named Clmin (for minimum value), and Clmax (for maximum value). These are used for calculating the pull range.

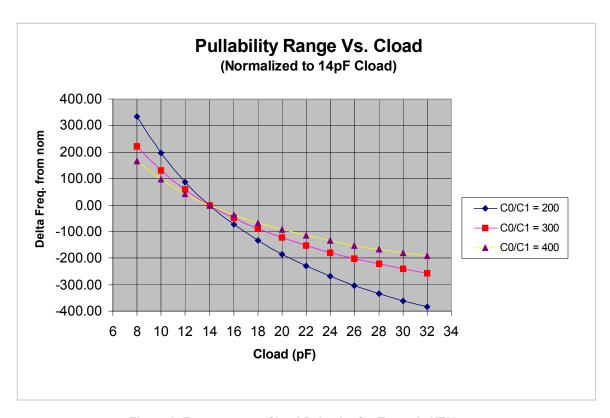

Please note that the CI range "center" is approximately 20 pF, but we may not want a XTAL calibrated to that load. This is because the pullability is not linear, as represented in the equation above. Plotting the pullability of the XTAL shows this expected behavior as shown in *Figure 8*. In this example, specifying a XTAL calibrated to 14 pF load provides a balanced ppm pullability range around the nominal frequency.

### Example:[5]

Clmin = (12 pF IC input cap + 0 pF pulling cap+ 6 pF trace cap on board)/2 = 9 pF Clmax = (12 pF IC input cap + 48 pF pulling cap+ 6 pF trace cap on board)/2 = 33 pF Pull Range =(fClmin–fClmax)/fClmin = ((C1)/2)[(1/(C0+Clmin))–(1/(C0+Clmax))] ×  $10^6$  Pull Range in ppm = ((C1)/2)[(1/(C0+Clmin))–(1/(C0+Clmax))] ×  $10^6$

#### Note:

5. The above example shows the maximum range the FailSafe internal capacitor array is capable of (0 to 48.6 pF). Cypress recommends the min/max capacitor array values be programmed to a narrower range such as 6 pF–30 pF, or 7.5 pF–27 pF. This ensures the XTAL operates between series resonance and anti-resonance. Please contact Cypress for choosing these range settings.

Figure 8. Frequency vs. Cload Behavior for Example XTAL

Table 3. Pullability Range fro XTAL with Different C0/C1 Ratio

| C0/C1 Ratio | Cload(min.) | Cload(max.) | Pullability<br>Range |     |

|-------------|-------------|-------------|----------------------|-----|

| 200         | 8.0         | 32.0        | -385                 | 333 |

| 300         | 8.0         | 32.0        | -256                 | 222 |

| 400         | 8.0         | 32.0        | -192                 | 166 |

Calculated value of the pullability range for the XTAL with C0/C1 ratio of 200, 300 and 400 are shown in *Table 3*. For this calculation Cl(min) = 8 pF and Cl(max)= 32 pF has been used. Using a XTAL that has a nominal frequency specified at load capacitance of 14 pF, almost symmetrical pullability range has been obtained.

Next, it is important to calculate the pullability range including error tolerances. This would be the **capture range** of the input reference frequency that the FailSafe device and XTAL combination would reliably span.

Calculating the **capture range** involves subtracting error tolerances as follows:

| Parameter                         | f error (ppm) |

|-----------------------------------|---------------|

| Manufacturing frequency tolerance | 15            |

| Temperature stability             | 30            |

| Aging                             | 3             |

| Board / trace variation           | 5             |

| Total                             | 53            |

Example: Capture Range for XTAL with C0/C1 Ratio of 200 Negative Capture Range = -385 ppm + 53 ppm = -332 ppm Positive Capture Range = 333 ppm - 53 ppm = +280 ppm

It is important to note that the XTAL with lower C0/C1 ratio has wider **pullability/capture range** as compared to the higher C0/C1 ratio. This will help the user in selecting the appropriate XTAL for use in the FailSafe application.

## **Absolute Maximum Conditions**

| Parameter          | Description                                             | Condition                                  | Min.            | Max.                 | Unit |

|--------------------|---------------------------------------------------------|--------------------------------------------|-----------------|----------------------|------|

| $V_{DD}$           | Supply Voltage                                          |                                            | -0.5            | 4.6                  | V    |

| V <sub>IN</sub>    | Input Voltage                                           | Relative to V <sub>SS</sub>                | -0.5            | V <sub>DD</sub> +0.5 | VDC  |

| T <sub>S</sub>     | Temperature, Storage                                    | Non Functional                             | -65             | +150                 | °C   |

| T <sub>A</sub>     | Temperature, Operating Ambient                          | Commercial Grade                           | 0               | 70                   | °C   |

|                    |                                                         | Industrial Grade                           | -40             | 85                   | °C   |

| T <sub>J</sub>     | Temperature, Junction                                   | Functional                                 |                 | 125                  | °C   |

| ESD <sub>HBM</sub> | ESD Protection (Human Body Model)                       | MIL-STD-883, Method 3015                   | 2000            |                      | V    |

| Ø <sub>JC</sub>    | Dissipation, Junction to Case                           | Mil-Spec 883E Method 1012.1                | 29              | 9.87                 | °C/W |

| Ø <sub>JA</sub>    | Dissipation, Junction to Ambient JEDEC (JESD 51) 120.11 |                                            |                 |                      | °C/W |

| UL-94              | Flammability Rating At 1/8 in. V=0                      |                                            | ′–0             |                      |      |

| MSL                | Moisture Sensitivity Level 1                            |                                            |                 |                      |      |

| Multiple Suppli    | es: The Voltage on any input or I/O pin cannot exce     | ed the power pin during power-up. Power su | oply sequencing | is NOT required.     | I    |

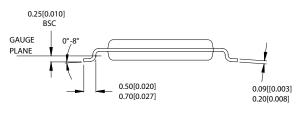

## Recommended Pullable Crystal Specifications<sup>[6]</sup>

| Parameter                      | Name                                                     | Comments                                                                             | Min. | Тур. | Max.  | Unit |

|--------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|------|------|-------|------|

| F <sub>NOM</sub>               | Nominal crystal frequency                                | Parallel resonance, fundamental mode, AT cut                                         | 8.00 | _    | 30.00 | MHz  |

| C <sub>LNOM</sub>              | Nominal load capacitance                                 |                                                                                      | ı    | 14   | -     | pF   |

| R <sub>1</sub>                 | Equivalent series resistance (ESR)                       | Fundamental mode                                                                     | _    | _    | 25    | Ω    |

| R <sub>3</sub> /R <sub>1</sub> | Ratio of third overtone mode ESR to fundamental mode ESR | Ratio used because typical R <sub>1</sub> values are much less than the maximum spec | 3    | _    | _     |      |

| DL                             | Crystal drive level                                      | No external series resistor assumed                                                  | _    | 0.5  | 2     | mW   |

| F <sub>3SEPLI</sub>            | Third overtone separation from 3*F <sub>NOM</sub>        | High side                                                                            | 300  | _    | _     | ppm  |

| F <sub>3SEPLO</sub>            | Third overtone separation from 3*F <sub>NOM</sub>        | Low side                                                                             | _    | _    | -150  | ppm  |

| C <sub>0</sub>                 | Crystal shunt capacitance                                |                                                                                      |      | -    | 7     | pF   |

| C <sub>0</sub> /C <sub>1</sub> | Ratio of shunt to motional capacitance                   |                                                                                      | 180  | _    | 250   |      |

| C <sub>1</sub>                 | Crystal motional capacitance                             |                                                                                      | 14.4 | 18   | 21.6  | fF   |

## Table 4. Operating Conditions for FailSafe Commercial/Industrial Temperature Devices

| Parameter        | Description                                                                                   | Min.  | Max.  | Unit |

|------------------|-----------------------------------------------------------------------------------------------|-------|-------|------|

| $V_{DDC}$        | 3.3V Supply Voltage                                                                           | 3.135 | 3.465 | V    |

| $V_{DD}$         | 2.5V Supply Voltage Range                                                                     | 2.375 | 2.625 | V    |

|                  | 3.3V Supply Voltage Range                                                                     | 3.135 | 3.465 | V    |

| T <sub>A</sub>   | Ambient Operating Temperature, Commercial                                                     | 0     | 70    | °C   |

|                  | Ambient Operating Temperature, Industrial                                                     | -40   | 85    | °C   |

| C <sub>L</sub>   | Output Load Capacitance (Fout ≤ 100 MHz)                                                      |       | 30    | pF   |

|                  | Output Load Capacitance (Fout > 100 MHz)                                                      |       | 15    | pF   |

| C <sub>IN</sub>  | Input Capacitance (except XIN)                                                                |       | 7     | pF   |

| C <sub>XIN</sub> | Crystal Input Capacitance (all internal caps off)                                             | 10    | 13    | pF   |

| T <sub>PU</sub>  | Power-up time for all VDDs to reach minimum specified voltage (power ramps must be monotonic) | 0.05  | 500   | ms   |

## Note:

Document #: 38-07304 Rev \*B

Ecliptek ECX-5788-13.500M, ECX-5807-19.440M, ECX-5872-19.53125M, ECX-5806-18.432M, ECX-5808-27.000M, ECX-5884-17.664M, ECX-5883-16.384M,ECX-5882-19.200M,ECX-5880-24.576M meet these specifications.

## Table 5. Electrical Characteristics for FailSafe Commercial/Industrial Temperature Devices

| Parameter        | Description         | Test Conditions                                                       | Min.                  | Тур. | Max.                  | Unit |

|------------------|---------------------|-----------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| $V_{IL}$         | Input Low Voltage   | CMOS Levels, 30% of V <sub>DD</sub>                                   |                       |      | 0.3 × V <sub>DD</sub> | V    |

| V <sub>IH</sub>  | Input High Voltage  | CMOS Levels, 70% of V <sub>DD</sub>                                   | 0.7 × V <sub>DD</sub> |      |                       | V    |

| I <sub>IL</sub>  | Input Low Current   | V <sub>IN</sub> = V <sub>SS</sub> (100k pull-up only)                 |                       |      | 50                    | μΑ   |

| I <sub>IH</sub>  | Input High Current  | $V_{IN} = V_{DD}$ (100k pull-down only)                               |                       |      | 50                    | μA   |

| I <sub>OL</sub>  | Output Low Current  | $V_{OL} = 0.5V, V_{DD} = 2.5V$                                        |                       | 18   |                       | mA   |

|                  |                     | $V_{OL} = 0.5V, V_{DD} = 3.3V$                                        |                       | 20   |                       | mA   |

| I <sub>ОН</sub>  | Output High Current | $V_{OH} = V_{DD} - 0.5V, V_{DD} = 2.5V$                               |                       | 18   |                       | mA   |

|                  |                     | $V_{OH} = V_{DD} - 0.5V, V_{DD} = 3.3V$                               |                       | 20   |                       | mA   |

| I <sub>DDQ</sub> | Quiescent Current   | All inputs grounded, PLL and DCXO in bypass mode, Reference Input = 0 |                       |      | 250                   | μΑ   |

## Table 6. Switching Characteristics for FailSafe Commercial/Industrial Temperature Devices

| Parameter <sup>[8]</sup> | Description           | Test Conditions                                                | Min. | Max. | Unit              |

|--------------------------|-----------------------|----------------------------------------------------------------|------|------|-------------------|

| f <sub>REF</sub>         | Reference Frequency   | Commercial/Industrial Grades                                   | 4.17 | 170  | MHz               |

| f <sub>OUT</sub>         | Output Frequency      | 15-pF Load, Commercial/Industrial Grades                       | 4.17 | 170  | MHz               |

| f <sub>XIN</sub>         | DCXO Frequency        |                                                                | 8.0  | 30   | MHz               |

| t <sub>DC</sub>          | Duty Cycle            | Measured at V <sub>DD</sub> /2                                 | 47   | 53   | %                 |

| t <sub>SR(I)</sub>       | Input Slew Rate       | Measured on REF1 Input, 30% to 70% of V <sub>DD</sub>          | 0.5  | 4.0  | V/ns              |

| t <sub>SR(O)</sub>       | Output Slew Rate      | Measured from 20% to 80% of V <sub>DD</sub> = 3.3V, 15 pF Load | 0.8  | 4.0  | V/ns              |

|                          |                       | Measured from 20% to 80% of V <sub>DD</sub> = 2.5V, 15 pF Load | 0.4  | 3.0  | V/ns              |

| t <sub>SK(O)</sub>       | Output to Output Skew | All outputs equally loaded, measured at V <sub>DD</sub> /2     |      | 200  | ps                |

| t <sub>SK(PP)</sub>      | Part to Part Skew     | Measured at V <sub>DD</sub> /2                                 |      | 500  | ps                |

| $t_{(\phi)}^{[7]}$       | Static Phase Offset   | Measured at V <sub>DD</sub> /2                                 |      | 250  | ps                |

| $t_{D(\phi)}^{[7]}$      | Dynamic Phase Offset  | Measured at V <sub>DD</sub> /2                                 |      | 200  | ps                |

| t <sub>J(CC)</sub>       | Cycle-to-cycle Jitter | Load = 15 pF, f <sub>OUT</sub> ≥ 6.25 MHz                      |      | 200  | ps                |

|                          |                       |                                                                |      | 35   | ps <sub>RMS</sub> |

## **Ordering Information**

| Part Number | Package Type                 | Product Flow              |

|-------------|------------------------------|---------------------------|

| CY23FS04ZI  | 16-Pin TSSOP                 | Industrial, –40°C to 85°C |

| CY23FS04ZIT | 16-Pin TSSOP – Tape and Reel | Industrial, –40°C to 85°C |

| CY23FS04ZC  | 16-Pin TSSOP                 | Commercial, 0°C to 70°C   |

| CY23FS04ZCT | 16-Pin TSSOP – Tape and Reel | Commercial, 0°C to 70°C   |

### Notes:

- The t<sub>(φ)</sub> reference feedback input delay is guaranteed for a maximum 4:1 input edge ratio between the two signals as long as t<sub>SR(I)</sub> is maintained.

Parameters guaranteed by design and characterization, not 100% tested in production.

Includes typical board trace capacitance of 6–7pF each XIN, XOUT.

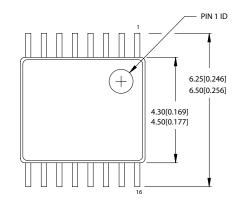

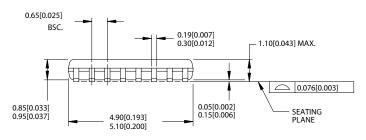

## **Package Drawing and Dimensions**

## 16-lead TSSOP 4.40 MM Body Z16.173

DIMENSIONS IN MM[INCHES] MIN. MAX.

**REFERENCE JEDEC MO-153**

PACKAGE WEIGHT 0.05 gms

| PART #   |                |  |

|----------|----------------|--|

| Z16.173  | STANDARD PKG.  |  |

| ZZ16.173 | LEAD FREE PKG. |  |

51-85091-\*A

FailSafe is a trademark of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders.

## **Document History Page**

| Document Title: CY23FS04 Failsafe™ 2.5V/ 3.3V Zero Delay Buffer<br>Document #: 38-07304 Rev. *B |         |            |                    |                                                     |

|-------------------------------------------------------------------------------------------------|---------|------------|--------------------|-----------------------------------------------------|

| REV.                                                                                            | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change                               |

| **                                                                                              | 123698  | 04/24/03   | RGL                | New data sheet                                      |

| *A                                                                                              | 223811  | See ECN    | RGL/ZJX            | Changed the XTAL Specifications table.              |

| *B                                                                                              | 276712  | See ECN    | RGL                | Removed (T <sub>LOCK</sub> )Lock Time Specification |