捷多邦,专业PCB打样工厂 ,24小时加急出货

# 262,144-Bit Dynamic RAM

# HYB 41256-10/-12/-15

- $262,144 \times 1$ -bit organization

- Industry standard 16 pins

- Single + 5 V supply, ± 10 % tolerance

- Low power dissipation:

- 358 mW active (max.)

- 28 mW standby (max.)

- 100 ns access time

200 ns cycle time (HYB 41256-10)

120 ns access time

220 ns cycle time (HYB 41256-12)

150 ns access time

260 ns cycle time (HYB 41256-15)

- All inputs and outputs TTL-compatible

- On-chip substrate bias generator

- Tristate data output

- Read, write, read-modify-write, RAS-only refresh, hidden-refresh

- Common I/O capability using "early write" operation

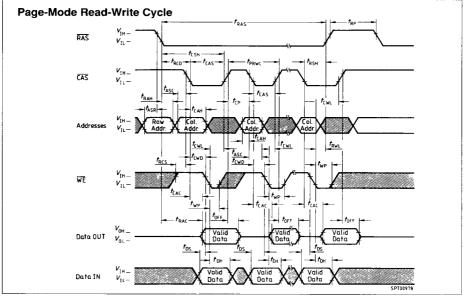

- Page mode read and write, read-write

- 256 refresh cycles with 4 ms refresh period

- Redundancy incorporated for increasing yield activation via laser links

Pin Names

# Pin Configuration

#### A 8 16 VSS DI 2 15 CAS WE 3 14 DO RAS 4 13 A6 HYB 41256 A0 5 12 AR A2 6 11 A4 A 1 10 A5 7 Δ7 9 SPP00969 .dzsc.com

| A0 A8 | Address Inputs        |  |

|-------|-----------------------|--|

| CAS   | Column Address Strobe |  |

| DI    | Data Input            |  |

| DO    | Data Output           |  |

| RAS   | Row Address Strobe    |  |

| WE    | Write Enable          |  |

| Vcc   | Power Supply (+ 5 V)  |  |

| Vss   | Ground (0 V)          |  |

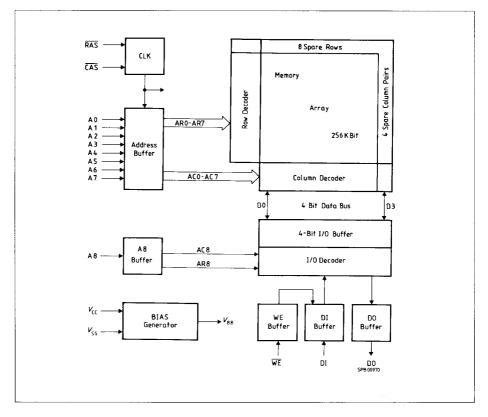

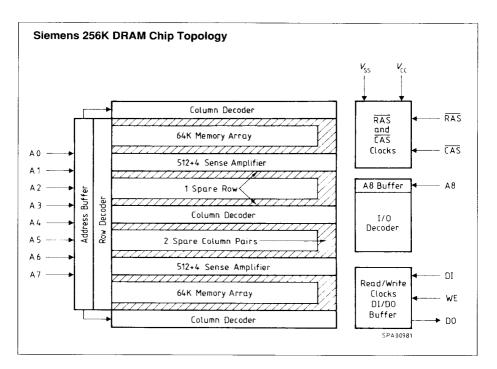

The HYB 41256 is a 262,144 word by 1-bit dynamic random access memory. This 5 V-only component is fabricated with Siemens high-performance N-channel silicon gate technology. The use of tantalum polycide provides high speed. A low radiation molding compound protects the chip against soft errors.

Nine multiplexed address inputs permit the HYB 41256 to be packaged in an industry standard 16-pin dual-in-line package. System-oriented features include single power supply with  $\pm$  10 % tolerance, on-chip address and data registers which eliminate the need for interface registers, and fully TTL-compatible inputs and output, including clocks. In addition to the usual read, write and read-modify-write cycles, the HYB 41256 is capable of early and late write cycles, RAS-only refresh, and hidden refresh. Common I/O capability is given by using early write operation.

The HYB 41256 also features page mode which allows high-speed random access of bits in the same row.

The HYB 41256 has the capability of using laser links to perform redundancy.

# **Functional Description**

# **Device Initialization**

Since the HYB 41256 is a dynamic RAM with a single 5 V supply, no power sequencing is required. For power-up, an initial pause of 200 microseconds is necessary for the internal bias generator to establish the proper substrate bias voltage. To initialize the nodes of the dynamic circuitry, a minimum of 8 active cycles of the row address strobe (RAS) has to be performed. This is also necessary after an extended inactive state of greater than 4 milliseconds.

# Addressing (A0 – A8)

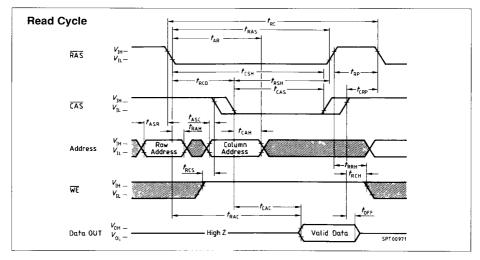

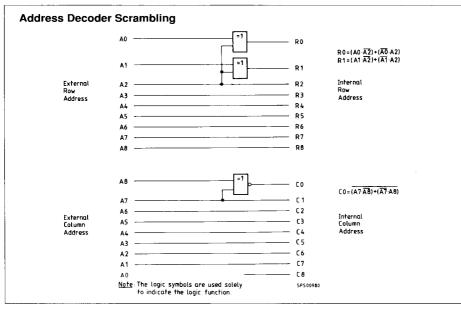

For selecting one of the 262,144 memory cells, a total of 18 address bits is required. First, 9 row address bits are set up on pins A0 through A8 and latched into the row address latches by the row address strobe (RAS). Then, the 9 column address bits are set up on pins A0 through A8 and latched into the column address latches by the column address strobe (CAS). All input addresses must be stable on the falling edges of RAS and CAS. It should be noted that RAS is similar to a "chip enable" insofar as it activates the sense amplifiers as well as the row decoder. CAS is used as a chip select activating the column decoder and the input and output buffers.

# Write Enable (WE)

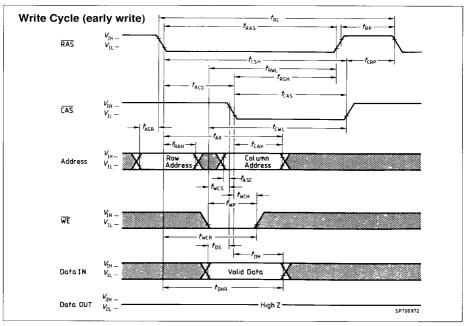

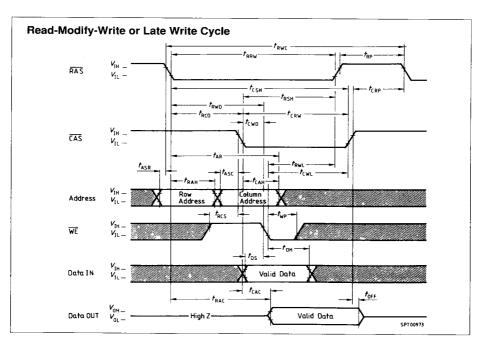

The read or write mode is selected with the  $\overline{WE}$  input. A logic high ( $V_{H}$ ) on  $\overline{WE}$  dictates read mode; logic low ( $V_{L}$ ) dictates write mode. The data input is disabled when read mode is selected. When  $\overline{WE}$  goes low prior to  $\overline{CAS}$ , data output (DO) will remain in the high-impedance state for the entire cycle permitting common I/O operation.

# Data Input (DI)

Data is written during a write or read-modify-write cycle. The falling edge of CAS or WE strobes data into the on-chip data latch. In an early write cycle WE is brought low prior to CAS and the data is strobed in by CAS with setup and hold times referenced to this signal.

# Data Output (DO)

The output is tristate TTL-compatible with a fan-out of two standard TTL loads. DO has the same polarity as DI. The output is in a high-impedance state until CAS is brought low. In a read cycle or read-write cycle, the output is valid after *I*BAC from transition of RAS when *I*BCD (min.) is satisfied, or after *I*CAC from transition of CAS when the transition occurs after *I*BCD (max.). In an early write cycle, the output is always in the high-impedance state. In a delayed write or read-modify-write cycle, the output will follow the sequence for the read cycle. With CAS going high the output returns to the high-impedance state within *I*OFF.

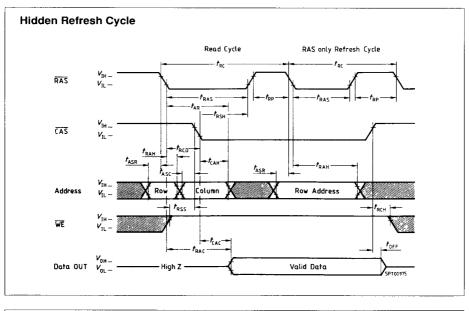

# Hidden refresh

RAS-only refresh cycle may take place while maintaining valid output data. This feature is referred to as hidden refresh. Hidden refresh is performed by holding CAS at  $V_{IL}$  of a previous memory read cycle.

### **Refresh cycle**

A refresh operation must be performed at least every four milliseconds to retain data. Since the output buffer is in the high-impedance state unless CAS is applied, the RAS-only refresh sequence avoids any signal during refresh. Strobing each of the 256 row addresses (A0 through A7) with RAS, causes all bits in each row to be refreshed. CAS can remain high (inactive) for this refresh sequence to conserve power.

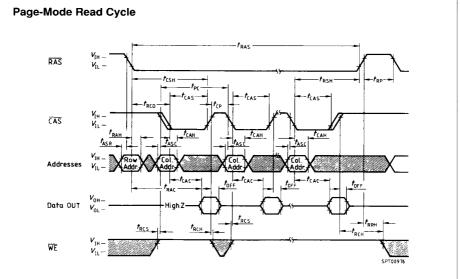

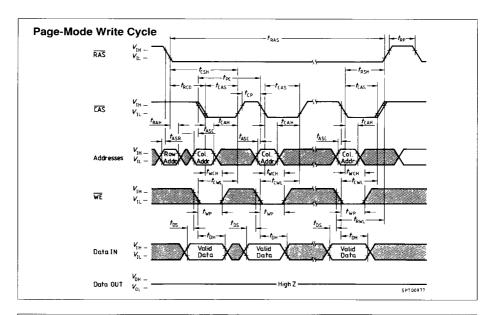

#### Page mode

Page-mode operation allows effectively faster memory access by maintaining the row address and strobing random column addresses on the chip. Thus, the time necessary to setup and strobe sequential row addresses for the same page is no longer required. The maximum number of columns that can be addressed in sequence is determined by *I*<sub>RAS</sub>, the maximum RAS low pulse width.

# **Absolute Maximum Ratings**

Operating temperature range Storage temperature range Voltage on any pin relative to *Vss* Power dissipation Data output current (short circuit) 0 to + 70 °C - 65 to + 150 °C - 1 to 7 V 1 W 50 mA

# **DC Characteristics**

$T_{\rm A} = 0$  to 70 °C;  $V_{\rm SS} = 0$  V,  $V_{\rm CC} = +5$  V ± 10 %

| Symbol | Parameter                                                                                                                                       | Lim                | Unit           | Test                |           |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|---------------------|-----------|--|

|        |                                                                                                                                                 | min.               | max.           |                     | condition |  |

| VIH    | Input high voltage (all inputs)                                                                                                                 | 2.4                | Vcc + 1        | V                   | 2) 3)     |  |

| VIL    | Input low voltage (all inputs)                                                                                                                  | - 1.0              | 0.8            | V                   | 2) 3)     |  |

| Vон    | Output high voltage                                                                                                                             | 2.4                | _              | V                   | 7)        |  |

| VOL    | Output low voltage                                                                                                                              | -                  | 0.4            | V                   | 8)        |  |

| ICC1   | Average Vcc supply current<br>-10 hc = 200 ns<br>-12 hc = 220 ns<br>-15 hc = 260 ns                                                             | – 85<br>– 75<br>65 |                | mA                  | 4)        |  |

| ICC2   | Standby Vcc supply current                                                                                                                      | -                  | 5              | mA                  | 5)        |  |

| Іссз   | Average $v_{CC}$ supply current<br>during RAS-only refresh cycles<br>- 10 $h_{CC} = 200$ ns<br>- 12 $h_{CC} = 220$ ns<br>- 15 $h_{CC} = 260$ ns | -                  | 70<br>60<br>50 | <sup>4)</sup><br>mA |           |  |

| ICC4   | Average Vcc supply current<br>during page mode<br>$-10 \ lpc = 100 \ ns$<br>$-12 \ lpc = 120 \ ns$<br>$-15 \ lpc = 150 \ ns$                    | _                  | 70<br>60<br>50 | mA 4)               |           |  |

| /I(L)  | Input leakage current<br>(any input)                                                                                                            | - 10               | 10             | μA                  | -         |  |

| IO(L)  | Output leakage current<br>(CAS at logic 1,<br>0 < Vout ≤ 5.5)                                                                                   | - 10               | 10             | μΑ –                |           |  |

| Vcc    | Vcc supply voltage                                                                                                                              | 4.5                | 5.5            | v                   | 2)        |  |

| Vss    | Vss supply voltage                                                                                                                              | 0                  | 0              | V                   | 2)        |  |

Notes see page 40.

### Capacitance

| Symbol | Parameter                                                                  | Lim  | Unit | Test |           |  |

|--------|----------------------------------------------------------------------------|------|------|------|-----------|--|

|        |                                                                            | min. | max. |      | condition |  |

| C11    | Input capacitance (A0 – A8, DI)                                            | _    | 7    | pF   | 6)        |  |

| C12    | Input capacitance (RAS, CAS, WE)                                           | -    | 7    | pF   | 6)        |  |

| Со     | Output capacitance (DO,<br>$\overline{CAS} = V \mapsto to disable output)$ | -    | 7    | pF   | 6)        |  |

- <sup>1)</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2) All voltages refered to Vss.

- <sup>3)</sup> Overshooting and undershooting on input levels of 6.5 V or -2 V for a period of 30 ns max. will not influence function and reliability of the device.

- 4) Icc depends on frequency of operation. Maximum current is measured at the fastest cycle rate.

- 5) **RAS** and **CAS** are both  $V_{\text{IH}}$ .

- 6) Effective capacitance calculated from the equation.  $C = \frac{I + \Delta I}{\Delta V}$  with  $\Delta V = 3$  V or measured with Boonton meter.

- <sup>7)</sup> Iон = 5.0 mA

- 8) /OL = + 4.2 mA

# **AC Test Conditions**

Input pulse levels Input rise and fall times Input timing reference levels Output timing reference levels Output load

5 ns between

0 to 3.0 V 0.8 and 2.4 V 0.8 to 2.4 V 0.4 to 2.4 V equivalent to 2 standard TTL loads and 100 pF

# **AC Characteristics**

$T_A = 0$  to 70 °C;  $V_{CC} = +5 \text{ V} \pm 10 \%$  (unless otherwise specified; see notes 9, 10, 11)

| Symbol       | Parameter                                                  | Limit values           |      |      |      |      | Unit |    |

|--------------|------------------------------------------------------------|------------------------|------|------|------|------|------|----|

|              |                                                            | HYB 41256<br>- 10 - 12 |      |      | - 15 |      |      |    |

|              |                                                            | min.                   | max. | min. | max. | min. | max. |    |

| <i>t</i> RC  | Random read or write cycle time 12)                        | 200                    | -    | 220  | -    | 260  | -    | ns |

| <i>t</i> rwc | Read-modify-write cycle time 12)                           | 235                    | -    | 265  | -    | 310  | -    | ns |

| <i>t</i> RAC | Access time from RAS 13) 14)                               | -                      | 100  | -    | 120  | -    | 150  | ns |

| <i>t</i> cac | Access time from CAS 13) 15)                               | -                      | 50   | -    | 60   | -    | 75   | ns |

| <i>t</i> ras | RAS pulse width                                            | 100                    | 104  | 120  | 104  | 150  | 104  | ns |

| <i>t</i> cas | CAS pulse width                                            | 50                     | -    | 60   | -    | 75   | -    | ns |

| <i>I</i> REF | Refresh period                                             | -                      | 4    | -    | 4    | -    | 4    | ms |

| <i>Í</i> RP  | RAS precharge time                                         | 90                     | -    | 90   |      | 100  | -    | ns |

| <i>t</i> CRP | CAS to RAS precharge time                                  | 0                      | -    | 0    | -    | 0    | -    | ns |

| <i>t</i> RCD | RAS to CAS delay time 16)                                  | 25                     | 50   | 30   | 60   | 30   | 75   | ns |

| <i>t</i> rsh | RAS hold time                                              | 50                     | -    | 60   | -    | 75   | -    | ns |

| <i>t</i> csh | CAS hold time                                              | 100                    | -    | 120  | -    | 150  | -    | ns |

| <i>t</i> asr | Row address setup time                                     | 0                      | -    | 0    | -    | 0    | -    | ns |

| <i>Í</i> RAH | Row address hold time                                      | 15                     | -    | 20   | -    | 20   | -    | ns |

| <i>t</i> asc | Column address setup time                                  | 0                      | -    | 0    | -    | 0    | -    | ns |

| <i>Í</i> CAH | Column address hold time                                   | 20                     | -    | 30   | -    | 30   | -    | ns |

| <i>t</i> ar  | Column address hold time referenced to RAS 17)             | 70                     | -    | 90   | -    | 105  | -    | ns |

| <i>t</i> r   | Transition time (rise and fall) 9)                         | 3                      | 50   | 3    | 50   | 3    | 50   | ns |

| <i>t</i> acs | Read command setup time                                    | 0                      | -    | 0    | -    | 0    | -    | ns |

| <i>t</i> rch | Read command hold time<br>referenced to CAS <sup>18)</sup> | 0                      | -    | 0    | -    | 0    | -    | ns |

| <i>Í</i> RBH | Read command hold time<br>referenced to RAS <sup>18)</sup> | 10                     | -    | 10   | -    | 10   | -    | ns |

| <b>I</b> OFF | Output buffer turn-off delay 19)                           | 0                      | 30   | 0    | 30   | 0    | 40   | ns |

| <i>t</i> wcs | Write command setup time 20)                               | 0                      | -    | 0    | -    | 0    | -    | ns |

| <b>f</b> wch | Write command hold time                                    | 35                     | 1_   | 40   | -    | 45   | -    | ns |

Notes see page 42.

| Symbol        | Parameter                                             |      | Limit values |                   |      |      |      |    |

|---------------|-------------------------------------------------------|------|--------------|-------------------|------|------|------|----|

|               |                                                       | - 10 |              | HYB 41256<br>- 12 |      | - 15 |      |    |

|               |                                                       | min. | max.         | min.              | max. | min. | max. |    |

| <b>f</b> wcr  | Write command hold time referenced to RAS 17          | 100  | -            | 100               | -    | 120  | -    | ns |

| <b>t</b> w₽   | Write command pulse width                             | 30   | -            | 40                | -    | 45   | -    | ns |

| <i>t</i> RWL  | Write command to RAS lead time                        | 30   | -            | 40                | -    | 45   | 1-   | ns |

| <i>t</i> cwl  | Write command to CAS lead time                        | 30   | -            | 40                | -    | 45   | -    | ns |

| <i>t</i> os   | Data in setup time 21)                                | 0    | -            | 0                 | -    | 0    | -    | ns |

| tон           | Data in hold time 21)                                 | 30   | -            | 40                | -    | 45   | -    | ns |

| <i>t</i> dhr  | Data in hold time<br>referenced to RAS <sup>17)</sup> | 90   | -            | 100               | -    | 120  | -    | ns |

| <i>t</i> cwd  | CAS to WE delay 20)                                   | 50   | -            | 60                | -    | 75   | -    | ns |

| <i>t</i> RWD  | RAS to WE delay 20)                                   | 100  | -            | 120               | -    | 150  | -    | ns |

| <i>I</i> RRW  | RMW cycle RAS pulse width                             | 140  | -            | 165               | -    | 200  | _    | ns |

| <i>t</i> CRW  | RMW cycle CAS pulse width                             | 85   | -            | 105               | -    | 125  | -    | ns |

| <i>t</i> PC   | Page mode cycle time 12)                              | 100  | -            | 120               | -    | 145  | _    | ns |

| <i>t</i> PRWC | Page mode read-write cycle time                       | 130  | -            | 160               | -    | 190  | -    | ns |

| <i>t</i> CP   | Page mode CAS precharge time                          | 40   | -            | 50                |      | 60   | -    | ns |

#### AC Characteristics (cont'd)

9) ViH and ViL are reference levels to measure timing of input signals. Also, transition times are measured between ViH and ViL.

<sup>10)</sup> An initial pause of 200 µs is required after power-up followed by a minimum of eight initialization cycles prior to normal operation.

<sup>11)</sup> The time parameters specified here are valid for a transition time of t = 5 ns for the input signals.

- <sup>12)</sup> The specification for IRc (min.), Iawc (min.), and page-mode cycle time (IPc) are only used to indicate cycle time at which proper operation over full temperature range (0 °C ≤ TA ≤ 70 °C) is assured.

- 13) Measured with a load equivalent to two TTL loads and 100 pF.

- 14) Assumes that IRCD ≤ IRCD (max.). If IRCD is greater than the maximum recommended value shown in this table, IRAC will increase by the amount that IRCD exceeds the value shown.

- 15) Assumes that  $t_{RCD} \ge t_{RCD}$  (max.).

- <sup>16)</sup> Operation within the *I*<sub>RCD</sub> (max.) limit ensures that *I*<sub>RAC</sub> (max.) can be met. *I*<sub>RCD</sub> (max.) is specified as a reference point only; if *I*<sub>RCD</sub> is greater than the specified *I*<sub>RCD</sub> (max.) limit, then access time is controlled exclusively by *t*<sub>CAC</sub>.

- 17)  $t_{RCD} + t_{CAH} \ge t_{AR} \min$ ,  $t_{RCD} + t_{DH} \ge t_{DHR} \min$ ,  $t_{RCD} + t_{WCH} \ge t_{WCR} \min$ .

- <sup>18)</sup> Either *t*RRH or *t*RCH must be satisfied for a read cycle.

- <sup>19)</sup> toFF (max.) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- <sup>20)</sup> Mxcs, *t*cwb and *t*Rwc are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only: If *t*wcs ≥ *t*wcs (min.), the cycle is an early write cycle and the data output will remain open-circuit (high-impedance) throughout the entire cycle; if *t*cwb ≥ *t*cwb (min.) and *t*Rwb ≥ *t*Rwb (min.) the cycle is a read-write cycle and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.

- <sup>21)</sup> tos and ton are referenced to the leading edge of CAS in early write cycles, and to the leading edge of WE in delayed write of read-modify-write cycles.

#### Waveforms

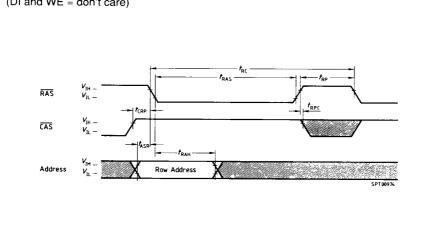

RAS-Only Refresh Cycle (DI and WE = don't care)

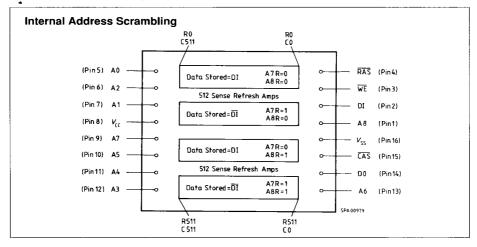

### Address Decoder Scrambling (without redundancy)

The evaluation and incoming testing of RAMs normally requires a description of the internal address scrambling of the device in order to check for 'worst case' pattern.

# Redundancy

### **Redundancy Concept**

The HYB 41256 takes advantage of the redundancy concept for increasing yield. This is done by providing the chip with a total of 8 spare rows and 4 spare column pairs. Two spare rows can be selected independently in each of four 64K cell arrays, and two spare column pairs can be selected independently in each of two 128K cell blocks. The spare lines can be selected by spare decoders which have to be programmed by laser technique during wafer probe.

### Laser Technology

For activation of redundant circuitry a laser pulse is used to open polycide links within the spare row and spare column decoders. The laser technique is used because it is mature and has proven reliable in a number of semiconductor applications including the implementation of redundant memory circuitry. Due to the fact, that the laser beam is very fine and can easily and accurately be positioned, and that it incorporates the energy for a controlled blowup of the polycide links, the laser technique is well suited for highly complex memory circuitry. All that results in a more efficient use of chip area.

# **Ordering Information**

| Туре         | Ordering code | Description               |  |  |

|--------------|---------------|---------------------------|--|--|

| HYB 41256-10 | Q67100-Q380   | DRAM (access time 100 ns) |  |  |

| HYB 41256-12 | Q67100-Q346   | DRAM (access time 120 ns) |  |  |

| HYB 41256-15 | Q67100-Q347   | DRAM (access time 150 ns) |  |  |