#### **General Description**

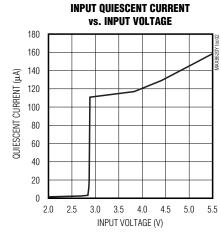

The MAX8620Y micro-power-management integrated circuit (µPMIC) powers low-voltage microprocessors or DSPs in portable devices. The µPMIC includes a highefficiency step-down DC-DC converter, two lowdropout linear regulators (LDOs), a microprocessor reset output, and power-on/off control logic. This device maintains high efficiency at light loads with a low 115µA supply current, and its miniature TDFN package makes it ideal for portable devices.

The MAX8620Y's step-down DC-DC converter utilizes a proprietary 4MHz hysteretic-PWM control scheme that allows for ultra-small external components. Internal synchronous rectification improves efficiency and eliminates the external Schottky diode that is required in conventional step-down converters. The output voltage is adjustable from 0.6V to 3.3V, with guaranteed output current up to 500mA.

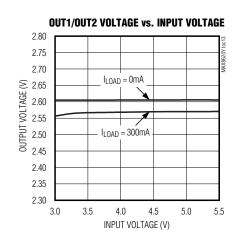

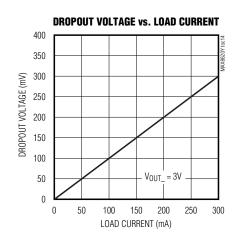

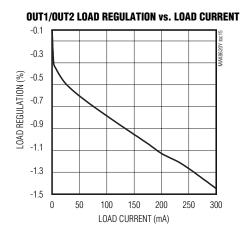

The MAX8620Y's two LDOs offer low 45µVRMs output noise and a low dropout of only 200mV at 200mA. Each LDO delivers at least 300mA of continuous output current. The output voltages are pin selectable from 1.8V to 3.3V for flexibility.

A microprocessor reset output (RESET) monitors OUT1 and warns the system of impending power loss allowing safe shutdown. RESET asserts during power-up, power-down, shutdown, and fault conditions where Vout1 is below its regulation voltage.

### **Applications**

Cellular Handsets

Smart Phones/PDA Phones

**PDAs**

MIXIN

Wireless LAN

Microprocessor and DSP Solutions including MSMTM, XScaleTM, ARMTM, and OMAPTM

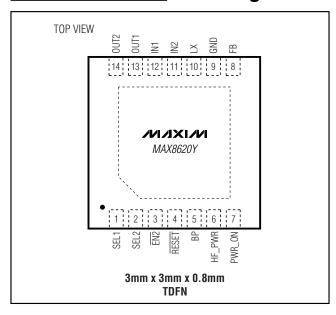

Pin Configuration appears at end of data sheet.

MSM is a trademark of QUALCOMM, Inc. XScale is a trademark of Intel Corp. ARM is a trademark of ARM Limited. OMAP is a trademark of Texas Instruments, Inc.

- ◆ Three Regulators and a Reset in One Package

- ♦ High-Efficiency Step-Down Converter Up to 4MHz Fixed Switching Frequency **500mA Guaranteed Output Current** 0.6V to 3.3V Adjustable Output Voltage ±2% Initial Accuracy **Fast Voltage-Positioning Transient Response Internal Synchronous Rectifier**

- ♦ Two 300mA LDO Regulators 200mV Dropout at 200mA Load Low 45µVRMS Output Noise 3% Accuracy over Line, Load, and Temperature **Overcurrent Protection** Nine Pin-Selectable Output-Voltage Settings

- ♦ 30ms (min) RESET Output Flag

- ♦ 2.7V to 5.5V Input

- ♦ 115µA (typ) Supply Current at No Load

- ♦ Thermal-Overload Protection

- ◆ Tiny 3mm x 3mm x 0.8mm TDFN Package

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-<br>PACKAGE         | TOP<br>MARK |

|-------------|----------------|-------------------------|-------------|

| MAX8620YETD | -40°C to +85°C | 14 TDFN-EP<br>(T1433-2) | AAB         |

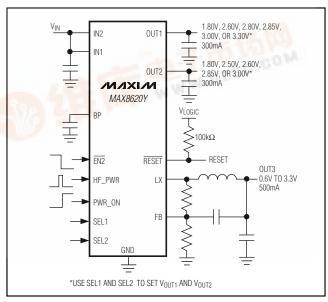

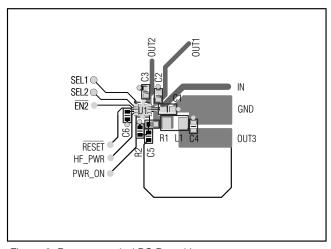

### Typical Operating Circuit

#### **ABSOLUTE MAXIMUM RATINGS**

| IN1, IN2, PWR_ON, RESET, EN2, SEL1, SEL2,          | Operating Temperature Range40°C to + | 85°C |

|----------------------------------------------------|--------------------------------------|------|

| HF_PWR, FB, BP to GND0.3V to +6.0V                 | Junction Temperature+1               | 50°C |

| OUT1, OUT2 to GND0.3V to (V <sub>IN1</sub> + 0.3V) | Storage Temperature Range65°C to +1  | 50°C |

| LX Current1.5A <sub>RMS</sub>                      | Lead Temperature (soldering, 10s)+3  | 00°C |

| Continuous Power Dissipation (TA = +70°C)          |                                      |      |

| 14-Pin TDFN (derate 18 2mW/°C above +70°C) 1454mW  |                                      |      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN1} = V_{IN2} = +3.7V, C_{IN} = 10\mu F, C_{BP} = 0.01\mu F, T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                 | SYMBOL                              | CONDITIO                                                                             | NS                                                                                    | MIN   | TYP          | MAX   | UNITS |  |

|-------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|--------------|-------|-------|--|

| Supply Voltage Range                      | V <sub>IN1</sub>                    |                                                                                      |                                                                                       | 2.7   |              | 5.5   | V     |  |

| Shutdown Supply Current                   | ISHDN                               | V <sub>IN1</sub> = V <sub>IN2</sub> = 4.2V, PWR_ON = HF_PWR = GND                    |                                                                                       |       | 5.5          | 10    | μΑ    |  |

|                                           |                                     | All outputs enabled, no lo                                                           | ad                                                                                    |       | 115          | 140   |       |  |

| Supply Current                            | I <sub>IN1</sub> + I <sub>IN2</sub> | V <sub>OUT1</sub> = V <sub>OUT3</sub> = 1.8V, I <sub>O</sub><br>500μA, OUT2 disabled | V <sub>OUT1</sub> = V <sub>OUT3</sub> = 1.8V, I <sub>OUT1</sub> = I <sub>OUT3</sub> = |       | 430          |       | μΑ    |  |

| UNDERVOLTAGE LOCKOUT                      |                                     |                                                                                      |                                                                                       |       |              |       |       |  |

| UVLO Threshold                            | V <sub>U</sub> VLO                  | $V_{IN1} = V_{IN2}$ rising $V_{IN1} = V_{IN2}$ falling                               |                                                                                       | 2.70  | 2.85<br>2.35 | 3.05  | V     |  |

| THERMAL PROTECTION                        |                                     | -                                                                                    |                                                                                       | 1     |              |       | •     |  |

| Thermal-Shutdown Threshold                |                                     | Temperature rising                                                                   |                                                                                       |       | +160         |       | °C    |  |

| Thermal-Shutdown Hysteresis               |                                     |                                                                                      |                                                                                       |       | 15           |       | °C    |  |

| REFERENCE (BP)                            |                                     |                                                                                      |                                                                                       |       |              |       |       |  |

| Reference Bypass Output<br>Voltage        | V <sub>BP</sub>                     | 0 ≤ I <sub>BP</sub> ≤ 1μA                                                            |                                                                                       | 1.231 | 1.250        | 1.269 | V     |  |

| LOGIC AND CONTROL INPUTS (I               | PWR_ON, H                           | PWR, EN2)                                                                            |                                                                                       |       |              |       |       |  |

| PWR_ON, HF_PWR, EN2 Input<br>Low Voltage  | VIL                                 | $V_{IN1} = V_{IN2} = 2.7V \text{ to } 4.2V$                                          | / (Note 2)                                                                            |       |              | 0.4   | V     |  |

| PWR_ON, HF_PWR, EN2 Input<br>High Voltage | VIH                                 | $V_{IN1} = V_{IN2} = 2.7V \text{ to } 4.2V$                                          | / (Note 2)                                                                            | 1.44  |              |       | V     |  |

| Input Bias Current                        | I <sub>INB</sub>                    | VPWR_ON = VHF_PWR = VE                                                               | EN2 = 0V or 5.5V                                                                      | -1    |              | +1    | μΑ    |  |

| HF_PWR Timer                              | tHF                                 | From the rising edge of Hone-shot timer expires (Fig.                                |                                                                                       | 1.05  | 1.31         | 1.46  | S     |  |

| LINEAR REGULATORS (OUT1, O                | UT2)                                |                                                                                      |                                                                                       |       |              |       |       |  |

|                                           |                                     | $I_{LOAD} = 1mA, 3.7V \le V_{IN}$                                                    | 0°C to +85°C                                                                          | -1.3  |              | +1.8  | ]     |  |

| OUT1, OUT2 Output-Voltage                 | Vout1,                              | ≤ 5.5V                                                                               | -40°C to +85°C                                                                        | -1.5  |              | +1.8  | %     |  |

| Accuracy                                  | V <sub>OUT2</sub>                   | 1mA ≤ I <sub>LOAD</sub> ≤ 300mA<br>I <sub>LOAD</sub> = 150mA                         |                                                                                       |       | -1.2         |       | 7/0   |  |

|                                           |                                     |                                                                                      |                                                                                       |       | 0            |       |       |  |

| OUT1, OUT2 Output Current                 | I <sub>OUT</sub> _                  |                                                                                      |                                                                                       | 300   |              |       | mA    |  |

| OUT1, OUT2 Output Current Limit           | ILIM_                               | V <sub>OUT</sub> = 0V                                                                |                                                                                       | 310   | 550          | 940   | mA    |  |

| OUT1, OUT2 Dropout Voltage                | $V_{DO}$                            | $I_{LOAD} = 200 \text{mA}, T_A = +85$                                                | 5°C (Note 3)                                                                          |       | 200          | 380   | mV    |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = +3.7V, C_{IN} = 10 \mu F, C_{BP} = 0.01 \mu F, T_A = -40 ^{\circ}C$  to  $+85 ^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ}C$ .) (Note 1)

| PARAMETER                                               | SYMBOL                                                                         | CONE                                                                                        | DITIONS                                             | MIN                | TYP  | MAX   | UNITS |  |

|---------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------|------|-------|-------|--|

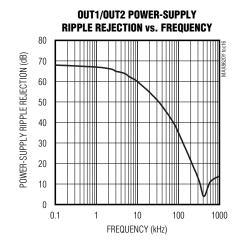

| OUT1, OUT2 Power-Supply<br>Rejection Ratio              |                                                                                | f = 10Hz to $10kHz$ , $CI_{LOAD} = 30mA$                                                    | OUT_ = 4.7μF,                                       |                    | 60   |       | dB    |  |

| Output Naise Valteers                                   |                                                                                | f = 100Hz to 100kHz,<br>I <sub>LOAD</sub> = 30mA                                            | C <sub>OUT</sub> _ = 4.7µF,                         |                    | 45   |       | \/    |  |

| Output Noise Voltage                                    | f = 100Hz to 100kHz, $C_{OUT}$ = 4.7 $\mu$ F, $I_{LOAD}$ = 30mA, $C_{BP}$ open |                                                                                             |                                                     | 100                |      | μVRMS |       |  |

| STEP-DOWN CONVERTER (OUT:                               | 3)                                                                             |                                                                                             |                                                     |                    |      |       |       |  |

| Output Voltage Range                                    | V <sub>OUT3</sub>                                                              |                                                                                             |                                                     | 0.6                |      | 3.3   | V     |  |

| FB Threshold Voltage                                    | V <sub>TH</sub>                                                                | V <sub>FB</sub> falling                                                                     |                                                     |                    | 0.6  |       | V     |  |

| FB Threshold Line Regulation                            |                                                                                | $V_{IN1} = V_{IN2} = 2.7V \text{ to}$                                                       | 5.5V (Note 2)                                       |                    | 0.08 |       | %/V   |  |

| FB Threshold Voltage Accuracy                           |                                                                                | Louize Om A                                                                                 | T <sub>A</sub> = +25°C                              | -2                 |      | +2    | %     |  |

| (Falling) (% of V <sub>TH</sub> )                       |                                                                                | I <sub>OUT3</sub> = 0mA                                                                     | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | -3                 |      | +3    | %     |  |

| FB Threshold Voltage Hysteresis (% of V <sub>TH</sub> ) | V <sub>H</sub> YS                                                              |                                                                                             |                                                     |                    | 2    |       | %     |  |

| ED Disa Ossessat                                        |                                                                                | OUT3 disabled                                                                               |                                                     |                    | 10   |       |       |  |

| FB Bias Current                                         | I <sub>FB</sub>                                                                | V <sub>FB</sub> = 0.5V                                                                      |                                                     |                    | 10   |       | μΑ    |  |

| O                                                       | I <sub>LIM3P</sub>                                                             | pFET switch                                                                                 |                                                     | 675                | 950  | 1200  | A     |  |

| Current Limit                                           | I <sub>LIM3N</sub>                                                             | nFET rectifier                                                                              |                                                     | 875                | 1000 | 1200  | mA    |  |

| On Basistanas                                           | RONP                                                                           | pFET switch, $I_{LX} = -2$                                                                  | 00mA                                                |                    | 0.65 | 1.5   | 0     |  |

| On-Resistance                                           | Ronn                                                                           | nFET rectifier, I <sub>L</sub> X = +                                                        | -200mA                                              |                    | 0.35 | 0.8   | Ω     |  |

| Rectifier-Off Current Threshold                         | ILXOFF                                                                         |                                                                                             |                                                     |                    | 30   | 60    | mA    |  |

| Minimum On and Off Times                                | ton                                                                            |                                                                                             |                                                     |                    | 107  |       | 200   |  |

| Minimum On- and Off-Times                               | toff                                                                           |                                                                                             |                                                     |                    | 95   |       | ns    |  |

| OPEN-DRAIN, ACTIVE-LOW RES                              | ET OUTPUT                                                                      | (RESET)                                                                                     |                                                     |                    |      |       |       |  |

| RESET Output-Voltage Low                                | V <sub>OL</sub>                                                                | ISINK = 500µA                                                                               |                                                     |                    |      | 0.3   | V     |  |

| RESET Output Leakage Current                            |                                                                                | V <sub>RESET</sub> = 5.5V                                                                   |                                                     |                    |      | 100   | nA    |  |

| RESET Threshold Voltage                                 | V <sub>THR</sub>                                                               | Percent of the OUT1 (Note 4)                                                                | regulation voltage                                  | 84                 | 87   | 90    | %     |  |

| RESET Timeout Period                                    | t <sub>RP</sub>                                                                | Figure 4                                                                                    |                                                     | 30                 | 60   |       | ms    |  |

| LDO OUTPUT-VOLTAGE SELECT                               | T INPUTS (SI                                                                   | EL1, SEL2)                                                                                  |                                                     | •                  |      |       | •     |  |

| SEL_ Input Low Threshold                                |                                                                                |                                                                                             |                                                     |                    |      | 1     | V     |  |

| SEL_ Input High Threshold                               |                                                                                |                                                                                             |                                                     | V <sub>IN</sub> 0. | 2V   |       | V     |  |

| SEL_ Input Bias Current                                 |                                                                                | V <sub>IN1</sub> = V <sub>IN2</sub> = 4.2V, V<br>V <sub>SEL2</sub> = 0V or V <sub>IN1</sub> | SEL1 = 0V or V <sub>IN1</sub> ,                     |                    | ±0.1 |       | μA    |  |

- Note 1: Specifications are 100% production tested at  $T_A = +25$ °C. Maximum and minimum limits over temperature are guaranteed by design and characterization.

- Note 2: After startup.

- Note 3: Guaranteed by design.

- Note 4: RESET asserts low when Vout1 drops below the specified percent of the OUT1 regulation voltage.

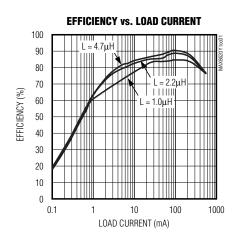

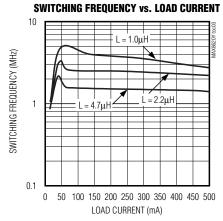

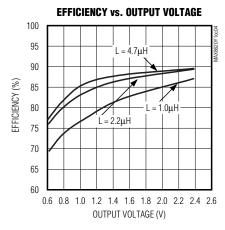

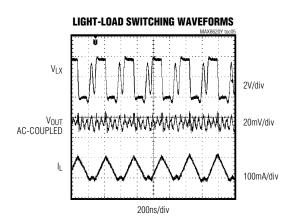

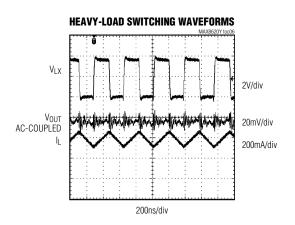

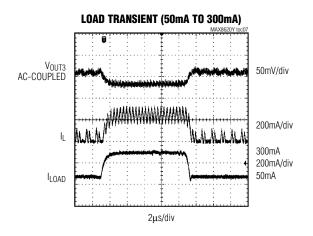

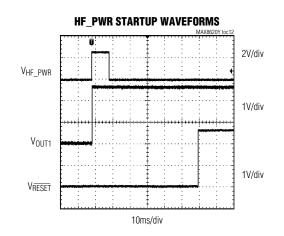

#### **Typical Operating Characteristics**

$(V_{IN1}=V_{IN2}=3.7V, PWR\_ON=IN1, L=2.2\mu H (LQH31CN2R2M53), C_{FF}=150pF, V_{OUT1}=V_{OUT2}=2.6V, V_{OUT3}=1.867V (R1=150k\Omega, R2=75k\Omega), C_{IN}=10\mu F, C_{BP}=0.01\mu F, C_{OUT1}=C_{OUT2}=4.7\mu F, C_{OUT3}=2.2\mu F, \overline{RESET} \ pulled \ up \ with \ 100k\Omega \ to \ OUT1, T_A=+25^{\circ}C, \ unless \ otherwise \ noted.)$

#### Typical Operating Characteristics (continued)

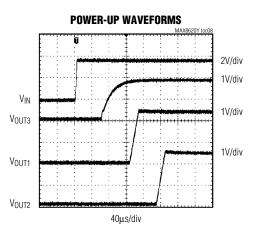

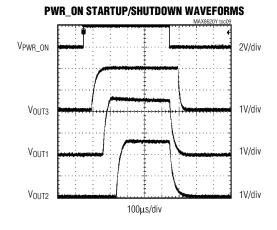

$(V_{IN1}=V_{IN2}=3.7V, PWR\_ON=IN1, L=2.2\mu H (LQH31CN2R2M53), C_{FF}=150pF, V_{OUT1}=V_{OUT2}=2.6V, V_{OUT3}=1.867V (R1=150k\Omega, R2=75k\Omega), C_{IN}=10\mu F, C_{BP}=0.01\mu F, C_{OUT1}=C_{OUT2}=4.7\mu F, C_{OUT3}=2.2\mu F, \overline{RESET} \ pulled up with 100k\Omega to OUT1, T_A=+25°C, unless otherwise noted.)$

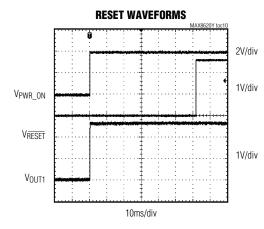

#### Typical Operating Characteristics (continued)

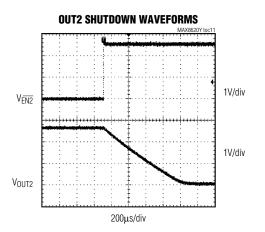

$(V_{IN1}=V_{IN2}=3.7V, PWR\_ON=IN1, L=2.2\mu H (LQH31CN2R2M53), C_{FF}=150pF, V_{OUT1}=V_{OUT2}=2.6V, V_{OUT3}=1.867V (R1=150k\Omega, R2=75k\Omega), C_{IN}=10\mu F, C_{BP}=0.01\mu F, C_{OUT1}=C_{OUT2}=4.7\mu F, C_{OUT3}=2.2\mu F, \overline{RESET} \ pulled \ up \ with \ 100k\Omega \ to \ OUT1, T_A=+25^{\circ}C, \ unless \ otherwise \ noted.)$

### Pin Description

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SEL1   | LDO Output-Voltage Select Input 1. SEL1 and SEL2 set the OUT1 and OUT2 voltages to one of nine combinations (Table 1).                                                                                                                                                                                                                                                                      |

| 2   | SEL2   | LDO Output-Voltage Select Input 2. SEL1 and SEL2 set the OUT1 and OUT2 voltages to one of nine combinations (Table 1).                                                                                                                                                                                                                                                                      |

| 3   | ĒN2    | OUT2 Enable Input. Drive EN2 low to enable OUT2. Drive EN2 high to disable OUT2. If the MAX8620Y is placed into shutdown (PWR_ON = HF_PWR = low), OUT2 does not power regardless of the status of EN2 (Table 2, Figure 4).                                                                                                                                                                  |

| 4   | RESET  | Open-Drain, Active-Low Reset Output. RESET asserts low when V <sub>OUT1</sub> drops below 87% (typ) of regulation. RESET remains asserted for t <sub>RP</sub> after V <sub>OUT1</sub> rises above 87% (typ) of regulation. RESET also asserts when OUT1 is disabled (Figure 4). RESET deasserts if OUT1 is enabled and V <sub>OUT1</sub> is above 87% of regulation after t <sub>RP</sub> . |

| 5   | BP     | Reference Bypass Capacitor Node. Bypass BP with a 0.01µF capacitor to GND. BP is high impedance when the MAX8620Y is disabled (PWR_ON = HF_PWR = low).                                                                                                                                                                                                                                      |

| 6   | HF_PWR | Hands-Free Enable Input. Drive HF_PWR high or apply a pulse to enable the MAX8620Y. Power is enabled for 1.31s (typ) following a rising edge at HF_PWR (Table 2, Figure 4).                                                                                                                                                                                                                 |

| 7   | PWR_ON | Power-Enable Input. Drive PWR_ON high to enable the MAX8620Y (Table 2, Figure 4). Drive PWR_ON low to enter shutdown mode. In shutdown, the LX node is high impedance and both LDOs are disabled (depending on the state of HF_PWR).                                                                                                                                                        |

| 8   | FB     | Step-Down Converter Output-Voltage Feedback Input. VFB regulates to 0.6V (typ). Connect FB to the center of an external resistor-divider between LX and GND to set V <sub>OUT3</sub> between 0.6V and 3.3V (see the Setting the Step-Down Output Voltage (OUT3) section).                                                                                                                   |

| 9   | GND    | Ground. Connect GND to the exposed pad.                                                                                                                                                                                                                                                                                                                                                     |

| 10  | LX     | Inductor Connection. LX is internally connected to the drain of the internal p-channel power MOSFET and the drain of the n-channel synchronous rectifier. LX is high impedance when OUT3 is disabled.                                                                                                                                                                                       |

| 11  | IN2    | Power Input 2. Connect IN2 to IN1 as close to the device as possible.                                                                                                                                                                                                                                                                                                                       |

| 12  | IN1    | Power Input 1. Connect IN1 to IN2 as close to the device as possible. Bypass IN1 to GND with a 10µF ceramic capacitor, as close to the device as possible.                                                                                                                                                                                                                                  |

| 13  | OUT1   | 300mA LDO Output 1. Bypass OUT1 to GND with a 4.7μF ceramic capacitor for 300mA applications, or a 2.2μF ceramic capacitor for 150mA applications. OUT1 is high impedance when disabled.                                                                                                                                                                                                    |

| 14  | OUT2   | 300mA LDO Output 2. Bypass OUT2 to GND with a 4.7µF ceramic capacitor for 300mA applications, or a 2.2µF ceramic capacitor for 150mA applications. OUT2 is high impedance when disabled.                                                                                                                                                                                                    |

| EP  | EP     | Exposed Pad. Connect EP to GND.                                                                                                                                                                                                                                                                                                                                                             |

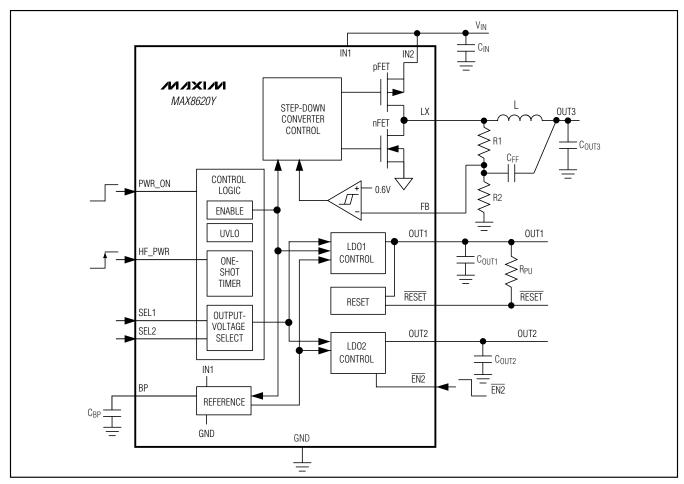

#### **Detailed Description**

The MAX8620Y  $\mu$ PMIC is designed to power low-corevoltage microprocessors or DSPs in portable devices. The  $\mu$ PMIC contains a fixed-frequency, high-efficiency step-down converter; two low-dropout regulators (LDOs); a 30ms (min) reset timer; and power-on/off control logic (Figure 1).

#### Step-Down DC-DC Control Scheme

The MAX8620Y step-down converter is optimized for high-efficiency voltage conversion over a wide load range while maintaining excellent transient response, minimizing external component size, and minimizing output voltage ripple. The DC-DC converter (OUT3) also features an optimized on-resistance internal MOSFET switch and synchronous rectifier to maximize efficiency. The MAX8620Y utilizes a proprietary hysteretic-PWM control scheme that switches with nearly

fixed frequency up to 4MHz, allowing for ultra-small external components. The step-down converter output current is guaranteed up to 500mA.

When the step-down converter output voltage falls below the regulation threshold, the error comparator begins a switching cycle by turning the high-side pFET switch on. This switch remains on until the minimum ontime (ton) expires and the output voltage is in regulation or the current-limit threshold ( $I_{LIM3P}$ ) is exceeded. Once off, the high-side switch remains off until the minimum off-time (toff) expires and the output voltage again falls below the regulation threshold. During this off period, the low-side synchronous rectifier turns on and remains on until either the high-side switch turns on or the inductor current reduces to the rectifier-off current threshold ( $I_{LXOFF} = 30\text{mA}$  (typ)). The internal synchronous rectifier eliminates the need for an external Schottky diode.

Figure 1. Functional Diagram

#### **Voltage-Positioning Load Regulation**

As seen in Figure 2, the MAX8620Y uses a unique step-down converter feedback network. By taking feedback from the LX node through R1, the usual phase lag due to the output capacitor is removed, making the loop exceedingly stable and allowing the use of a very small ceramic output capacitor. This configuration causes the output voltage to shift by the inductor series resistance multiplied by the load current. This output-voltage shift is known as voltage-positioning load regulation. Voltage-positioning load regulation greatly reduces overshoot during load transients, which effectively halves the peak-to-peak output-voltage excursions compared to traditional step-down converters. See the Load-Transient Response graph in the *Typical Operating Characteristics* section.

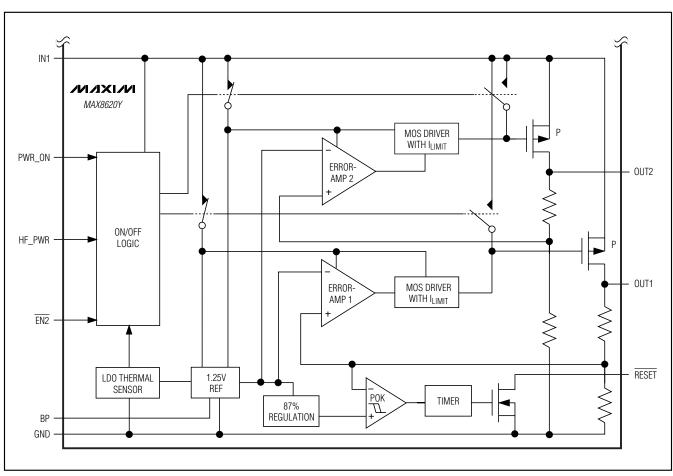

Two low-dropout, low-quiescent-current, high-accuracy linear regulators supply loads up to 300mA each. The LDO output voltages are set using SEL1 and SEL2 (see Table 1). As shown in Figure 3, the LDOs include an internal reference, error amplifiers, p-channel pass transistors, internal-programmable voltage-dividers, and an OUT1 power-good comparator. Each error amplifier

compares the reference voltage to a feedback voltage and amplifies the difference. If the feedback voltage is lower than the reference voltage, the pass-transistor gate is pulled lower, allowing more current to pass to the outputs and increasing the output voltage. If the feedback voltage is too high, the pass-transistor gate is pulled up, allowing less current to pass to the output.

Table 1. MAX8620Y Output-Voltage Selection

| SEL1 | SEL2 | OUT1  | OUT2  |

|------|------|-------|-------|

| IN1  | IN1  | 3.00V | 2.50V |

| IN1  | OPEN | 2.85V | 2.85V |

| IN1  | GND  | 3.00V | 3.00V |

| OPEN | IN1  | 3.30V | 2.50V |

| OPEN | OPEN | 2.80V | 2.60V |

| OPEN | GND  | 3.30V | 1.80V |

| GND  | IN1  | 2.85V | 2.60V |

| GND  | OPEN | 2.60V | 2.60V |

| GND  | GND  | 1.80V | 2.60V |

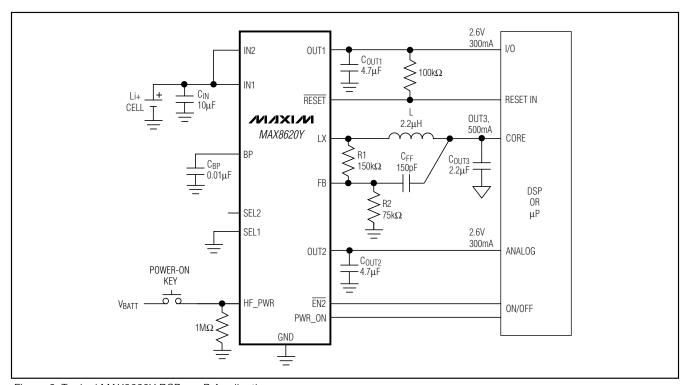

Figure 2. Typical MAX8620Y DSP or µP Application

Figure 3. Linear-Regulator Functional Diagram

#### LDO Output-Voltage Selection (SEL1, SEL2)

As shown in Table 1, the LDO output voltages, OUT1 and OUT2, are set according to the logic states of SEL1 and SEL2. SEL1 and SEL2 are trilevel inputs: IN1, open, and GND. The input voltage,  $V_{\rm IN1}$ , must be a dropout voltage ( $V_{\rm DO}$ ) greater than the selected OUT1 and OUT2 voltages.

#### Power-Enable Input (PWR\_ON)

Drive PWR\_ON low to place the MAX8620Y in power-down mode and reduce supply current to 5.5µA (typ). Connect PWR\_ON to IN1 = IN2 or logic-high to enable the MAX8620Y. EN2 enables and disables OUT2 when

PWR\_ON is high (Table 2). OUT1, OUT2, and OUT3 are all disabled when PWR\_ON is low. HF\_PWR can temporarily bring the MAX8620 out of power-down mode when PWR\_ON is low (see the *HF\_PWR* section). In power-down, the control circuitry, internal-switching p-channel MOSFET, and the internal synchronous rectifier (n-channel MOSFET) turn off, and LX becomes high impedance. In addition, both LDOs are disabled.

#### **OUT2 Enable (EN2)**

Drive  $\overline{\text{EN2}}$  low to enable OUT2. Drive  $\overline{\text{EN2}}$  high to disable OUT2. If the MAX8620Y is placed into power-down using PWR\_ON (PWR\_ON = low), OUT2 does not power regardless of the status of  $\overline{\text{EN2}}$  (Table 2).

**Table 2. MAX8620Y Power Modes**

| PWR_ON | HF_PWR* | EN2 | OUT1 AND OUT3 | OUT2     |

|--------|---------|-----|---------------|----------|

| 1      | X       | 1   | Enabled       | Disabled |

| 1      | X       | 0   | Enabled       | Enabled  |

| 0      | 1       | 1   | Enabled       | Disabled |

| 0      | 1       | 0   | Enabled       | Enabled  |

| 0      | 0       | X   | Disabled      | Disabled |

<sup>\*</sup>A rising edge at HF\_PWR initiates a 1.31s one-shot timer. The status of HF\_PWR shown in Table 2 indicates whether the one-shot period has expired as follows:

#### Hands-Free Enable Input (HF\_PWR)

A rising edge at HF\_PWR generates an internal one-shot pulse that enables the MAX8620Y for 1.31s (t<sub>HF</sub>). If HF\_PWR remains high after t<sub>HF</sub> expires, the MAX8620Y reenters shutdown. During t<sub>HF</sub>, OUT3 and OUT1 are enabled so the microprocessor ( $\mu$ P) can initialize and assert a logic-high at PWR\_ON. OUT2 enables during t<sub>HF</sub> if EN2 is low. Once PWR\_ON is high, the status of HF\_PWR is ignored. If PWR\_ON remains low after t<sub>HF</sub> expires, the MAX8620Y reenters shutdown.

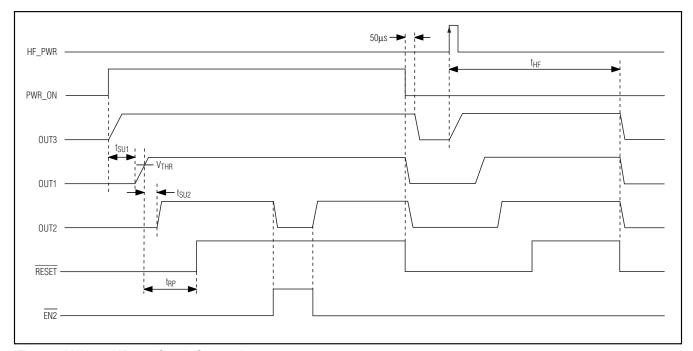

#### **Power-Supply Sequencing**

The step-down converter output (OUT3) always powers up first and powers down last (Figure 4). OUT1 powers approximately 70µs after OUT3, and OUT2 powers approximately 50µs after V<sub>OUT1</sub> reaches 87% (typ) of its regulation voltage. When PWR\_ON goes low, OUT1 turns off, then OUT2 turns off, then OUT3 turns off 50µs after PWR\_ON goes low.

Figure 4. MAX8620Y Power-Supply Sequencing

$<sup>1 =</sup> During t_{HP}$

$<sup>0 =</sup> t_{HP}$  has expired

#### Reset Output (RESET)

RESET is an open-drain, active-low output that indicates the status of OUT1. RESET is typically pulled up through a  $100k\Omega$  resistor to the system logic voltage. RESET asserts at power-up. The reset timer begins once V<sub>OUT1</sub> reaches 87% of regulation. RESET deasserts 60ms after V<sub>OUT1</sub> rises above 87% (typ) of regulation (see the *Typical Operating Characteristics*). RESET also asserts when OUT1 is disabled.

#### Reference Bypass Capacitor Node (BP)

An optional 0.01 $\mu$ F bypass capacitor at BP creates a lowpass filter for LDO noise reduction. OUT1 and OUT2 exhibit 45 $\mu$ V<sub>RMS</sub> of output-voltage noise with C<sub>BP</sub> = 0.01 $\mu$ F and C<sub>OUT1</sub> = C<sub>OUT2</sub> = 4.7 $\mu$ F.

#### **Undervoltage Lockout**

$V_{\rm IN1} = V_{\rm IN2}$  must exceed the 2.85V typical undervoltage-lockout threshold ( $V_{\rm UVLO}$ ) before the MAX8620Y enables OUT3 to begin power-supply sequencing (see the *Power-Supply Sequencing* section). The UVLO threshold hysteresis is typically 0.5V.

#### **Current Limiting**

The MAX8620Y 300mA LDOs limit their output current to  $I_{LIM}$  = 550mA (typ). If the LDO output current exceeds  $I_{LIM}$ , the corresponding LDO output voltage drops. The step-down converter limits  $I_{LIM3P}$  to 675mA (min).

#### **Thermal-Overload Protection**

Thermal-overload protection limits total power dissipation in the MAX8620Y. Independent thermal-protection circuits monitor the step-down converter and the linear-regulator circuits. When the MAX8620Y junction temperature exceeds T<sub>J</sub> = +160°C, the thermal-overload protection circuit disables the corresponding circuitry, allowing the IC to cool. The thermal-overload protection circuitry enables the MAX8620Y after the junction temperature cools by 15°C, resulting in a pulsed output during continuous thermal-overload conditions. Thermal-overload protection safeguards the MAX8620Y in the

event of fault conditions. For continuous operation, do not exceed the absolute-maximum junction-temperature rating of  $T_{J} = +150$ °C.

#### \_Applications Information

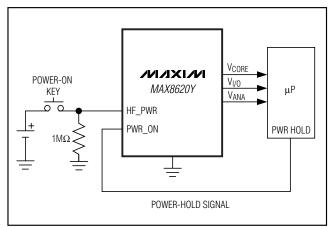

#### **Power-On Closed-Loop System**

When the MAX8620Y is used in conjunction with a microcontroller, HF\_PWR and PWR\_ON can implement a short-key power-on closed-loop system (Figure 5). The MAX8620Y detects a rising edge at HF\_PWR and generates an internal 1.31s (typ) one-shot pulse that begins power sequencing and temporarily enables OUT1, OUT2, and OUT3 (depending on the state of EN2). The 1.31s of power provides time for the processor to initialize and assert a logic-high at PWR\_ON. Once PWR\_ON is driven high, OUT3, OUT1, and OUT2 (depending on the state of EN2) remain enabled. If the microcontroller does not drive PWR\_ON high during the the MAX8620Y disables OUT1, OUT2, and OUT3, and reenters shutdown.

Figure 5. Short-Key Power-On Closed-Loop System

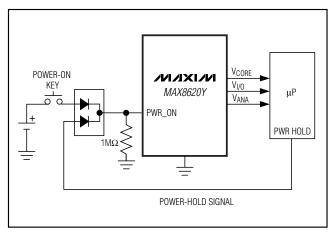

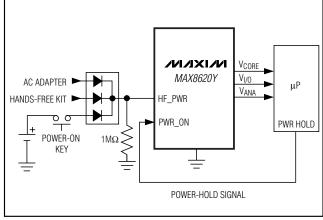

If a long-key press is preferred, see Figure 6. PWR\_ON must remain high until a microprocessor asserts a logic-high signal when using this circuit. If a system includes multiple power-on sources, use a diode OR configuration, as shown in Figure 7.

Figure 6. Long-Key Power-On Closed Loop

Figure 7. Multiple Power-On Inputs

### Setting the Step-Down Output Voltage (OUT3)

Select a step-down converter output voltage between 0.6V and 3.3V by connecting a resistor voltage-divider between LX, FB, and GND (see Figure 2). The FB bias

current, IFB, is typically 10nA. Select R2 so the resistor-divider bias current dominates IFB by a factor of 10. A wide range of resistor values is acceptable, but a good starting point is to choose R2 =  $100k\Omega$ . R1 is given by:

$$R1 = R2 \left( \frac{V_{OUT3}}{V_{FB}} - 1 \right)$$

where  $V_{FB} = 0.6V$ .

V<sub>OUT3</sub> can be set between 0.6V and 3.3V, but the stepdown converter dropout voltage and inductor voltage drop impact how close V<sub>OUT3</sub> can be to V<sub>IN2</sub>. Total dropout voltage is a function of the pFET on-resistance, the DCR of the inductor, and the load as follows:

$$V_{OUT3(DO)} = I_{OUT3} \times (R_{ONP} + DCR_{INDUCTOR})$$

For example, with 300mA load:

$$V_{OUT3(DO)} = 300 \text{mA} \times (0.65\Omega + 50 \text{m}\Omega) = 210 \text{mV}$$

As a result,  $V_{IN1} = V_{IN2}$  must exceed the desired  $V_{OUT3}$  by 210mV to maintain regulation.

#### **Inductor Selection**

The MAX8620Y step-down converter operates with inductors between 1 $\mu$ H and 4.7 $\mu$ H. Low inductance values are physically smaller but require faster switching, which results in some efficiency loss. See the *Typical Operating Characteristics* section for efficiency and switching frequency versus inductor value plots. The inductor's DC current rating needs to be only 100mA greater than the application's maximum load current because the MAX8620Y step-down converter features zero-current overshoot during startup and load transients.

For output voltages above 2.0V, when light-load efficiency is important, the minimum recommended inductor is 2.2  $\mu$ H. For optimum voltage-positioning load transients, choose an inductor with DC series resistance in the  $50m\Omega$  to  $150m\Omega$  range (Table 3). For higher efficiency at heavy loads (above 200mA) or minimal load regulation (but some transient overshoot), the resistance should be kept below  $100m\Omega$ . For light-load applications up to 200mA, much higher resistance is acceptable with very little impact on performance.

**Table 3. Suggested Inductors**

| MANUFACTURER | SERIES    | INDUCTANCE (µH)                 | ESR<br>(Ω)                           | CURRENT RATING (mA)             | DIMENSIONS (mm)                                                                                                                                                                                                                                                |

|--------------|-----------|---------------------------------|--------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | LB2012    | 1.0<br>2.2                      | 0.15<br>0.23                         | 300<br>240                      | 2.0 x 1.25 x 1.25<br>= 3.1mm <sup>3</sup>                                                                                                                                                                                                                      |

|              | LB2016    | 1.0<br>1.5<br>2.2<br>3.3        | 0.09<br>0.11<br>0.13<br>0.20         | 455<br>350<br>315<br>280        | $2.0 \times 1.6 \times 1.8$<br>= $5.8$ mm <sup>3</sup>                                                                                                                                                                                                         |

|              | LB2518    | 1.0<br>1.5<br>2.2<br>3.3        | 0.06<br>0.07<br>0.09<br>0.11         | 500<br>400<br>340<br>270        | 2.5 x 1.8 x 2.0<br>= 9mm <sup>3</sup>                                                                                                                                                                                                                          |

| Taiyo Yuden  | LBC2518   | 1.0<br>1.5<br>2.2<br>3.3<br>4.7 | 0.08<br>0.11<br>0.13<br>0.16<br>0.20 | 775<br>660<br>600<br>500<br>430 | $2.5 \times 1.8 \times 2.0$<br>= $9 \text{mm}^3$                                                                                                                                                                                                               |

|              | CB2012    | 2.2<br>4.7                      | 0.23<br>0.40                         | 410<br>300                      |                                                                                                                                                                                                                                                                |

|              | CB2016    | 2.2<br>4.7                      | 0.13<br>0.25                         | 510<br>340                      | $2.0 \times 1.6 \times 1.8$<br>= $5.8$ mm <sup>3</sup>                                                                                                                                                                                                         |

|              | CB2518    | 2.2<br>4.7                      | 0.09<br>0.13                         | 510<br>340                      | $2.5 \times 1.8 \times 2.0$<br>= 9mm <sup>3</sup>                                                                                                                                                                                                              |

| Murata       | LQH32C_53 | 1.0<br>2.2<br>4.7               | 0.06<br>0.10<br>0.15                 | 1000<br>790<br>650              | $3.2 \times 2.5 \times 1.7$<br>= $14 \text{mm}^3$                                                                                                                                                                                                              |

|              | LQM43FN   | 2.2<br>4.7                      | 0.10<br>0.17                         | 400<br>300                      | = 3.1mm <sup>3</sup> 2.0 x 1.6 x 1.8 = 5.8mm <sup>3</sup> 2.5 x 1.8 x 2.0 = 9mm <sup>3</sup> 2.5 x 1.8 x 2.0 = 9mm <sup>3</sup> 2.0 x 1.25 x 1.25 = 3.1mm <sup>3</sup> 2.0 x 1.6 x 1.8 = 5.8mm <sup>3</sup> 2.5 x 1.8 x 2.0 = 9mm <sup>3</sup> 3.2 x 2.5 x 1.7 |

|              | D310F     | 1.5<br>2.2<br>3.3               | 0.13<br>0.17<br>0.19                 | 1230<br>1080<br>1010            |                                                                                                                                                                                                                                                                |

| TOKO         | D312C     | 1.5<br>2.2<br>2.7<br>3.3        | 0.10<br>0.12<br>0.15<br>0.17         | 1290<br>1140<br>980<br>900      |                                                                                                                                                                                                                                                                |

| Sumida       | CDRH2D11  | 1.5<br>2.2<br>3.3<br>4.7        | 0.05<br>0.08<br>0.10<br>0.14         | 900<br>780<br>600<br>500        |                                                                                                                                                                                                                                                                |

#### **Capacitor Selection**

#### Step-Down Converter Output Capacitor

The output capacitor,  $C_{OUT3}$ , is required to keep the output voltage ripple small and to ensure regulation loop stability.  $C_{OUT3}$  must have low impedance at the switching frequency. Ceramic capacitors with X5R or X7R dielectric are highly recommended due to their small size, low ESR, and small temperature coefficients. Due to the unique feedback network, the output capacitance can be very low. For most applications, a 2.2 $\mu$ F capacitor is sufficient. For optimum load-transient performance and very low output ripple, the output capacitor value in  $\mu$ Fs should be equal to or larger than the inductor value in  $\mu$ Hs.

#### Input Capacitor

The input capacitor,  $C_{IN}$ , reduces the current peaks drawn from the battery or input power source and reduces switching noise in the IC. The impedance of  $C_{IN}$  at the switching frequency should be kept very low. Ceramic capacitors with X5R or X7R dielectrics are highly recommended due to their small size, low ESR, and small temperature coefficients. Use a  $10\mu F$  ceramic capacitor or equivalent amount of multiple capacitors in parallel between IN1 and GND. Connect  $C_{IN}$  as close as possible to the MAX8620Y to minimize the impact of PC board trace inductance.

#### Feed-Forward Capacitor

The feed-forward capacitor, CFF, sets the feedback loop response, controls the switching frequency, and is critical in obtaining the best efficiency possible. Choose a small ceramic COG (NPO) or X7R capacitor with a value given by:

$$C_{FF} = \frac{L}{R1} \times 10S$$

where R1 is the resistor between LX and FB (Figure 2). Select the closest standard value to CFF as possible.

#### LDO Output Capacitors

For applications that require greater than 150mA of output current, connect a 4.7µF ceramic capacitor between the LDO output and GND. For applications that require less than 150mA of output current, connect a 2.2µF ceramic capacitor between the LDO output and GND. The LDO output capacitor's (COUT) equiva-

lent series resistance (ESR) affects stability and output noise. Use output capacitors with an ESR of  $0.1\Omega$  or less to ensure stability and optimum transient response. Surface-mount ceramic capacitors have very low ESR and are commonly available in values up to  $10\mu F$ . Connect COUT as close as possible to the MAX8620Y to minimize the impact of PC board trace inductance.

### Power Dissipation and Thermal Considerations

The MAX8620Y total power dissipation,  $P_D$ , is estimated using the following equations:

$$P_{D} = P_{LOSS(OUT1)} + P_{LOSS(OUT2)} + P_{LOSS(OUT3)}$$

$$P_{LOSS(OUT1)} = I_{(OUT1)}(V_{IN} - V_{OUT1})$$

$$P_{LOSS(OUT2)} = I_{(OUT2)}(V_{IN} - V_{OUT2})$$

$$P_{LOSS(OUT3)} = P_{IN(OUT3)} \left(1 - \frac{\eta}{100}\right) - I_{(OUT3)}^{2}$$

$$\times P_{INDUCTOR}$$

where PIN(OUT3) is the input power for OUT3,  $\eta$  is the step-down converter efficiency, and  $R_{DC(INDUCTOR)}$  is the inductor's DC resistance.

The die junction temperature can be calculated as follows:

$$T_J = T_A + P_D \times \theta_{JA}$$

where  $\theta_{JA} = 55^{\circ}\text{C/W}$  at  $+70^{\circ}\text{C}$ .

T<sub>J</sub> should not exceed +150°C in normal operating conditions.

#### **PC Board Layout and Routing**

High switching frequencies and relatively large peak currents make the PC board layout a very important aspect of design. Good design minimizes excessive EMI on the feedback paths and voltage gradients in the ground plane, both of which can result in instability or regulation errors. Connect C<sub>IN</sub> close to IN1 and GND. Connect the inductor and output capacitors (C<sub>OUT3</sub>) as close to the IC as possible and keep the traces short, direct, and wide.

The traces between C<sub>OUT3</sub>, C<sub>FF</sub>, and FB are sensitive to inductor magnetic-field interference. Route these traces between ground planes or keep the traces away from the inductor.

Connect GND to the ground plane. The external feedback network should be very close to the FB pin, within 0.2in (5mm). Keep noisy traces, such as the LX node, as short as possible. Connect GND to the exposed paddle directly under the IC. Figure 8 and the MAX8620Y evaluation kit illustrate examples of PC board layout and routing schemes.

Figure 8. Recommended PC Board Layout

#### **Pin Configuration**

#### **Chip Information**

**TRANSISTOR COUNT: 4481**

PROCESS: BiCMOS

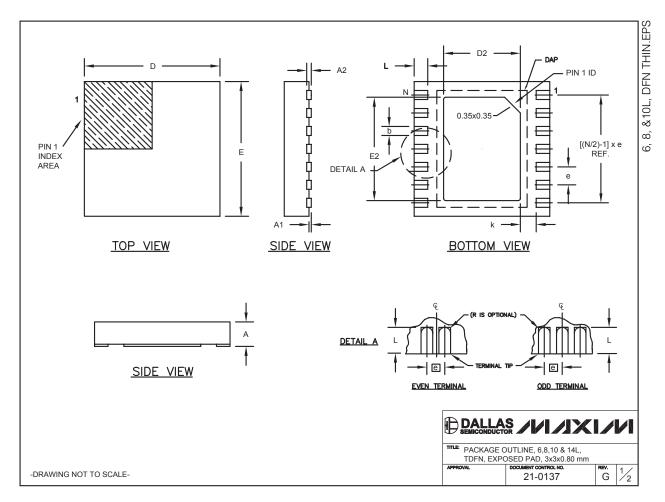

#### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

#### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

| COMMON DIMENSIONS |              |      |  |  |  |  |  |

|-------------------|--------------|------|--|--|--|--|--|

| SYMBOL            | MIN.         | MAX. |  |  |  |  |  |

| Α                 | 0.70         | 0.80 |  |  |  |  |  |

| D                 | 2.90         | 3.10 |  |  |  |  |  |

| E                 | 2.90         | 3.10 |  |  |  |  |  |

| A1                | 0.00         | 0.05 |  |  |  |  |  |

| L 0.20 0.40       |              |      |  |  |  |  |  |

| k 0.25 MIN.       |              |      |  |  |  |  |  |

| A2                | A2 0.20 REF. |      |  |  |  |  |  |

| PACKAGE VARIATIONS |    |           |           |          |                |           |               |                      |

|--------------------|----|-----------|-----------|----------|----------------|-----------|---------------|----------------------|

| PKG. CODE          | N  | D2        | E2        | е        | JEDEC SPEC     | b         | [(N/2)-1] x e | DOWNBONDS<br>ALLOWED |

| T633-1             | 6  | 1.50±0.10 | 2.30±0.10 | 0.95 BSC | MO229 / WEEA   | 0.40±0.05 | 1.90 REF      | NO                   |

| T633-2             | 6  | 1.50±0.10 | 2.30±0.10 | 0.95 BSC | MO229 / WEEA   | 0.40±0.05 | 1.90 REF      | NO                   |

| T833-1             | 8  | 1.50±0.10 | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      | NO                   |

| T833-2             | 8  | 1.50±0.10 | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      | NO                   |

| T833-3             | 8  | 1.50±0.10 | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      | YES                  |

| T1033-1            | 10 | 1.50±0.10 | 2.30±0.10 | 0.50 BSC | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      | NO                   |

| T1433-1            | 14 | 1.70±0.10 | 2.30±0.10 | 0.40 BSC |                | 0.20±0.05 | 2.40 REF      | YES                  |

| T1433-2            | 14 | 1.70±0.10 | 2.30±0.10 | 0.40 BSC |                | 0.20±0.05 | 2.40 REF      | NO                   |

- NOTES:

1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

2. COPLANARITY SHALL NOT EXCEED 0.08 mm.

3. WARPAGE SHALL NOT EXCEED 0.10 mm.

4. PACKAGE LENGTH/PACKAGE WIDTH ARE CONSIDERED AS SPECIAL CHARACTERISTIC(S).

- 5. DRAWING CONFORMS TO JEDEC MO229, EXCEPT DIMENSIONS "D2" AND "E2", AND T1433—1 & T1433—2.

6. "N" IS THE TOTAL NUMBER OF LEADS.

7. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

DALLAS /// SEMICONDUCTOR PACKAGE OUTLINE, 6,8,10 & 14L, TDFN, EXPOSED PAD, 3x3x0.80 mm  $\begin{array}{c|c} \mathbf{EV.} & 2/2 \end{array}$ 21-0137

-DRAWING NOT TO SCALE-

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.