# YAMAHA L SI -----

Outline

MA-3 is a synthesizer LSI for mobile phones that realize advanced game sounds.

This LSI has a built-in speaker amplifier, and thus, is an ideal device for outputting sounds that are used by mobile phones in addition to game sounds and ringing melodies that are replayed by a synthesizer.

**YMU762**

**MA-3**

**Mobile Audio 3**

The synthesizer section adopts "stereophonic hybrid synthesizer system" that are given advantages of both FM synthesizers and Wave Table synthesizers to allow simultaneous generation of up to thirty two FM voices and eight Wave Table voices.

Since FM synthesizer is able to present countless voices by specifying parameters with only several tens of bytes, memory capacity and communication band can be saved, and thus, the device exhibits the features in operating environment of mobile phones such as allowing distribution of arbitrary melodies with voices.

On the other hand, Wave Table synthesizer can pronounce the voice built in ROM and arbitrary ADPCM/PCM voices from sequencer by the download of the melody with voices etc..

MA-3 has a built-in hardware sequencer that helps to realize complex play without heavily loading the host CPU. The device also has a built-in circuit for controlling vibrators and LEDs synchronizing with play of music.

#### Features

MA-3 has features as described below.

- Simultaneous generation of up to 40 tones: FM + Wave Table stereophonic hybrid synthesizer.

- Polyphonic synthesizer specification.

- Has built-in default voices for FM and Wave Table synthesizers in the ROM, and the voices can be downloaded to RAM.

- Fundamental waveforms for FM and algorithm are improved compared with YMU759 (MA-2), and voice parameters of detune etc. are added.

- Stream replay with ADPCM / PCM (shared use of Wave Table section).

- Software interrupt mechanism for external synchronization.

- Equipped with 8 bit parallel I/F for control from CPU.

- Equipped with speaker amplifier and equalizer circuit.

- Equipped with vibration control circuit, and LED lighting control circuit.

- Has built-in PLL to support inputting of master clock up to 20 MHz.

- Contains a 16-bit stereophonic D/A converter.

- Equipped with a stereophonic output terminal for headphone.

- Supports power down mode.

- Digital power supply: 2.7V to 3.3V (Typ 3.0V)

- Analog power supply: 2.7V to 4.5V (Typ 3.6V)

- 32-pin QFN plastic package

The contents of this booklet are target specifications and they are subject to change without a prior notice. Please check the finalized specifications before actually using this LSI.

### YAMAHA CORPORATION

YMU762 CATALOG CATALOG No.:LSI-4MU762A3

## YMU762

YAMAHA

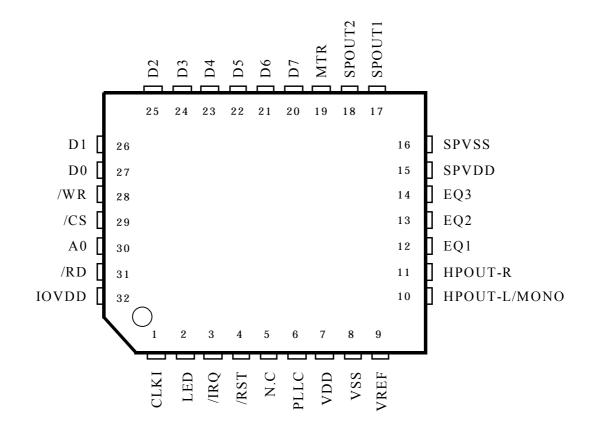

### **Pin configuration**

<32pin QFN Top View>

### Functions of pins

| 6PLLCAVDDbetween this pin and VSS(*).<br>(*)Directly connect VSS used here and VSS of 8th pin.7VDDConnect 0.1 $\mu$ F and 4.7 $\mu$ F capacitors between this pin and VSS.8VSSGround9VREFAVDDAnalog reference voltage<br>Connect 0.1 $\mu$ F capacitor between this pin and VSS.10HPOUT-L/<br>MONOAVDDHeadphone output<br>Equalizer pin 111HPOUT-RAVDDHeadphone output<br>Equalizer pin 113EQ2AVDDEqualizer pin 314EQ3AVDDEqualizer pin 315SPVDDSpeaker amplifier analog power supply (Typ +3.6V)<br>Connect 0.1 $\mu$ F capacitors between this pin and SPVSS.16SPVSSSpeaker connection pin 118SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDExternal motor control pin (Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 6(Drive Capability = 1 mA)21D6I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)23D4I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)                                                                                                                                                                | No. | Pin name | I/O | Power supply | Function                                                                                                  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|--------------|-----------------------------------------------------------------------------------------------------------|--|--|

| 3/IRQ0IOVDDInterrupt output (Drive Capability = 1 mA)4/RSTIshIOVDDHardware reset input5N.CNo Connection (during regular operations)6PLLCAVDDConnection of capacitor for built-in PLL<br>Connect a series connection of 1000 pF capacitor and 3.3 kΩ resist<br>between this pin and VSS(*).<br>(*)Directly connect VSS used here and VSS of 8 <sup>th</sup> pin.7VDDGround8VSSGround9VREFAVDDConnect 0.1 µF capacitors between this pin and VSS.10HPOUT-L/<br>MONOA VDDHeadphone output Lch (Can be used as MONO output)11HPOUT-L/<br>MONOAVDDHeadphone output Lch (Can be used as MONO output)11HPOUT-L/<br>MONOAVDDEqualizer pin 113EQ2AVDDEqualizer pin 315SPVDDSpeaker connection pin 118SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDCPU UF data bus 7(Drive Capability = 1 mA)20D7I/OIOVDDCPU UF data bus 6(Drive Capability = 1 mA)23D4I/OIOVDDCPU UF data bus 3(Drive Capability = 1 mA)24D3I/OIOVDDCPU UF data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU UF data bus 3 <td>1</td> <td>CLKI</td> <td>Ish</td> <td>IOVDD</td> <td>Clock input ( 2 MHz to 20 MHz)</td>                                                                                         | 1   | CLKI     | Ish | IOVDD        | Clock input ( 2 MHz to 20 MHz)                                                                            |  |  |

| 4//RSTIshIOVDDHardware reset input5N.CNo Connection (during regular operations)6PLLCAVDDConnection of capacitor for built-in PLL<br>Connect a series connection of 1000 pF capacitor and 3.3 kΩ resist<br>between this pin and VSS(*).<br>(*)Directly connect VSS used here and VSS of $\delta^{th}$ pin.7VDDPower supply (Typ +3.0V)<br>Connect 0.1 µF and 4.7 µF capacitors between this pin and VSS.8VSSGround9VREFAVDDAnalog reference voltage<br>Connect 0.1 µF capacitor between this pin and VSS.10HPOUT-L/<br>MONOAVDDHeadphone output Lch (Can be used as MONO output)11HPOUT-RAVDDEqualizer pin 113EQ2AVDDEqualizer pin 214EQ3AVDDEqualizer pin 315SPVDDSpeaker connection pin 118SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDCPU L/F data bus 7(Drive Capability = 1 mA)21D6L/OIOVDDCPU L/F data bus 3(Drive Capability = 1 mA)23D4L/OIOVDDCPU L/F data bus 3(Drive Capability = 1 mA)24D3L/OIOVDDCPU L/F data bus 3(Drive Capability = 1 mA)25D2L/OIOVDDCPU L/F data bus 3(Drive Capability = 1 mA)                                                                                                                                                        | 2   | LED      | 0   | IOVDD        | External LED control (Drive Capability = 4 mA)                                                            |  |  |

| 5       N.C       -       -       No Connection (during regular operations)         6       PLLC       A       VDD       Connection of capacitor for built-in PLL<br>Connect a series connection of 1000 pF capacitor and 3.3 kΩ resists<br>between this pin and VSS(*).         7       VDD       -       -       Power supply (Typ +3.0V)         8       VSS       -       -       Ground         9       VREF       A       VDD       Analog reference voltage<br>Connect 0.1 µF capacitor between this pin and VSS.         10       HPOUT-L/<br>MONO       A       VDD       Headphone output       Lch (Can be used as MONO output)         11       HPOUT-R       A       VDD       Equalizer pin 1       1         13       EQ2       A       VDD       Equalizer pin 2         14       EQ3       A       VDD       Equalizer pin 3         15       SPVDD       -       -       Speaker amplifier analog ground         17       SPOUT1       A       SPVDD       Speaker amplifier analog ground         17       SPUD1       -       -       Speaker amplifier analog ground         17       SPUD1       A       SPVDD       Speaker connection pin 1         18       SPUUT1       A       SPVDD | 3   | /IRQ     | 0   | IOVDD        | Interrupt output (Drive Capability = 1 mA)                                                                |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4   | /RST     | Ish | IOVDD        | Hardware reset input                                                                                      |  |  |

| 6PLLCAVDDConnect a series connection of 1000 pF capacitor and 3.3 kΩ resists<br>between this pin and VSS(*).<br>(*)Directly connect VSS used here and VSS of 8 <sup>th</sup> pin.7VDDPower supply (Typ +3.0V)<br>Connect 0.1 µF and 4.7 µF capacitors between this pin and VSS.8VSSGround9VREFAVDDAnalog reference voltage<br>Connect 0.1 µF capacitor between this pin and VSS.10HPOUT-L/<br>MONOAVDDHeadphone output<br>Equalizer pin 113EQ2AVDDEqualizer pin 214EQ3AVDDEqualizer pin 315SPVDDSpeaker amplifier analog power supply (Typ +3.6V)<br>Connect 0.1 µF and 4.7 µF capacitors between this pin and SPVSS.16SPVSSSpeaker amplifier analog ground17SPODDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 120D7I/OIOVDDCPU IF data bus 721D6I/OIOVDDCPU IF data bus 422D5I/OIOVDDCPU IF data bus 423D4I/OIOVDDCPU IF data bus 424D3I/OIOVDDCPU IF data bus 425D2I/OIOVDDCPU IF data bus 426D1I/OIOVDDCPU IF data bus 427D0I/OIOVDDCP                                                                                                                                                                                                                 | 5   | N.C      | _   | —            | No Connection (during regular operations)                                                                 |  |  |

| 7VDDConnect 0.1 $\mu$ F and 4.7 $\mu$ F capacitors between this pin and VSS.8VSSGround9VREFAVDDAnalog reference voltage<br>Connect 0.1 $\mu$ F capacitor between this pin and VSS.10HPOUT-L/<br>MONOAVDDHeadphone output<br>Equalizer pin 111HPOUT-RAVDDHeadphone output<br>Equalizer pin 113EQ2AVDDEqualizer pin 214EQ3AVDDEqualizer pin 315SPVDDSpeaker amplifier analog power supply (Typ +3.6V)<br>Connect 0.1 $\mu$ F and 4.7 $\mu$ F capacitors between this pin and SPVSS.16SPVSSSpeaker amplifier analog ground17SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDCPU I/F data bus 7(Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 6(Drive Capability = 1 mA)21D6I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)23D4I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)26D1I/O <td< td=""><td>6</td><td>PLLC</td><td>А</td><td>VDD</td><td>Connect a series connection of 1000 pF capacitor and 3.3 k<math>\Omega</math> resistor between this pin and VSS(*).</td></td<>           | 6   | PLLC     | А   | VDD          | Connect a series connection of 1000 pF capacitor and 3.3 k $\Omega$ resistor between this pin and VSS(*). |  |  |

| 9VREFAVDDAnalog reference voltage<br>Connect 0.1 $\mu$ F capacitor between this pin and VSS.10HPOUT-L/<br>MONOAVDDHeadphone outputLch (Can be used as MONO output)11HPOUT-RAVDDHeadphone outputRch12EQ1AVDDEqualizer pin 113EQ2AVDDEqualizer pin 214EQ3AVDDEqualizer pin 315SPVDDSpeaker amplifier analog power supply (Typ +3.6V)<br>Connect 0.1 $\mu$ F and 4.7 $\mu$ F capacitors between this pin and SPVSS.16SPVSSSpeaker connection pin 118SPOUT1ASPVDDSpeaker connection pin 219MTROIOVDDCPU I/F data bus 720D7I/OIOVDDCPU I/F data bus 621D6I/OIOVDDCPU I/F data bus 423D4I/OIOVDDCPU I/F data bus 324D3I/OIOVDDCPU I/F data bus 325D2I/OIOVDDCPU I/F data bus 126D1I/OIOVDDCPU I/F data bus 027D0I/OIOVDDCPU I/F data bus 028/WR1IOVDDCPU I/F read enable29/CS1IOVDDCPU I/F read enable29/CS1IOVDDCPU I/F read enable29/CS1IOVDDCPU I/F read enable29/CS1IOVDDCPU                                                                                                                                                                                                                                                                                                                                      | 7   | VDD      | —   | —            |                                                                                                           |  |  |

| 9VREFAVDDConnect 0.1 $\mu$ F capacitor between this pin and VSS.10HPOUT-L/<br>MONOAVDDHeadphone outputLch (Can be used as MONO output)11HPOUT-RAVDDEqualizer pin 112EQ1AVDDEqualizer pin 214EQ2AVDDEqualizer pin 315SPVDDSpeaker amplifier analog power supply (Typ +3.6V)<br>Connect 0.1 $\mu$ F and 4.7 $\mu$ F capacitors between this pin and SPVSS.16SPVSSSpeaker connection pin 118SPOUT1ASPVDDSpeaker connection pin 219MTROIOVDDExternal motor control pin (Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 721D6I/OIOVDDCPU I/F data bus 6(Drive Capability = 1 mA)22D5I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)23D4I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)27D0I/O <td< td=""><td>8</td><td>VSS</td><td>_</td><td>_</td><td></td></td<>                                                                                                                                                  | 8   | VSS      | _   | _            |                                                                                                           |  |  |

| 10MONOAVDDHeadphone outputLch (Can be used as MONO output)11HPOUT-RAVDDHeadphone outputRch12EQ1AVDDEqualizer pin 113EQ2AVDDEqualizer pin 214EQ3AVDDEqualizer pin 315SPVDDSpeaker amplifier analog power supply (Typ +3.6V)<br>Connect 0.1 $\mu$ F and 4.7 $\mu$ F capacitors between this pin and SPVSS.16SPVSSSpeaker amplifier analog ground17SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDCPU I/F data bus 720D7I/OIOVDDCPU I/F data bus 621D6I/OIOVDDCPU I/F data bus 522D5I/OIOVDDCPU I/F data bus 423D4I/OIOVDDCPU I/F data bus 324D3I/OIOVDDCPU I/F data bus 325D2I/OIOVDDCPU I/F data bus 126D1I/OIOVDDCPU I/F data bus 027D0I/OIOVDDCPU I/F data bus 028/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F write enable29/CS <t< td=""><td>9</td><td>VREF</td><td>А</td><td>VDD</td><td></td></t<>                                                                                                                                                                                                                                                                                                  | 9   | VREF     | А   | VDD          |                                                                                                           |  |  |

| 12EQ1AVDDEqualizer pin 113EQ2AVDDEqualizer pin 214EQ3AVDDEqualizer pin 315SPVDDSpeaker amplifier analog power supply (Typ +3.6V)<br>Connect 0.1 $\mu$ F and 4.7 $\mu$ F capacitors between this pin and SPVSS.16SPVSSSpeaker amplifier analog ground17SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDExternal motor control pin (Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 721D6I/OIOVDDCPU I/F data bus 622D5I/OIOVDDCPU I/F data bus 523D4I/OIOVDDCPU I/F data bus 324D3I/OIOVDDCPU I/F data bus 325D2I/OIOVDDCPU I/F data bus 126D1I/OIOVDDCPU I/F data bus 127D0I/OIOVDDCPU I/F data bus 028/WRIIOVDDCPU I/F data bus 029/CSIIOVDDCPU I/F data bus 029/CSIIOVDDCPU I/F ead enable29/CSIIOVDDCPU I/F ead enable29/CSIIOVDDCPU I/F ead enable29/RDIIOVDDCPU I/F ead enable29/RDIIOVDD <t< td=""><td>10</td><td></td><td>A</td><td>VDD</td><td>Headphone output Lch (Can be used as MONO output)</td></t<>                                                                                                                                                                                                                                                    | 10  |          | A   | VDD          | Headphone output Lch (Can be used as MONO output)                                                         |  |  |

| 13EQ2AVDDEqualizer pin 214EQ3AVDDEqualizer pin 315SPVDD $ -$ Speaker amplifier analog power supply (Typ +3.6V)<br>Connect 0.1 µF and 4.7 µF capacitors between this pin and SPVSS.16SPVSS $ -$ Speaker amplifier analog ground17SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDExternal motor control pin (Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 721D6I/OIOVDDCPU I/F data bus 622D5I/OIOVDDCPU I/F data bus 523D4I/OIOVDDCPU I/F data bus 424D3I/OIOVDDCPU I/F data bus 325D2I/OIOVDDCPU I/F data bus 126D1I/OIOVDDCPU I/F data bus 127D0I/OIOVDDCPU I/F data bus 028/WRIIOVDDCPU I/F data bus 029/CSIIOVDDCPU I/F hip select30A0IIOVDDCPU I/F read enable29/CSIIOVDDCPU I/F read enable29/RDIIOVDDCPU I/F read enable29/RDIIOVDDCPU I/F read enable29/RDIIOVDDCPU I/F read enable29/RDI <td< td=""><td>11</td><td>HPOUT-R</td><td>А</td><td>VDD</td><td>Headphone output Rch</td></td<>                                                                                                                                                                                                                                                                  | 11  | HPOUT-R  | А   | VDD          | Headphone output Rch                                                                                      |  |  |

| 14EQ3AVDDEqualizer pin 315SPVDDSpeaker amplifier analog power supply (Typ +3.6V)<br>Connect 0.1 $\mu$ F and 4.7 $\mu$ F capacitors between this pin and SPVSS.16SPVSSSpeaker amplifier analog ground17SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDExternal motor control pin (Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 721D6I/OIOVDDCPU I/F data bus 622D5I/OIOVDDCPU I/F data bus 523D4I/OIOVDDCPU I/F data bus 424D3I/OIOVDDCPU I/F data bus 325D2I/OIOVDDCPU I/F data bus 126D1I/OIOVDDCPU I/F data bus 027D0I/OIOVDDCPU I/F data bus 028/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F chip select30A0IIOVDDCPU I/F read enable29/CSIIOVDDCPU I/F read enable29/CSI <td>12</td> <td>EQ1</td> <td>А</td> <td>VDD</td> <td>Equalizer pin 1</td>                                                                                                                                                                                                                                                                                 | 12  | EQ1      | А   | VDD          | Equalizer pin 1                                                                                           |  |  |

| 15SPVDDSpeaker amplifier analog power supply (Typ +3.6V)<br>Connect 0.1 $\mu$ F and 4.7 $\mu$ F capacitors between this pin and SPVSS.16SPVSSSpeaker amplifier analog ground17SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDExternal motor control pin (Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 721D6I/OIOVDDCPU I/F data bus 622D5I/OIOVDDCPU I/F data bus 523D4I/OIOVDDCPU I/F data bus 424D3I/OIOVDDCPU I/F data bus 325D2I/OIOVDDCPU I/F data bus 226D1I/OIOVDDCPU I/F data bus 127D0I/OIOVDDCPU I/F data bus 028/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F hip select30A0IIOVDDCPU I/F address signal31/RDIIOVDDCPU I/F read enablePin power supply (Typ +3.0V)Pin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13  | EQ2      | А   | VDD          | Equalizer pin 2                                                                                           |  |  |

| 15SPVDDConnect 0.1 $\mu$ F and 4.7 $\mu$ F capacitors between this pin and SPVSS.16SPVSSSpeaker amplifier analog ground17SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDExternal motor control pin (Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 721D6I/OIOVDDCPU I/F data bus 622D5I/OIOVDDCPU I/F data bus 523D4I/OIOVDDCPU I/F data bus 424D3I/OIOVDDCPU I/F data bus 325D2I/OIOVDDCPU I/F data bus 126D1I/OIOVDDCPU I/F data bus 127D0I/OIOVDDCPU I/F data bus 028/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F chip select30A0IIOVDDCPU I/F read enable29/CSIIOVDDCPU I/F read enable29/CSIIOVDDCPU I/F read enable29/CSIIOVDDCPU I/F cad enable29/CSIIOVDDCPU I/F read enable29/CSIIOVDDCPU I/F read enable29/RDIIOVDDCPU I/F cad reas signal31/RDIIOVDDCPU I/F read enable<                                                                                                                                                                                                                                                                                                                                                                              | 14  | EQ3      | А   | VDD          | · · ·                                                                                                     |  |  |

| 16SPVSSSpeaker amplifier analog ground17SPOUT1ASPVDDSpeaker connection pin 118SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDExternal motor control pin (Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 7(Drive Capability = 1 mA)21D6I/OIOVDDCPU I/F data bus 6(Drive Capability = 1 mA)22D5I/OIOVDDCPU I/F data bus 5(Drive Capability = 1 mA)23D4I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 2(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)28/WR1IOVDDCPU I/F write enable29/CS1IOVDDCPU I/F write enable29/CS1IOVDDCPU I/F ead enable30A01IOVDDCPU I/F ead enable31/RD1IOVDDCPU I/F ead enable9Pin power supply (Typ +3.0V)Pin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                          | 15  | SPVDD    | _   | _            |                                                                                                           |  |  |

| 18SPOUT2ASPVDDSpeaker connection pin 219MTROIOVDDExternal motor control pin (Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 7(Drive Capability = 1 mA)21D6I/OIOVDDCPU I/F data bus 6(Drive Capability = 1 mA)22D5I/OIOVDDCPU I/F data bus 5(Drive Capability = 1 mA)23D4I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 2(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)29/CSIIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)30A0IIOVDDCPU I/F write enable31/RDIIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)31Pin power supply (Typ +3.0V)Pin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                         | 16  | SPVSS    | _   | _            | Speaker amplifier analog ground                                                                           |  |  |

| 19MTROIOVDDExternal motor control pin (Drive Capability = 4 mA)20D7I/OIOVDDCPU I/F data bus 7(Drive Capability = 1 mA)21D6I/OIOVDDCPU I/F data bus 6(Drive Capability = 1 mA)22D5I/OIOVDDCPU I/F data bus 5(Drive Capability = 1 mA)23D4I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 2(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F write enable30A0IIOVDDCPU I/F read enable31/RDIIOVDDCPU I/F read enable9Pin power supply (Typ +3.0V)Pin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17  | SPOUT1   | А   | SPVDD        | Speaker connection pin 1                                                                                  |  |  |

| 20D7I/OIOVDDCPU I/F data bus 7(Drive Capability = 1 mA)21D6I/OIOVDDCPU I/F data bus 6(Drive Capability = 1 mA)22D5I/OIOVDDCPU I/F data bus 5(Drive Capability = 1 mA)23D4I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 2(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)29/CSIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F write enable30A0IIOVDDCPU I/F read enable31/RDIIOVDDCPU I/F read enable9Pin power supply (Typ +3.0V)Pin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18  | SPOUT2   | А   | SPVDD        | Speaker connection pin 2                                                                                  |  |  |

| 21D6I/OIOVDDCPU I/F data bus 6(Drive Capability = 1 mA)22D5I/OIOVDDCPU I/F data bus 5(Drive Capability = 1 mA)23D4I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 2(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)29/CSIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F chip select30A0IIOVDDCPU I/F read enable31/RDIIOVDDCPU I/F read enablePin power supply (Typ +3.0V)IIOVDDCPU I/F write start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19  | MTR      | 0   | IOVDD        | External motor control pin (Drive Capability = 4 mA)                                                      |  |  |

| 21D6I/OIOVDDCPU I/F data bus 6(Drive Capability = 1 mA)22D5I/OIOVDDCPU I/F data bus 5(Drive Capability = 1 mA)23D4I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 2(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)29/CSIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F chip select30A0IIOVDDCPU I/F read enable31/RDIIOVDDCPU I/F read enablePin power supply (Typ +3.0V)IIOVDDCPU I/F write start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20  | D7       | I/O | IOVDD        |                                                                                                           |  |  |

| 22D5I/OIOVDDCPU I/F data bus 5(Drive Capability = 1 mA)23D4I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 2(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F write enable30A0IIOVDDCPU I/F address signal31/RDIIOVDDCPU I/F read enablePin power supply (Typ +3.0V)IIOVDDCPU I/F write y=3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21  | D6       |     |              |                                                                                                           |  |  |

| 23D4I/OIOVDDCPU I/F data bus 4(Drive Capability = 1 mA)24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 2(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F write enable30A0IIOVDDCPU I/F address signal31/RDIIOVDDCPU I/F read enablePin power supply (Typ +3.0V)IIOVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | D5       |     |              |                                                                                                           |  |  |

| 24D3I/OIOVDDCPU I/F data bus 3(Drive Capability = 1 mA)25D2I/OIOVDDCPU I/F data bus 2(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F chip select30A0IIOVDDCPU I/F read enable31/RDIIOVDDCPU I/F read enablePin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |          |     |              |                                                                                                           |  |  |

| 25D2I/OIOVDDCPU I/F data bus 2(Drive Capability = 1 mA)26D1I/OIOVDDCPU I/F data bus 1(Drive Capability = 1 mA)27D0I/OIOVDDCPU I/F data bus 0(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F chip select30A0IIOVDDCPU I/F address signal31/RDIIOVDDCPU I/F read enablePin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | D3       |     |              | · · · · · ·                                                                                               |  |  |

| 27D0I/OIOVDDCPU I/F data bus 0<br>CPU I/F data bus 0<br>(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F chip select30A0IIOVDDCPU I/F address signal31/RDIIOVDDCPU I/F read enablePin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25  | D2       | I/O | IOVDD        |                                                                                                           |  |  |

| 27D0I/OIOVDDCPU I/F data bus 0<br>CPU I/F data bus 0<br>(Drive Capability = 1 mA)28/WRIIOVDDCPU I/F write enable29/CSIIOVDDCPU I/F chip select30A0IIOVDDCPU I/F address signal31/RDIIOVDDCPU I/F read enablePin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26  | D1       | I/O | IOVDD        | CPU I/F data bus 1 (Drive Capability = $1 \text{ mA}$ )                                                   |  |  |

| 29     /CS     I     IOVDD     CPU I/F chip select       30     A0     I     IOVDD     CPU I/F address signal       31     /RD     I     IOVDD     CPU I/F read enable       Pin power supply (Typ +3.0V)     Pin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27  | D0       | I/O | IOVDD        |                                                                                                           |  |  |

| 30     A0     I     IOVDD     CPU I/F address signal       31     /RD     I     IOVDD     CPU I/F read enable       Pin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28  | /WR      | Ι   | IOVDD        | CPU I/F write enable                                                                                      |  |  |

| 31     /RD     I     IOVDD     CPU I/F read enable       Pin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29  | /CS      | Ι   | IOVDD        | CPU I/F chip select                                                                                       |  |  |

| Pin power supply (Typ +3.0V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30  | A0       | Ι   | IOVDD        | CPU I/F address signal                                                                                    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31  | /RD      | Ι   | IOVDD        | CPU I/F read enable                                                                                       |  |  |

| board).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32  | IOVDD    | _   | _            | Be sure to apply potential equivalent to 7 <sup>th</sup> pin (directly connect on the                     |  |  |

~

A : Analog pin Ish : Schmitt input

YAMAHA

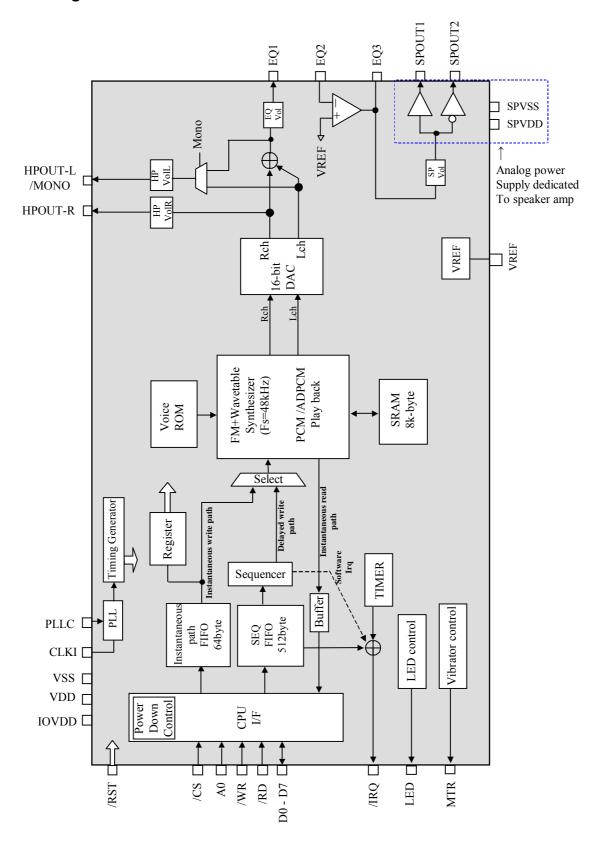

### **Block diagram**

### YAMAHA

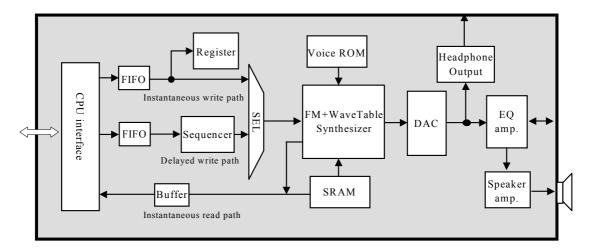

### **Outline of blocks**

This section outlines functions of blocks contained in this device and flow of signals.

#### **CPU** interface

CPU interface is an 8-bit parallel type.

- "Instantaneous write path" that enables Write command immediately (equipped with 64byte FIFO),

- "Delayed write path" that enables Write command after elapse of specified time, and

- Instantaneous read path

are available.

#### Hardware sequencer and FIFO

The sequencer is a block that controls time and register access.

The structure of sequence data includes "time information data + MA-3 register control data", for which 512 byte FIFO is provided. The sequence data is written into delayed write path.

#### FM+Wave Table synthesizer

This device contains a Polyphonic synthesizer that adopts FM +Wave Table stereophonic hybrid system that generates up to 40 tones.

The FM synthesizer has two operation modes; "16-Voice 4 operation mode" and "32-Voice 2 operation mode" which can be changed to each other freely (except during tone generation).

Since waveform for FM operation can be set arbitrarily, the device is able to create voices that are more complex than by conventional devices.

Wave Table synthesizers is able to generate eight voices simultaneously, and supports 8 bit PCM and 4 bit ADPCM data format. The sampling frequency is 48 kHz. Stream replaying is also available, realizing interchangeability with ADPCM replay capability of MA-2.

#### Voice ROM and SRAM

This device stores voice parameters (GM 128 voices + DRUM 40 voices) for FM and waveform data for Wave Table in the ROM. SRAM is used when downloading arbitrary FM voice parameter and waveform data for Wave Table. It is also used as waveform data buffer at stream replay with PCM/ADPCM.

#### DAC

Converts digital signal from a synthesizer into analog signal. The data length is 16 bit.

#### **IRQ and TIMER**

This device supports FIFO, two hardware TIMERs, and interrupt output with software interrupt.

#### Headphone output

This device supports stereophonic analog output for the headphone. Monaural output is available.

#### EQ amplifier

The filter response and gain of the amplifier can be changed by adjusting external parts such as resistors and/or capacitors.

#### Speaker amplifier

A speaker amplifier of which maximum out is 580 mW at SPVDD=3.6V is built in this device. A control that adjusts the output level of the amplifier is provided in the previous stage of the amplifier.

#### LED and vibrator control block

LEDs and vibrator can be controlled synchronizing with a play. Control asynchronous with play is also possible.

#### **Clock generating block**

This devices supports clock input ranging from 2 MHz to 20 MHz. (Stop = 0 Hz is possible at power down.) This block increases the frequency of inputted clock with various frequency by using PLL to create clocks with fixed frequency that are needed in the device.

## YAMAHA

### **Electrical Characteristics**

#### Absolute maximum rating

| Item                                                        | Symbol            | Min. | Max.      | Unit |

|-------------------------------------------------------------|-------------------|------|-----------|------|

| SPVDD pin, power supply voltage (Speaker amplifier section) | SPVDD             | -0.3 | 6.0       | v    |

| VDD pin, power supply voltage                               | VDD               | -0.3 | 4.2       | V    |

| IOVDD pin, power supply voltage                             | IOVDD             | -0.3 | 4.2       | V    |

| SPOUT1, SPOUT2 pin, applied voltage                         | V <sub>INSP</sub> | -0.3 | SPVDD+0.3 | V    |

| Analog input voltage                                        | V <sub>INA</sub>  | -0.3 | VDD+0.3   | V    |

| Digital input voltage                                       | V <sub>IND</sub>  | -0.3 | IOVDD+0.3 | V    |

| Permissible loss (*)                                        | Pd                |      | 1197      | mW   |

| Storage temperature                                         | T <sub>STG</sub>  | -50  | 125       | °C   |

Note: VSS = SPVSS = 0V

(\*) : Top= 25 °C, and glass epoxy PCB ( $30mm \times 100mm \times 1.0mm$ ) is installed.

Operation with Top= 25 °C or higher degrees the permissible loss at the rate of 12mW per 1 °C.

#### **Recommended operating conditions**

| Item                                                   | Symbol          | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|-----------------|------|------|------|------|

| SPVDD operating voltage<br>(Speaker amplifier section) | SPVDD           | 2.7  | 3.6  | 4.5  | V    |

| VDD operating voltage                                  | VDD             | 2.7  | 3.0  | 3.3  | V    |

| IOVDD operating voltage                                | IOVDD           | 2.7  | 3.0  | 3.3  | V    |

| Operating ambient temperature                          | T <sub>OP</sub> | -20  | 25   | 85   | °C   |

Note: VSS = SPVSS = 0V

Make VDD and IOVDD into same electric potential (Connect them directly on the circuit board).

#### **DC** characteristics

| Item                     | Symbol          | Condition      | Min.               | Тур. | Max.                      | Unit |

|--------------------------|-----------------|----------------|--------------------|------|---------------------------|------|

| Input voltage "H" level  | V <sub>IH</sub> |                | $0.7 \times IOVDD$ |      |                           | V    |

| Input voltage "L" level  | V <sub>IL</sub> |                |                    |      | $0.2 \times \text{IOVDD}$ | V    |

| Output voltage "H" level | V <sub>OH</sub> | $I_{OH} = (*)$ | $0.8 \times IOVDD$ |      |                           | V    |

| Output voltage "L" level | V <sub>OL</sub> | $I_{OL} = (*)$ |                    |      | 0.4                       | V    |

| Schmitt width            | Vsh             |                |                    | 0.5  |                           | V    |

| Input leakage current    | IL              |                | -10                |      | 10                        | μA   |

| Input capacity           | CI              |                |                    |      | 10                        | pF   |

Note: T<sub>OP</sub>=-20 to 85°C, VDD, IOVDD=3.0±0.3V, Capacitor load=50 pF

(\*): /IRQ, D0 ~ D7 are  $I_{OH}$ = -1 mA,  $I_{OL}$ = +1 mA LED, MTR are  $I_{OH}$ = -4 mA,  $I_{OL}$ = +4 mA

### YAMAHA

#### AC characteristics

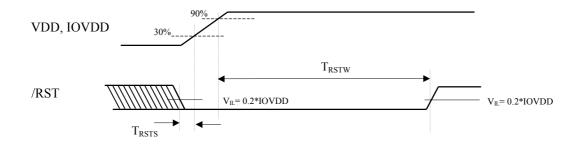

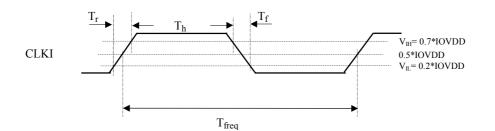

#### /RST, CLKI

| Item                                         | Symbol            | Min. | Тур. | Max. | Unit |  |  |

|----------------------------------------------|-------------------|------|------|------|------|--|--|

| /RST "L" pulse width                         | T <sub>RSTW</sub> | 100  |      |      | μs   |  |  |

| /RST (indefinite $\rightarrow$ L) setup time | T <sub>RSTS</sub> | 0    |      |      | μs   |  |  |

| CLKI frequency                               | 1 / Tfreq         | 0    |      | 20   | MHz  |  |  |

| CLKI rise / fall time                        | Tr / Tf           |      |      | 30   | ns   |  |  |

| CLKI duty factor                             | Th / Tfreq        | 30   | 50   | 70   | %    |  |  |

Note: T<sub>OP</sub>=-20 to 85°C, VDD, IOVDD=3.0±0.3V, Capacitor load=50 pF

The input to Clock can be stopped (=0Hz) during reset period and power down state (DP0=1). However, the input level is to be H or L, and input of intermediate level is prohibited.

The reset width is defined as the time from the moment VDD or IOVDD has risen to 90%. /RST has to be settled at "L" level at the time VDD or IOVDD has risen to 30%.

| Meas              | surement point |

|-------------------|----------------|

| $V_{\mathrm{IH}}$ | = 0.7*IOVDD    |

| $V_{IL}$          | = 0.2*IOVDD    |

| $V_{OH}$          | = 0.8*IOVDD    |

| VOL               | = 0.2*IOVDD    |

|                   |                |

### YAMAHA

### CPU interface

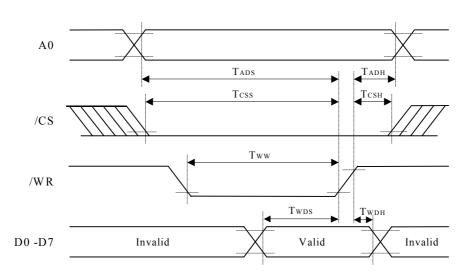

| (Write cycle)          |                  |     |      |      |  |  |  |  |  |

|------------------------|------------------|-----|------|------|--|--|--|--|--|

| Item                   | Symbol           | Min | Max. | Unit |  |  |  |  |  |

| Address setup time     | T <sub>ADS</sub> | 50  |      | ns   |  |  |  |  |  |

| Address hold time      | T <sub>ADH</sub> | 0   |      | ns   |  |  |  |  |  |

| Chip select setup time | T <sub>CSS</sub> | 50  |      | ns   |  |  |  |  |  |

| Chip select hold time  | T <sub>CSH</sub> | 0   |      | ns   |  |  |  |  |  |

| Write pulse width      | $T_{WW}$         | 50  |      | ns   |  |  |  |  |  |

| Data setup time        | T <sub>WDS</sub> | 30  |      | ns   |  |  |  |  |  |

| Data hold time         | T <sub>WDH</sub> | 0   |      | ns   |  |  |  |  |  |

T<sub>OP</sub>=-20 to 85°C, VDD,IOVDD=3.0±0.3V, Capacitor load=50 pF

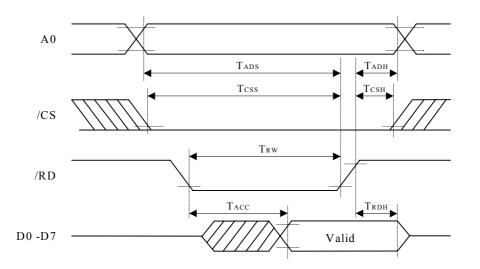

| (Read cycle)           |                  |     |      |      |  |  |  |

|------------------------|------------------|-----|------|------|--|--|--|

| Item                   | Symbol           | Min | Max. | Unit |  |  |  |

| Address setup time     | T <sub>ADS</sub> | 80  |      | ns   |  |  |  |

| Address hold time      | T <sub>ADH</sub> | 0   |      | ns   |  |  |  |

| Chip select setup time | T <sub>CSS</sub> | 80  |      | ns   |  |  |  |

| Chip select hold time  | T <sub>CSH</sub> | 0   |      | ns   |  |  |  |

| Read pulse width       | T <sub>RW</sub>  | 80  |      | ns   |  |  |  |

| Read data access time  | T <sub>ACC</sub> |     | 70   | ns   |  |  |  |

| Data hold time         | T <sub>RDH</sub> | 0   | 30   | ns   |  |  |  |

T<sub>OP</sub>=-20 to 85°C, VDD,IOVDD=3.0±0.3V, Capacitor load=50 pF

Write cycle

Note : Under the conditions of  $T_{CSH} \ge 0ns$ ,

$\begin{array}{ll} T_{ADH,}\,T_{WDH}: & \mbox{Defined with respect to the point where the rise of /WR has reached 0.7*IOVDD.} \\ T_{ADS,}\,T_{WDS}: & \mbox{Defined with respect to the point where the rise of /WR has reached 0.2*IOVDD.} \end{array}$

YAMAHA

Read cycle

Note : Under the conditions of  $T_{CSH} \ge 0$ ns,

| T <sub>ADH</sub> , T <sub>RDH</sub> : | : | Defined with respect to the point where the rise of /RD has reached 0.7*IOVDD.         |

|---------------------------------------|---|----------------------------------------------------------------------------------------|

| T <sub>ADS</sub> , T <sub>CSS</sub> : | : | Defined with respect to the point where the rise of /RD has reached 0.2*IOVDD.         |

| T <sub>ACC</sub> :                    | : | Defined with respect to the point where any of $/CS$ , $/RD$ and A0 has changed later. |

| T <sub>RDH</sub> :                    | : | Time to the point where D0-D7 pins become high impedance.                              |

#### **Power consumption**

| Item                                              |  | Typical | Max. | Unit |

|---------------------------------------------------|--|---------|------|------|

| Load current of VDD+ IOVDD (at regular operation) |  | 25      |      | mA   |

| At SPVDD side no tone                             |  | 4       |      | mA   |

| At SPVDD side 80hm load 400mW output              |  | 210     |      | mA   |

| Power down mode (VDD + IOVDD+SPVDD) (*)           |  | 1       | 10   | μA   |

Note: T<sub>OP</sub>=-20 to 85°C, VDD, IOVDD=3.0±0.3V, SPVDD=3.6V

(\*) : Measurement condition : /CS input pin is fixed to  $V_{IH}\!\!=\!\!VDD.$

#### Analog characteristics

Conditions of  $T_{OP}$ =25°C, VDD, IOVDD=3.0V and SPVDD=3.6V apply to all items.

#### SP amplifier

| Item                                                    | Min. | Typical  | Max. | Unit  |

|---------------------------------------------------------|------|----------|------|-------|

| Gain setting (fixed)                                    |      | ±2       |      | times |

| Min. load resistance (RL)                               |      | 8        |      | Ω     |

| Max. output voltage amplitude (RL= $8\Omega$ )          |      | 6.0      |      | Vp-p  |

| Max. output power (RL= $8\Omega$ , THD+N $\leq 1.0\%$ ) |      | 580      |      | mW    |

| THD + N (RL= $8\Omega$ , f=1 kHz, output = 400mW)       |      | 0.025    |      | %     |

| Noise at no signal (A-filter: weighting filter)         |      | -90      |      | dBV   |

| PSRR (f=1 kHz)                                          |      | 90       |      | dB    |

| Amplitude center potential (VSEL2, VSEL1 =0, 0)         |      | 0.6×VDD  |      | V     |

| (VSEL2, VSEL1 =0, 1)                                    |      | 0.5×VDD  |      | V     |

| (VSEL2, VSEL1 =1, 0)                                    |      | 0.67×VDD |      | V     |

| Differential Output Voltage                             |      | 10       | 50   | mV    |

#### EQ amplifier

| Item                                    | Min. | Typical | Max. | Unit |

|-----------------------------------------|------|---------|------|------|

| Gain settable range                     |      |         | 30   | dB   |

| Max. output voltage amplitude           |      | 2.7     |      | Vp-p |

| THD + N $(f=1 \text{ kHz})$             |      |         | 0.05 | %    |

| Noise at no signal (A-filter)           |      | -90     |      | dBV  |

| Input impedance                         | 10   |         |      | MΩ   |

| Feedback resistance between EQ2 and EQ3 | 20   |         |      | kΩ   |

#### SP Volume

| Item                        | Min. | Typical | Max. | Unit |

|-----------------------------|------|---------|------|------|

| Volume setting range        | -30  |         | 0    | dB   |

| Volume step width           |      | 1       |      | dB   |

| THD + N $(f=1 \text{ kHz})$ |      |         | 0.05 | %    |

#### EQ Volume

| Item                          | Min. | Typical | Max. | Unit |

|-------------------------------|------|---------|------|------|

| Volume setting range          | -30  |         | 0    | dB   |

| Volume step width             |      | 1       |      | dB   |

| Noise at no signal (A-filter) |      | -90     |      | dBV  |

| Max. output current           | 120  |         |      | μΑ   |

| Max. output voltage amplitude |      | 1.5     |      | Vp-p |

| Output impedance              |      | 300     | 600  | Ω    |

## YAMAHA

#### HP Volume

| Item                          | Min. | Typical | Max. | Unit |

|-------------------------------|------|---------|------|------|

| Volume setting range          | -30  |         | 0    | dB   |

| Volume step width             |      | 1       |      | dB   |

| Noise at no signal (A-filter) |      | -90     |      | dBV  |

| Max. output current           | 120  |         |      | μΑ   |

| Max. output volt. amplitude   |      | 1.5     |      | Vp-p |

| Output impedance              |      | 300     | 600  | Ω    |

#### VREF

| Item         | Min. | Typical | Max. | Unit |

|--------------|------|---------|------|------|

| VREF voltage |      | 0.5×VDD |      | V    |

#### DAC

| Item                                  | Min.     | Typical | Max. | Unit |

|---------------------------------------|----------|---------|------|------|

| Resolution                            |          | 16      |      | Bit  |

| Full scale output volt.               |          | 1.5     |      | Vp-p |

| THD+N $(f=1 \text{ kHz})$             |          |         | 0.5  | %    |

| Noise at no signal (A-filter)         |          | -85     | -80  | dBV  |

| Frequency response (f=50Hz to 20 kHz) | -3.0 (*) |         | +0.5 | dB   |

(\*): Reduction of response in high frequency range caused by aperture effect

YAMAHA

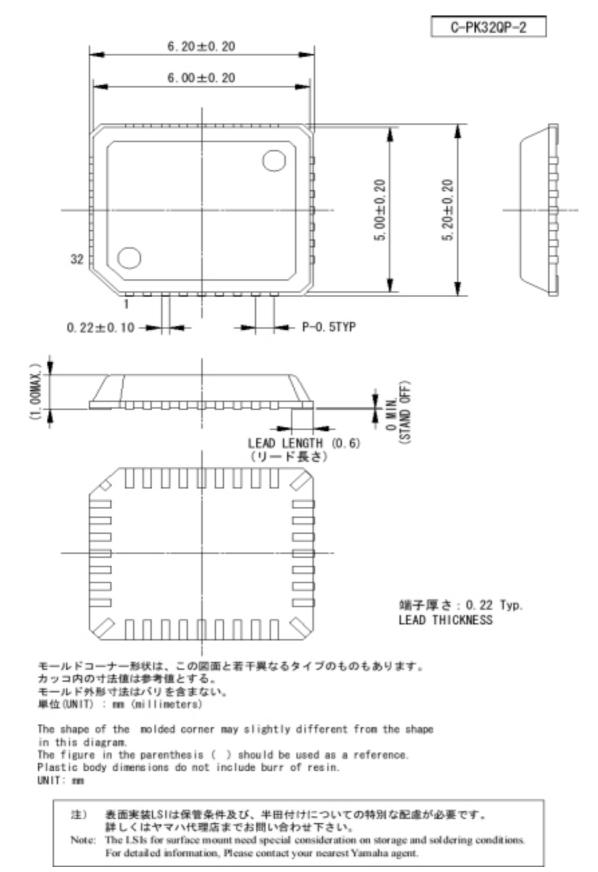

### External dimensions of package

#### **IMPORTANT NOTICE**

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANYTHIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

Note) The specifications of this product are subject to change without notice.

| Agency | Address inquiries to:                                                                                                                                       |         |                                                   |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------|--|--|

| C J    | <ul> <li>Semiconductor Sales &amp; Marketing Department</li> <li>Head Office 203, Matsunokijima, Toyooka-mu<br/>Iwata-gun, Shizuoka-ken, 438-019</li> </ul> |         |                                                   |  |  |

|        | Tel. +81-539-6                                                                                                                                              | 62-4918 | Fax. +81-539-62-5054                              |  |  |

|        | ■ Tokyo Office                                                                                                                                              |         | , Takanawa, Minato-ku,<br>108-8568                |  |  |

|        | Tel. +81-3-548                                                                                                                                              | 38-5431 | Fax. +81-3-5488-5088                              |  |  |

|        | ■ Osaka Office                                                                                                                                              |         | , Minami Senba, Chuo-ku,<br>City, Osaka, 542-0081 |  |  |

|        | Tel. +81-6-625                                                                                                                                              | 52-6221 | Fax. +81-6-6252-6229                              |  |  |