# YSS243B

### AC3F

AC-3 5.1ch Full decoder

#### OUTLINE

YSS243B(AC3F) is a Dolby AC-3 5.1 channel full decoder LSI which decodes the signal that has been coded as prescribed in IEC958 interface standard and outputs PCM data conforming to the Dolby AC-3 specification. This LSI provides very accurate PCM data, because the decoding process uses 24 bit DSP. Use of low frequency clock(20 MHz) for its operation achieves low power consumption. Thus, it is not

#### FEATURES

- Both AC-3 and PCM data can be accepted for input data format. Output channel(s) can be selected from monaural to various down-mixing modes, or 5.1channels of PCM data.

- Processes Dolby AC-3 data at the rate of up to 640 kbps.

- Operates in AC-3 karaoke mode.

- Has a built-in buffer for input data. Has data interface terminals for connection of external SRAM. Note: It is necessary to add an external SRAM (256K bits) to be used for buffering the output data.

- Has a built-in PLL oscillation circuit to generate its own operating clock(20 MHz). Thus the frequency of an operating clock generated by the crystal oscillator, or of an external clock, can be selected in the range between 2.5 and 40 MHz.

- Interface formats for input data and output data can be specified independently.

necessary to consider radiation of heat when designing an AC-3 decoding system.

- Processes one selected language data decoding from multi-language encoded data (possible to decode based on data stream number).

- Generates either pink noise or white noise as specified in the control register.

- Has two more mixed signal output channels in addition to 5.1 PCM data output channels.

- Controls time delay of signals at center and surround channels with respect to the left and right channel signals.

- One of four types of dynamic range compression methods recommended by Dolby, can be selected.

- Compression of dynamic range for high amplitude signals and low level signals can be made independently by setting the control register.

- Reads AC-3 bitstream information through the microprocessor interface.

- The delay time for processing AC-3 data decoding is fixed to three audio blocks(768 samples).

- 5V single power supply, Si-gate CMOS process.

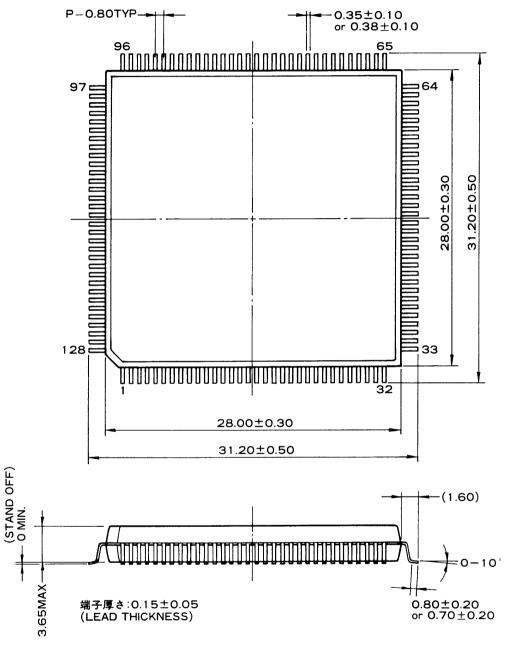

- 128 pin QFP (YSS243B-F)

.dzsc.com

Note: "Dolby" and "AC-3" are registered trademarks of Dolby laboratories Licensing Corporation.

Use of this LSI requires licensing by Dolby Laboratories Licensing Corporation.

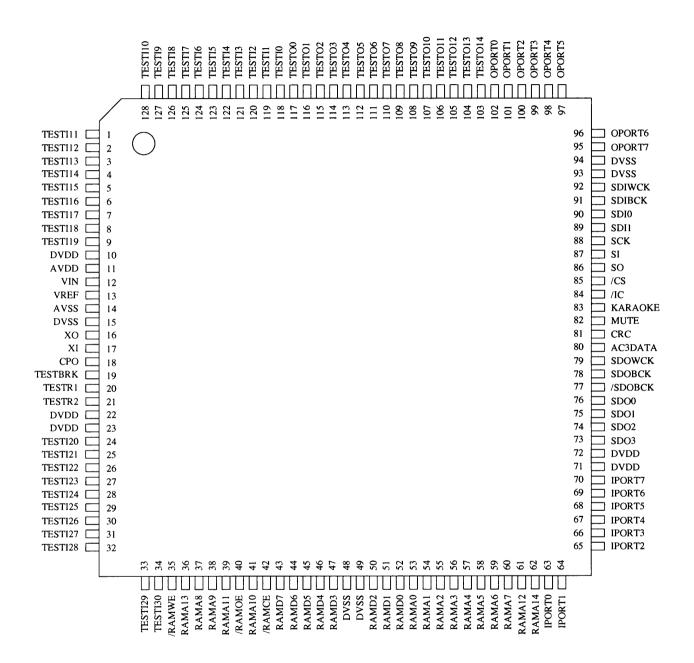

#### **■PIN CONFIGURATION**

< 128 pin QFP top view >

# **YSS243B**

#### **PIN FUNCTION**

| No. | NAME    | I/O | FUNCTION                                                               |

|-----|---------|-----|------------------------------------------------------------------------|

| 1   | TESTI11 | I+  | LSI test terminal (To be open in use)                                  |

| 2   | TESTI12 | I+  | LSI test terminal (To be open in use)                                  |

| 3   | TESTI13 | I+  | LSI test terminal (To be open in use)                                  |

| 4   | TESTI14 | I+  | LSI test terminal (To be open in use)                                  |

| 5   | TESTI15 | I+  | LSI test terminal (To be open in use)                                  |

| 6   | TESTI16 | I+  | LSI test terminal (To be open in use)                                  |

| 7   | TESTI17 | I+  | LSI test terminal (To be open in use)                                  |

| 8   | TESTI18 | I+  | LSI test terminal (To be open in use)                                  |

| 9   | TESTI19 | I+  | LSI test terminal (To be open in use)                                  |

| 10  | DVDD    | -   | +5V power supply (for digital circuit)                                 |

| 11  | AVDD    | -   | +5V power supply (for PLL circuit)                                     |

| 12  | VIN     | ΑI  | Input terminal for PLL circuit                                         |

|     |         |     | Connect with CPO terminal through the external analog filter.          |

| 13  | VREF    | AI  | Input terminal for PLL circuit                                         |

| 1   |         |     | Connect with AVDD through the external analog filter.                  |

| 14  | AVSS    | -   | Ground (for PLL circuit)                                               |

| 15  | DVSS    | -   | Ground (for digital circuit)                                           |

| 16  | XO      | О   | Connect with crystal oscillator                                        |

| 17  | XI      | I   | Connect with crystal oscillator or input external clock (2.5M~40.0MHz) |

| 18  | CPO     | AO  | Output terminal for PLL circuit                                        |

|     |         |     | Connect with VIN terminal through the external analog filter.          |

| 19  | TESTBRK | I+  | LSI test terminal (To be open in use)                                  |

| 20  | TESTR1  | I+  | LSI test terminal (To be open in use)                                  |

| 21  | TESTR2  | I+  | LSI test terminal (To be open in use)                                  |

| 22  | DVDD    | -   | +5V power supply (for digital circuit)                                 |

| 23  | DVDD    | -   | +5V power supply (for digital circuit)                                 |

| 24  | TESTI20 | I+  | LSI test terminal (To be open in use)                                  |

| 25  | TESTI21 | I+  | LSI test terminal (To be open in use)                                  |

| 26  | TESTI22 | I+  | LSI test terminal (To be open in use)                                  |

| 27  | TESTI23 | I+  | LSI test terminal (To be open in use)                                  |

| 28  | TESTI24 | I+  | LSI test terminal (To be open in use)                                  |

| 29  | TESTI25 | I+  | LSI test terminal (To be open in use)                                  |

| 30  | TESTI26 | I+  | LSI test terminal (To be open in use)                                  |

| 31  | TESTI27 | I+  | LSI test terminal (To be open in use)                                  |

| 32  | TESTI28 | I+  | LSI test terminal (To be open in use)                                  |

| 33  | TESTI29 | I+  | LSI test terminal (To be open in use)                                  |

| 34  | TESTI30 | I+  | LSI test terminal (To be open in use)                                  |

| 35  | /RAMWE  | O   | External SRAM Interface /WE                                            |

| 36  | RAMA13  | O   | External SRAM Interface address                                        |

| 37  | RAMA8   | O   | External SRAM Interface address                                        |

| 38  | RAMA9   | O   | External SRAM Interface address                                        |

| 39  | RAMA11  | 0   | External SRAM Interface address                                        |

| 40  | /RAMOE  | O   | External SRAM Interface /OE                                            |

| 41  | RAMA10  | O   | External SRAM Interface address                                        |

| 42  | /RAMCE  | 0   | External SRAM Interface /CE                                            |

| 43  | RAMD7   | I/O | External SRAM Interface data                                           |

| 44  | RAMD6   | ΙΌ  | External SRAM Interface data                                           |

| 45  | RAMD5   | I/O | External SRAM Interface data                                           |

| 46  | RAMD4   | I/O | External SRAM Interface data                                           |

| 47  | RAMD3   | Ι/O | External SRAM Interface data                                           |

| No.      | NAME     | I/O      | FUNCTION                                                                                 |

|----------|----------|----------|------------------------------------------------------------------------------------------|

| 48       | DVSS     | -        | Ground (for digital circuit)                                                             |

| 49       | DVSS     | -        | Ground (for digital circuit)                                                             |

| 50       | RAMD2    | I/O      | External SRAM Interface data                                                             |

| 51       | RAMD1    | I/O      | External SRAM Interface data                                                             |

| 52       | RAMD0    | I/O      | External SRAM Interface data                                                             |

| 53       | RAMA0    | О        | External SRAM Interface address                                                          |

| 54       | RAMA1    | О        | External SRAM Interface address                                                          |

| 55       | RAMA2    | О        | External SRAM Interface address                                                          |

| 56       | RAMA3    | О        | External SRAM Interface address                                                          |

| 57       | RAMA4    | О        | External SRAM Interface address                                                          |

| 58       | RAMA5    | О        | External SRAM Interface address                                                          |

| 59       | RAMA6    | О        | External SRAM Interface address                                                          |

| 60       | RAMA7    | О        | External SRAM Interface address                                                          |

| 61       | RAMA12   | О        | External SRAM Interface address                                                          |

| 62       | RAMA14   | О        | External SRAM Interface address                                                          |

| 63       | IPORT0   | I+       | Input port for general purpose                                                           |

| 64       | IPORT1   | I+       | Input port for general purpose                                                           |

| 65       | IPORT2   | I+       | Input port for general purpose                                                           |

| 66       | IPORT3   | I+       | Input port for general purpose                                                           |

| 67       | IPORT4   | I+       | Input port for general purpose                                                           |

| 68       | IPORT5   | I+       | Input port for general purpose                                                           |

| 69       | IPORT6   | I+       | Input port for general purpose                                                           |

| 70       | IPORT7   | I+       | Input port for general purpose                                                           |

| 71       | DVDD     | -        | +5V power supply (for digital circuit)                                                   |

| 72       | DVDD     | -        | +5V power supply (for digital circuit)                                                   |

| 73       | SDO3     | O        | PCM output terminal (MIX0, MIX1)                                                         |

| 74       | SDO2     | О        | PCM output terminal (C, LFE)                                                             |

| 75       | SDO1     | O        | PCM output terminal (LS, RS)                                                             |

| 76       | SDO0     | O        | PCM output terminal (L, R)                                                               |

| 77       | /SDOBCK  | O        | Output terminal of inverted SDOBCK                                                       |

| 78       | SDOBCK   | I+       | Bit clock for SDO output                                                                 |

| 79       | SDOWCK   | I+       | Word clock for SDO output                                                                |

| 80       | AC3DATA  | O        | Detection of AC-3 bitstream data                                                         |

| 81       | CRC      | 0        | Detection of CRC error (when AC-3 bitstream data is decoded)                             |

| 82       | MUTE     | 0        | Detection of output data mute                                                            |

| 83       | KARAOKE  | O        | Detection of AC-3 karaoke data                                                           |

| 84       | /IC      | Is<br>Io | Initial clear Microprocessor interface Chip salect                                       |

| 85       | /CS      | Is       | Microprocessor interface Chip select                                                     |

| 86<br>87 | SO<br>SI | O<br>Is  | Microprocessor interface Serial data output Microprocessor interface Serial data input   |

| 88       | SCK      | Is<br>Is | Microprocessor interface Serial data input Microprocessor interface Clock                |

| 89       | SDI1     | IS       | AC-3 bitstream (or PCM) data input terminal                                              |

| 90       | SDI1     | I        | AC-3 bitstream (or PCM) data input terminal  AC-3 bitstream (or PCM) data input terminal |

| 90       | SDIBCK   | I        | Bit clock for SDI input                                                                  |

| 92       | SDIWCK   | I        | Word clock for SDI input                                                                 |

| 93       | DVSS     | 1<br>-   | Ground (for digital circuit)                                                             |

| 93       | DVSS     | -        | Ground (for digital circuit)                                                             |

| 95       | OPORT7   | O        | Output port for general purpose                                                          |

| 96       | OPORT6   | 0        | Output port for general purpose  Output port for general purpose                         |

| 97       | OPORT5   | 0        | Output port for general purpose  Output port for general purpose                         |

| 98       | OPORT4   | O        | Output port for general purpose  Output port for general purpose                         |

| 99       | OPORT3   | 0        | Output port for general purpose  Output port for general purpose                         |

| 27       | OI OICI3 | J        | Output port for general purpose                                                          |

| No. | NAME    | I/O | FUNCTION                              |

|-----|---------|-----|---------------------------------------|

| 100 | OPORT2  | O   | Output port for general purpose       |

| 101 | OPORT1  | О   | Output port for general purpose       |

| 102 | OPORT0  | О   | Output port for general purpose       |

| 103 | TESTO14 | О   | LSI test terminal (To be open in use) |

| 104 | TESTO13 | О   | LSI test terminal (To be open in use) |

| 105 | TESTO12 | 0   | LSI test terminal (To be open in use) |

| 106 | TESTO11 | О   | LSI test terminal (To be open in use) |

| 107 | TESTO10 | О   | LSI test terminal (To be open in use) |

| 108 | TESTO9  | О   | LSI test terminal (To be open in use) |

| 109 | TESTO8  | О   | LSI test terminal (To be open in use) |

| 110 | TESTO7  | О   | LSI test terminal (To be open in use) |

| 111 | TESTO6  | О   | LSI test terminal (To be open in use) |

| 112 | TESTO5  | О   | LSI test terminal (To be open in use) |

| 113 | TESTO4  | О   | LSI test terminal (To be open in use) |

| 114 | TESTO3  | 0   | LSI test terminal (To be open in use) |

| 115 | TESTO2  | 0   | LSI test terminal (To be open in use) |

| 116 | TESTO1  | 0   | LSI test terminal (To be open in use) |

| 117 | TESTO0  | О   | LSI test terminal (To be open in use) |

| 118 | TESTI0  | I+  | LSI test terminal (To be open in use) |

| 119 | TESTI1  | I+  | LSI test terminal (To be open in use) |

| 120 | TESTI2  | I+  | LSI test terminal (To be open in use) |

| 121 | TESTI3  | I+  | LSI test terminal (To be open in use) |

| 122 | TESTI4  | I+  | LSI test terminal (To be open in use) |

| 123 | TESTI5  | I+  | LSI test terminal (To be open in use) |

| 124 | TESTI6  | I+  | LSI test terminal (To be open in use) |

| 125 | TESTI7  | I+  | LSI test terminal (To be open in use) |

| 126 | TESTI8  | I+  | LSI test terminal (To be open in use) |

| 127 | TESTI9  | I+  | LSI test terminal (To be open in use) |

| 128 | TESTI10 | I+  | LSI test terminal (To be open in use) |

NOTE) Is: Schmidt input terminal

I+: Input terminal with a pull-up resistor

AI: Analog input terminal AO: Analog output terminal

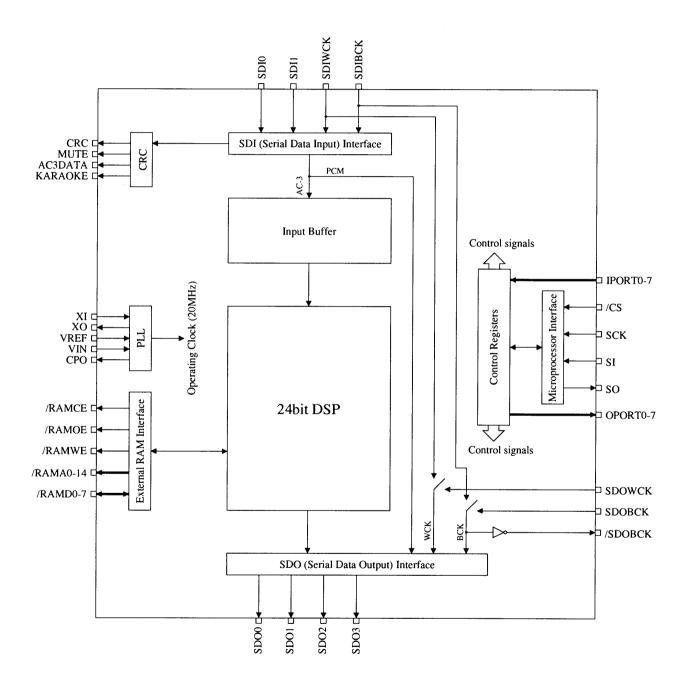

#### **BLOCK DIAGRAM**

#### FUNCTION DESCRIPTION

#### 1. Clocks XI, XO, VREF, CPO

XI and XO terminals are used to form a crystal oscillation circuit. The oscillation frequency is 40 MHz that is divided by 2 internally to provide the operating clock of 20 MHz.

To make clock signal, use XI and XO terminals and perform a self oscillation or feed an external clock signal to the XI terminal.

This LSI operates in a PLL oscillation mode as well. When PLL oscillating mode is chosen and a frequency lower than 20MHz clock signal to the XI terminal is applied to utilize multiplier, an external analog filter has to be connected between VIN, VREF, and CPO terminals.

#### 2. Data Interface SDIBCK, SDIWCK, SDI0, SDI1, SDOBCK, SDOWCK, /SDOBCK, SDO0-3

AC-3 bitstream data or PCM data has to be fed from either SDI0 or SDI1 terminal. This signal has to be synchronized with SDIBCK(bit clock) and SDIWCK(word clock).

PCM data are outputted from the terminals SDO0 to SDO3.

Synchronization of PCM output data with input data of SDIBCK / SDIWCK, or with those clocks inputted from SDOBCK / SDOWCK terminals can be selected according to the setting of the control register.

One of the following parameters can be selected according to the setting of the control register: SDI0 or SDI1 port selection, phase of bit and word clocks, input and output data formats, numbers of data bits.

Please refer to "INPUT/OUTPUT DATA FORMAT" section for detail of interface and serial data format. (page 9)

#### 3. Input Data Status AC3DATA, MUTE, CRC, KARAOKE

Status of SDI input signal can be known by monitoring signals outputted from the AC3DATA, MUTE, CRC, and KARAOKE terminals. Their levels become high when the conditions are met. These status also can be known by reading address 5F of the control registers.

| AC3DATA | Detects whether SDI input is AC-3 bitstream data.       |

|---------|---------------------------------------------------------|

| MUTE    | Detects whether output signals of SD0 to SD3 are muted. |

| CRC     | Detects CRC error in the AC-3 bitstream data.           |

| KARAOKE | Detects whether SDI input is AC-3 karaoke data.         |

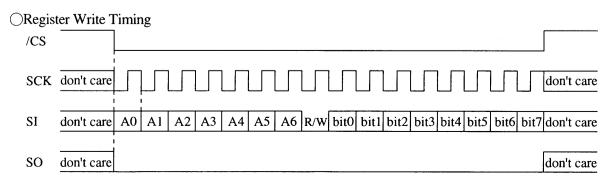

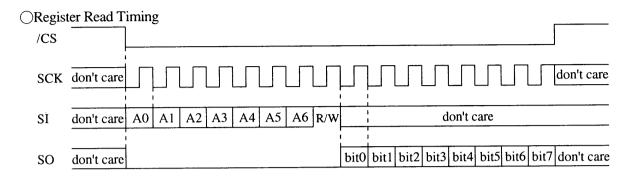

#### 4. Microprocessor Interface /CS, SCK, SI, SO

The control register can be read / written via microprocessor interface. Four terminals /CS, SCK, SI and SO are used for this purpose.

Please refer to the following format chart for the details of read / write timing.

Data read / write method

When writing data:

Set the address bits (A0 to A6) for the first 7 bits of the SI terminal, then set the R/W bit to "0" for writing. Data should be entered from the SI terminal following R/W bit.

#### When reading data:

Set the address bits (A0 to A6) for the first 7 bits of the SI terminal, then set the R/W bit to "1" for reading. Register data will be outputted from the SO terminal with bits 9 to 16 that synchronize with SCK clock.

Note: Both address bits and data bits should be inputted with LSB first.

#### 5. General Purpose I/O ports **OPORT7-0, IPORT7-0**

OPORT7 to 0 terminals are data output ports. Data written on the control register (address \$06) is outputted from these terminals.

IPORT7 to 0 terminals are data input ports. Data entry to the control register (address \$07) should be made from these terminals.

#### 6. External RAM /RAMCE, /RAMOE, /RAMWE, RAMA0-14, RAMD0-7

This LSI requires an external SRAM for outputting the PCM data.

The specifications for the SRAM should be:

Capacity: 256Kbit (32Kwordx8bit)

Access time: 35 nsec or less

#### 7. Initial Clear /IC

This LSI requires initial clear when turning on the power.

#### 8. LSI Test Terminals TESTI0-30, TESTO0-14, TESTR1-2, TESTBRK

TESTI0-30, TESTO0-14, TESTR1-2 and TESTBRK are LSI test terminals. They must be open in normal use.

#### **■INPUT/OUTPUT DATA FORMAT**

| PUI/OUTPUT L                     | AIA FUKIV                           | IAI                                                                                                                                                                                                                                 |

|----------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | R(RS,LFE,MIX1) ch R(RS,LFE,MIX1) ch | 15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0                                                                                                                                                                 |

|                                  | L(LS,C,MIX0) ch L(LS,C,MIX0) ch     | 15  14  13  12   11   10 9   8   7   6   5   4   3   2   1   0     17  16  15  14  13  12   11   10 9   8   7   6   5   4   3   2   1   0     19  18  17  16  15  14  13  12   11   10 9   8   7   6   5   4   3   2   1   0     10 |

| Bit Clock<br>(SDIBCK,<br>SDOBCK) | Word Clock<br>(SDIWCK,<br>SDOWCK)   | Data<br>(SDI,<br>SDO0-3)                                                                                                                                                                                                            |

#### **CONTROL REGISTER**

The AC-3 decoding system is controlled by reading and writing the control registers through microprocessor interface (/CS, SCK, SI, SO).

\* All bits are set to "0" by initial clear except for PLL0 (bit 3) of PLL register (\$00).

#### REGISTER MAP (1)

The following addresses ( $$00 \sim $47$ ) are registers which can read and write.

| The f         | The following addresses ( $$00 \sim $47$ ) are registers which can read and write. |                                     |                                        |              |              |               |              |                 |            |  |  |

|---------------|------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------|--------------|--------------|---------------|--------------|-----------------|------------|--|--|

| addr          | NAME                                                                               | bit 7                               | bit 6                                  | bit 5        | bit 4        | bit 3         | bit 2        | bit 1           | bit 0      |  |  |

| \$00          | PLL register                                                                       | PLLUSE PLL3 - 0                     |                                        |              |              | AC3/PCM       | AMOFF        | SDISEL          |            |  |  |

| \$01          | DSN register                                                                       | PLL8X don't care                    |                                        |              | DSNIGN       |               | DSN2 - 0     |                 |            |  |  |

|               | Mute register                                                                      | LMUTEN                              | CMUTEN                                 | RMUTEN       | RSMUTEN      | LSMUTEN       | LFEMUTEN     | M0MUTEN         | MIMUTEN    |  |  |

| \$03          | SDI register                                                                       | don't                               | care                                   | SDIFN        | /T1 - 0      | SDIB          | T1 - 0       | SDIWP           | SDIBP      |  |  |

| \$04          | SDO register                                                                       | SDOCKSEL                            | don't care                             | SDOF         | MT1 - 0      | SDOB          | IT1 - 0      | SDOWP           | SDOBP      |  |  |

|               | SDO3 register                                                                      | KROKON                              | don't care                             | SDO3F        | MT1 - 0      | SDO3E         | BIT1 - 0     | SDO3WP          | don't care |  |  |

|               | OPORT register                                                                     |                                     |                                        |              | OPOR         | RT7 - 0       |              |                 |            |  |  |

|               | IPORT register                                                                     |                                     | ]                                      | IPORT7 - (   | ) (Unable t  | o write to tl | his register | )               |            |  |  |

| \$08          |                                                                                    |                                     |                                        |              |              |               |              |                 |            |  |  |

| :             | (not used)                                                                         |                                     | These                                  | registers aı | re not assig | ned. (All "(  | O" out when  | n read)         |            |  |  |

| \$1D          |                                                                                    |                                     |                                        |              |              |               |              |                 |            |  |  |

|               | Test register 0                                                                    |                                     |                                        |              |              | SI test. Do   |              |                 |            |  |  |

|               | Test register 1                                                                    |                                     |                                        |              |              | SI test. Do   |              |                 |            |  |  |

|               | Noise register                                                                     | NOISE                               | PN/WN                                  | NFS          | 1 - 0        |               | don't        | care            |            |  |  |

|               | Noise Level register                                                               |                                     |                                        |              |              | LEV7 - 0      |              |                 |            |  |  |

|               | MIX0 L register                                                                    |                                     | MIX0L7 - 0                             |              |              |               |              |                 |            |  |  |

|               | MIX1 L register                                                                    |                                     |                                        |              |              | L7 - 0        |              |                 |            |  |  |

|               | MIX0 C register                                                                    |                                     |                                        |              |              | C7 - 0        |              |                 |            |  |  |

|               | MIX1 C register                                                                    |                                     |                                        |              |              | C7 - 0        |              |                 |            |  |  |

|               | MIX0 R register                                                                    |                                     |                                        |              |              | R7 - 0        |              |                 |            |  |  |

|               | MIX1 R register                                                                    |                                     |                                        |              |              | R7 - 0        |              | ,               |            |  |  |

|               | MIX0 LS register                                                                   |                                     |                                        |              |              | LS7 - 0       |              |                 |            |  |  |

|               | MIX1 LS register                                                                   |                                     |                                        |              |              | LS7 - 0       |              |                 |            |  |  |

|               | MIX0 RS register                                                                   |                                     |                                        |              |              | RS7 - 0       |              |                 |            |  |  |

|               | MIX1 RS register                                                                   |                                     |                                        |              |              | RS7 - 0       |              |                 |            |  |  |

|               | MIX0 LFE register                                                                  |                                     |                                        |              |              | FE7 - 0       |              |                 |            |  |  |

|               | MIX1 LFE register                                                                  |                                     |                                        |              | MIX1L        | FE7 - 0       |              |                 |            |  |  |

|               | Center Delay register                                                              |                                     | don't                                  |              |              |               | CDELA        |                 |            |  |  |

|               | Surround Delay register                                                            |                                     | don't                                  | care         |              |               | SRDEL        | AY3 - 0         |            |  |  |

| \$30          |                                                                                    |                                     |                                        |              |              |               |              | •               |            |  |  |

| :             | (not used)                                                                         |                                     | These                                  | registers ar | e not assign | ned. (All "(  | )" out wher  | n read)         |            |  |  |

| \$3F          |                                                                                    |                                     | ······································ |              |              | 5440          |              | ~~~             |            |  |  |

|               | Compression register                                                               |                                     | don't                                  | care         | ****         |               | DIALOFF      | COMPM           | IOD1 - 0   |  |  |

|               | HDYNRNG register                                                                   |                                     |                                        |              |              | NG7 - 0       |              |                 |            |  |  |

|               | LDYNRNG register                                                                   |                                     |                                        |              |              | NG7 - 0       |              | VIII) ( 0 0 0 0 |            |  |  |

| <b>1</b>      | Output Mode register                                                               | don't care DUALMOD1 - 0 OUTMOD2 - 0 |                                        |              |              |               |              |                 |            |  |  |

|               | PCM register H                                                                     |                                     | PCMSFH7 - 0                            |              |              |               |              |                 |            |  |  |

|               | PCM register L                                                                     |                                     |                                        |              | PCMS         | FL7 - 0       |              |                 |            |  |  |

|               | Dither register                                                                    |                                     |                                        |              | don't care   |               |              |                 | DITHOFF    |  |  |

| <b> </b> \$47 | (not used)                                                                         |                                     |                                        |              | don't        | care          |              |                 |            |  |  |

## YSS243B

#### REGISTER MAP (2)

The following addresses ( $$48 \sim $7F$ ) are read only registers. Unable to write to these registers.

| addr | NAME                  | bit 7                | bit 6     | bit 5        | bit 4       | bit 3        | bit 2      | bit 1   | bit 0   |

|------|-----------------------|----------------------|-----------|--------------|-------------|--------------|------------|---------|---------|

| \$48 | Bitstream register 0  | fsc                  | cod       |              | frmsizecod  |              |            |         |         |

| \$49 | Bitstream register 1  |                      |           | bsid         |             |              | bsmod      |         |         |

|      | Bitstream register 2  |                      | acmod     |              | cmi         | xlev         | surm       | ixlev   | lfeon   |

| \$4B | Bitstream register 3  | dsur                 | mod       | copyrightb   | origbs      | 0            | 0          | 0       | 0       |

|      | Bitstream register 4  | 0                    | 0         | 0            |             |              | dialnorm   |         |         |

| \$4D | Bitstream register 5  | 0                    | 0         | 0            |             |              | dialnorm2  |         |         |

| \$4E | Bitstream register 6  | audprodie            |           |              | mixlevel    |              |            | roor    | ntyp    |

| \$4F | Bitstream register 7  | audprodi2e           |           |              | mixlevel2   |              | -          | roon    | ntyp2   |

|      | Bitstream register 8  | timecodle            |           |              |             |              |            |         |         |

|      | Bitstream register 9  | timecod1             |           |              |             |              |            |         |         |

| \$52 | Bitstream register 10 | timecod2e 0 timecod2 |           |              |             |              |            |         |         |

|      | Bitstream register 11 |                      |           |              | time        | cod2         |            |         |         |

|      | Bitstream register 12 | langcode             | langcod2e | compre       | compr2e     | 0            | 0          | 0       | 0       |

|      | Bitstream register 13 |                      |           |              | lang        | gcod         |            |         |         |

|      | Bitstream register 14 |                      |           |              | lang        | cod2         |            |         |         |

|      | Bitstream register 15 |                      |           |              | coi         | npr          |            |         |         |

|      | Bitstream register 16 | .,                   |           |              | con         | npr2         |            |         |         |

|      | Bitstream register 17 |                      |           |              | dyr         | ırng         |            |         |         |

|      | Bitstream register 18 |                      |           |              | dyn         | rng2         |            |         |         |

| \$5B |                       |                      |           |              |             |              |            |         |         |

|      | (not used)            |                      | These     | registers ar | e not assig | ned. (All "( | )" out whe | n read) |         |

| \$5E |                       |                      |           |              |             |              |            |         |         |

|      | Status register       | 0                    | 0         | 0            | 0           | KARAOKE      | MUTE       | CRC     | AC3DATA |

| \$60 |                       |                      |           |              |             |              |            |         |         |

|      | (not used)            |                      | These i   | registers ar | e not assig | ned. (All "( | out when   | n read) |         |

| \$7F |                       |                      |           |              |             |              |            |         |         |

\_\_\_

#### **ELECTRICAL CHARACTERISTICS**

#### 1. Absolute Maximum Ratings

| Parameter             | Symbol | Rating                   | Unit         |

|-----------------------|--------|--------------------------|--------------|

| Power Supply Voltage  | VDD    | -0.5 ~ 7.0               | V            |

| Input Voltage         | VI     | $-0.5 \sim V_{DD} + 0.5$ | V            |

| Operating Temperature | Тор    | -20 ~ 75                 | $\mathbb{C}$ |

| Storage Temperature   | Tstg   | <i>-</i> 50 ∼ 125        | $\mathbb{C}$ |

#### 2. Recommended Operating Conditions

| Parameter             | Symbol | Min. | Тур. | Max. | Unit          |

|-----------------------|--------|------|------|------|---------------|

| Power Supply Voltage  | VDD    | 4.75 | 5.00 | 5.25 | V             |

| Operating Temperature | Top    | 0    | 25   | 70   | ${\mathbb C}$ |

#### 3. DC Characteristics (under recommended operating condition)

| Parameter                 | Symbol | Condition        | Min.    | Тур. | Max. | Unit    |

|---------------------------|--------|------------------|---------|------|------|---------|

| Power Consumption         | W      | $V_{DD} = 5.0V$  |         | 500  |      | mW      |

| Input Voltage H Level (1) | Vihi   | *1)              | 3.5     |      |      | V       |

| Input Voltage H Level (2) | VIH2   | *2)              | 2.0     |      |      | V       |

| Input Voltage L Level (1) | VILI   | *1)              |         |      | 1.0  | V       |

| Input Voltage L Level (2) | VIL2   | *2)              |         |      | 0.8  | V       |

| Output Voltage H Level    | Vон    | $IOH = 80 \mu A$ | VDD-1.0 |      |      | V       |

| Output Voltage L Level    | Vol    | IOL = 1.6mA      |         |      | 0.4  | V       |

| Input Leakage Current     | ILI    |                  | -10     |      | 10   | $\mu A$ |

| Pull-up Resistor          | Rp     |                  | 50      |      | 400  | kΩ      |

<sup>\*1)</sup> Applicable to XI and /IC terminals.

<sup>\*2)</sup> Applicable to input terminals except XI and /IC terminals.

#### EXTERNAL DIMENSIONS

モールドコーナー形状は、この図面と若干異なるタイプのものもあります カッコ内の寸法値は参考値とする モールド外形寸法はバリを含まない 単位(UNIT):mm

The shape of the molded corner may slightly different from the shape in this diagram.

The figure in the parenthesis ( ) should be used as a reference. Plastic body dimensions do not include burr of resin. UNIT: mm

Note: The LSIs for surface mount need especial consideration on storage and soldering condisions. For derailed information, please contact your nearest agent of yamaha.

#### IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANYTHIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

Note) The specifications of this product are subject to improvement changes without prior notice.

#

#### YAMAHA CORPORATION

Address inquiries to:

Semiconductor Sales & Marketing Department

■ Head Office 203, Matsunokijima, Toyooka-mura,

Iwata-gun, Shizuoka-ken, 438-0192

Tel. +81-539-62-4918 Fax. +81-539-62-5054

■ Tokyo Office 2-17-11, Takanawa, Minato-ku,

Tokyo, 108-8568

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

Osaka Office Namba Tsujimoto Nissei Bldg. 4F

1-13-17, Namba Naka, Naniwa-ku, Osaka City, Osaka, 556-0011

Tel. +81-6-6633-3690 Fax. +81-6-6633-3691

■ U.S.A. Office YAMAHA Systems Technology

100 Century Center Court, San Jose, CA 95112

Tel. +1-408-467-2300 Fax. +1-408-437-8791

1el. +1-408-46/-2300 Fax. +1-408-43/-8/9