#### CUSTOMER PROCUREMENT SPECIFICATION

# Z86227 40-PIN LOW-COST DIGITAL TELEVISION CONTROLLER (4LDTC)

#### **GENERAL DESCRIPTION**

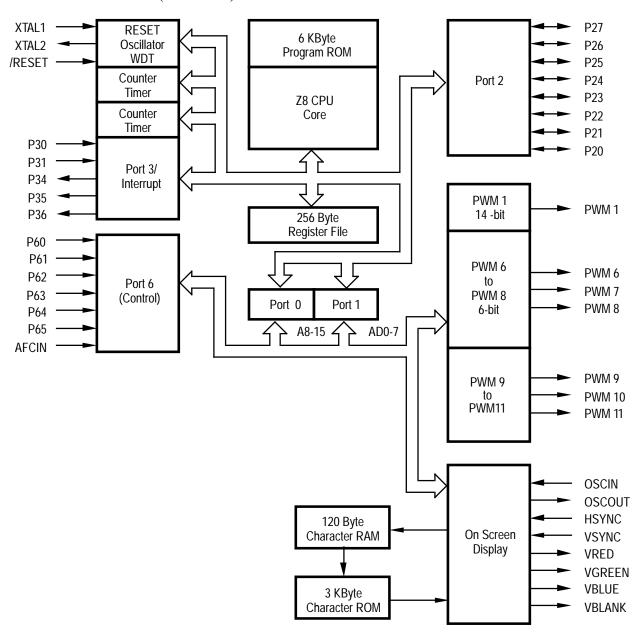

The Z86227 40-pin Low-Cost Digital Television Controller (4LDTC) introduces a new level of sophistication to single-chip architecture. The Z86227 is a member of the Z8® single-chip microcontroller family with 6 Kbytes of ROM and 236 bytes of RAM. The device is offered in a 40-pin package and is CMOS compatible. The 4LDTC offers mask programmed ROM which enables the Z8 microcontroller to be used in a high volume production application device embedded with a custom program (customer supplied program) and combines together with the Z86C27 (DTC) and Z86127 (LDTC) to provide support for high end, mid range and low end TV applications.

Zilog's 4LDTC offers fast execution, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, and easy hardware/software system expansion along with low cost and low power consumption. The device provides an ideal performance and reliability solution for consumer and industrial television applications.

The Z86227 architecture is characterized by utilizing Zilog's advanced Superintegration™ design methodology. The device has an 8-bit internal data path controlled by a Z8 microcontroller and On Screen Display (OSD) logic circuits and Pulse Width Modulators (PWM). On-chip peripherals include two register mapped I/O ports (Ports 2 and Port 3), interrupt control logic (one software, two external and three internal interrupts) and a standby mode recovery input port (Port 3, pin P30).

The OSD control circuits support 6 rows by 20 columns of characters. The character color is specified by row. One of the eight rows is assigned to show two kinds of colors for bar type displays such as volume control. The OSD is capable of displaying either low resolution (5x7 dot pattern) or high resolution (11x15 dot pattern) characters.

A 14-bit PWM port provides enough voltage resolution for a voltage synthesizer tuning system. Three 6-bit PWM ports are

used for controlling audio signal levels. Three 8-bit PWM ports used to vary picture levels.

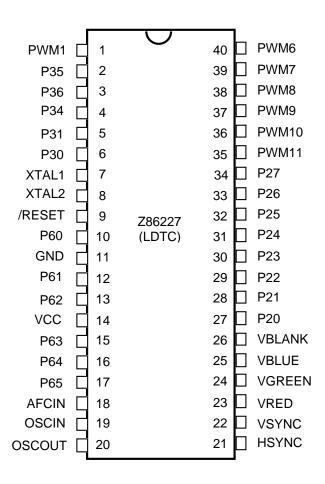

The 4LDTC applications demand powerful I/O capabilities. The Z86227 fulfills this with 24 pins dedicated to input or output. These lines are grouped into three ports, and are configurable under software control to provide timing, status signals, parallel I/O and an address/data bus for interfacing to external memory.

There are three basic address spaces available to support this wide range of configurations: Program Memory, Video RAM, and Register File. The Register File is composed of 236 bytes of general purpose registers, two I/O Port registers, 15 control and status registers and three reserved registers.

To unburden the program from coping with the real-time problems such as counting/timing and data communication, the 4LDTC offers two on-chip counter/timers with a large number of user selectable modes (Figure 1).

#### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device                     |  |

|------------|-----------------|----------------------------|--|

| Power      | V <sub>cc</sub> | $\mathbf{V}_{\mathrm{DD}}$ |  |

| Ground     | GND             | V <sub>SS</sub>            |  |

## **GENERAL DESCRIPTION** (Continued)

**Functional Block Diagram**

### **PIN CONFIGURATION**

40-Pin Mask-ROM Plastic DIP

#### **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol          | Parameters            | Min  | Max               | Units | Notes     |

|-----------------|-----------------------|------|-------------------|-------|-----------|

| V <sub>cc</sub> | Power Supply Voltage* | -0.3 | +7                | V     |           |

| $V_{I}^{cc}$    | Input Voltage         | -0.3 | $V_{cc} + 0.3$    | V     |           |

| V,              | Input Voltage         | -0.3 | $V_{cc}^{cc}+0.3$ | V     | [1]       |

| $V_{o}$         | Output Voltage        | -0.3 | $V_{cc}^{cc}+8.0$ | V     | [2,3]     |

| $I_{OH}$        | Output Current High   |      | -10               | mA    | 1 pin     |

| I <sub>OH</sub> | Output Current High   |      | -100              | mA    | All total |

| I <sub>OL</sub> | Output Current Low    |      | 20                | mA    | 1 pin     |

| Ţ               | Output Current Low    |      | 200               | mA    | All total |

| T <sub>OL</sub> | Operating Temperature | †    |                   |       |           |

| $T_{STG}^{A}$   | Storage Temperature   | -65  | +150              | C     |           |

#### Notes:

- [1] Port 2 open-drain

- [2] PWM open-drain outputs

- [3] PWM breakdown is 13.2V (normal operation). Will withstand 16V max. (non-momentary operating).

- \* Voltage on all pins with respect to GND.

- † See Ordering Information

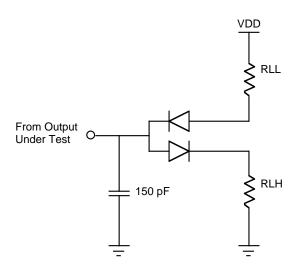

#### STANDARD TEST CONDITIONS

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (Test Load Diagram).

**Test Load Diagram**

## **CAPACITANCE**

$T_A = 25$  °C;  $V_{CC} = GND = 0V$ ; Freq=1.0 MHz; unmeasured pins to GND.

| Parameter                           | Max | Units |

|-------------------------------------|-----|-------|

| Input capacitance                   | 10  | pF    |

| Output capacitance                  | 20  | pF    |

| I/O capacitance                     | 25  | pF    |

| AFC <sub>IN</sub> input capacitance | 10  | pF    |

**DC CHARACTERISTICS**  $T_A$ =0°C to +70°C;  $V_{CC}$ =+4.5V to +5.5V;  $F_{OSC}$ =4 MHz

| Sym                                    | Parameter                      | T <sub>A</sub> =0°C<br>Min                    | to +70°C<br>Max                 | Typical<br>@ 25°C | Units | Conditions                                         |

|----------------------------------------|--------------------------------|-----------------------------------------------|---------------------------------|-------------------|-------|----------------------------------------------------|

| $V_{_{\rm IL}}$                        | Input Voltage Low              | 0                                             | 0.2 V <sub>cc</sub>             | 1.48              | V     |                                                    |

| $V_{_{\rm ILC}}^{^{12}}$               | Input XTAL/Osc In Low          |                                               | $0.07  \mathrm{V_{cc}}$         | 0.98              | V     | External Clock Generator Driven                    |

| $V_{_{\mathrm{IH}}}^{^{\mathrm{II}}}$  | Input Voltage XTAL/Osc In High | $0.7~\mathrm{V}_{\mathrm{cc}}$                | $V_{CC}$                        | 3.2               | V     | External Clock Generator Driven                    |

| V <sub>IHC</sub>                       | Input XTAL/Osc In High         | 0.8 V <sub>CC</sub>                           | V <sub>cc</sub>                 | 3.0               | V     | External Clock Generator Driven                    |

| V <sub>HV</sub>                        | Schmitt Hysteresis             | $0.1  \mathrm{V}_{\mathrm{cc}}^{\mathrm{cc}}$ |                                 | 0.8               | V     |                                                    |

| $V_{_{\mathrm{PU}}}^{^{\mathrm{III}}}$ | Maximum Pull-Up Voltage        |                                               | 12                              |                   | V     | [1]                                                |

| V <sub>OL</sub>                        | Output Voltage Low             |                                               | 0.4                             | 0.16              | V     | I <sub>oL</sub> =1.00 mA                           |

|                                        |                                |                                               | 0.4                             | 0.19              | V     | $I_{OL} = 0.75 \text{ mA} [1]$                     |

| V <sub>00-01</sub>                     | AFC Level 01 In                |                                               | 0.45 V <sub>CC</sub>            | 1.9               | V     |                                                    |

| V <sub>01-11</sub>                     | AFC Level 11 In                | $0.5~\mathrm{V}_{\mathrm{cc}}$                | $0.75~\mathrm{V}_{\mathrm{cc}}$ | 3.12              | V     |                                                    |

| $V_{OH}$                               | Output Voltage High            | $V_{\rm CC}$ $-0.4$                           |                                 | 4.75              | V     | $I_{OH} = -0.75 \text{ mA}$                        |

| I <sub>IR</sub>                        | Reset Input Current            |                                               | -80                             | -46               | μΑ    | V <sub>RL</sub> =0V                                |

| $I_{_{\rm IL}}$                        | Input Leakage                  | -3.0                                          | 3.0                             | 0.01              | μΑ    | $0\overline{\mathrm{V}}, \mathrm{V}_{\mathrm{CC}}$ |

| $I_{OL}$                               | Tri-State Leakage              | -3.0                                          | 3.0                             | 0.02              | μΑ    | $0V,V_{CC}$                                        |

| $I_{cc}$                               | Supply Current                 |                                               | 20                              | 13.2              | mA    | All inputs at rail                                 |

| $I_{CC1}$                              |                                |                                               | 6                               | 3.2               | mA    | All inputs at rail                                 |

| $I_{CC2}$                              |                                |                                               | 10                              | 2.0               | μΑ    | All inputs at rail                                 |

#### Note:

[1] PWM open-drain

## **AC CHARACTERISTICS**

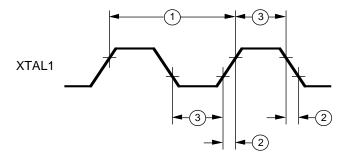

**Timing Diagrams**

**External Clock**

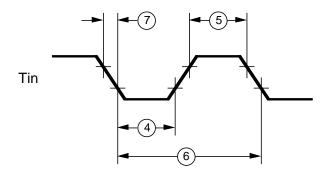

**Counter Timer**

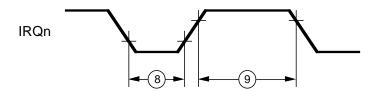

**Interrupt Request**

## **AC CHARACTERISTICS**

Timing Diagrams (Continued)

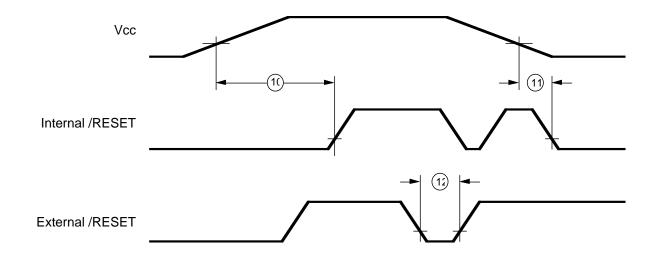

**Power-On Reset**

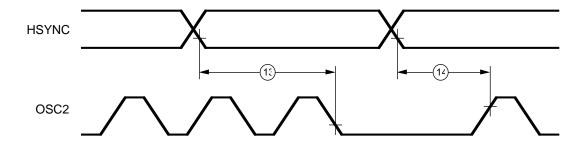

**On-Screen Display**

#### **AC CHARACTERISTICS**

$T_A = 0^{\circ} C \text{ to } +70^{\circ} C; V_{CC} = +4.5 \text{V to } +5.5 \text{V}; F_{OSC} = 4 \text{ MHz}$

| No | Symbol          | Parameter                                        | Min  | Max  | Unit |

|----|-----------------|--------------------------------------------------|------|------|------|

| 1  | ТрС             | Input Clock Period                               | 250  | 1000 | ns   |

| 2  | TrC,TfC         | Clock Input Rise and Fall                        |      | 15   | ns   |

| 3  | TwC             | Input Clock Width                                | 70   |      | ns   |

| 4  | TwTinL          | Timer Input Low Width                            | 70   |      | ns   |

| 5  | TwTinH          | Timer Input High Width                           | ЗТрС |      |      |

| 6  | TpTin           | Timer Input Period                               | 8TpC |      |      |

| 7  | TrTin,TfTin     | Timer Input Rise and Fall                        |      | 100  | ns   |

| 8a | TwIL            | Int Req Input Low                                | 70   |      | ns   |

| 8b | TwIL            |                                                  | ЗТрС |      |      |

| 9  | TwIH            | Int Request Input High                           | 3TpC |      |      |

| 10 | TdPOR           | Power On Reset Delay                             | 25   | 100  | ms   |

| 11 | <b>TdLVIRES</b> | Low Voltage Detect to                            | 200  |      | ns   |

|    |                 | Internal RESET Condition                         |      |      |      |

| 12 | TwRES           | Reset Minimum Width                              | 5TpC |      |      |

| 13 | TdHsOI          | $H_{\text{sync}}$ Start to $V_{\text{osc}}$ Stop | 2TpV | 3TpV |      |

| 14 | TdHsOh          | $H_{\text{sync}}$ End to $V_{\text{osc}}$ Start  | _    | 1TpV |      |

| 15 | TdWDT           | WDT Refresh Time                                 |      | 12   | ms   |

#### Note:

Refer to DC Characteristics for details on switching levels.

© 1993 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of merchantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 Telex 910-338-7621 FAX 408 370-8056