捷多邦,专业PCB打样工厂,24小时加急出货

## ZR36050

### ADVANCE INFORMATION

## JPEG IMAGE COMPRESSION PROCESSOR

### FEATURES

- Implements JPEG Baseline image compression and expansion, including:

- DCT/IDCT operations

- Quantization

- Variable length coding/decoding

- Full support of the JPEG Baseline standard, including:

- Bit and byte stuffing

- JPEG markers including restart (RST), application (APP), and comment (COM)

- JPEG Lossless compression and expansion

- DMA/SLAVE bus interface

- Motion video (30 frames/sec) compression/expansion capability for CCIR resolution (720 x 480)

- "Fast Preview" option

- Preview of "thumbnail" version of images (up to 25x faster)

- Bit rate control option

- Guarantees compressed image file size

- Low cost solution

- Low cost single chip

- Support for inexpensive memories

- Requires minimal host intervention

- TTL compatible

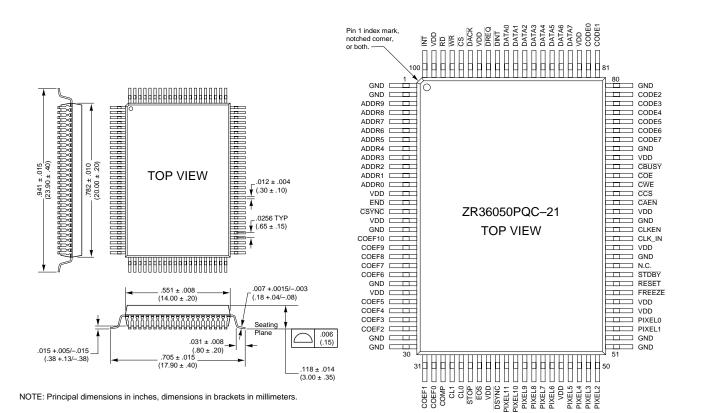

- 27 and 21 MSamples/sec data-rate

- Standby mode for very low power consumption

- 100-pin plastic quad flat-pack (PQFP) packaging

### **APPLICATIONS**

- Computer and multimedia add-in boards

- Full-motion video compression/expansion

- Digital still cameras and peripherals

- Security and industrial systems

- Videophones and color FAX machines

- Color printers and scanners

- Fixed bit rate image transmission devices

- Cost-sensitive image compression systems

### **GENERAL DESCRIPTION**

The ZR36050 is a high-speed JPEG Image Compression Processor that performs the algorithm specified by the JPEG Baseline and JPEG Lossless standards for high-quality image compression and expansion of continuous-tone color or monochrome images. The ZR36050 performs Discrete Cosine Transform (DCT), quantization and variable-length encoding for image compression (coding), and the corresponding inverse operations for expansion (decoding).

In the JPEG Baseline encoding operation, the ZR36050 performs the DCT operation on 8 x 8 blocks of image data, converting image data into its spatial frequency components, and quantizes them using a user defined "quantization table."

Because the human visual system is less sensitive at the higher spatial frequencies, these higher frequency components can be quantized more coarsely than the lower-frequency components, with negligible effect on image quality.

The coarser quantization of high-frequency coefficients results in long strings of zero valued quantized coefficients, when the 8x8 blocks are scanned in zigzag order. The scanned coefficients are characterized in terms of their nonzero values and the zero run lengths. As a result, a long string of zeroes is coded as a single number. The ZR36050 then performs Huffman coding using user defined Huffman tables, whereby bit patterns of different lengths code the nonzero values (values that occur frequently use the shortest codes; while those that infrequently occur use the longest codes). These techniques greatly reduce the amount of memory needed to store an image.

In the decoding operation, the compressed data is decoded (the inverse of the Huffman and the zigzag modified-run-length coding), and dequantized. A 2-D inverse Discrete Cosine Transform is performed on the DCT coefficients, resulting in an expanded image.

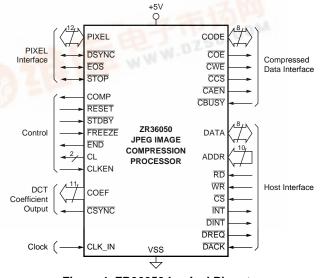

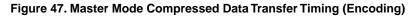

Figure 1. ZR36050 Logical Pinout

Z#RAN

In addition to the JPEG Baseline, the ZR36050 supports a subset of JPEG Lossless standard. The ZR36050 performs one dimensional differential prediction followed by variable-length encoding for JPEG Lossless compression, and the corresponding inverse operations for JPEG Lossless expansion.

The ZR36050 maintains full compatibility with the JPEG Baseline standard. The unique ability to perform bit rate control. Bit rate control capability allows the user to preset the size of a compressed image file. This capability is important because without bit rate control, the size of a compressed image is highly data dependent for a given set of quantization tables (images with fine detail generate considerably larger files than files generated from smooth images).

The ability to perform bit rate control is critical for applications where predictable file sizes for compressed images is desired, or where the time allocated to transmit an image across a communications network is fixed. The compressed image file size is constrained to be no greater than a user specified target, and is typically kept within a range of 95% to 100% of this target. The bit rate control feature relies on a two pass algorithm for its operation.

The ZR36050 has the ability to generate a "thumbnail" version of an image for "Fast Preview." This thumbnail image is a 1/64 scale version of the image, and is generated up to 25 times faster than full image expansion. The thumbnail image is generated from the JPEG Baseline compressed data, and eliminates the need for a separately encoded and stored thumbnail image. This feature is particularly useful for previewing large databases of images.

The ZR36050 operates as a dedicated processor requiring only minimal host intervention. The host processor controls the operation of the device by writing parameter values into the ZR36050's Internal Memory. Once initialized, the ZR36050 operates continuously until it has completed the compression or expansion of the image. Since the ZR36050 fully complies with the JPEG Baseline standard, the compressed data bit-stream generally requires no intervention by the host. Full JPEG capability also allows for the interchange of files created by other JPEG imaging systems with files generated by systems using the ZR36050.

The ZR36050 is useful for a wide range of motion and still video applications. For example, a typical multimedia application (30 seconds of video at 10 frames/sec and 320 x 240 resolution) would require 69 Mbytes of storage in uncompressed form. With compression using the ZR36050, the requirement can be reduced to 2.9 Mbytes, making storage feasible on a personal computer hard disk. Similarly, for digital still camera applications, the memory requirement can be reduced from a 22 Mbyte hard disk to a 1 Mbyte memory card for storage of twenty 768 x 480 compressed images.

The ZR36050 is fabricated with an advanced low-power CMOS technology, making it suitable for use in low-power, cost-sensitive applications. The device is available in a 100-pin Plastic Quad Flat Pack (PQFP).

## Table 1. Signal Description<sup>1, 2</sup>

|        | Ту     | pe <sup>3</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Encode | Decode          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VCC    | S      | S               | +5 volt Power supply. All VCC pins must be connected to +5V.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VSS    | S      | S               | Ground. All VSS pins must be connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

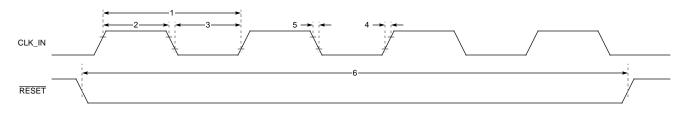

| CLK_IN | I      | I               | Data Transfer Clock. Provides data transfer timing for the device. All timing is referenced to the rising edge of this clock.                                                                                                                                                                                                                                                                                                                                                               |

| RESET  | I      | I               | Reset. This active-low input signal resets all the internal controls and places the ZR36050 in the Idle state. RESET can be activated only when CLKEN is asserted and must remain active for a minimum of four CLK_IN cycles.<br>The STATUS_0, INT_REQ_0, and INT_REQ_1 register bits are reset by this signal. The STATUS_1 bits except the END bit are reset; the END bit is set. RESET initializes the ZR36050 to the compression mode, and activates END, STOP and COMP.                |

|        |        |                 | RESET can be activated during the Standby state; in this case the device draws normal current as long as RESET is active.                                                                                                                                                                                                                                                                                                                                                                   |

| STDBY  | I      | I               | Standby. This active-low input signal places the ZR36050 in the Standby state. If CLKEN is active, only the internal clock circuit consumes power. If CLKEN is inactive in the Standby state, the device power consumption is further reduced.                                                                                                                                                                                                                                              |

|        |        |                 | The ZR36050 should be switched to the Standby state only when it is in the Idle state: after activation of a RESET and prior to loading the Internal Memory, or after the ZR36050 issues an END. If CLKEN is active, then STDBY should be deasserted at least four CLK_IN cycles before accessing the Internal Memory.                                                                                                                                                                      |

|        |        |                 | RESET can be activated during the Standby state, only when CLKEN is active. Reading from or writing to the Internal Memory during the Standby state is prohibited.                                                                                                                                                                                                                                                                                                                          |

| CLKEN  |        | 1               | Clock Enable. This active-high input signal enables the data transfer clock CLK_IN, and the internal PLL that generates an internal double-frequency clock. When inactive, this signal reduces power further in the Standby state by deactivating the internal clock. The frequency of CLK_IN must be stable before CLKEN is activated. Furthermore, 5000 CLK_IN cycles are required for the PLL to stabilize, after CLKEN has been activated and before the device is ready for operation. |

|        |        |                 | If the frequency of CLK_IN is changed without turning off the power, then CLKEN must be reactivated. When STDBY is high, this pin should also be high. For systems in which the 5000 CLK_IN recovery time is not significant, the STDBY and CLKEN pins can be tied together to the external standby signal.                                                                                                                                                                                 |

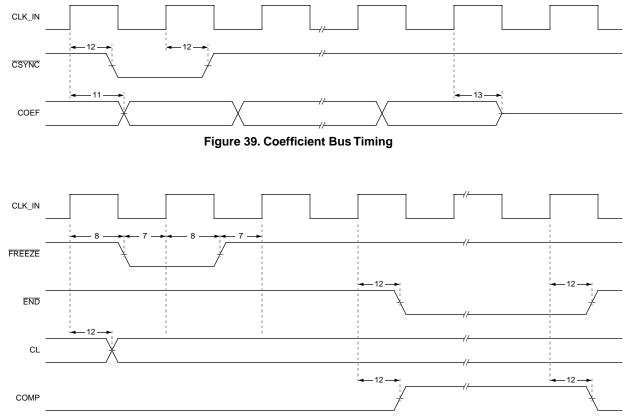

| FREEZE | I      | I               | Freeze. This active-low input signal freezes all chip operations. FREEZE is sampled on the rising edge of CLK_IN. Immediately after FREEZE is sampled, all buses float and all activities of the ZR36050 are frozen in their current state. All activities resume normally following the deassertion of FREEZE.                                                                                                                                                                             |

| END    | 0      | 0               | End Of Process. This active-low output signal indicates the normal end of an encoding or decoding process. If an encoding process ends because of an overflow, END is not activated.                                                                                                                                                                                                                                                                                                        |

|        |        |                 | <b>END</b> is activated after activation of <b>RESET</b> and at the completion of an encoding or decoding process. It stays activated until a GO command is issued or the STATUS_1 register in the Internal Memory is read.                                                                                                                                                                                                                                                                 |

1. The DATA, CODE, PIXEL, and COEF buses have internal pull-downs that provide 50 microamps of pull-down current at 0.4 volts.

The control pins: DSYNC, EOS, STOP, END, CL, CSYNC, COE, CWE, CCS, CAEN, INT, DINT, DREQ and COMP, have internal pull-up devices that provide 50 microamps at 2.4 volts. These pull-ups are turned on only when STDBY is active but RESET is inactive. When STDBY is active together with RESET, the above control pins float.

## Table 1. Signal Description<sup>1, 2</sup> (Continued)

|             | Ту     | pe <sup>3</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal      | Encode | Decode          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CL(1-0)     | -      | 0               | Color. During the decoding mode, the CL output signals designate the index of the color component that is being decoded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |        |                 | 00 - First MCU component.<br>01 - Second MCU component.<br>10 - Third MCU component.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |        |                 | <ul> <li>11 - Fourth MCU component or Idle.</li> <li>In the JPEG Baseline mode, the designation changes with the falling edge of the first DSYNC of the component or with the falling edge of EOS.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                     |

|             |        |                 | In the Fast Preview and Lossless decoding modes, CL is active together with the DSYNC which precedes the DC coefficient value and the pixel data, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |        |                 | CL is undefined in the encoding mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

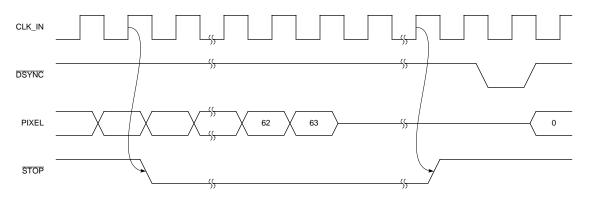

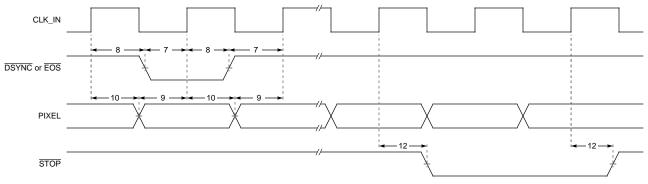

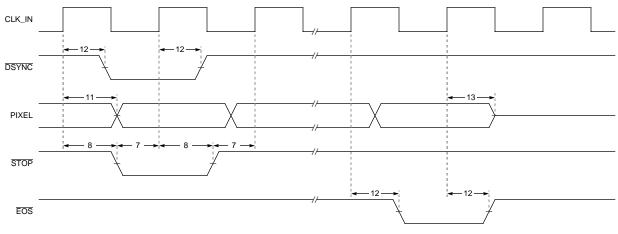

| STOP        | 0      | 1               | Stop Sending/Receiving. This active-low bidirectional signal is an input in encoding and output in decoding modes. STOP is used for the following purposes:                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |        |                 | At the start of and during an encoding operation, STOP is an output signal indicating that the ZR36050 is not ready to receive image data. STOP is activated when the ZR36050 is in the Idle state, and when reading or processing Internal Memory parameters during the encoding modes.                                                                                                                                                                                                                                                                                                          |

|             |        |                 | In the encoding mode, STOP is an output signal indicating that three of the ZR36050's four internal coefficient buffers are full. In this case, STOP is output 42 CLK_IN cycles prior to the last image data sample of the current block that is being input. If STOP remains active until the next DSYNC is due, then the system must not input the next DSYNC and the image data block. STOPs that are deactivated prior to the next DSYNC can be ignored. The system can resume inputting the next image data block immediately after STOP is deactivated.                                     |

|             |        |                 | In the Lossless encoding mode, the system must stop inputting data within three CLK_IN cycles of activation of STOP to prevent overflow.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |        |                 | In the decoding mode, STOP is an input signal that notifies the ZR36050 that it should not assert the next DSYNC and consequently delay output of the next decoded image data block at the end of the current block. In this case, STOP must be activated at least 24 CLK_IN cycles before the last image sample of the current block that is being output and must remain active at least until the end of the current block. Once STOP is deactivated, the ZR36050 outputs the next DSYNC followed by its corresponding image data block, at least 17 CLK_IN cycles after deactivation of STOP. |

|             |        |                 | In the Lossless decoding and Fast Preview modes, when STOP is activated or deactivated, the ZR36050 stops or resumes delivering image data after 2 CLK_IN cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

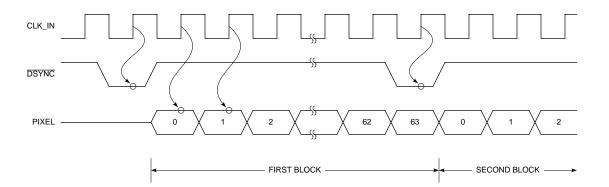

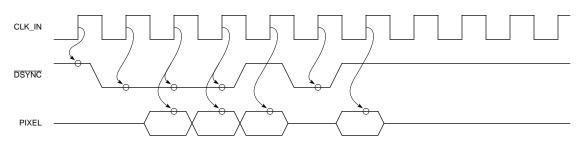

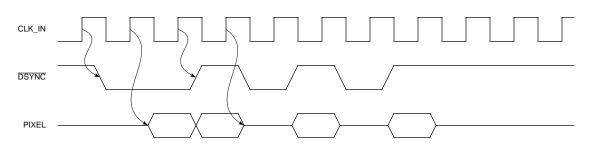

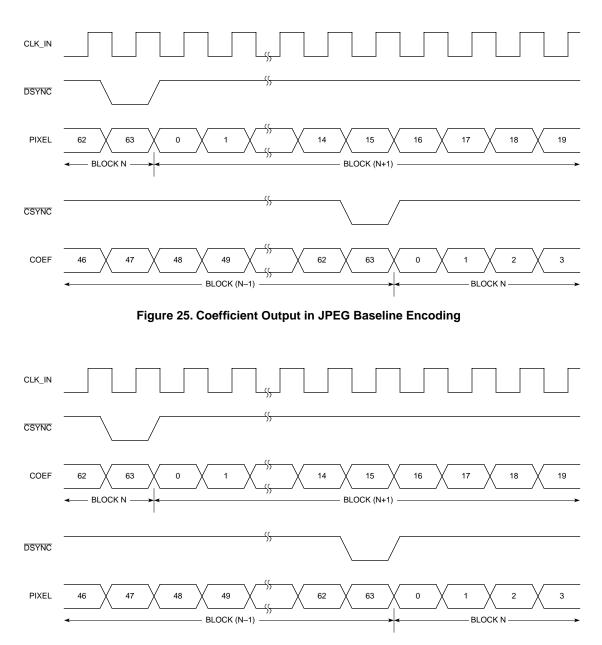

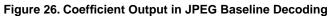

| PIXEL(11-0) | I      | 0               | Pixel bus. This 12-bit unsigned bidirectional bus is used for the following purposes:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |        |                 | In the encoding modes, the most significant 8 bits are used to carry the input image data. The remain-<br>ing 4 bits are "don't care" and can be left as unconnected pins.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |        |                 | In the Lossless encoding mode, it is a 12-bit input bus. If fewer than 12 bits are required, then the most significant bits of the bus are used to carry the input image data.                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |        |                 | In the decoding mode, the most significant 8 bits are used to carry the output image data. The least significant 4 bits are forced to "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |        |                 | In the Lossless decoding mode, this is a 12-bit output bus. If fewer than 12 bits are used, then the most significant bits of the bus are used to carry the output image data and the unused bits are forced to "0".                                                                                                                                                                                                                                                                                                                                                                              |

|             |        |                 | In the Fast Preview mode, it is an output bus carrying the 11-bit unsigned DC coefficient values on the most significant 11 bits of the bus. The least significant bit is forced to "0".                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |        |                 | The input/output data in the encoding and decoding modes is ordered in row-by-row scanned 8x8 blocks. In the Lossless encoding and decoding modes, the image data is scanned row by row.                                                                                                                                                                                                                                                                                                                                                                                                          |

1. The DATA, CODE, PIXEL, and COEF buses have internal pull-downs that provide 50 microamps of pull-down current at 0.4 volts.

The DATA, CODE, TAEE, and COLE bases have internal purchavits that provide so introlarings of purchavit current at 0.4 volts.

The control pins: DSYNC, EOS, STOP, END, CL, CSYNC, COE, CWE, CCS, CAEN, INT, DINT, DREQ and COMP, have internal pull-up devices that provide 50 microamps at 2.4 volts. These pull-ups are turned on only when STDBY is active but RESET is inactive. When STDBY is active together with RESET, the above control pins float.

## Table 1. Signal Description<sup>1, 2</sup> (Continued)

| Type <sup>3</sup> Signal         Encode |        | pe <sup>3</sup> |                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal                                  | Encode | Decode          | Description                                                                                                                                                                                                                                                                                                                                                                                      |

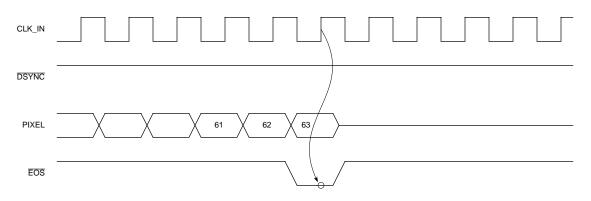

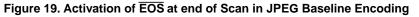

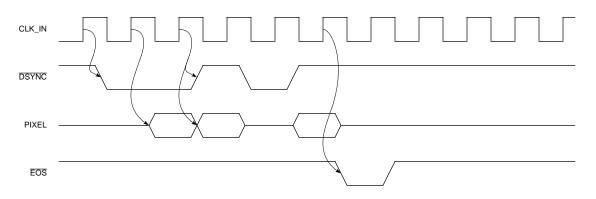

| DSYNC                                   | I      | 0               | Data Synchronization. This active- low signal is an input in encoding and output in decoding modes.                                                                                                                                                                                                                                                                                              |

|                                         |        |                 | In the encoding modes, DSYNC marks the start of an 8x8 image data block and should appear as an input one CLK_IN before the first image data of a block. In the decoding modes, DSYNC is output one CLK_IN before the first image data sample of a block. The width of DSYNC is one CLK_IN cycle.                                                                                                |

|                                         |        |                 | In the Fast Preview mode, and the Lossless encoding and decoding modes, this signal precedes each image data sample.                                                                                                                                                                                                                                                                             |

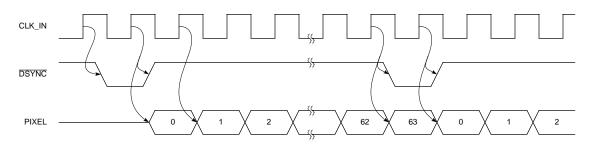

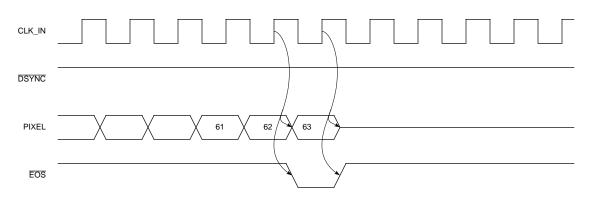

| EOS                                     | 1      | 0               | End Of Scan. This active-low signal is an input in encoding modes. EOS indicates the last image data sample of each scan entering the ZR36050. In encoding modes, EOS must be input regardless of the STOP signal.                                                                                                                                                                               |

|                                         |        |                 | $\overline{\text{EOS}}$ is an output signal in the decoding mode. It is generated together with the last image data sample of each scan leaving the ZR36050. In this case, $\overline{\text{DSYNC}}$ will not be issued.                                                                                                                                                                         |

|                                         |        |                 | In the Fast Preview and Lossless decoding modes, EOS is output within 64 CLK_IN cycles after the last sample of a scan. It is merely used in as an indication of the completion of the current process without having any timing significance.                                                                                                                                                   |

|                                         |        |                 | In decoding mode, EOS is output regardless of the STOP signal.                                                                                                                                                                                                                                                                                                                                   |

|                                         |        |                 | The width of EOS is one CLK_IN cycle.                                                                                                                                                                                                                                                                                                                                                            |

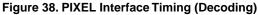

| COEF(10-0)                              | 0      | 0               | Coefficient Bus. This 11-bit output bus is used to transfer DCT coefficients out of the device in the encoding and decoding modes. The DCT coefficients are output in column-major order. This bus is not used in the Fast Preview and Lossless encoding and decoding modes.                                                                                                                     |

| CSYNC                                   | 0      | 0               | Coefficient Synchronization. This active-low signal indicates the beginning of an 8x8 DCT coefficient block.                                                                                                                                                                                                                                                                                     |

|                                         |        |                 | In the encoding and decoding modes, this signal is generated by the ZR36050. It is asserted one CLK_IN cycle before the first coefficient of a block is placed on the COEF bus by the ZR36050. The width of CSYNC is one CLK_IN cycle.                                                                                                                                                           |

|                                         |        |                 | CSYNC is not used in the Fast Preview and Lossless encoding and decoding modes.                                                                                                                                                                                                                                                                                                                  |

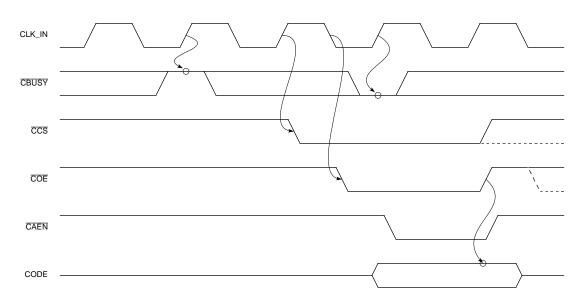

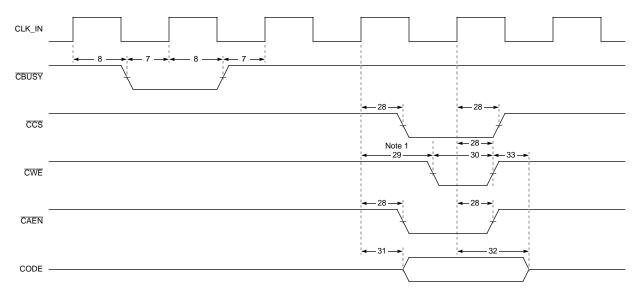

| CODE(7-0)                               | 0      | I               | Code. In Master mode Compressed Data Transfer, this 8-bit bidirectional bus is used to read the com-<br>pressed data from or write to the Compressed Data Memory.                                                                                                                                                                                                                                |

|                                         |        |                 | In the 16-bit Slave and DMA modes, this bus is used as an extension of the DATA bus.                                                                                                                                                                                                                                                                                                             |

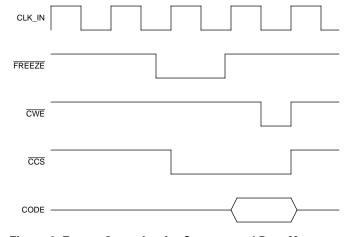

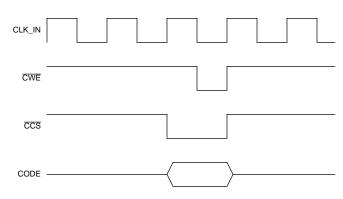

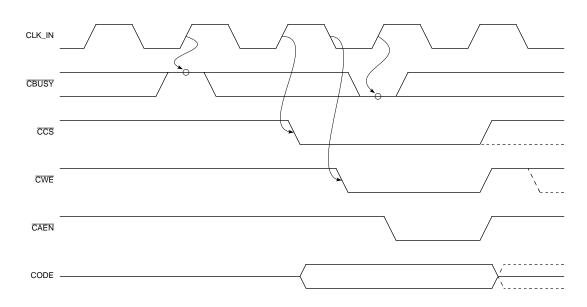

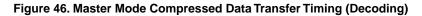

| COE                                     | -      | 0               | Compressed Data Memory Read. This active-low output signal acts as a read pulse from the ZR36050 to the Compressed Data Memory. $\overline{\text{COE}}$ goes active 0.5 CLK_IN cycles after the start of a read cycle and remains active until the end of the read cycle. The CODE bus is latched on the rising edge of $\overline{\text{COE}}$ .                                                |

| CWE                                     | 0      | -               | Compressed Data Memory Write. This active-low output signal acts as a write pulse from the ZR36050 to the Compressed Data Memory. <u>CWE</u> goes active 0.5 CLK_IN cycles after the start of a write cycle and remains active until the end of the write cycle.                                                                                                                                 |

| CCS                                     | 0      | 0               | Compressed Data Memory Chip Select. This active-low output signal acts as a chip select signal from the ZR36050 to the Compressed Data Memory. CCS goes active at the start of a read or write cycle and remains active throughout the cycle. CCS remains active continuously in back to back read or write cycles. The length of a read or write cycle can be from one to eight CLK_IN periods. |

| CAEN                                    | 0      | 0               | Address Counter Enable. This active-low output signal can be used to advance an external Com-<br>pressed Data Memory address counter.                                                                                                                                                                                                                                                            |

1. The DATA, CODE, PIXEL, and COEF buses have internal pull-downs that provide 50 microamps of pull-down current at 0.4 volts.

The control pins: DSYNC, EOS, STOP, END, CL, CSYNC, COE, CWE, CCS, CAEN, INT, DINT, DREQ and COMP, have internal pull-up devices that provide 50 microamps at 2.4 volts. These pull-ups are turned on only when STDBY is active but RESET is inactive. When STDBY is active together with RESET, the above control pins float.

Table 1. Signal Description<sup>1, 2</sup> (Continued)

|           | Туј    | pe <sup>3</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal    | Encode | Decode          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CBUSY     | I      | I               | Compressed Data Memory Busy. This active-low input signal indicates that the Compressed Data Memory is busy. During the encoding modes, CBUSY active means that the ZR36050 cannot write to the Compressed Data Memory. During the decoding modes, CBUSY active means that the ZR36050 cannot read from the Compressed Data Memory.<br>If CBUSY is activated at least one CLK_IN prior to the beginning of a read or write cycle, then the next read or write cycle will not be performed. The minimum width of CBUSY is one CLK_IN cycle. |

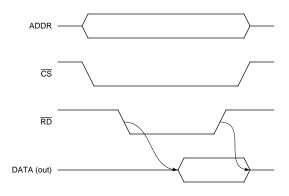

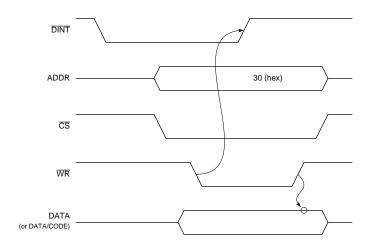

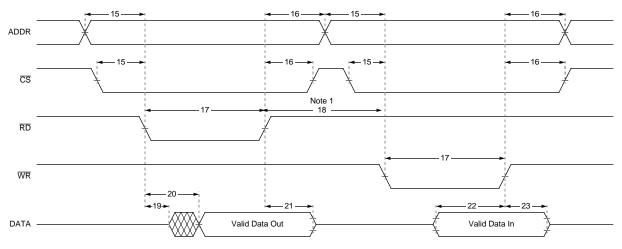

| ADDR(9-0) | I      | I               | Internal Memory Address. This 10-bit input bus is used to address the Internal Memory of the ZR36050.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

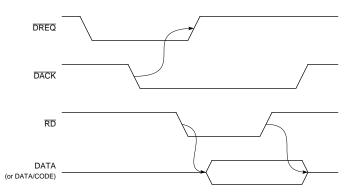

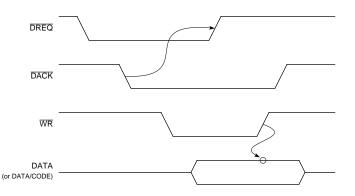

| DATA(7-0) | В      | В               | Internal Memory Data Bus. This 8-bit bidirectional bus is used to read from or write to the Internal Memory of the ZR36050. In the 16-bit Slave and DMA modes, the CODE bus is used as an extension of the DATA bus.                                                                                                                                                                                                                                                                                                                       |

| RD        | I      | I               | Read. This active-low input signal acts as a read pulse from the host to the ZR36050.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

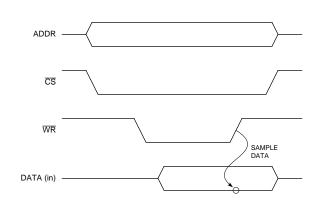

| WR        | I      | I               | Write. This active-low input signal acts as a write pulse from the host to the ZR36050. The DATA bus is latched on the rising edge of $\overline{WR}$ .                                                                                                                                                                                                                                                                                                                                                                                    |

| CS        | I      | I               | Chip Select. This active-low input signal acts as a chip select signal from the host to the ZR36050.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

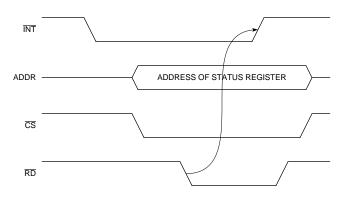

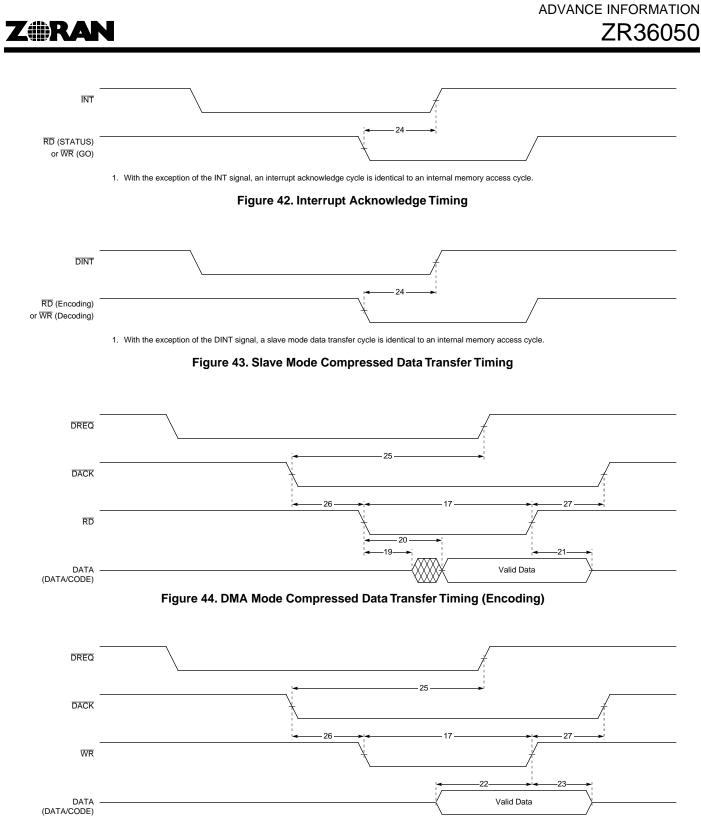

| ĪNT       | 0      | 0               | Interrupt. This active-low output signal notifies the host that one of the STATUS bits, except for DATRDY, is set. INT is reset by reading the relevant STATUS register, by activation of RESET, or by a GO command.                                                                                                                                                                                                                                                                                                                       |

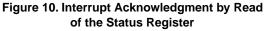

| DINT      | 0      | 0               | Data Ready Interrupt. In Slave mode Compressed Data Transfer, this active-low output signal notifies the host that the DATRDY bit in the STATUS_1 register is set. DINT is reset by reading the STATUS_1 register, by activation of RESET, or by reading or writing the compressed data in the Compressed Data Input/Output register at address 30H of the ZR36050 Internal Memory with $\overline{CS}$ active.                                                                                                                            |

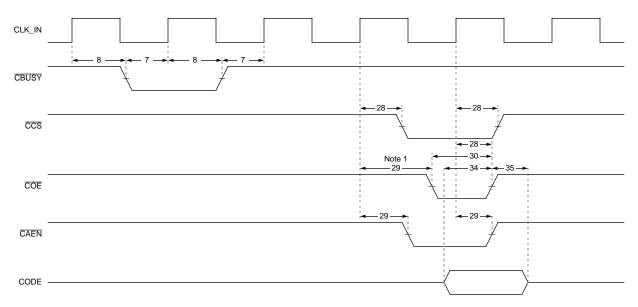

| DACK      | I      | I               | DMA Acknowledge. This active-low input signal is used in DMA mode Compressed Data Transfer.<br>DACK is an acknowledgment pulse from the DMA controller to the ZR36050. It must be active during the entire Read or Write cycle.                                                                                                                                                                                                                                                                                                            |

| DREQ      | 0      | 0               | DMA Request. This active-low output signal is used in DMA mode Compressed Data Transfer. DREQ is the DMA request from the ZR36050 to the host. The ZR36050 does not output a DREQ until the DACK signal to the previous DREQ has been deactivated.DREQ is deactivated by RESET, or by DACK.                                                                                                                                                                                                                                                |

| COMP      | 0      | 0               | Compress/Expand. This output signal provides an indication of the current operating mode of the ZR36050. When it is high, the ZR36050 is in the encoding mode; when it is low, the ZR36050 is in the decoding mode. The mode and the state of COMP are changed when the MODE register in the Internal Memory is read by the ZR36050 after a GO command is issued by the host. One CLK_IN cycle after COMP changes state, EOS, STOP, and DSYNC change directions. Activation of RESET sets COMP high.                                       |

1. The DATA, CODE, PIXEL, and COEF buses have internal pull-downs that provide 50 microamps of pull-down current at 0.4 volts.

2. The control pins: DSYNC, EOS, STOP, END, CL, CSYNC, COE, CWE, CCS, CAEN, INT, DINT, DREQ and COMP, have internal pull-up devices that provide 50 microamps at 2.4 volts. These pull-ups are turned on only when STDBY is active but RESET is inactive. When STDBY is active together with RESET, the above control pins float.

# Z RAN

### FUNCTIONAL OVERVIEW

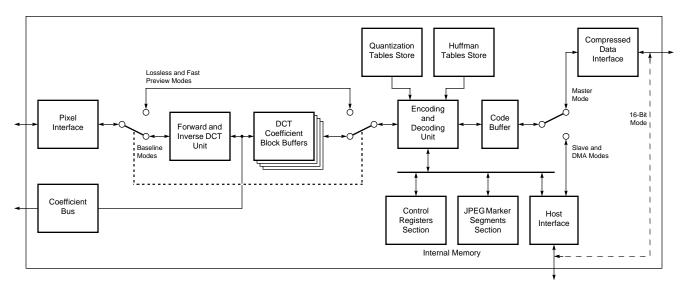

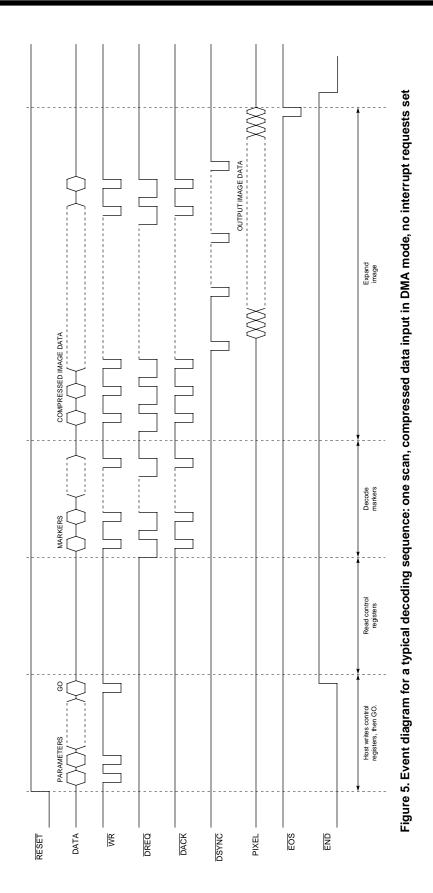

Figure 2 is a functional block diagram of the ZR36050 JPEG Image Compression Processor. The ZR36050 consists of two major processing units, the DCT Unit and the Encoding/Decoding Unit, with their associated buffers, an Internal Memory for data exchange with the host processor, special internal storage for tables, and three bus interfaces.

During a compression operation, image data flows in through the Pixel Interface and compressed data flows out through either the Compressed Data Interface or the Host Interface. The direction of data flow is reversed during an expansion operation.

### **Pixel Interface**

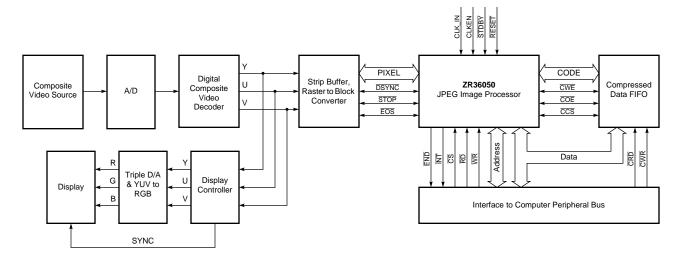

In compression of an image, the source of the image data samples is typically a strip, field, or frame buffer (see Figure 3, for example). The external image buffer control logic writes the image samples into the ZR36050 via the Pixel Interface, which operates synchronously, transferring each sample in on the rising edge of the clock. A synchronizing signal, driven by the buffer control logic, indicates to the Pixel Interface when valid samples are being presented to it.

In JPEG Baseline compression, each color component of the image must be partitioned into blocks of 8 x 8 samples. The image data enters the Pixel Interface one component block at a time, each block starting with the top left sample, scanned by rows, and ending with the bottom right sample. As required by the JPEG Baseline standard, the blocks are grouped into a repeating pattern of Minimum Coded Units, or MCU's. For example, in an interleaved scan of Y, U, and V components, with 4:2:2 subsampling, the MCU consists of two blocks of Y, one block of U, one block of V, and image blocks enter the device in the following order:

ADVANCE INFORMATION

where each component designator (Y, U or V) represents a block of 64 samples, and the subscript indicates the block index.

On the other hand, in JPEG Lossless compression, the image components enter the Pixel Interface in a normal raster. In the above example, the MCU then consists of two Y samples, one U sample and one V sample.

When outputting expanded image data, the Pixel Interface drives the synchronizing signal and the pixel data bus.

### **DCT Unit and Coefficient Buffers**

In JPEG Baseline compression, the DCT Unit transforms each component block into 64 DCT coefficients, and writes the coefficients into the next available DCT Coefficient Block Buffer. At the same time, it outputs the DCT coefficients on the Coefficient Bus. In expansion, it performs the inverse DCT, whenever a complete block of DCT coefficients is available in the buffer.

Because JPEG Lossless compression uses a spatial domain algorithm, when the ZR36050 operates in Lossless mode, the DCT Unit and Coefficient Block Buffers are bypassed. There is also a Fast Preview mode (described later) for expansion of JPEG Baseline compressed data, in which the Inverse DCT Unit and Coefficient Buffers are also bypassed.

### **Encoding/Decoding Unit, Code Buffer**

The Encoding/Decoding Unit performs the remainder of the JPEG compression and also formats the compressed data — including the insertion of JPEG bit and byte stuffing, JPEG markers, marker segments and their associated parameters. The compressed data conforms completely to the JPEG format and no reformatting or additional parameter insertion is needed.

$Y_0 Y_1 U_0 V_0 Y_2 Y_3 U_1 V_1 Y_4 Y_5 U_2 V_2 \dots$

Figure 2. ZR36050 Functional Block Diagram

In JPEG Baseline compression, the Encoding Unit reads the DCT coefficients from the Block Buffers in the JPEG zig-zag sequence and quantizes them using the tables in the Quantization Table Store. The Quantization Table Store holds up to four quantization tables. Each component of the image is assigned one of the quantization tables; this assignment is specified in the JPEG frame header.

The Encoding Unit encodes the difference of the quantized DC coefficients of the current and previous blocks, using one of the DC tables in the Huffman Table Store. After accumulating runs of zero-valued AC coefficients, it encodes the zero run lengths and the non-zero AC coefficients using the AC tables in the Huffman Table Store. The Huffman Table Store has space for two DC Huffman tables and two AC Huffman tables. Each component of a scan is assigned to one DC table and one AC table; this assignment is specified in the JPEG scan header.

Quantization tables are not used in Lossless compression. In this mode of operation, the Encoding Unit performs one-dimensional, horizontal predictive coding and Huffman coding of the samples, similar to that of the DC coefficients in Baseline compression.

When it has generated a Huffman code, or when it is transferring the marker segment data, the Encoding Unit writes the compressed data into the Code Buffer. From there, the compressed data is transferred out of the device, either via the Compressed Data Interface, or via the Host Interface.

The procedure for JPEG Baseline or Lossless image expansion is the inverse of the corresponding compression procedure When expanding an image, the Encoding/Decoding Unit detects and decodes all the markers and marker segment parameters included in the compressed data. The host does not need to extract or decode parameters, such as tables, from the JPEG compressed data file, since this is done automatically.

### **Compressed Data Interface**

The Compressed Data Interface is the fastest means of transferring the compressed data into or out of the ZR36050, therefore it could be used in a motion video compression application, (Refer to the example shown in Figure 3). Since it can optionally be configured to operate with up to seven internally generated wait states, it is also suitable for use with a slow compressed data store, such as a memory card. When the Compressed Data Interface is being used, it transfers data in a Master mode, driving the access control signals to an external auto-incrementing (e.g. FIFO) memory device.

### Host Interface

If the ZR36050 is configured to transfer the compressed data via the Host Interface, it can do so in one of two submodes. Slave or DMA modes. The principal function of the Host Interface is to allow the host to access the Internal Memory. This access is required in order to program the operating mode of the device, specify the JPEG marker segments and their parameters for compression, initiate the encoding or decoding operation and read the status of the device.

### **Internal Memory**

The Internal Memory is partitioned into a Control Registers Section and a JPEG Marker Segments Section.

The Control Registers Section contains the various configuration registers, status registers for interaction with the host, and informational registers that provide feedback to the host after the completion of an operation by the ZR36050.

The Marker Segments Section is where the host writes the contents of the JPEG marker segments before initiating compression of an image or changing markers between the frame and scan marker, or between scans. After an expansion, it

contains the marker segments that the Encoding/Decoding Unit extracted from the compressed data.

The Internal Memory space also contains a write-only virtual register (at address 0) by means of which the host issues the GO

# of which the host issues the GO

### **PROGRAMMING THE ZR36050**

The host configures the processing units and interfaces of the ZR36050 for the desired operation by means of the Control Registers and Marker Segments sections of the Internal Memory.

Many of the parameters that determine the proper operating configuration of a JPEG encoder or decoder are embedded in the marker segments that are included with JPEG compressed image data. For example, the JPEG frame header specifies the number of data units (blocks or samples) of each image component in the MCU, and the scan header specifies the number of image components in the scan. This information is essential for the Encoding/Decoding Unit to perform the quantization and Huffman coding correctly. The ZR36050 decodes these parameters automatically from marker segments in JPEG format. In compression, these marker segments must be written in the Marker Segments Section of Internal Memory by the host, before it initiates the compression. In expansion, the marker segments are part of the compressed data; the Encoding/Decoding Unit copies them from the Code Buffer into Internal Memory before decoding the parameters.

The basic operating mode and interface configuration are specified in the MODE and HARDWARE control registers. For an image expansion operation, these and the INT\_REQ registers are the only ones that need to be initialized. Other control registers, such as the OPTIONS and MARKERS\_EN registers, are used only in compression operation or Table Preload modes.

command to start operation. In Slave mode Compressed Data

Transfer, the host reads the compressed data from or writes it into, a Compressed Data Input/Output register. That is also

In addition to the frame (SOFn) and scan (SOSn) header marker segments, the Internal Memory has space allocated for the Define Restart Interval (DRI), Define Number of Lines (DNL), Define Quantization Tables (DQT), Define Huffman Tables (DHT), Application (APP) and Comment (COM) marker segments, which can optionally be included with the compressed image data in compression. The MARKERS\_EN register provides the means by which the host can specify which of the optional marker segments are to be included in the compressed data.

For further details on programming, refer to the section "INTER-NAL MEMORY FORMAT."

### STATUS AND INTERRUPTS

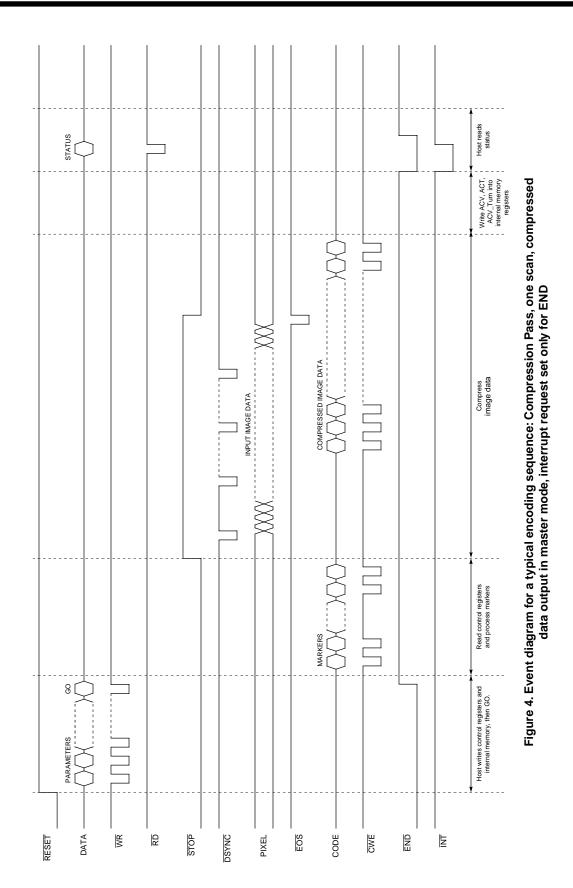

The ZR36050 has two status registers, that are readable by the host and provide feedback on the various events occurring during an encoding or decoding operation. Associated with the status registers are two interrupt enable registers, the bits of which correspond to those of the status registers. If the host sets an interrupt enable bit, the ZR36050 will interrupt it when the corresponding status bit becomes active and stops processing. The host can then take appropriate action before commanding the ZR36050 to continue processing (by means of the GO command).

The STATUS\_0 and INT\_REQ\_0 register bits correspond to the names of JPEG marker segments. In a decoding operation, the ZR36050 sets a STATUS\_0 bit when the corresponding marker segment has been extracted from the compressed data stream and written in the Internal Memory. If the INT\_REQ\_0 bit was also set, the host can read out the marker segment content before continuing.

The APP and COM bits of STATUS\_0 have a special mechanism associated with them, that makes it possible for the host to read out a segment of any length, even though there are only 64 bytes allocated to each of the APP and COM segments in Internal Memory. If the corresponding interrupt is enabled, and the segment is longer than 64 bytes, the ZR36050 stops after writing each 64 byte portion in Internal Memory, and waits for a GO command. The last portion may have fewer than 64 bytes.

The APP and COM bits of STATUS\_0 are also used, with a similar mechanism, to include APP or COM segments longer than 64 bytes in the compressed data. In this case, the host programs the APP or COM bit of the MARKERS\_EN register, writes the first 64 byte portion of the segment in the Internal Memory, and enables the interrupt in the INT\_REQ\_0 register. When the ZR36050 has transferred the portion to the Code Buffer, it stops as before, if the length parameter indicated a segment longer than 64 bytes. The host can then write the next 64 byte portion in the Internal Memory, and repeat the procedure until the whole segment is transferred. The ZR36050 does not stop after transferring the last portion of 64 or fewer bytes.

The STATUS\_1 and INT\_REQ\_1 register bits indicate miscellaneous conditions: readiness for data or new optional marker segments, end of process, and overflow conditions. A special bit in STATUS\_1, consisting of the logical OR of all the bits of STATUS\_0, permits the host to determine the type of event that caused an interrupt, by reading only the STATUS\_1 register.

ADVANCE INFORMATION

## CODE VOLUME CONTROL

The JPEG Baseline encoding algorithm does not inherently provide a means of achieving a target code volume for a compressed image (or an equivalent target average coding rate in bits per pixel, or target compression ratio). In fact, since the standard specifies that the whole image frame is encoded using the same set of quantization tables and Huffman coding tables, it provides no built-in mechanism to modify the coding rate once encoding of an image has started.

One way to achieve a target code volume in compression of a particular image is to iterate the compression, using different quantization tables each time, until the desired target is achieved. The Scale Factor (SF register in the Internal Memory) allows the host to modify the quantization tables by changing a single parameter. In operation, the ZR36050 multiples the quantization tables, specified in the DQT segment of Internal Memory, by the Scale Factor before storing them in the Quantization Tables Store.

When it is activated with appropriate values of the Scale Factor and an Allocation Factor (AF register), the unique Bit Rate Control feature of the ZR36050 ensures that the actual code volume achieved is equal to or slightly less than the target code volume. Moreover, if the Scale Factor is close enough to the correct value, the Bit Rate Control operates without affecting the compressed image quality. The ZR36050 has a Statistical Pass mode of operation, in which it performs a preliminary pass over the image data, and determines appropriate values of the Scale Factor and Allocation Factor for use in a Compression Pass with Bit Rate Control. The host specifies the target code volume to be used in the computation of the Scale Factor and Allocation Factor, in the TCV\_DATA register. There is also a mode of operation in which the ZR36050 performs a Statistical Pass followed automatically by a Compression Pass with Bit Rate Control. For more details on these modes of operation, see the "ENCODING MODES" section.

The code volume overflow detection option (activated by the OVF bit of the OPTIONS register) is useful if Bit Rate Control is not used, or if the Scale Factor and Allocation Factor contain inappropriate values. With this option selected, the ZR36050 continuously compares the accumulated code volume with a target limit specified in the TCV\_NET register. If the code volume exceeds the limit at any time during a compression pass, the TCVOVF status register bit is set, and the interrupt pin is activated to notify the host. Since this is considered a destructive event, the ZR36050 aborts the compression pass and goes Idle.

## **COMPRESSED DATA FORMAT**

The ZR36050 supports encoding and decoding of all three compressed data format classes defined by the JPEG standard:

- The full interchange format, in which the specifications of all the tables used for encoding the image are included with the compressed image data, in their marker segments. This format is used when the compressed image must be decoded by a JPEG decoder that has no knowledge of the tables used.

- The abbreviated format for compressed data. This format contains the compressed image data and the frame and scan headers, but where some or all of the tables are omitted.

- The abbreviated tables-only format. This format contains marker segments with table specifications but no compressed image data.

The two abbreviated formats complement each other in applications based on the ZR36050. For example, when a sequence of image frames, such as a video clip, are compressed, the same Huffman tables are used for all the images in the sequence. If the compressed sequence is to be sent to a JPEG decoder that has no prior knowledge of the tables, it is most economical for the encoder to create initially, an abbreviated format compressed data-less image, containing only the Huffman tables, followed by a sequence of compressed images in which the Huffman tables are omitted. To expand the image sequence, the JPEG decoder first decodes the tables-only data, thus installing the Huffman tables, which are subsequently used in the decoding of all the images in the sequence. Compressed data generated by the ZR36050 fully complies with the JPEG standard and includes all headers and marker segments necessary to allow it to be decoded by a compliant JPEG decoder. The JPEG standard allows virtually unlimited permutations in the order and repetition of optional marker segments. As a practical matter, there are some restrictions on the permutations and repetitions in compressed data generated by the ZR36050:

- The order of optional marker segments is fixed, as follows: APP, COM, DRI, DQT, DHT.

- Only one instance of each optional marker segment can be inserted before each SOS, or the SOF, marker.

- The frame header can specify up to eight image components.

- A compressed image can contain up to eight scans.

A compressed image to be decoded by the ZR36050 must be in JPEG standard format. The ZR36050 recognizes and decodes all the following marker types: SOI, SOF (SOF0 or SOF3), SOS, APP, COM, DRI, RST, DQT, DHT, DNL, EOI. All marker segments other than JPEG Baseline marker segments, i.e., markers followed by a length parameter, are disregarded and do not cause any error. Markers without a following length parameter, except for SOI, RST and EOI, will cause unpredictable behavior. A marker can be prefixed by any number of FF bytes.

In its decoding modes, the ZR36050 can expand any JPEG Baseline compressed image. The finite size of the Internal

## ADVANCE INFORMATION ZR36050

Memory, however, does impose some restrictions, that have only a very minor effect on the applicability of the device:

- The number of image components specified in the frame header must be eight or fewer.

- A DHT marker segment must have a length of 420 or fewer bytes (excluding the DHT marker), otherwise the tables may be decoded incorrectly into the Huffman Table Store.

A JPEG Baseline DHT segment has a length of only 418 bytes, so this is not normally a problem. The restriction, however, stems from the fact that the standard does not explicitly disallow the repetition of the same tables in a DHT segment. A DQT marker segment of any length is decoded correctly into the Quantization Tables Store. If, however, its length (excluding the DQT marker) is greater than 262 bytes, it may overwrite the DHT, APP, and COM segments in Internal Memory, affecting the ability of the host to read out the contents of these segments correctly.

A JPEG Baseline DQT segment has a maximum length of 262 bytes. The restriction again stems from the fact that the standard does not explicitly disallow the repetition of the same tables in a DQT segment.

In addition to the above restrictions, to be decoded correctly, the frame header of a JPEG Lossless compressed image must specify a precision of 12 or fewer bits, and only horizontal subsampling. The scan header must select a type 1 predictor (onedimensional horizontal), and can specify at most two different Huffman tables.

## **OPERATING MODES**

The host sets the operating mode of the ZR36050 by programming the MODE register. Nine distinct modes can be selected, falling into two categories:

- six encoding modes, involving compression and associated functions. The encoding modes are: JPEG Baseline Compression Pass, Auto Bit Rate Control, Statistical Pass, Compression Pass with Bit Rate Control, Tables-only Pass, and Tables Preload.

- three decoding modes, involving expansion: JPEG Baseline Expansion, Fast Preview, and Tables Preload.

Two additional modes, the Lossless compression and expansion modes of operation, are not distinguished from the JPEG Baseline Compression Pass and Expansion, respectively, in the programming of the MODE register. Rather, the ZR36050 enters the JPEG Baseline or Lossless mode based on the SOF (Start Of Frame) marker. If the marker found in internal memory (compression) or the compressed data (expansion) is SOF0 (FFC0), the ZR36050 configures itself for JPEG Baseline operation. Otherwise, if the marker is SOF3 (FFC3), it configures itself for Lossless operation.

Auto Bit Rate Control, Statistical Pass, and Compression Pass with Bit Rate Control are relevant only to JPEG Baseline compression, and Fast Preview is useful only with JPEG Baseline compressed data. These modes have no meaning for Lossless operation.

### **ENCODING MODES**

### JPEG Baseline Compression Pass

The Compression Pass performs the Baseline encoding operation on the input image component samples. During a Compression Pass, the ZR36050 reads the JPEG marker segment information written by the host in the Marker Segments Section of Internal Memory, and uses it to determine the MCU configuration, and includes the compulsory and optional marker segments (selected by the MARKERS\_EN register) in the compressed data stream. Note that, if the DQT marker segment is enabled, the ZR36050 first multiplies the quantization tables specified in the DQT segment of Internal Memory by the Scale Factor, and stores the scaled tables in the Quantization Table Store. The quantization tables included in the compressed data are the same as the stored (scaled) tables. At the completion of the JPEG Baseline Compression Pass, the ZR36050 calculates a New Scale Factor (NSF) and saves it in the SF Internal Memory register. The NSF can be used in the next encoding operation or the host can overwrite it by its own Scale Factor.

### **Statistical Pass**

In the Statistical Pass, the ZR36050 performs the computations for JPEG Baseline encoding of the image, with the initially specified Scale Factor, but without transferring any data to the Code Buffer. It accumulates the code volume and a total activity measure. Based on the Target Code Volume (TCV\_DATA register), it calculates the Allocation Factor and a new Scale Factor at the end of the pass. It writes the new Scale Factor in the SF register, in place of the initial Scale Factor, and the Allocation Factor, Accumulated Code Volume, and Total Activity measure, in their respective registers (SF, AF, ACV, and ACT), where the host can access them if needed.

### **Compression Pass with Bit Rate Control**

This mode allows the user to ensure a compressed data volume equal to or slightly less than the Target Code Volume. Before encoding each block, the ZR36050 computes a measure of the block activity, and allocates a code volume to the block based on the activity and the Allocation Factor (AF register). During encoding of the block, if the accumulated code volume for the block exceeds the allocation, the ZR36050 truncates the code for the block. The code is also truncated if it exceeds the Maximum Block Code Volume specified in the MBCV register. Aside from the bit rate control, this mode is the same as a JPEG

Baseline Compression Pass, and the resulting compressed data is fully JPEG compatible. At the completion of the Compression Pass with or without Bit Rate Control, the ZR36050 calculates a New Scale Factor (NSF) and saves it in the SF Internal Memory register. The NSF can be used in the next encoding operation or the host can overwrite it by its own Scale Factor.

#### Auto Bit Rate Control

In this mode the ZR36050 performs a Statistical Pass followed automatically (without host intervention) by a Compression Pass with Bit Rate Control. The ZR36050 computes the new Scale Factor and the Allocation Factor at the end of the Statistical Pass, and rescales the quantization tables by the new scale factor at the start of the Compression Pass. The DQT marker must be enabled for Auto Bit Rate Control to work correctly.

#### **Tables-Only Pass**

In this mode, the ZR36050 generates compressed data in the JPEG abbreviated format for table specification. The abbreviated format compressed data contains only the SOI marker, quantization and/or Huffman tables specifications (DQT and/or DHT marker segments), optional APP, COM marker segments, and the EOI marker. The content of the MARKERS\_EN register specifies which marker segments are to be included in the abbreviated format data. The Pixel Interface is inoperative in this mode.

### **Tables Preload for Encoding**

Prior to encoding a sequence of images with the same quantization and/or Huffman tables, this mode is used to preload the tables. The DQTI and DHTI bits of the MARKERS\_EN register specify which tables to preload. If DQTI is set, the ZR36050 multiplies the quantization tables, specified in the DQT segment of Internal Memory by the Scale Factor, and stores the scaled tables in the Quantization Tables Store. If DHTI is set, it decodes the Huffman tables specifications from the DHT segment of Internal Memory, where they are specified in accordance with the JPEG syntax, and stores the decoded tables in the Huffman Tables Store, for use in compressing the images. In this mode, the Pixel Interface and the Code Buffer are inoperative.

### JPEG Lossless Compression

In a Compression Pass, if the ZR36050 finds the SOF3 frame marker in the Internal Memory, it switches to the JPEG Lossless Compression mode. JPEG Lossless compression uses a spatial algorithm, so the DCT Unit is bypassed in this mode. No quantization is performed, so the Quantization Tables Store is not used. The ZR36050 encodes the image samples using the JPEG one-dimensional horizontal prediction method and Huffman coding. Up to two Huffman tables are allowed in JPEG Lossless compression. The sample precision can be from 2 to 12 bits. Horizontally subsampled components are supported and no point transform is performed (the point transform parameter in the scan header marker segment is ignored).

### **DECODING MODES**

#### JPEG Baseline Expansion

In Expansion mode, the ZR36050 reads compressed data and expands it using the inverse of the JPEG Baseline encoding algorithm. It stores the marker segments extracted from the compressed data in the Marker Segments Section of Internal Memory, where the host can access the information. When it encounters a DQT or DHT marker segment, it decodes the segment and stores the tables in the Table Stores. It expands any subsequent compressed image data using the stored tables. If the compressed data contains multiple instances of a marker segment, a new segment will overwrite the previous segment of the same type in the internal memory. This mode is also used to decode abbreviated format tables-only compressed data.

#### **Fast Preview**

In this mode, the ZR36050 decodes only the DC coefficients from the JPEG Baseline compressed image data, and outputs them, after level-shifting to form unsigned DC values, via the Pixel Interface. Since only one sample is output for each 8 x 8 block, the result is a thumbnail version of the image, scaled down by a factor of eight horizontally and vertically. It is generated up to 25 times faster than full image expansion. The inverse DCT computation is bypassed in this mode.

### **Tables Preload for Decoding**

The ZR36050 reads the quantization and/or Huffman tables from Internal Memory and stores them in the Table Stores for decoding images in the JPEG abbreviated data-only format. The DQTI and DHTI bits of the MARKERS\_EN register specify which tables to preload. If DQTI is set, the ZR36050 multiplies the quantization tables by the Scale Factor and stores the scaled tables in the Quantization Tables Store. If DHTI is set, it decodes the Huffman tables specifications from the DHT segment of the Internal Memory, where they are specified in accordance with the JPEG syntax, and stores the decoded tables in the Huffman Tables Store. In this mode, the Pixel Interface and the Code Buffer are inoperative.

### JPEG Lossless Expansion

In Expansion mode, if the ZR36050 detects the SOF3 frame marker in the compressed data, it switches to the JPEG Lossless Expansion mode. The DCT Unit is bypassed in this mode, and the quantization tables are not used. The compressed image is decoded by the inverse of the method used in the Lossless Compression mode. As in Lossless Compression, up to two Huffman tables are allowed. The sample precision can be from 2 to 12 bits. Horizontally subsampled components are supported and no point transform is performed (the point transform parameter in the scan header marker segment is ignored. Therefore if a lossless bitstream with point transform other than zero is input into the ZR36050, it will be decoded as if the point transform is zero).

## **QUANTIZATION AND HUFFMAN TABLES**

The tables used by the ZR36050 to encode the image data are always the ones that reside in the Quantization and Huffman Table Stores. The host does not, however, write the table data directly into these Table Stores, but in the Marker Segments Section of Internal Memory. Therefore, before it can encode or decode actual image data, the ZR36050 must first have preloaded the table data in the Table Stores.

In encoding, this can be done as part of the Statistical Pass or Compression Pass (Baseline or Lossless), if the appropriate bits of the MARKERS\_EN register are set. Alternatively, it can be accomplished as a separate operation, in the Tables Preload for Encoding mode.

In decoding, if the marker segments preceding the compressed image data contain table specifications, the ZR36050 decodes

these marker segments and preloads the tables in the Table Stores, and decodes the image using these tables. Otherwise, it uses the tables that pre-exist in the Table Stores, either decoded from a previous image expansion, or preloaded using the Tables Preload for Decoding operation.

Note that the same Huffman Table Store is used both in encoding and decoding. However, the internal format of the tables is different. Therefore, after a switch from encoding to decoding, or vice versa, the Huffman Table Store is invalid, and Huffman tables must be preloaded before image data can be encoded or decoded. The Quantization Table Store remains valid. In encoding, however, if the Scale Factor is changed, the Quantization Table Store is clearly invalidated and must be preloaded before the new Scale Factor can take effect.

### **NON-OPERATING STATES**

The ZR36050 has four states in which it does not process data: Idle, Waiting, Standby, and Freeze.

The host can access the Internal Memory in the Idle and Waiting states, but not in the Standby and Freeze states.

### Idle

The ZR36050 enters the Idle state after these events:

- de-activation of RESET

- activation of END at the end of an encoding or decoding process

- abort of encoding, due to code volume overflow, or DCT Coefficient Buffer(s) overflow.

It remains Idle until the host issues the GO command (write to address 0 of Internal Memory), to initiate a new encoding or decoding process.

### Waiting

In this state, the ZR36050 has stopped processing during encoding or decoding, and is waiting for a response from the host or system control circuitry in order to continue. It enters a Waiting state in one of these conditions: