## 150-mA Low Noise, Low Dropout Regulator

## **APPLICATIONS**

- · Cellular Phones, Wireless Handsets

- PDAs

- MP3 Players

- · Digital Cameras

- Pagers

- Wireless Modem

- Noise-Sensitive Electronic Systems

## **DESCRIPTION**

The SiP21106 BiCMOS 150 mA low noise LDO voltage regulators are the perfect choice for low battery operated low powered applications. An Ultra low ground current and low dropout voltage of 135 mV at 150 mA load helps to extend battery life for portable electronics. Systems requiring a quiet voltage source, such as RF applications, will benefit from the SiP21106 low output noise.

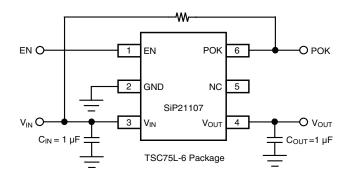

The SiP21107 do not require a noise bypass cpacitor and provides an error flag pin (POK or Power OK). POK output requires an external pull-up resistor and goes low when the supply has not come up to voltage.

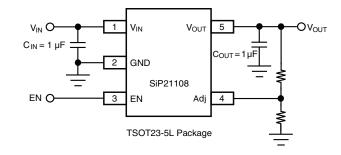

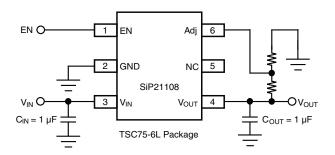

The SiP21108 output is adjusted with an external resistor network.

The SiP21106/7/8 regulators allow stable operation with very small ceramic output capacitors, reducing board space and component cost. They are designed to maintain regulation while delivering 330 mA peak current upon turn-on. During start-up, an active pull-down circuit improves the output transient response and regulation. In shutdown mode, the output automatically discharges to ground through a 100  $\Omega$  NMOS.

The SiP21106/7/8 are available in TSOT23-5L and a super thin lead (Pb)-free TSC75-6L packages for operation over the industrial operation range (- 40 °C to 85 °C).

## **FEATURES**

TSC75-6L Package (1.6 x 1.6 x 0.6 mm), and TSOT23-5L Package Options

- Low Dropout Voltage: 135 mV at 150 mA

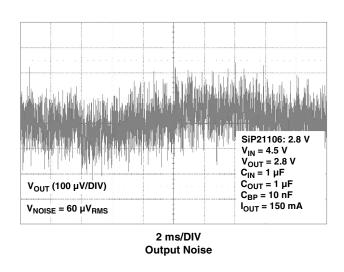

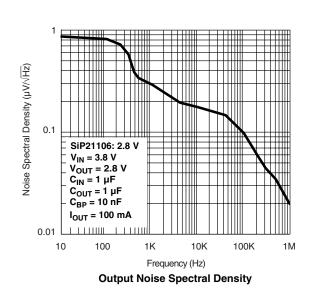

- SiP21106 Low Noise: 60 µV<sub>(rms)</sub> (10 Hz to 100 kHz Bandwidth)

With 10 nF Over Full Load Range

- 35 μA (typical) Ground Current at 1 mA Load

- 1 μA Maximum Shutdown Current at 85 °C

- · Output Auto Discharge at Shutdown Mode

- Built-in Short Circuit (330 mA typical) and Thermal Protection (160 °C typical)

- SiP21108 Adjustable Output Voltage

- SiP21107 POK Error Flag

- 40 °C to + 125 °C Junction Temperature Range for Operation

- Uses Low ESR Ceramic Capacitors

- Fixed Voltage Output 1.3 V to 5 V in 50 mV Steps

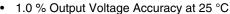

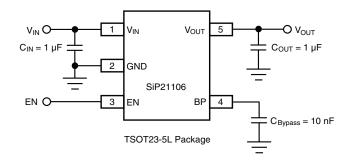

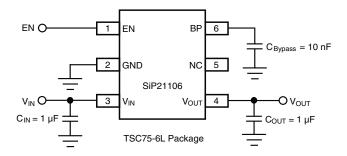

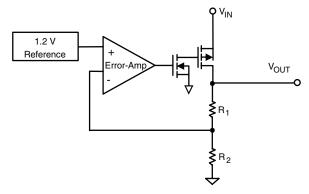

## TYPICAL APPLICATION CIRCUIT

Pb-free

RoHS

# Vi**含油以89116000X**-18-E3"供应商

| Parameter                                                  | Li                             | Limit         |      |

|------------------------------------------------------------|--------------------------------|---------------|------|

| Input Voltage, V <sub>IN</sub> to GND                      | - 0.3                          | - 0.3 to 6    |      |

| V <sub>EN</sub> (See Detailed Description)                 | - 0.3                          | - 0.3 to 6    |      |

| Output Current (I <sub>OUT</sub> )                         | Short Circu                    | uit Protected |      |

| Output Voltage (V <sub>OUT</sub> )                         | - 0.3 to V <sub>IN</sub> + 0.3 |               | V    |

|                                                            | TSC75-6L                       | TSOT23-5L     |      |

| Package Power Dissipation (P <sub>D</sub> ) <sup>a</sup>   | 420                            | 440           | mW   |

| Package Thermal Resistance (θ <sub>JA</sub> ) <sup>b</sup> | 131                            | 180           | °C/W |

| Maximum Junction Temperature, T <sub>J(max)</sub>          | 1:                             | 125           |      |

| Storage Temperature, T <sub>STG</sub>                      | - 65                           | - 65 to 150   |      |

| Lead Temperature, T <sub>L</sub> <sup>c</sup>              | 2                              | 260           |      |

## Notes:

- a. Derate 7.6 mW/ $^{\circ}$ C for TSC75-6L package and 5.5 mW/ $^{\circ}$ C for TSOT23-5L package above T<sub>A</sub> = 70  $^{\circ}$ C.

- b. Device mounted with all leads soldered or welded to PC board.

- c. Soldering for 5 sec.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating/conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE                  |            |      |  |  |  |

|----------------------------------------------|------------|------|--|--|--|

| Parameter                                    | Limit      | Unit |  |  |  |

| Input Voltage, V <sub>IN</sub>               | 2.2 to 5.5 | V    |  |  |  |

| Operating Ambient Temperature T <sub>A</sub> | - 40 to 85 | °C   |  |  |  |

|                                                           |                      | Test Conditions Unless Specif                                             | ied               |                  |                  |                  |              |

|-----------------------------------------------------------|----------------------|---------------------------------------------------------------------------|-------------------|------------------|------------------|------------------|--------------|

|                                                           |                      | $V_{IN} = V_{OUT(nom)} + 1.0 V = V_{EI}$                                  |                   |                  |                  |                  |              |

|                                                           |                      | $I_{OUT} = 1$ mA, $C_{IN} = 1$ $\mu$ F, $C_{OUT} =$                       |                   |                  |                  |                  |              |

| Parameter                                                 | Symbol               | - 40 °C < T <sub>A</sub> < 85 °C for full                                 | Temp <sup>a</sup> | Min <sup>b</sup> | Тур <sup>с</sup> | Max <sup>b</sup> | Unit         |

| Input Voltage Range                                       | V <sub>IN</sub>      |                                                                           |                   | 2.2              |                  | 5.5              | V            |

| Outrat Valtage Assurance                                  |                      | 1 4 50                                                                    | Room              | - 1.0            |                  | 1.0              | %            |

| Output Voltage Accuracy                                   | V <sub>OUT</sub>     | I <sub>OUT</sub> = 1 mA                                                   | Full              | - 2.5            |                  | 2.5              |              |

| Line Regulation                                           |                      | All others                                                                | Full              | - 0.2 0.00       | 0.006            | 0.2              | %/V          |

| Line Regulation                                           |                      | For 4.6 V to 5.0 V                                                        | Full              | - 0.4            |                  | 0.4              | 70/ <b>V</b> |

|                                                           |                      | I <sub>OUT</sub> = 50 mA                                                  | Room              |                  | 45               |                  |              |

|                                                           |                      | 1001 = 30 MA                                                              | Full              |                  | 55               |                  |              |

| Dropout Voltage <sup>d</sup>                              | $V_{DO}$             | I <sub>OUT</sub> = 100 mA                                                 | Room              |                  | 90               |                  | mV           |

| $(2.2 \text{ V} \le \text{V}_{OUT(nom)} < 2.6 \text{ V})$ | *DO                  | 1001 = 100 111/1                                                          | Full              |                  | 106              |                  |              |

|                                                           |                      | I <sub>OUT</sub> = 150 mA                                                 | Room              |                  | 135              | 250              |              |

|                                                           |                      | .001                                                                      | Full              |                  | 160              | 300              |              |

|                                                           |                      | I <sub>OUT</sub> = 50 mA                                                  | Room              |                  | 45               |                  | mV           |

|                                                           | V <sub>DO</sub>      | .001                                                                      | Full              |                  | 55               |                  |              |

| Dropout Voltage                                           |                      | I <sub>OUT</sub> = 100 mA                                                 | Room              |                  | 90               |                  |              |

| $(V_{OUT(nom)} \ge 2.6 \text{ V})$                        |                      | 301                                                                       | Full              |                  | 106              |                  |              |

|                                                           |                      | I <sub>OUT</sub> = 150 mA                                                 | Room              |                  | 135              | 180              |              |

|                                                           |                      | 301                                                                       | Full              |                  | 160              | 220              |              |

|                                                           | I <sub>GND</sub>     | I <sub>OUT</sub> = 1 mA                                                   | Room              |                  | 35               | 75               | μΑ           |

| Ground Pin Current <sup>e</sup>                           |                      |                                                                           | Full              |                  |                  | 85               |              |

|                                                           |                      | I <sub>OUT</sub> = 150 mA                                                 | Room              |                  | 39               | 75               |              |

|                                                           | e <sub>N</sub>       | SiP21106                                                                  | Full              |                  |                  | 85               |              |

|                                                           |                      | $V_{OUT(nom)} = 2.8 \text{ V, BW} = 10 \text{ Hz to } 10^{-10} \text{ J}$ | 00 kHz. Room      | Room             | 60               |                  | μV           |

| a contract frames                                         |                      | 1 mA < I <sub>OUT</sub> < 150 mA, C <sub>BP</sub> = 0.0                   | 1 µF              |                  |                  |                  | ۳.           |

| Output Noise Voltage <sup>f</sup> (RMS)                   |                      | SiP21107/8                                                                |                   |                  |                  |                  |              |

|                                                           |                      | $V_{OUT(nom)} = 2.8 \text{ V, BW} = 10 \text{ Hz to } 10$                 | 00 kHz, Room      | Room             | 350              |                  | μV           |

|                                                           |                      | 1 mA < I <sub>OUT</sub> < 150 mA                                          |                   |                  |                  |                  |              |

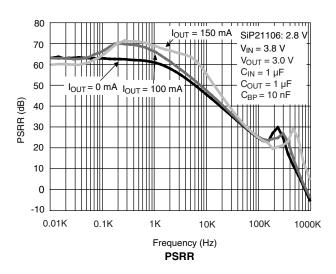

| Disale Deiestica                                          | DODD                 |                                                                           | kHz Room          | _                | 70               |                  | 40           |

| Ripple Rejection                                          | PSRR                 | 001                                                                       |                   | _                | 55               |                  | dB           |

|                                                           |                      |                                                                           | 00 kHz Room       |                  | 25               |                  |              |

|                                                           |                      | $V_{OUT} \ge 2.6 \text{ V},$ $I_{OUT}$ : 1 mA to 150 mA                   | Room              |                  | 0.003            | 0.006            |              |

| Load Regulation                                           | LDR                  | V <sub>OUT</sub> < 2.6 V,                                                 |                   |                  |                  |                  | %/mA         |

|                                                           |                      | I <sub>OUT</sub> : 1 mA to 150 mA                                         | Room              |                  | 0.005            | 0.009            | <u></u>      |

| Auto Discharge Resistance                                 | R <sub>DIS</sub>     | V <sub>OUT</sub> = 2 V                                                    | Room              |                  | 100              | İ                | Ω            |

| Thermal Shutdown Junction                                 |                      |                                                                           | Boom              |                  | 160              |                  |              |

| Temperature                                               | T <sub>J(S/D)</sub>  |                                                                           | Room              |                  | 100              |                  | °C           |

| Thermal Hysteresis                                        | T <sub>HYST</sub>    |                                                                           | Room              |                  | 20               |                  | C            |

| Output Current Limit                                      | I <sub>O_LIMIT</sub> | V <sub>OUT</sub> = 0 V                                                    | Room              | 170              | 330              | 600              | mA           |

| Shutdown Supply Current                                   | I <sub>CC(off)</sub> | V <sub>EN</sub> = 0 V                                                     | Full              |                  | 0.02             | 1                | μΑ           |

| EN Pin Input Voltage                                      | V <sub>ENH</sub>     | High = Regulator ON (Rising)                                              | Full              | 1.2              |                  | 5.5              | V            |

| Livi in input voitage                                     | V <sub>ENL</sub>     | NL Low = Regulator OFF (Falling)                                          |                   |                  |                  | 0.4              |              |

| EN Pin Input Current                                      | I <sub>EN</sub>      |                                                                           | Room              |                  | 0.009            |                  | μΑ           |

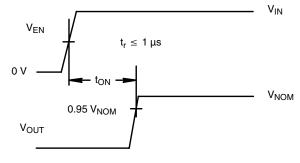

| Output Voltage Turn-On Time                               | t <sub>on</sub>      | EN to V <sub>OUT</sub> delay; I <sub>OUT</sub> = 1 mA                     |                   |                  | 70               |                  | μs           |

# Vi**含油以89116000X**-18-E3"供应商

| SPECIFICATIONS                          |                    |                                                                |                   |                  |                  |                  |          |

|-----------------------------------------|--------------------|----------------------------------------------------------------|-------------------|------------------|------------------|------------------|----------|

|                                         |                    | Test Conditions Unless Specified                               |                   |                  |                  |                  |          |

|                                         |                    | $V_{IN} = V_{OUT(nom)} + 1.0 V$                                |                   |                  |                  |                  |          |

|                                         |                    | $I_{OUT}$ = 1 mA, $C_{IN}$ = 1 $\mu$ F, $C_{OUT}$ = 1 $\mu$ F  |                   |                  |                  |                  |          |

| Parameter                               | Symbol             | - 40 $^{\circ}$ C < T <sub>A</sub> < 85 $^{\circ}$ C for full  | Temp <sup>a</sup> | Min <sup>b</sup> | Typ <sup>c</sup> | Max <sup>b</sup> | Unit     |

| Adjustable Voltage Section (SiP21108    | Version only       |                                                                |                   |                  |                  |                  |          |

| Feedback Voltage                        | V                  |                                                                | Room              | 1.188            | 1.2              | 1.212            | <b>V</b> |

| reedback voltage                        | $V_{Adj}$          |                                                                | Full              | 1.170            |                  | 1.230            | V        |

| Error Flag Section (SiP21107 Version of | only)              |                                                                |                   |                  |                  |                  |          |

| POK(OFF) Leakage                        | I <sub>OFF</sub>   | R <sub>PU</sub> to V <sub>OUT</sub> or V <sub>IN</sub>         | Full              |                  |                  | 1                | μΑ       |

| POK(ON) Voltage                         | V <sub>POKL</sub>  | I <sub>SINK</sub> = 0.5 mA                                     | Full              |                  |                  | 0.4              | V        |

| POK Threshold <sup>g</sup>              | V <sub>POKLH</sub> | V <sub>IN</sub> rising, I <sub>OUT</sub> = 1 mA, POK goes high | Full              | 90               |                  | 96               | %        |

| POK Hysteresis                          | V <sub>HYST</sub>  | V <sub>IN</sub> falling, I <sub>OUT</sub> = 1 mA, POK goes low | Room              |                  | 1.5              |                  | /0       |

#### Notes:

- a. Room = 25 °C, Full = -40 to 85 °C. Derate 7.6 mW/°C for TSC75 and 5.5 mW/°C for SOT23 above  $T_A = 70$  °C

- b. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

- c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- d. Dropout voltage is defined as the input-to-output differential voltage at which the output voltage drops 2 % below its nominal value with constant load. For outputs = 2.2 V, dropout voltage is not applicable due to 2.2 V minimum input voltage requirement.

- e. Ground current is specified for normal operation as well as "drop-out" operation.

- f. Output noise is proportional to output voltage. Use formula  $e_N = 60 \ \mu V (rms)^* V_{OUT}/2.8 \ V$ .

- g. POK threshold percentage is calculated by  $\rm V_{IN}/\rm V_{OUT}~x~100~\%.$

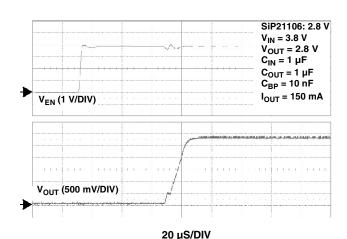

## **TIMING WAVEFORMS**

Figure 1.

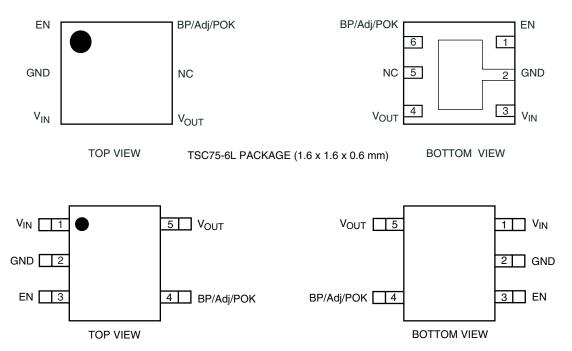

## **PIN CONFIGURATION**

TSOT23-5L Package Figure 2.

| PIN DESCRIPTION                               |   |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-----------------------------------------------|---|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Number Pin Number TSC75-6L TSOT23-5L Name |   | Name             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 1                                             | 3 | EN               | By applying less than 0.4 V to this pin, the device will be turned off. Connect this pin $V_{\text{IN}}$ if unused. Do not leave floating.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 2                                             | 2 | GND              | Ground pin. For better thermal capability, directly connected to large ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 3                                             | 1 | V <sub>IN</sub>  | Input supply pin. Bypass this pin with a 1 µF ceramic or tantalum capacitor to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 4                                             | 5 | V <sub>OUT</sub> | Output voltage. Connect C <sub>OUT</sub> between this pin and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 5                                             | = | NC               | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 6                                             | 4 | BP/Adj/POK       | - BP (SiP21106): Noise bypass pin. For low noise applications, a 10 nF ceramic capacitor should be connected from this pin to ground.  - Adj (SiP21108): Adjust input pin. Connect feedback resistors to program the output voltage for trim value of 1.2005 V.  - POK (SiP21107): Power OK (Error Flag) pin. Open-drain output, which requires connecting a pull-up resistor to V <sub>IN</sub> or V <sub>OUT</sub> . POK pin is actively high to indicate an output normal operation condition on regulator and goes low to indicate under-voltage fault condition. |  |  |

# SiP21106/7/8

# Vi**含词以89IIcon**X-18-E3"供应商

| ORDERING INFORMATION |         |            |                   |           |  |  |

|----------------------|---------|------------|-------------------|-----------|--|--|

| Part Number          | Marking | Voltage    | Temperature Range | Package   |  |  |

| SiP21108DVP-T1-E3    | AA      | Adjustable |                   |           |  |  |

| SiP21106DVP-18-E3    | BG      | 1.8        |                   |           |  |  |

| SiP21106DVP-25-E3    | BP      | 2.5        |                   |           |  |  |

| SiP21106DVP-26-E3    | BR      | 2.6        |                   |           |  |  |

| SiP21106DVP-28-E3    | BT      | 2.8        |                   |           |  |  |

| SiP21106DVP-30-E3    | BV      | 3.0        |                   |           |  |  |

| SiP21106DVP-33-E3    | BY      | 3.3        |                   |           |  |  |

| SiP21106DVP-46-E3    | CM      | 4.6        |                   |           |  |  |

| SiP21106DVP-285-E3   | СТ      | 2.85       | - 40 °C to 85 °C  | TSC75-6L  |  |  |

| SiP21107DVP-18-E3    | DG      | 1.8        |                   |           |  |  |

| SiP21107DVP-25-E3    | DP      | 2.5        |                   |           |  |  |

| SiP21107DVP-26-E3    | DR      | 2.6        |                   |           |  |  |

| SiP21107DVP-28-E3    | DT      | 2.8        |                   |           |  |  |

| SiP21107DVP-30-E3    | DV      | 3.0        |                   |           |  |  |

| SiP21107DVP-33-E3    | DY      | 3.3        |                   |           |  |  |

| SiP21107DVP-46-E3    | EM      | 4.6        |                   |           |  |  |

| SiP21107DVP-285-E3   | ET      | 2.85       |                   |           |  |  |

| SiP21108DT-T1-E3     | N9      | Adjustable |                   |           |  |  |

| SiP21106DT-18-E3     | N1      | 1.8        |                   |           |  |  |

| SiP21106DT-25-E3     | NA      | 2.5        |                   |           |  |  |

| SiP21106DT-26-E3     | NC      | 2.6        |                   |           |  |  |

| SiP21106DT-28-E3     | N2      | 2.8        |                   |           |  |  |

| SiP21106DT-285-E3    | NE      | 2.85       |                   |           |  |  |

| SiP21106DT-30-E3     | NG      | 3.0        |                   |           |  |  |

| SiP21106DT-33-E3     | N3      | 3.3        |                   |           |  |  |

| SiP21106DT-46-E3     | N4      | 4.6        | - 40 °C to 85 °C  | TSOT23-5L |  |  |

| SiP21107DT-18-E3     | N5      | 1.8        |                   |           |  |  |

| SiP21107DT-25-E3     | NB      | 2.5        |                   |           |  |  |

| SiP21107DT-26-E3     | ND      | 2.6        |                   |           |  |  |

| SiP21107DT-28-E3     | N6      | 2.8        |                   |           |  |  |

| SiP21107DT-285-E3    | NF      | 2.85       |                   |           |  |  |

| SiP21107DT-30-E3     | NH      | 3.0        |                   |           |  |  |

| SiP21107DT-33-E3     | N7      | 3.3        |                   |           |  |  |

| SiP21107DT-46-E3     | N8      | 4.6        |                   |           |  |  |

Other fixed output voltage options are available. Please contact your Vishay sales representative or distributor for details.

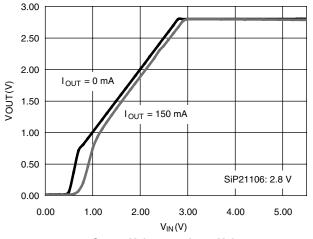

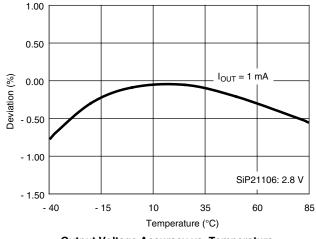

## **TYPICAL CHARACTERISTICS**

**Output Voltage vs. Input Voltage**

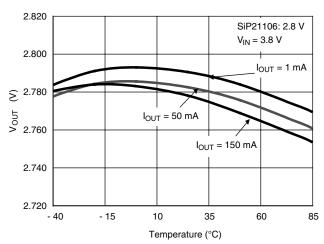

**Output Voltage Accuracy vs. Temperature**

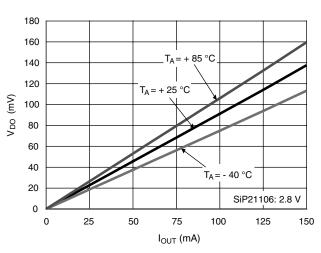

**Dropout Voltage vs. Load Current**

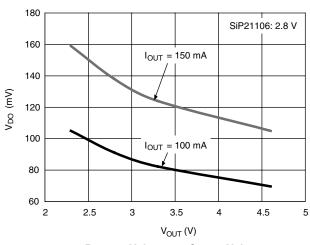

**Dropout Voltage vs. Output Voltage**

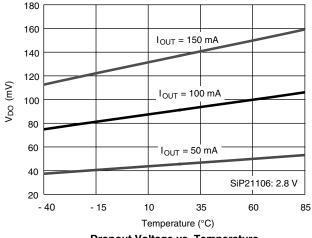

**Dropout Voltage vs. Temperature**

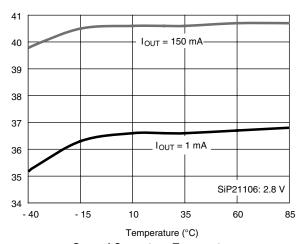

Ground Current vs. Temperature

# Vi**含油以89116000X**-18-E3"供应商

# VISHAY.

## **TYPICAL CHARACTERISTICS**

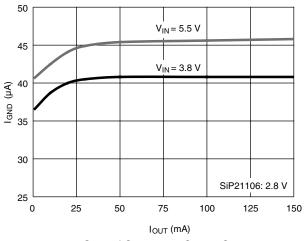

**Ground Current vs. Output Current**

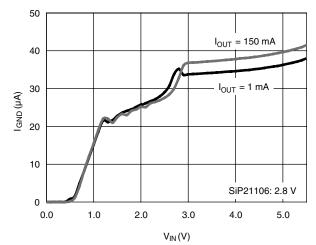

Ground Current vs. Input Voltage at 25 °C

350 300 250 150 100 0 0.001 0.0056 0.01 0.056 0.1

$\label{eq:BP} \mbox{BP Capacitance } (\mu F) \\ \mbox{Output Noise vs. BP Capacitance}$

SiP21106: 2.8 V

**Output Voltage Accuracy vs. Load Current**

400

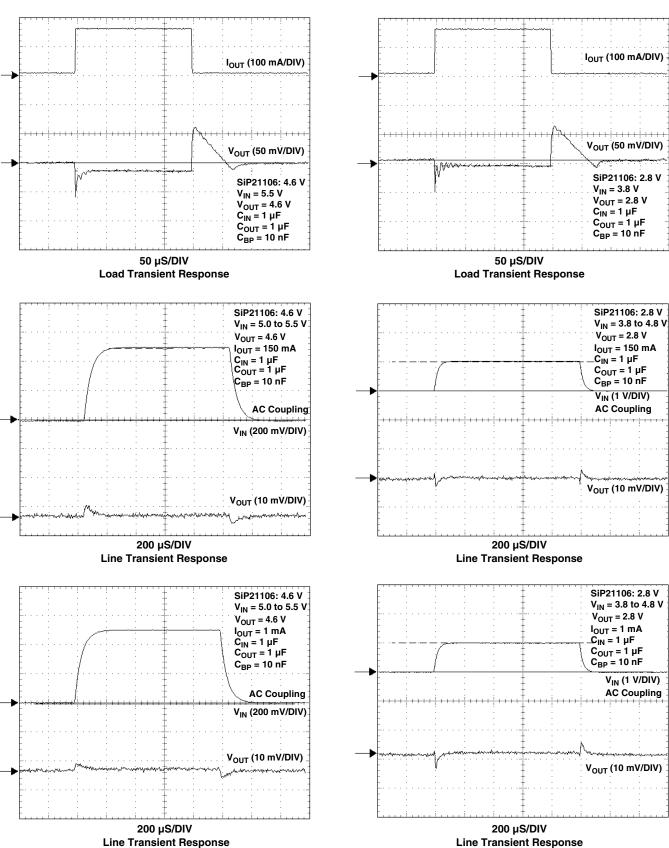

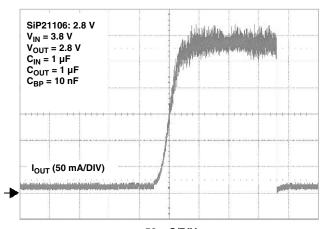

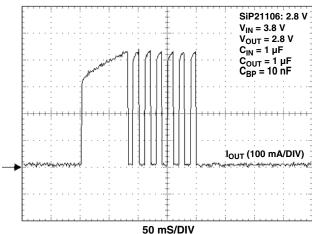

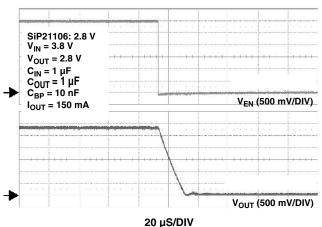

## **TYPICAL OPERATING WAVEFORMS**

## Vi**ghay**618IId0600X-18-E3"供应商

# VISHAY

## TYPICAL OPERATING WAVEFORMS

50 mS/DIV Output Short Circuit Current

Output Short Thermal Cycling

20 μ5/DIV

Output Voltage Power-Down

**Output Voltage Start-Up**

## **TYPICAL WAVEFORMS**

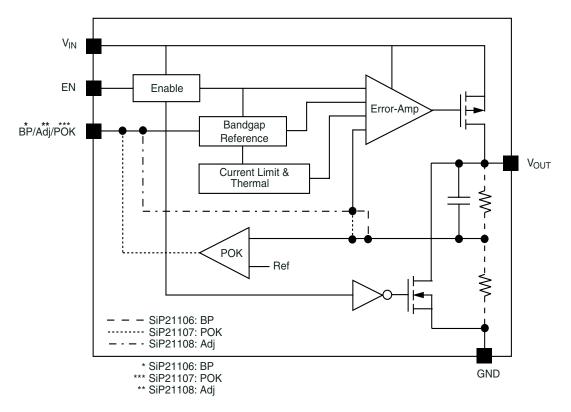

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 3.

## Vi**含 泡 (6 18 11 16 06 10 X** - 18 - E3 "供应商

## DETAILED DESCRIPTION

As shown in the block diagram, the circuit consists of a bandgap reference, error amplifier, P-Channel pass transistor and an internal feedback resistor voltage divider, which is used to monitor and control the output voltage.

A constant 1.2 V bandgap reference voltage is applied to the non-inverting input of the error amplifier. The error amplifier compares this reference with the feedback voltage on its inverting input and amplifies the difference. If the feedback voltage is lower than the reference voltage, the pass-transistor gate is pulled low. This increases the PMOS's gate to source voltage and allows more current to pass through the transistor to the output which increases the output voltage. Conversely, if the feedback voltage is higher than the reference voltage, the pass transistor gate is pulled high, decreasing the gate-to-source voltage, thereby allowing less current to pass to the output and causing it to drop.

## **Internal P-Channel Pass Transistor**

A 0.9  $\Omega$  (typical) P-Channel MOSFET is used as the pass transistor for the SiP21106/7/8 part series. The MOSFET transistor offers many advantages over the more, formerly, common PNP pass transistor designs, which ultimately result in longer battery lifetime. The main disadvantage of PNP pass transistors is that they require a certain base current to stay on, which significantly increases under heavy load conditions. In addition, during dropout, when the pass transistor saturates, the PNP regulators waste considerable current. In contrast, P-Channel MOSFETS require virtually zero-base drive and do not suffer from the stated problems. These savings in base drive current translate to lower quiescent current which is typical around 35  $\mu$ A as shown in the *Typical Characteristics*.

## Shutdown and Auto-Dischage/No-Discharge

Bringing the EN voltage low will place the part in shutdown mode where the device output enters a high-impedance state and the quiescent current is reduced to below 1  $\mu$ A, reducing the drain on the battery in standby mode and increasing standby time. Connect EN pin to input for normal operation. The output has an internal pull down to discharge the output to ground when the EN pin is low. The internal pull down is a 100  $\Omega$  typical resistor, which can discharge a 1  $\mu$ F in less than 1 ms. Refer to *Typical Operating Waveforms* for turn-off waveforms.

## **Output Voltage Selection**

The SiP21106 has fixed voltage outputs that are preset to voltages from 1.8 V to 4.6 V (see Ordering Information).

Figure 4.

The SiP21108 has a user-adjustable output that can be set through the resistor feedback network consisting of  $R_1$  and  $R_2$ .  $R_2$  range of 100K to 400K is recommended to be consistent with ground current specification.  $R_1$  can then be determined by the following equation:

$$R_1 = R_2 x \left( \frac{V_{OUT}}{V_{ref}} - 1 \right)$$

Where  $V_{ref}$  is typically 1.2005 V. Use 1 % or better resistors for better output voltage accuracy (see Figure 4).

#### **Current Limit**

The SiP21106/7/8 include a current limit block which monitors the current passing through the pass transistor through a current mirror and controls the gate voltage of the MOS-FET, limiting the output current to 330 mA (typical). This current limit feature allows for the output to be shorted to ground for an indefinite amount of time without damaging the device.

## **Thermal-Overload Protection**

The thermal overload protection limits the total power dissipation and protects the device from being damaged. When the junction temperature exceeds  $T_J=150~^{\circ}\text{C}$ , the device turns the P-Channel pass transistor off allowing the device to cool down. Once the temperature drops by about 20  $^{\circ}\text{C}$ , the thermal sensor turns the pass transistor on again and resumes normal operation. Consequently, a continuous thermal overload condition will result in a pulsed output. It is generally recommended to not exceed the junction temperature rating of 125  $^{\circ}\text{C}$  for continuous operation.

## Noise Reduction in SiP21106

For the SiP21106, an external 10 nF bypass capacitor at BP pin is used to create a low pass filter for noise reduction. The startup time is fast, since a power-on circuit pre-charges the bypass capacitor. After the power-up sequence the pre-charge circuit is switched to standby mode in order to save current. It is therefore not recommended to use larger bypass capacitor values than 50 nF. When the circuit is used without a capacitor, stable operation is guaranteed.

## **POK Status in SiP21107**

The POK comparator monitors the output until the supply comes up to specified percentage of  $V_{IN}$ . This open drain NMOS output requires an external pull-up resistor to either  $V_{OUT}$  or  $V_{IN}$ . The internal NMOS can drive up to 0.5 mA loads. POK pin is actively high to indicate an output normal operation condition on regulator and goes low to indicate under-voltage on regulator.

## **APPLICATION INFORMATION**

# Input/Output Capacitor Selection and Regulator Stability

It is recommended that a low ESR 1  $\mu$ F capacitor be used on the SiP21106/7/8 input. A larger input capacitance with lower ESR would improve noise rejection and line-transient response. A larger input bypass capacitor may be required in applications involving long inductive traces between the source and LDO. The circuit is stable with only a small output capacitor equal to 6 nF/mA (≈ 1 µF at 150 mA) of load. Since the bandwidth of the error amplifier is around 1 - 3 MHz and the dominant pole is at the output node, the capacitor should be capacitive in this range, i.e., for 150 mA load current, an ESR < 0.4  $\Omega$  is necessary. Parasitic inductance of about 10 nH can be tolerated. Applying a larger output capacitor would increase power supply rejection and improve loadtransient response. Some ceramic dielectrics such as the Z5U and Y5V exhibit large capacitance and ESR variation over temperature. If such capacitors are used, a 2.2 µF or larger value may be needed to ensure stability over the industrial temperature range. If using higher quality ceramic capacitors, such as those with X7R and Y7R dielectrics, a 1  $\mu$ F capacitor will be sufficient at all operating temperatures.

## **Operating Region and Power Dissipation**

An important consideration when designing power supplies is the maximum allowable power dissipation of a part. The maximum power dissipation in any application is dependant on the maximum junction temperature,  $T_{J(max)}$  = 125 °C, the ambient temperature,  $T_{A}$ , and the junction-to-ambient thermal resistance for the package, which is the summation of  $\theta_{J\text{-}C}$ , the thermal resistance of the package, and  $\theta_{C\text{-}A}$ , the thermal resistance through the PC board and copper traces. Power dissipation may be formulaically expressed as:

$$P_{(max)} = \frac{T_{J (max)} - T_{A}}{\theta_{J-C} + \theta_{C-A}}$$

The GND pin of the SiP21106/7/8 acts as both the electrical connection to GND as well as a path for channeling away heat. Connect this pin to a GND plane to maximize heat dissipation. Once maximum powChanneler dissipation is calculated using the equation above, the maximum allowable output current for any input/output potential can be calculated as

$$I_{OUT(max)} = \frac{P_{(max)}}{V_{IN} - V_{OUT}}$$

## **PCB Layout**

The component placement around the LDO should be done carefully to achieve good dynamic line and load response. The input and noise capacitor should be kept close to the LDO. The rise in junction temperature depends on how efficiently the heat is carried away from junction-to-ambient. The junction-to-lead thermal impedance is a characteristic of the package and is fixed. The thermal impedance between lead-to-ambient can be reduced by increasing the copper area on PCB. Increase the input, output and ground trace area to reduce the junction-to-ambient thermal impedance.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/ppg?74442">http://www.vishay.com/ppg?74442</a>.