## **SM5301BS**

3-channel Video Buffer with Built-in Wideband Filters with Filter Through Function

### **OVERVIEW**

The SM5301BS is a video filter LSI with buffered outputs for VESA-standard ATSC digital TV. The filter employs a 5-order Butterworth lowpass filter configuration. The filter characteristics have been optimized for minimal overshoot and flat group delay, it has a variable cutoff frequency and guaranteed output buffer-stage channel gain difference and phase difference values. It has also filter through mode.

## **FEATURES**

- Supply voltage:  $5V \pm 10\%$

- VESA-standard ATSC digital TV RGB/YUV video filters

- RGB/YUV switching multiplexer function

- Synctip clamp input

- 0dB, 6dB gain switching function (input-to-output AC signal gain)

- Channel-to-channel gain difference: 0.5dB (± 5% supply voltage variation)

- Channel-to-channel phase difference: 3.5 degree

- Output signal harmonic distortion (all channels):

1.5%

- Cutoff frequency: 5 to 37MHz variable

- Filter through mode (passband frequency is 46MHz, when gain is 6dB)

- Package: 28-pin HSOP (Pb free)

# **APPLICATIONS**

- Set-top boxes

- Digital television

- DVD players

### **ORDERING INFORMATION**

| Device   | Package     |

|----------|-------------|

| SM5301BS | 28-pin HSOP |

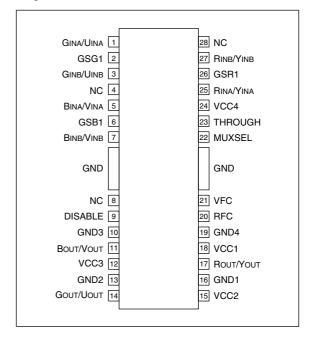

## **PINOUT**

(Top view)

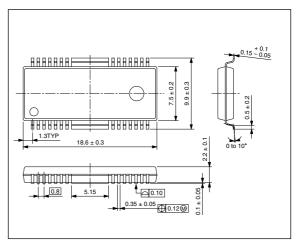

### PACKAGE DIMENSIONS

(Unit: mm)

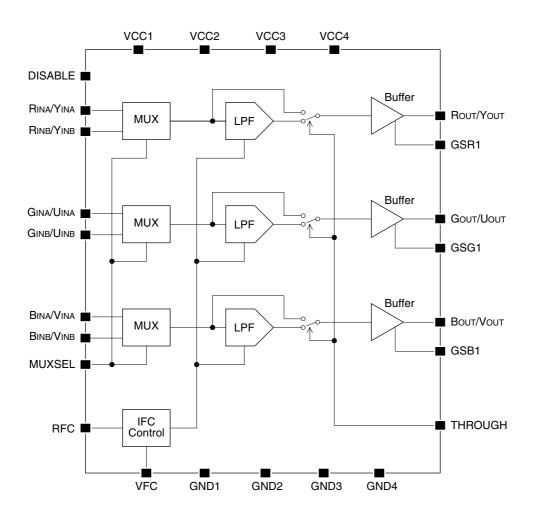

## **BLOCK DIAGRAM**

Note. Power supply pin distinction VCC1, GND1: R/Y block

VCC2, GND2: G/U block

VCC3, GND3: B/V block

VCC4, GND4: IFCCONT block, and logic input control block

# **PIN DESCRIPTION**

| Number | Name                               | I/O <sup>1</sup> | Description                                                                                                                                                                                  |

|--------|------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | G <sub>INA</sub> /U <sub>INA</sub> | I                | Analog G <sub>INA</sub> or U <sub>INA</sub> signal input                                                                                                                                     |

| 2      | GSG1                               | lpu              | G <sub>OUT</sub> /U <sub>OUT</sub> output buffer gain set input                                                                                                                              |

| 3      | G <sub>INB</sub> /U <sub>INB</sub> | I                | Analog G <sub>INB</sub> or U <sub>INB</sub> signal input                                                                                                                                     |

| 4      | NC                                 | -                | No connection (leave open or connect to ground)                                                                                                                                              |

| 5      | B <sub>INA</sub> /V <sub>INA</sub> | ı                | Analog B <sub>INA</sub> or V <sub>INA</sub> signal input                                                                                                                                     |

| 6      | GSB1                               | lpu              | B <sub>OUT</sub> /V <sub>OUT</sub> output buffer gain set input                                                                                                                              |

| 7      | B <sub>INB</sub> /V <sub>INB</sub> | I                | Analog B <sub>INB</sub> or V <sub>INB</sub> signal input                                                                                                                                     |

| 8      | NC                                 | _                | No connection (leave open or connect to ground)                                                                                                                                              |

| 9      | DISABLE                            | lpd              | Power save function L: Enable H: Disable (Output pins: R <sub>OUT</sub> /Y <sub>OUT</sub> , G <sub>OUT</sub> /U <sub>OUT</sub> , and B <sub>OUT</sub> /V <sub>OUT</sub> are high impedance.) |

| 10     | GND3                               | -                | Analog ground                                                                                                                                                                                |

| 11     | B <sub>OUT</sub> /V <sub>OUT</sub> | 0                | B/V signal output                                                                                                                                                                            |

| 12     | VCC3                               | -                | Analog 5V supply                                                                                                                                                                             |

| 13     | GND2                               | -                | Analog ground                                                                                                                                                                                |

| 14     | G <sub>OUT</sub> /U <sub>OUT</sub> | 0                | G/U signal output                                                                                                                                                                            |

| 15     | VCC2                               | -                | Analog 5V supply                                                                                                                                                                             |

| 16     | GND1                               | -                | Analog ground                                                                                                                                                                                |

| 17     | R <sub>OUT</sub> /Y <sub>OUT</sub> | 0                | R/Y signal output                                                                                                                                                                            |

| 18     | VCC1                               | _                | Analog 5V supply                                                                                                                                                                             |

| 19     | GND4                               | _                | Analog ground                                                                                                                                                                                |

| 20     | RFC                                | _                | LPF (lowpass filter) cutoff frequency setting resistor connection                                                                                                                            |

| 21     | VFC                                | I                | LPF (lowpass filter) cutoff frequency setting voltage input                                                                                                                                  |

| 22     | MUXSEL                             | lpd              | Input select signal L: $\times_{INA}$ pin select H: $\times_{INB}$ pin select                                                                                                                |

| 23     | THROUGH                            | lpd              | Filter mode select pin L: Filter mode H: Filter through mode                                                                                                                                 |

| 24     | VCC4                               | _                | Analog 5V supply                                                                                                                                                                             |

| 25     | R <sub>INA</sub> /Y <sub>INA</sub> | I                | Analog R <sub>INA</sub> or Y <sub>INA</sub> signal input                                                                                                                                     |

| 26     | GSR1                               | lpu              | R <sub>OUT</sub> /Y <sub>OUT</sub> output buffer gain set input                                                                                                                              |

| 27     | R <sub>INB</sub> /Y <sub>INB</sub> | I                | Analog R <sub>INB</sub> or Y <sub>INB</sub> signal input                                                                                                                                     |

| 28     | NC                                 | _                | No connection (leave open or connect to ground)                                                                                                                                              |

$<sup>1.\</sup> l: input\ pin,\ lpd: input\ pin\ with\ pull-down\ resistor,\ lpu: input\ pin\ with\ pull-up\ resistor,\ o: output\ pin$

## **SPECIFICATIONS**

# **Absolute Maximum Ratings**

| Parameter                             | Symbol           | Rating        | Unit |

|---------------------------------------|------------------|---------------|------|

| Supply voltage range                  | V <sub>CC</sub>  | - 0.3 to 7.0  | ٧    |

| Supply voltage deviation <sup>1</sup> | $\Delta V_{CC}$  | ± 0.1         | ٧    |

| Storage temperature range             | T <sub>stg</sub> | - 55 to + 125 | °C   |

| Power dissipation 1 <sup>2</sup>      | P <sub>D1</sub>  | 1.0           | W    |

| Power dissipation 2 <sup>3</sup>      | P <sub>D2</sub>  | 0.9           | W    |

| Junction temperature                  | T <sub>j</sub>   | 125           | °C   |

Supply voltage deviation of each power supply pin. Supply the power to VCC1 to VCC4 pin, simultaneously.

# **Recommended Operating Conditions**

| Parameter                     | Symbol          | Rating     | Unit |

|-------------------------------|-----------------|------------|------|

| Supply voltage range          | V <sub>CC</sub> | 4.5 to 5.5 | V    |

| Operating ambient temperature | Ta              | – 25 to 85 | °C   |

<sup>2.</sup> When mounted on a substrate: mounted on a 111  $\times$  80  $\times$  1.6mm glass-epoxy substrate with 90% copper (Cu) wiring factor, 0m/s air flow,  $\theta$ jc = 52°C/W, and Ta = - 25 to 70 °C.

When mounted on a substrate: mounted on a 111 × 80 × 1.6mm glass-epoxy substrate with 90% copper (Cu) wiring factor, 0m/s air flow, θjc = 52°C/W, and Ta = 70 to 80 °C.

# **Electrical Characteristics**

# **Input and Output Characteristics**

$V_{CC}$  = 4.5 to 5.5V, Ta = -25 to 85°C unless otherwise noted. Refer to "Measurement Circuit".

| Dawawatan                                | Comple al          | O a maliai a m                                                                                                                                                                                                                 | Rating                |     |       | I I mile | Test  |

|------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-------|----------|-------|

| Parameter                                | Symbol             | Condition                                                                                                                                                                                                                      | min                   | typ | max   | Unit     | level |

| Supply current 1                         | I <sub>CC1</sub>   | $V_{CC} = 5.5$ V, RFC = 820 $\Omega$ to GND, VFC = 0.2V, DISABLE = "L"                                                                                                                                                         | 70                    | 100 | 130   | mA       | I     |

| Supply current 2                         | I <sub>CC2</sub>   | $V_{CC} = 5.5$ V, RFC = 820 $\Omega$ to GND, VFC = 1.6V, DISABLE = "L"                                                                                                                                                         | 90                    | 120 | 160   | mA       | I     |

| Supply current 3                         | I <sub>CC3</sub>   | $V_{CC} = 5.5$ V, RFC = 820 $\Omega$ to GND, VFC = 0.2V, DISABLE = "H"                                                                                                                                                         | 1                     | 2.5 | 5     | mA       | I     |

| Output gain error 1                      | $\Delta A_{V1}$    | Gain = 0dB/6dB,<br>V <sub>CC</sub> = 4.75 to 5.25V, Ta = 0 to 70°C                                                                                                                                                             | -                     | -   | ± 0.5 | dB       | I     |

| Output gain error 2                      | $\Delta A_{V2}$    | Gain = 0dB/6dB, Ta = - 25 to 85°C                                                                                                                                                                                              | -                     | -   | ±1    | dB       | Ι     |

| Maximum output voltage                   | V <sub>out</sub>   | $RL = 75\Omega$ to GND, $Gain = 6dB$                                                                                                                                                                                           | 2.4                   | -   | -     | Vp-p     | I     |

| DISABLE-mode input impedance (pull-down) | R <sub>IN1</sub>   | R <sub>INA</sub> /Y <sub>INA</sub> , R <sub>INB</sub> /Y <sub>INB</sub> , G <sub>INA</sub> /U <sub>INA</sub> ,<br>G <sub>INB</sub> /U <sub>INB</sub> , B <sub>INA</sub> /V <sub>INA</sub> , B <sub>INB</sub> /V <sub>INB</sub> | 40                    | 50  | 60    | kΩ       | I     |

| Clamp response time                      | T <sub>clamp</sub> | Time for 90% output signal change for 10mV input signal, $C_{\text{IN}} = 0.1 \mu \text{F}$                                                                                                                                    | -                     | 8   | -     | ms       | II    |

| Maximum input amplitude                  | VI                 | AC coupling input, Gain = 6dB                                                                                                                                                                                                  | -                     | -   | 1.4   | Vp-p     | 1     |

| Maximum overshoot                        | V <sub>OS</sub>    | 2Vp-p pulse output                                                                                                                                                                                                             | -                     | 10  | -     | %        | Ш     |

| Maximum load capacitance                 | C <sub>L</sub>     | B <sub>OUT</sub> /V <sub>OUT</sub> , G <sub>OUT</sub> /U <sub>OUT</sub> , R <sub>OUT</sub> /Y <sub>OUT</sub>                                                                                                                   | -                     | -   | 15    | pF       | II    |

| Output drive load                        | RL                 | one load unit = $150\Omega$                                                                                                                                                                                                    | -                     | -   | 2     | load     | I     |

| Channel-to-channel gain difference       | dG                 | Between R/G/B, fc/2 [Hz]                                                                                                                                                                                                       | -                     | -   | 0.5   | dB       | I     |

| Channel-to-channel phase difference      | dφ                 | Between R/G/B, fc/2 [Hz]                                                                                                                                                                                                       | -                     | 3.5 | -     | degree   | II    |

| Output harmonic distortion               | T <sub>HD</sub>    | Vout = 2Vp-p, f = 1MHz                                                                                                                                                                                                         | -                     | 1.5 | -     | %        | Ш     |

| Power supply rejection ratio             | PSRR               | V <sub>CC</sub> = 0.5Vp-p, f = 100kHz                                                                                                                                                                                          | -                     | 35  | -     | dB       | II    |

| Output short-circuit current             | I <sub>SC</sub>    |                                                                                                                                                                                                                                | -                     | -   | 100   | mA       | Ш     |

| Logic HIGH-level input voltage 1         | V <sub>IH1</sub>   | DISABLE, MUXSEL, THROUGH                                                                                                                                                                                                       | 2.5                   | -   | -     | ٧        | 1     |

| Logic LOW-level input voltage 1          | V <sub>IL1</sub>   | DISABLE, MUXSEL, THROUGH                                                                                                                                                                                                       | -                     | -   | 1.0   | ٧        | I     |

| Logic HIGH-level input voltage 2         | V <sub>IH2</sub>   | GSB1, GSG1, GSR1                                                                                                                                                                                                               | V <sub>CC</sub> - 0.5 | -   | -     | ٧        | 1     |

| Logic LOW-level input voltage 2          | V <sub>IL2</sub>   | GSB1, GSG1, GSR1                                                                                                                                                                                                               | -                     | -   | 0.5   | ٧        | I     |

| Logic pull-up resistance                 | R <sub>IN2</sub>   | GSB1, GSG1, GSR1                                                                                                                                                                                                               | 32                    | 40  | 48    | kΩ       | I     |

| Logic pull-down resistance               | R <sub>IN3</sub>   | DISABLE, MUXSEL, THROUGH                                                                                                                                                                                                       | 40                    | 50  | 60    | kΩ       | - 1   |

### **Filter Mode Characteristics**

$V_{CC}$  = 4.5 to 5.5V, Ta = -25 to 85°C, THROUGH = Low,  $V_{I}$  = 0.7Vp-p unless otherwise noted. Refer to "Measurement Circuit".

| Davamatav                         | Complete          | Condition                                  |                              |            | Rating      |      | 11-4 | Test  |    |

|-----------------------------------|-------------------|--------------------------------------------|------------------------------|------------|-------------|------|------|-------|----|

| Parameter                         | Symbol            |                                            |                              |            | typ         | max  | Unit | level |    |

| Cutoff frequency adjustment range | F <sub>C</sub>    | Ta=25°C (see Figure 1–1)                   |                              | 5.8        | -           | 37   | MHz  | I     |    |

| Cutoff frequency error            | $\Delta F_{C}$    | Ta = 25°C, V <sub>CC</sub> = 5             | .0V                          | _          | -           | ± 20 | %    | I     |    |

| 4fc attenuation                   | f <sub>SB</sub>   | fIN ≥ 4fc                                  |                              | _          | 50          | -    | dB   | II    |    |

| Crosstalk                         | X <sub>TALK</sub> | Between 2 channels with input 0.5Vp-p 1MHz |                              | -          | <b>- 47</b> | -    | dB   | II    |    |

| Multiplexer crosstalk             | X <sub>TALK</sub> | Between MUX A–B with input 0.5Vp-p 1MHz    |                              | -          | <b>- 49</b> | -    | dB   | II    |    |

| Channel-to-channel group delay    | T <sub>PD</sub>   | Each input = 500kHz                        |                              | _          | 10          | -    | ns   | II    |    |

|                                   | ΔТ                | AT                                         | $\Delta T_{PD1}$ Fc = 6.7MHz | to 3.58MHz | _           | 9    | -    | ns    | II |

|                                   | ΔI <sub>PD1</sub> | (500kHz)                                   | to 4.43MHz                   | -          | 15          | -    | ns   | II    |    |

|                                   |                   |                                            | to 3.58MHz                   | _          | 1           | -    | ns   | II    |    |

| Group delay variation             | $\Delta T_{PD2}$  | Fc = 24MHz<br>(500kHz)                     | to 4.43MHz                   | _          | 1           | -    | ns   | II    |    |

|                                   |                   | (**************************************    | to 10MHz                     | -          | 2           | -    | ns   | II    |    |

|                                   |                   |                                            | - Fc = 36MHz                 | to 10MHz   | _           | 0.5  | -    | ns    | II |

| $\DeltaT_{PD3}$                   | ΔIPD3             | (1MHz) to 30MHz                            | to 30MHz                     | -          | 5           | -    | ns   | II    |    |

| VFC input voltage range           | VFC               | Filter mode, through mode                  |                              | 0.2        | -           | 1.6  | ٧    | I     |    |

## **Through Mode Characteristics**

$V_{CC}$  = 5.0V, Ta = - 25 to 85°C, THROUGH = High,  $V_{I}$  = 0.7Vp-p unless otherwise noted. Refer to "Measurement Circuit".

| Parameter              | Symbol            | Condition                                         | Rating |             |     | Unit  | Test  |

|------------------------|-------------------|---------------------------------------------------|--------|-------------|-----|-------|-------|

| raiametei              | Symbol            | Condition                                         |        | typ         | max | Oilit | level |

| Cutoff frequency (6dB) | F <sub>C</sub>    | Ta=25°C, Gain = 6dB, VFC = 1.6V, RFC=820 $\Omega$ | 42     | 46          | -   | MHz   | I     |

| Cutoff frequency (0dB) | F <sub>C</sub>    | Ta=25°C, Gain = 0dB, VFC = 1.6V, RFC=820 $\Omega$ | 39     | 43          | -   | MHz   | I     |

| Crosstalk              | X <sub>TALK</sub> | Between 2 channels with input 0.5Vp-p 1MHz        | -      | <b>- 60</b> | -   | dB    | II    |

| Multiplexer crosstalk  | X <sub>TALK</sub> | Between MUX A–B with input 0.5Vp-p 1MHz           | -      | <b>- 60</b> | -   | dB    | II    |

#### Test level

I: 100% of products tested at Ta = +25°C.

II: Guaranteed as result of design and characteristics evaluation.

## **Measurement Circuit**

## **FUNCTION DESCRIPTION**

# **Output Buffer Gain Control**

GS×1 pin sets the output buffer gain.

| GSR1, GSG1, GSB1 | Gain [dB] |

|------------------|-----------|

| Low              | 0         |

| High or Open     | 6         |

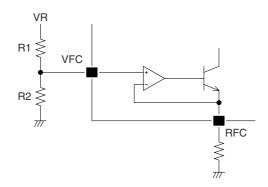

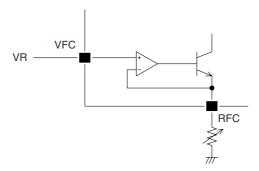

# **Cutoff Frequency Control (RFC and VFC)**

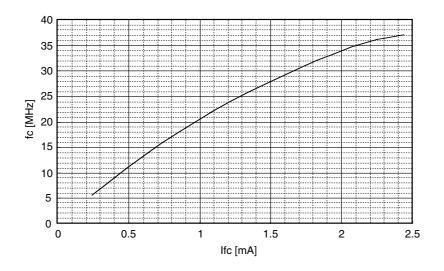

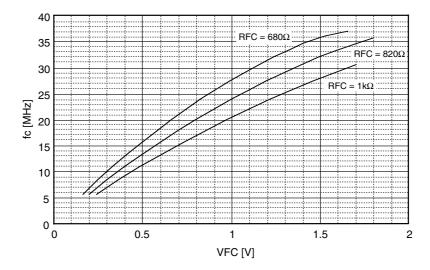

Cutoff frequency (fc) can be controlled by control current Ifc (= VFC/RFC) shown as Figure 1-1. And relation of fc vs VFC at RFC =  $680\Omega$ ,  $820\Omega$ ,  $1k\Omega$  is shown as Figure 1-2.

Figure 1-1. fc vs. Ifc

Figure 1-2. fc vs. VFC

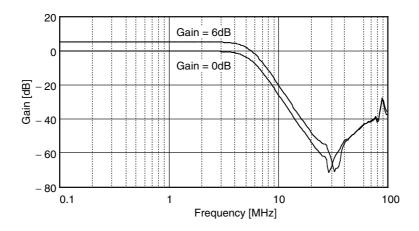

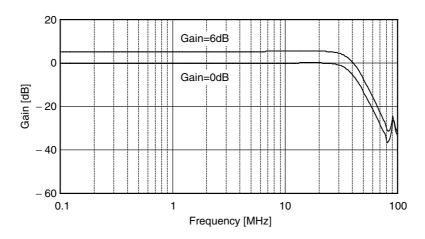

Figure 2-1. Filter characteristic (RFC =  $820\Omega$ , VFC = 0.2V)

Figure 2-2. Filter characteristic (RFC =  $820\Omega$ , VFC = 1.0V)

Figure 2-3. Filter characteristic (RFC =  $820\Omega$ , VFC = 1.6V)

## Filter Through Mode

THROUGH pin sets the through mode. It functions only output buffer, and bypasses the LPF.

| THROUGH     | Filter mode/Through mode |

|-------------|--------------------------|

| Low or Open | Filter mode              |

| High        | Through mode             |

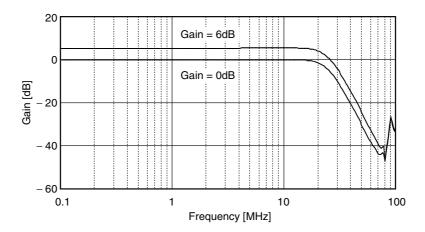

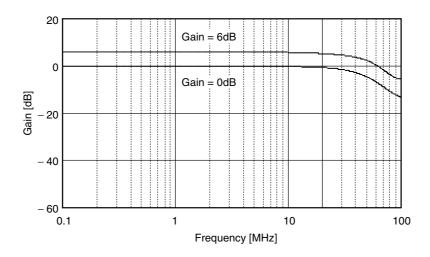

Frequency characteristics of through mode is shown as Figure 3 (VFC = 1.6V, RFC =  $820\Omega$ ).

Figure 3. Through mode frequency characteristic

## **Analog Signal Input**

### **Input Channel Selection**

MUXSEL pin sets the analog input channel  $\times_{INA}$  or  $\times_{INB}$ .

| MUXSEL      | Analog input channel |

|-------------|----------------------|

| Low or Open | × <sub>INA</sub>     |

| High        | × <sub>INB</sub>     |

Selected pins are connected to the internal synctip clamp circuit. Clamp voltage is 2.3V (typ).

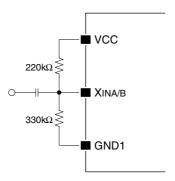

## **BIAS Input**

When input signal is color difference signal of component signal, BIAS input is suitable better than CLAMP input. Connect the resistors as Figure 4, it functions BIAS input.

Figure 4. Resistor connection for BIAS input

# **Adjusting the Cutoff Frequency**

## Constant-voltage control 1

Cutoff frequency control using a reference voltage VR generated by voltage divider formed by R1 and R2.

## Constant-voltage control 2

Cutoff frequency control by adjusting the resistance connected to RFC.

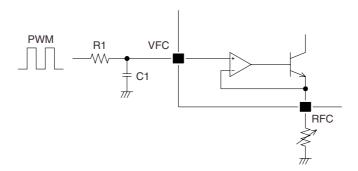

### **PWM control**

Cutoff frequency control by smoothing the PWM signal, using R1 and C1, input to VFC.

When VFC = 0.2V

$$V_{DD}$$

= 3.3V, 6% duty drive  $V_{DD}$  = 5.0V, 4% duty drive

When VFC = 1.6V

$$V_{DD}$$

= 3.3V, 48% duty drive  $V_{DD}$  = 5.0V, 32% duty drive

Note: The resistor connected to RFC can affect the cutoff frequency response, so a high-precision component should be used. It is recommended to set the RC filter cutoff frequency to < 1/100fc of the PWM waveform frequency.

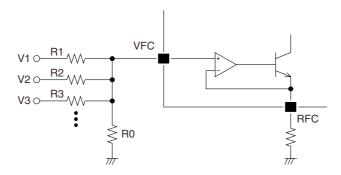

## **Resistor switch control**

The VFC voltage can be controlled using multi-logic voltage levels switching inputs to a voltage divider resistor network.

The VFC voltage is determined by the logic voltage (V1, V2, V3) and the corresponding voltage divider resistor network.

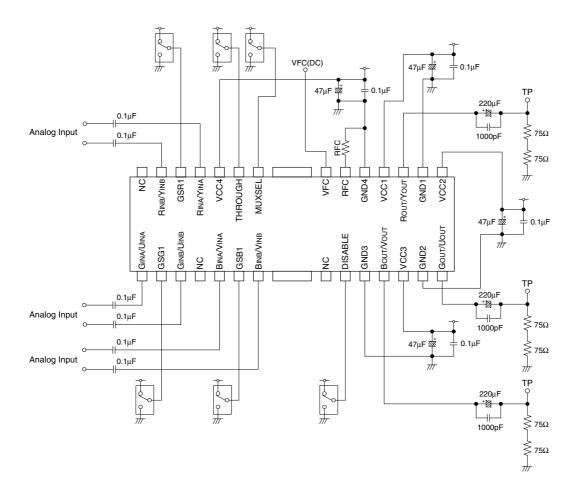

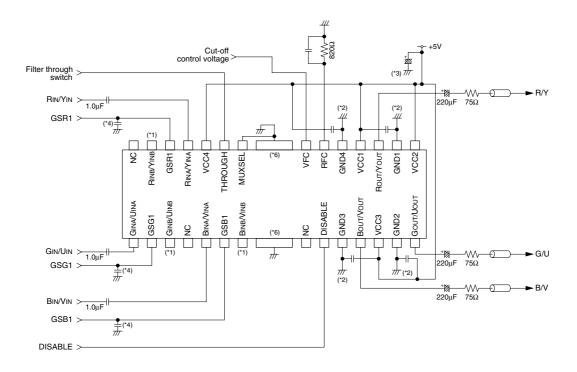

#### TYPICAL APPLICATION CIRCUITS

## **ATSC Digital TV Application**

- (\*1) Pins without an input signal, set by NUXSEL, should be left open or tied to GND.

- (\*2) Connect  $4 \times 0.1 \mu F$  capacitor between the supply pins close to the IC.

- (\*3) Connect a 47µF capacitor between the supply pins close to the IC.

- (\*4) Connect a capacitor if an error occurs due to external noise for GSR1, GSG1, GSB1 pins. Also, if open-circuit, the internal impedance and external capacitance (C) form an RC network. When power is applied, the open-circuit potential rises with time constant  $\tau = C \times 10k$  (sec).

- (\*5) Printed circuit board supply wiring

- If the supply is used for other digital circuits, there is a possibility that noise will be introduced. Accordingly, these circuits should be connected to the application's analog supply.

- Ground-plane wiring should be performed, as much as possible, to provide low GND line impedance.

- If ground-plane wiring up to the GND pins is difficult, the ground plane should be as close to the IC as possible with a separate wire to each GND pin.

- (\*6) The tab (radiation fin) between 7 pin and 8 pin and between 21 pin and 22 pin should be connected to the large ground plane as much as possible for radiation.

## Input Capacitor and High Pass Filter Cutoff Frequency

The capacitor connected to pins  $R_{INA}/Y_{INA}$ ,  $R_{INB}/Y_{INB}$ ,  $G_{INA}/U_{INB}$ ,  $G_{INB}/U_{INB}$ ,  $B_{INA}/V_{INA}$ , and  $B_{INB}/V_{INB}$  forms a highpass filter (HPF) with the internal impedance.

The HPF cutoff frequency is given by the following equation.

$$fc = \frac{1}{2\pi CR}$$

(C: input capacitance, R: signal input impedance =  $9.3k\Omega$  (typ))

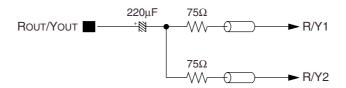

## 2-load Output Connection

$R_{OUT}/Y_{OUT}$  output 2-load connection (similarly for  $G_{OUT}/U_{OUT}$ ,  $B_{OUT}/V_{OUT}$  outputs)

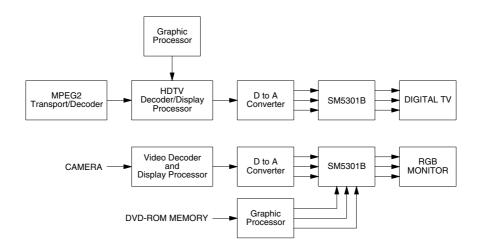

# **Digital TV Receiver and HDTV Decoder Box**

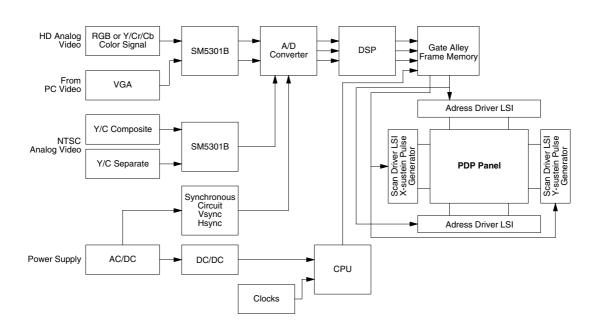

## **Plasma Display Panel**

Please pay your attention to the following points at time of using the products shown in this document.

The products shown in this document (hereinafter "Products") are not intended to be used for the apparatus that exerts harmful influence on human lives due to the defects, failure or malfunction of the Products. Customers are requested to obtain prior written agreement for such use from SEIKO NPC CORPORATION (hereinafter "NPC"). Customers shall be solely responsible for, and indemnify and hold NPC free and harmless from, any and all claims, damages, losses, expenses or lawsuits, due to such use without such agreement. NPC reserves the right to change the specifications of the Products in order to improve the characteristic or reliability thereof. NPC makes no claim or warranty that the contents described in this document dose not infringe any intellectual property right or other similar right owned by third parties. Therefore, NPC shall not be responsible for such problems, even if the use is in accordance with the descriptions provided in this document. Any descriptions including applications, circuits, and the parameters of the Products in this document are for reference to use the Products, and shall not be guaranteed free from defect, inapplicability to the design for the mass-production products without further testing or modification. Customers are requested not to export or re-export, directly or indirectly, the Products to any country or any entity not in compliance with or in violation of the national export administration laws, treaties, orders and regulations. Customers are requested appropriately take steps to obtain required permissions or approvals from appropriate government agencies.

#### SEIKO NPC CORPORATION

15-6, Nihombashi-kabutocho, Chuo-ku, Tokyo 103-0026, Japan Telephone: +81-3-6667-6601 Facsimile: +81-3-6667-6611 http://www.npc.co.jp/ Email: sales@npc.co.jp

NC0208BE 2006.04