www.ti.com

SLAS592C-MARCH 2008-REVISED NOVEMBER 2008

# 24 V, EIGHT-CHANNEL DIGITAL-INPUT SERIALIZER

#### **FEATURES**

- Eight Sensor Inputs

- High Input Voltage up to 30 V

- Selectable Debounce Filters From 0 ms to

- Adjustable Current Limits From 0.2 mA to 5.2 mA

- Field Inputs and Supply Lines Protected to **15-kV HBM**

- **Output Drivers for External Status LEDs**

- Cascadable for More Inputs in Multiples of **Eight**

- **SPI-Compatible Interface**

- Regulated 5-V Output for External Digital Isolator

- Over-Temperature and Low-Supply Voltage Indicator

## **APPLICATIONS**

- Sensor Inputs for Industrial Automation and **Process Control**

- IEC61131-2 Type 1, 2, or 3 Switches

- EN60947-5-2 Proximity Switches

- High Channel Count Digital Input Modules for WWW.DZSC.COM PC and PLC Systems

- Decentralized I/O Modules

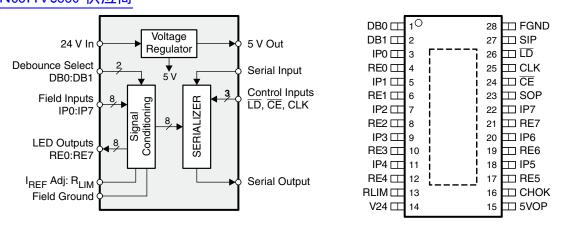

#### DESCRIPTION

The SN65HVS880 is a 24-V, eight-channel, digital-input serializer for high-channel density digital input modules of PC and PLC based systems in industrial automation. In combination with galvanic isolators the device completes the interface between the 24-V sensor outputs of the field-side and the low-voltage controller inputs at the control-side. Input signals provided by EN60947-5-2 compliant 2- and 3-wire proximity switches are current-limited and then validated by internal debounce filters. The input switching characteristic is in accordance with IEC61131-2 for Type 1, 2, and 3 sensor switches.

Upon the application of load and clock signals, input data is latched in parallel into the shift register and afterwards clocked out serially via a subsequent isolator into a serial PLC input.

Cascading of multiple SN65HVS880 is possible by connecting the serial output of the leading device with the serial input of the following device, enabling the design of high-channel count input modules. Input status is indicated via 3-mA constant current LED outputs. An external precision resistor is required to set the internal reference current. The integrated voltage regulator provides a 5-V output to supply low-power isolators. An on-chip temperature sensor together with an internal supply voltage monitor provides a chip-okay (CHOK) indication.

The SN65HVS880 comes in a 28-pin PWP PowerPAD™ package allowing for efficient heat dissipation. The device is specified for operation at temperatures from -40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

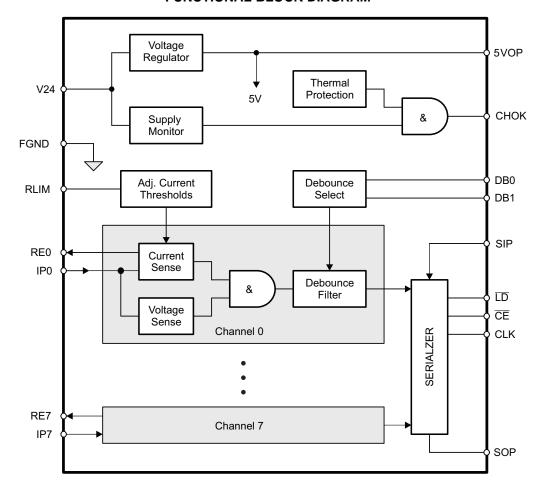

#### **FUNCTIONAL BLOCK DIAGRAM**

**\*\*室特奶**165HV\$880"供应商

## **TERMINAL FUNCTIONS**

| TERM                           | INAL     | DESCRIPTION                              |

|--------------------------------|----------|------------------------------------------|

| PIN NO.                        | NAME     | DESCRIPTION                              |

| 1, 2                           | DB0, DB1 | Debounce select inputs                   |

| 3, 5, 7, 9,<br>11, 18, 20, 22  | IPx      | Input channel x                          |

| 4, 6, 8, 10,<br>12, 17, 19, 21 | REx      | Return path x (LED drive)                |

| 13                             | RLIM     | Current limiting resistor                |

| 14                             | V24      | 24 VDC field supply                      |

| 15                             | 5VOP     | 5 V output to supply low-power isolators |

| 16                             | CHOK     | Chip okay indicator output               |

| 23                             | SOP      | Serial data output                       |

| 24                             | CE       | Clock enable input                       |

| 25                             | CLK      | Serial clock input                       |

| 26                             | LD       | Load pulse input                         |

| 27                             | SIP      | Serial data input                        |

| 28                             | FGND     | Field ground                             |

# SLASSAGC MARCH 2008 OREWISED NOWEMBER 2008 **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)

|                  |                                    |                          |                                                                     | MIN  | MAX  | UNIT |

|------------------|------------------------------------|--------------------------|---------------------------------------------------------------------|------|------|------|

| V24              | Field power input                  |                          | V24                                                                 | -0.3 | 35   | V    |

| $V_{IPx}$        | Field digital inputs               |                          | IPx                                                                 | -0.3 | 35   | V    |

| V <sub>ID</sub>  | Voltage at any logic input         |                          | DB0, DB1, CLK, SIP, $\overline{\text{CE}}$ , $\overline{\text{LD}}$ | -0.5 | 6    | V    |

| lo               | Output current                     |                          | CHOK, SOP                                                           |      | ±8   | mA   |

|                  |                                    | Livean Body Model(1)     | All pins                                                            | ±    |      | kV   |

| V                |                                    | Human-Body Model (1)     | IPx,V24                                                             |      | ±15  | ΚV   |

| $V_{ESD}$        | Electrostatic discharge            | Charged-Device Model (2) | All pins                                                            |      | ±1   | kV   |

|                  |                                    | Machine Model (3)        | All pins                                                            |      | ±100 | V    |

| P <sub>TOT</sub> | Continuous total power dissipation |                          | See Thermal Characteristics table                                   | e    | ·    |      |

| TJ               | Junction temperature               |                          |                                                                     |      | 170  | °C   |

<sup>(1)</sup> JEDEC Standard 22, Method A114-A.

## THERMAL CHARACTERISTICS

|                      | PARAMETER                            | TEST CONDITIONS                                                                                                                                                                                                                            | MIN | TYP  | MAX  | UNIT |

|----------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| $\theta_{JA}$        | Junction-to-air thermal resistance   | High-K thermal resistance                                                                                                                                                                                                                  |     | 35   |      | °C/W |

| $\theta_{JB}$        | Junction-to-board thermal resistance |                                                                                                                                                                                                                                            |     | 15   |      | °C/W |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance  |                                                                                                                                                                                                                                            |     | 4.27 |      | °C/W |

| PD                   | Device power dissipation             | $\begin{split} I_{LOAD} = 50 \text{ mA, } R_{IN} = 0, IPO-IP7 = V24 = 30 \text{ V,} \\ RE7 = FGND, f_{CLK} = 100 \text{ MHz,} \\ I_{IP\text{-}LIM} \text{ and } I_{CC} = \text{worst case with } R_{LIM} = 25 \text{ k}\Omega \end{split}$ |     |      | 2591 | mW   |

## RECOMMENDED OPERATING CONDITIONS

|                  |                                                     | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------------------------------|-----|-----|-----|------|

| V <sub>24</sub>  | Field supply voltage                                | 18  | 24  | 30  | V    |

| V <sub>IPL</sub> | Field input low-state input voltage <sup>(1)</sup>  | 0   |     | 6   | V    |

| V <sub>IPH</sub> | Field input high-state input voltage <sup>(1)</sup> | 10  |     | 30  | V    |

| V <sub>IL</sub>  | Logic low-state input voltage                       | 0   |     | 0.8 | V    |

| V <sub>IH</sub>  | Logic high-state input voltage                      | 2   |     | 5.5 | V    |

| R <sub>LIM</sub> | Current limiter resistor                            | 17  | 25  | 500 | kΩ   |

| f <sub>IP</sub>  | Input data rate <sup>(2)</sup>                      | 0   |     | 1   | Mbps |

| TJ               |                                                     |     |     | 150 | °C   |

| T <sub>A</sub>   |                                                     | -40 |     | 85  | °C   |

<sup>(2)</sup> JEDEC Standard 22, Method C101

JEDEC Standard 22, Method A115-A

<sup>(1)</sup> Field input voltages correspond to an input resistor of  $R_{IN}$  = 1.2 k $\Omega$  (2) Maximum data rate corresponds to 0 ms debounce time, (DB0 = open, DB1 = FGND), and  $R_{IN}$  = 0  $\Omega$

## **ELECTRICAL CHARACTERISTICS**

all voltages measured against FGND unless otherwise stated, see Figure 12

| SYMBOL                     | PARAMETER                                                        | TERMINAL                                  | TEST CONDITIONS                                                                                                                           | MIN  | TYP   | MAX | UNIT |  |

|----------------------------|------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|------|--|

| V <sub>TH-(IP)</sub>       | Low-level device input threshold voltage                         |                                           |                                                                                                                                           | 4    | 4.3   |     | V    |  |

| V <sub>TH+(IP)</sub>       | High-level device input threshold voltage                        | IP0-IP7                                   | 18 V< V24 < 30 V,<br>$R_{IN} = 0 \Omega$                                                                                                  |      | 5.2   | 5.5 | V    |  |

| V <sub>HYS(IP)</sub>       | Device input hysteresis                                          |                                           | 11(N = 0.12                                                                                                                               |      | 0.9   |     | V    |  |

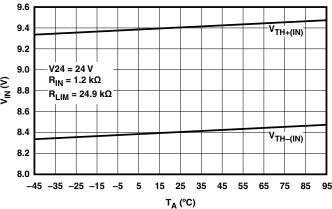

| V <sub>TH-(IN)</sub>       | Low-level field input threshold voltage                          |                                           | 18 V < V24 < 30 V,                                                                                                                        | 6    | 8.4   |     | V    |  |

| V <sub>TH+(IN)</sub>       | High-level field input threshold voltage                         | measured at field side of R <sub>IN</sub> | $R_{IN} = 1.2 \text{ k}\Omega \pm 5\%$                                                                                                    |      | 9.4   | 10  | V    |  |

| V <sub>HYS(IN)</sub>       | Field input hysteresis                                           | noid olde of Tilly                        | $R_{LIM} = 25 \text{ k}\Omega$                                                                                                            |      | 1     |     | V    |  |

| V <sub>TH-(V24)</sub>      | Low-level V24-monitor threshold voltage                          |                                           |                                                                                                                                           | 15   | 16.05 |     | V    |  |

| V <sub>TH+(V24)</sub>      | High-level V24-monitor threshold voltage                         | V24                                       |                                                                                                                                           |      | 16.8  | 18  | V    |  |

| V <sub>HYS(V24)</sub>      | V24-monitor hysteresis                                           |                                           |                                                                                                                                           |      | 0.75  |     | V    |  |

| R <sub>IP</sub>            | Input resistance                                                 | IP0-IP7                                   | $3 \text{ V} < \text{V}_{\text{IPx}} < 6 \text{ V},$ $R_{\text{IN}} = 1.2 \text{ k}\Omega \pm 5\%,$ $R_{\text{LIM}} = 25 \text{ k}\Omega$ | 1.4  | 1.83  | 2.3 | kΩ   |  |

| I <sub>IP-LIM</sub>        | Input current limit                                              |                                           | $10 \text{ V} < \text{V}_{\text{IPx}} < 30 \text{ V},$ $\text{R}_{\text{LIM}} = 25 \text{ k}\Omega$                                       | 3.15 | 3.6   | 4   | mA   |  |

| $V_{OL}$                   | Logic low-level output voltage                                   | SOP, CHOK                                 | $I_{OL} = 20 \mu A$                                                                                                                       |      |       | 0.4 | V    |  |

| $V_{OH}$                   | Logic high-level output voltage                                  | SOF, CHOK                                 | $I_{OH} = -20  \mu A$                                                                                                                     | 4    |       |     | V    |  |

| I <sub>IL</sub>            | Logic input leakage current                                      | DB0, DB1, SIP,<br>LD, CE, CLK             |                                                                                                                                           | -50  |       | 50  | μΑ   |  |

| I <sub>RE-on</sub>         | RE on-state current                                              | RE0-RE7                                   | $R_{LIM} = 25 \text{ k}\Omega,$<br>$RE_X = FGND$                                                                                          | 2.8  | 3.15  | 3.5 | mA   |  |

| I <sub>CC(V24)</sub>       | Supply current                                                   | V24                                       | IP0 to IP7 = V24,<br>5VOP = open,<br>RE <sub>X</sub> = FGND,<br>All logic inputs open                                                     |      |       | 8.7 | mA   |  |

| V <sub>O(5V)</sub>         | Linear regulator output voltage                                  |                                           | 18 V < V24 < 30 V,<br>no load                                                                                                             | 4.5  | 5     | 5.5 | V    |  |

| 10(31)                     |                                                                  | 5VOP                                      | 18 V < V24 < 30 V,<br>I <sub>L</sub> = 50 mA                                                                                              | 4.5  | 5     | 5.5 |      |  |

| I <sub>LIM(5V)</sub>       | Linear regulator output current limit                            |                                           |                                                                                                                                           |      | 115   |     | mA   |  |

| $\Delta V_5/\Delta V_{24}$ | Line regulation                                                  | 5VOP, V24                                 | 18 V < V24 < 30 V,<br>I <sub>L</sub> = 5 mA                                                                                               |      |       | 2   | mV/V |  |

|                            |                                                                  |                                           | DB0 = open,<br>DB1 = FGND                                                                                                                 |      | 0     |     |      |  |

| t <sub>DB</sub>            | Debounce times of input channels                                 | IP0-IP7                                   | DB0 = FGND,<br>DB1 = open                                                                                                                 |      | 1     |     | ms   |  |

|                            |                                                                  |                                           | DB0 = DB1 = open                                                                                                                          | 3    |       |     | 1    |  |

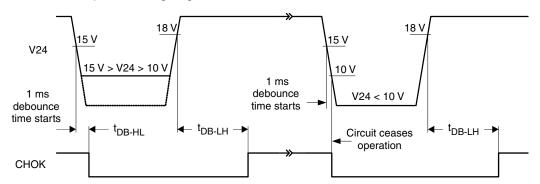

| t <sub>DB-HL</sub>         | Voltage monitor debounce time after V24 < 15 V (CHOK turns low)  | V24 CHOK                                  |                                                                                                                                           |      | 1     |     | ms   |  |

| t <sub>DB-LH</sub>         | Voltage monitor debounce time after V24 > 18 V (CHOK turns high) | V24, CHOK                                 |                                                                                                                                           |      | 6     |     | ms   |  |

| T <sub>OVER</sub>          | Over-temperature indication                                      |                                           |                                                                                                                                           |      | 150   |     | °C   |  |

| T <sub>SHDN</sub>          | Shutdown temperature                                             |                                           |                                                                                                                                           |      | 170   |     | °C   |  |

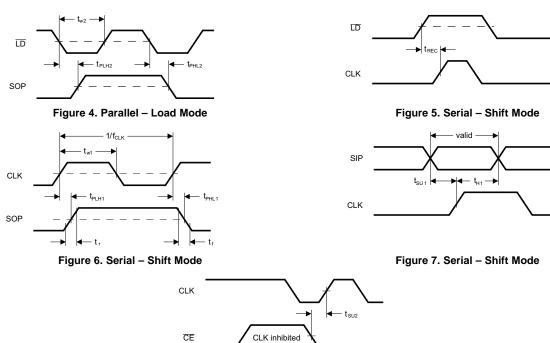

## **TIMING REQUIREMENTS**

over operating free-air temperature range (unless otherwise noted)

| SYMBOL           | PARAMETER                                          | MIN          | TYP | MAX | UNIT |     |

|------------------|----------------------------------------------------|--------------|-----|-----|------|-----|

| t <sub>W1</sub>  | CLK pulse width                                    | See Figure 6 | 4   |     |      | ns  |

| t <sub>W2</sub>  | LD pulse width                                     | See Figure 4 | 6   |     |      | ns  |

| t <sub>SU1</sub> | SIP to CLK setup time                              | See Figure 7 | 4   |     |      | ns  |

| t <sub>H1</sub>  | SIP to CLK hold time                               | See Figure 7 | 2   |     |      | ns  |

| t <sub>SU2</sub> | Falling edge to rising edge (CE to CLK) setup time | See Figure 8 | 4   |     |      | ns  |

| t <sub>REC</sub> | LD to CLK recovery time                            | See Figure 5 | 2   |     |      | ns  |

| f <sub>CLK</sub> | Clock pulse frequency                              | See Figure 6 | DC  |     | 100  | MHz |

## **SWITCHING CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

| SYMBOL                                | PARAMETER           | TEST CONDITIONS                      | MIN | TYP | MAX | UNIT |

|---------------------------------------|---------------------|--------------------------------------|-----|-----|-----|------|

| t <sub>PLH1</sub> , t <sub>PHL1</sub> | CLK to SOP          | C <sub>L</sub> = 15 pF, see Figure 6 |     |     | 10  | ns   |

| t <sub>PLH2</sub> , t <sub>PHL2</sub> | LD to SOP           | C <sub>L</sub> = 15 pF, see Figure 4 |     |     | 14  | ns   |

| t <sub>r</sub> , t <sub>f</sub>       | Rise and fall times | C <sub>L</sub> = 15 pF, see Figure 6 |     |     | 5   | ns   |

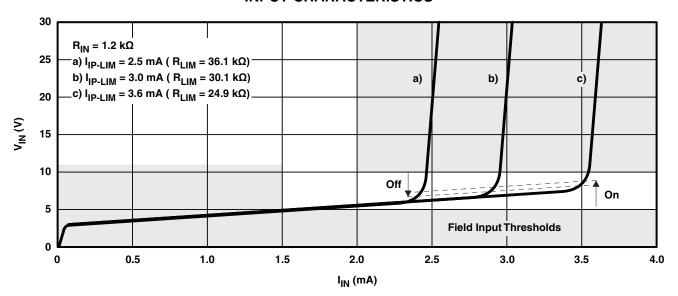

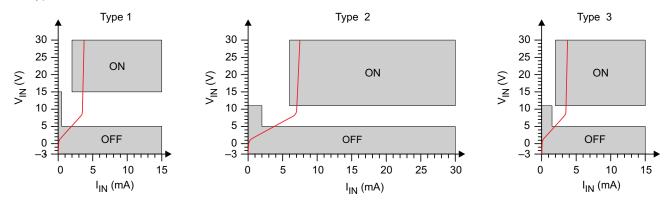

## INPUT CHARACTERISTICS

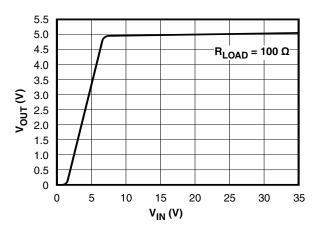

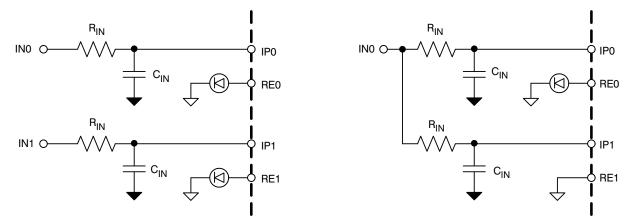

Figure 1. Typical Input Characteristics

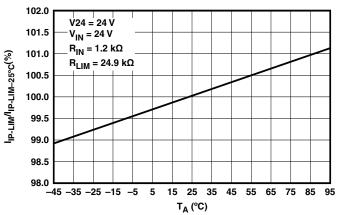

Figure 2. Typical Current Limiter Variation vs Ambient Temperature

Figure 3. Typical Limiter Threshold Voltage Variation vs Ambient Temperature

## PARAMETER MEASUREMENT INFORMATION

## **Waveforms**

For the complete serial interface timing, refer to Figure 21.

Figure 8. Serial - Shift Clock Inhibit Mode

**NSTRUMENTS**

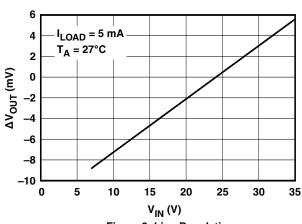

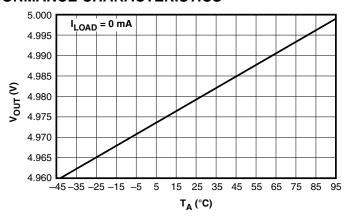

## **VOLTAGE REGULATOR PERFORMANCE CHARACTERISTICS**

Figure 9. Line Regulation

Figure 10. Output Voltage vs Ambient Temperature

Figure 11. Output Voltage vs Input Voltage

## **SIGNAL CONVENTIONS**

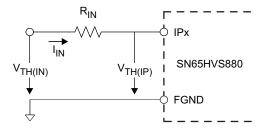

Figure 12. On/Off Threshold Voltage Measurements

Copyright © 2008, Texas Instruments Incorporated

#### **DEVICE INFORMATION**

## **Digital Inputs**

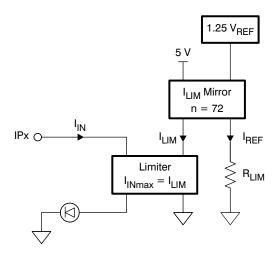

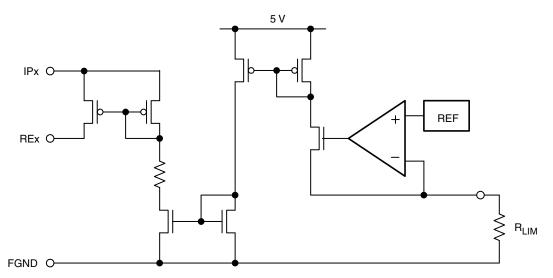

Figure 13. Digital Input Stage

Each digital input operates as a controlled current sink limiting the input current to a maximum value of  $I_{LIM}$ . The current limit is derived from the reference current via  $I_{LIM} = n \times I_{REF}$ , and  $I_{REF}$  is determined by  $I_{REF} = V_{REF}/R_{LIM}$ . Thus, changing the current limit requires the change of  $R_{LIM}$  to a different value via:  $R_{LIM} = n \times V_{REF}/I_{LIM}$ .

Inserting the actual values for n and  $V_{REF}$  gives:  $R_{LIM} = 90 \text{ V} / I_{LIM}$ .

While the device is specified for a current limit of **3.6 mA**, (via  $R_{LIM} = 25 \text{ k}\Omega$ ), it is easy to lower the current limit to further reduce the power consumption. For example, for a current limit of **2.5 mA** simply calculate:

$$R_{LIM} = \frac{90 \text{ V}}{I_{LIM}} = \frac{90 \text{ V}}{2.5 \text{ mA}} = 36 \text{ k}\Omega$$

## **Debounce Filter**

The HVS880 applies a simple analog/digital filtering technique to remove unintended signal transitions due to contact bounce or other mechanical effects. Any new input (either low or high) must be present for the duration of the selected debounce time to be latched into the shift register as a valid state.

The logic signal levels at the control inputs, DB0 and DB1 of the internal Debounce-Select logic determine the different debounce times listed in the following truth table.

**Table 1. Debounce Times**

| DB1  | DB0  | FUNCTION                        |

|------|------|---------------------------------|

| Open | Open | 3 ms delay                      |

| Open | FGND | 1 ms delay                      |

| FGND | Open | 0 ms delay<br>(Filter bypassed) |

| FGND | FGND | Reserved                        |

Figure 14. Equivalent Input Diagram

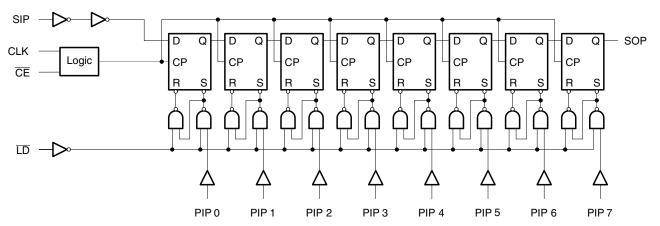

## **Shift Register**

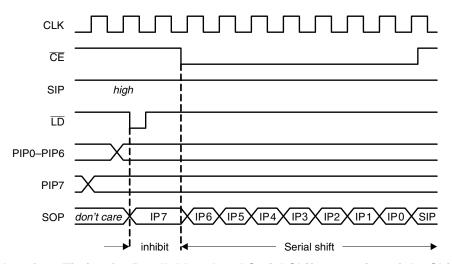

The conversion from parallel input to serial output data is performed by an eight-channel, parallel-in serial-out shift register. Parallel-in access is provided by the internal inputs, PIP0–PIP7, that are enabled by a low level at the load input (LD). When clocked, the latched input data shift towards the serial output (SOP). The shift register also provides a clock-enable function.

Clocking is accomplished by a low-to-high transition of the clock (CLK) input while  $\overline{LD}$  is held high and the clock enable (CE) input is held low. Parallel loading is inhibited when  $\overline{LD}$  is held high. The parallel inputs to the register are enabled while  $\overline{LD}$  is low independently of the levels of the CLK,  $\overline{CE}$ , or serial (SIP) inputs.

Figure 15. Shift Register Logic Structure

**Table 2. Function Table**

|    | INPUTS |    | FUNCTION             |  |  |  |

|----|--------|----|----------------------|--|--|--|

| LD | CLK    | CE | FUNCTION             |  |  |  |

| L  | Х      | Х  | Parallel load        |  |  |  |

| Н  | Х      | Н  | No change            |  |  |  |

| Н  | 1      | L  | Shift <sup>(1)</sup> |  |  |  |

Shift = content of each internal register shifts towards serial outputs.

Data at SIP is shifted into first register.

## **Voltage Regulator**

The on-chip linear voltage regulator provides a 5 V supply to the internal- and external circuitry, such as digital isolators, with an output drive capability of 50 mA and a typical current limit of 115 mA. The regulator accepts input voltages from 30 V down to 10 V. Because the regulator output is intended to supply external digital isolator circuits proper output voltage decoupling is required. For best results connect a 1  $\mu$ F and a 0.1  $\mu$ F ceramic capacitor as close as possible to the 5VOP-output. For longer traces between the SN65HVS880 and isolators of the ISO72xx family use additional 0.1  $\mu$ F and 10 pF capacitors next to the isolator supply pins. Make sure, however, that the total load capacitance does not exceed 4.7  $\mu$ F.

For good stability the voltage regulator requires a minimum load current,  $I_{L-MIN}$ . Ensure that under any operating condition the ratio of the minimum load current in mA to the total load capacitance in  $\mu F$  is larger than 1:

$$\frac{I_{L-MIN}}{C_I} > \frac{1 \text{ mA}}{1 \text{ }\mu\text{F}}$$

## **Supply Voltage Monitor**

The integrated supply voltage monitor senses the supply voltage of the SN65HVS880 at the V24-pin. If this voltage drops below 15 V but stays within the regulator's operating range, i.e., 15 V > V24 > 10 V, the output CHOK goes low 1 ms later. When the supply voltage returns to 24 V, the CHOK output turns logic high after 6 ms. Should the supply voltage drop below 10 V, the device ceases operation. Upon the supply returning to above 18 V, the CHOK output turns high again after 6 ms.

Figure 16. CHOK Output Timing as a Function of Supply Voltage Drop at V24

#### **Temperature Sensor**

An on-chip temperature sensor monitors the device temperature and signals a fault condition if the device becomes too hot. A first trip point exists at 150°C. If the junction temperature exceeds this trip point, the sensor output, being active low, presents a low to the input of the AND gate forcing the CHOK output to go low. If the junction temperature continues to rise, passing a second trip point at 170°C, all device outputs assume tri-state.

SLAS592C-MARCH 2008-REVISED NOVEMBER 2008

## Chip Okay (CHOK) Output

The CHOK output is the Boolean AND-function of the two, active-low fault conditions: temperature failure and supply failure. As such CHOK is a device health indicator, assuming logic high in the absence of any fault condition. If either one of the two or both fault conditions occur, CHOK becomes logic low.

A special condition occurs, however, when the chip temperature exceeds the second temperature trip point due to an output short. Then the CHOK output buffer becomes tri-state, thus separating the buffer from the external circuitry. An internal 100  $k\Omega$  pulldown resistor, connecting the CHOK-pin to ground, is used as a "cooling down" resistor, which continues to provide a logic low level to the external circuitry.

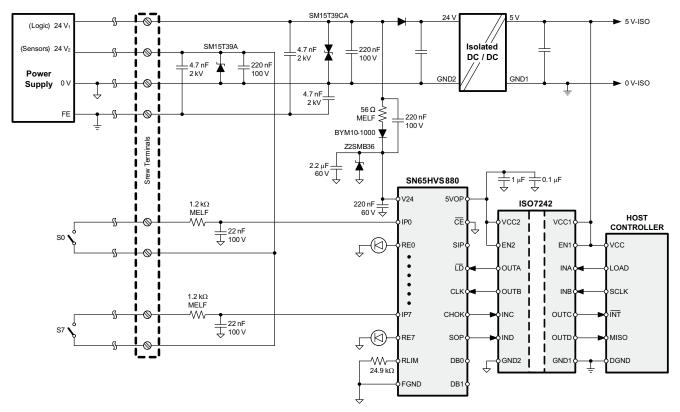

#### **APPLICATION INFORMATION**

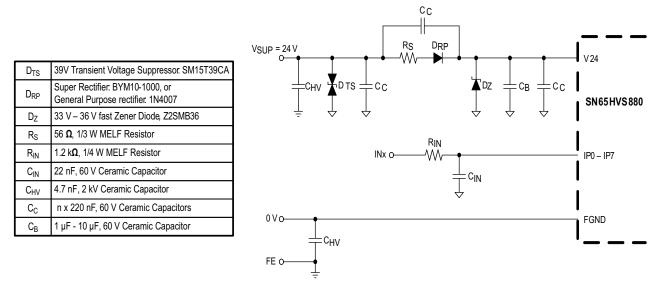

## System-Level EMC

The SN65HVS880 must operate reliably in harsh industrial environments. At a system level, the device is tested according to several international electromagnetic compatibility (EMC) standards.

In addition to the device internal ESD structures, external protection circuitry, such as the one in Figure 17, is needed to absorb as much energy from burst- and surge-transients as possible.

Figure 17. Typical EMC Protection Circuitry for Supply and Signal Inputs

## **Input Channel Switching Characteristics**

The input stage of the HVS880 is so designed, that for an input resistor  $R_{IN} = 1.2 \text{ k}\Omega$  the trip point for signalling an ON-condition is at 9.4 V at 3.6 mA. This trip point satisfies the switching requirements of IEC61131-2 Type 1 and Type 3 switches.

Figure 18. Switching Characteristics for IEC61131-2 Type 1, 2, and 3 Proximity Switches

For a Type 2 switch application, two inputs are connected in parallel. The current limiters then add to a total maximum current of 7.2 mA. While the return-path (RE-pin), of one input might be used to drive an indicator LED, the RE-pin of the other input channel should be connected to ground (FGND).

Paralleling input channels reduces the number of available input channels from an octal Type 1 or Type 3 input to a quad Type 2 input device. Note, that in this configuration output data of an input channel is represented by two shift register bits.

Figure 19. Paralleling Two Type 1 or Type 3 Inputs Into One Type 2 Input

## **Digital Interface Timing**

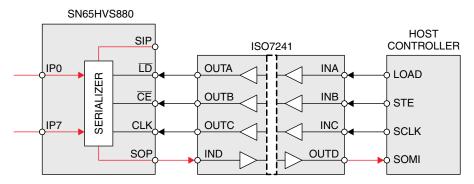

The digital interface of the SN65HVS880 is SPI compatible and interfaces, isolated or non-isolated, to a wide variety of standard micro controllers.

Figure 20. Simple Isolation of the Shift Register Interface

Upon a low-level at the load input,  $\overline{\text{LD}}$ , the information of the field inputs, IP0 to IP7 is latched into the shift register. Taking /LD high again blocks the parallel inputs of the shift register from the field inputs. A low-level at the clock-enable input,  $\overline{\text{CE}}$ , enables the clock signal, CLK, to serially shift the data to the serial output, SOP. Data is clocked at the rising edge of CLK. Thus after eight consecutive clock cycles all field input data have been clocked out of the shift register and the information of the serial input, SIP, appears at the serial output, SOP.

Figure 21. Interface Timing for Parallel-Load and Serial-Shift Operation of the Shift Register

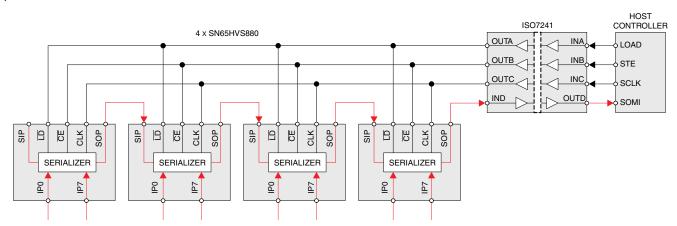

## **Cascading for High Channel Count Input Modules**

Designing high-channel count modules require cascading multiple SN65HVS880 devices. Simply connect the serial output (SOP) of a leading device with the serial input (SIP) of a following device without changing the processor interface.

Figure 22. Cascading Four SN65HVS880 for a 32-Channel Input Module

**\*\*室特奶**165HV\$880"供应商

## **Typical Digital Input Module Application**

Figure 23. Typical Digital Input Module Application

5-Nov-2008

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| SN65HVS880PWP    | ACTIVE                | HTSSOP          | PWP                | 28   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| SN65HVS880PWPG4  | ACTIVE                | HTSSOP          | PWP                | 28   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| SN65HVS880PWPR   | ACTIVE                | HTSSOP          | PWP                | 28   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| SN65HVS880PWPRG4 | ACTIVE                | HTSSOP          | PWP                | 28   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

5-Nov-2008

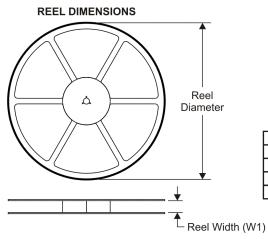

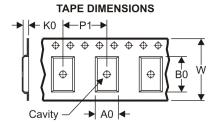

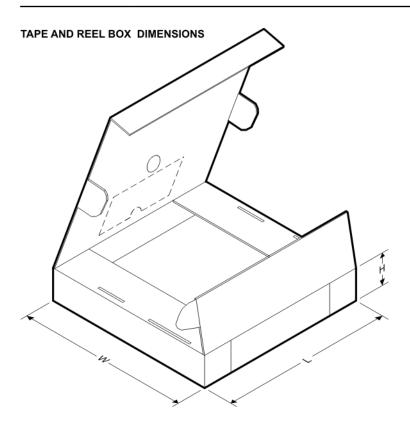

## **TAPE AND REEL INFORMATION**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

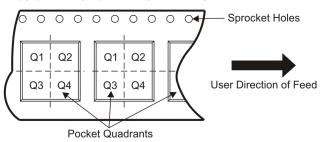

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| SN65HVS880PWPR | HTSSOP          | PWP                | 28 | 2000 | 330.0                    | 16.4                     | 6.9     | 10.2    | 1.8     | 12.0       | 16.0      | Q1               |

#### \*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65HVS880PWPR | HTSSOP       | PWP             | 28   | 2000 | 346.0       | 346.0      | 33.0        |

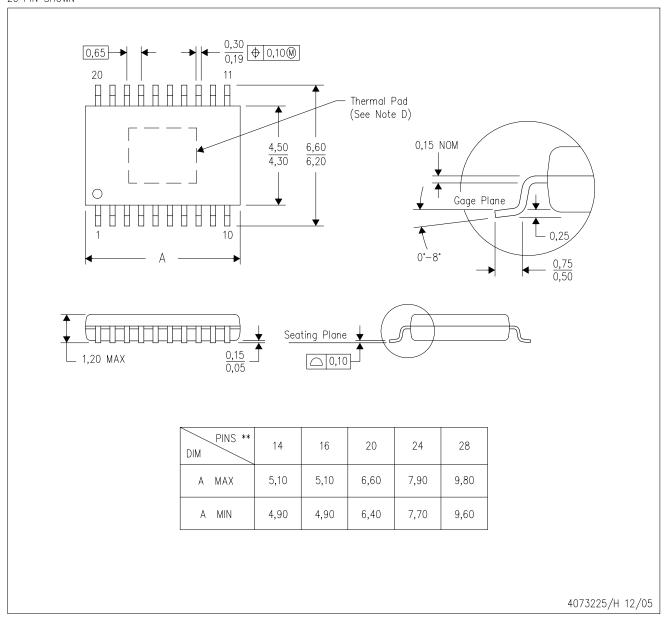

PWP (R-PDSO-G\*\*) PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE 20 PIN SHOWN

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

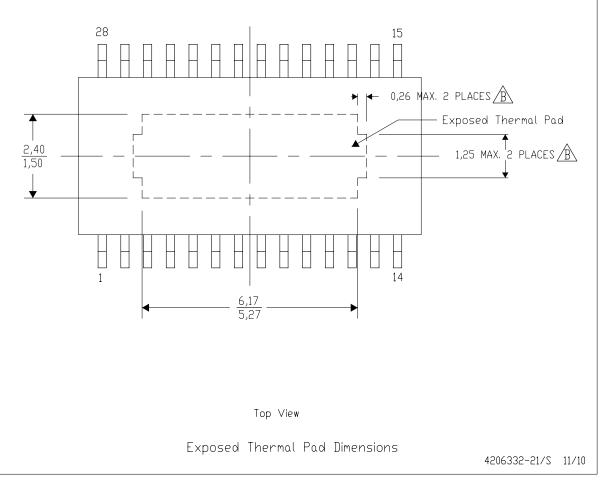

## PWP (R-PDSD-G28)

# PowerPAD™ SMALL PLASTIC DUTLINE

#### THERMAL INFORMATION

This PowerPAD™ package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: A. All linear dimensions are in millimeters

B. Exposed tie strap features may vary in shape or may not be present.

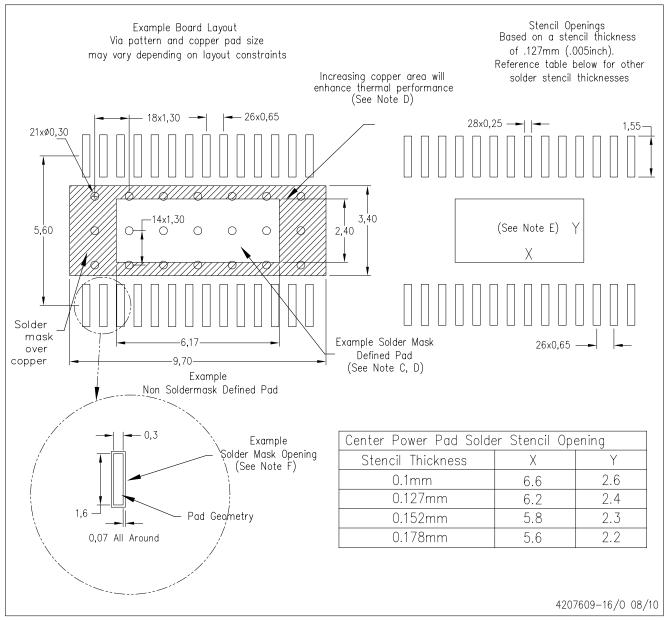

# PWP (R-PDSO-G28)

## PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets.

- E. For specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PowerPAD is a trademark of Texas Instruments.

## 查询"\$N65HV\$880"供应商

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                 |                                   |

|-----------------------------|------------------------|------------------------------|-----------------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio                        | www.ti.com/audio                  |

| Data Converters             | dataconverter.ti.com   | Automotive                   | www.ti.com/automotive             |

| DLP® Products               | www.dlp.com            | Communications and Telecom   | www.ti.com/communications         |

| DSP                         | <u>dsp.ti.com</u>      | Computers and<br>Peripherals | www.ti.com/computers              |

| Clocks and Timers           | www.ti.com/clocks      | Consumer Electronics         | www.ti.com/consumer-apps          |

| Interface                   | interface.ti.com       | Energy                       | www.ti.com/energy                 |

| Logic                       | logic.ti.com           | Industrial                   | www.ti.com/industrial             |

| Power Mgmt                  | <u>power.ti.com</u>    | Medical                      | www.ti.com/medical                |

| Microcontrollers            | microcontroller.ti.com | Security                     | www.ti.com/security               |

| RFID                        | www.ti-rfid.com        | Space, Avionics & Defense    | www.ti.com/space-avionics-defense |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video and Imaging            | www.ti.com/video                  |

|                             |                        | Wireless                     | www.ti.com/wireless-apps          |

|                             |                        |                              |                                   |