HC05C0GRS/D REV 1.2

# 68HC05C0

## SPECIFICATION (General Release)

© October 4, 1995

CSIC System Design Group Austin, Texas

# 查询"HC05C0GRS"供应TABLE OF CONTENTS

| <b>SECTION 1</b>                                                                                                                                           | INTRODUCTION1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                                                                                        | GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.2                                                                                                                                                        | FEATURES1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.3                                                                                                                                                        | MASK OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.4                                                                                                                                                        | SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.4.1                                                                                                                                                      | VDD AND VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.4.2                                                                                                                                                      | IRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.4.3                                                                                                                                                      | OSC1, OSC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.4.4                                                                                                                                                      | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.4.5                                                                                                                                                      | <del>A15</del> ,A14-A8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.4.6                                                                                                                                                      | AD7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.4.7                                                                                                                                                      | AS (ADDRESS STROBE)/ CS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.4.8                                                                                                                                                      | RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.4.9                                                                                                                                                      | <del>WR</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.4.10                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.4.11                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.4.12                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.4.13                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.4.14                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

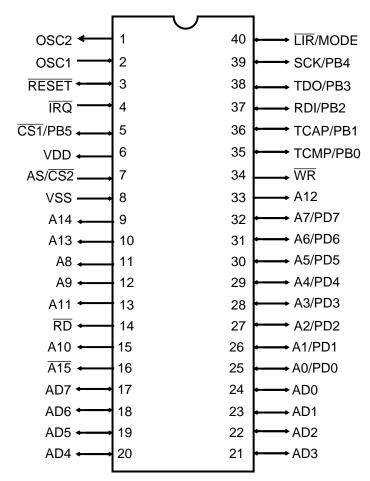

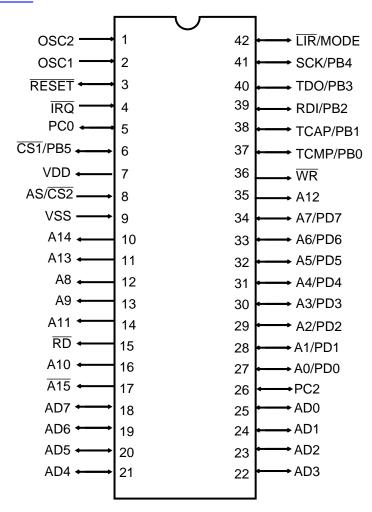

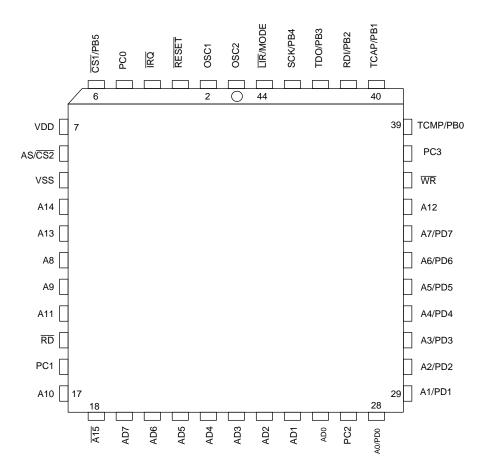

| 1.5                                                                                                                                                        | DEVICE PINOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>SECTION 2</b>                                                                                                                                           | MEMORY9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1                                                                                                                                                        | EXTERNAL MAPPING EXCEPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.1<br>2.2                                                                                                                                                 | EXTERNAL MAPPING EXCEPTIONS 11<br>RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1                                                                                                                                                        | EXTERNAL MAPPING EXCEPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1<br>2.2<br>SECTION 3<br>3.1                                                                                                                             | EXTERNAL MAPPING EXCEPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1                                                                                                                    | EXTERNAL MAPPING EXCEPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1<br>2.2<br>SECTION 3<br>3.1                                                                                                                             | EXTERNAL MAPPING EXCEPTIONS       11         RAM       11 <b>CPU CORE 13</b> REGISTERS       13         ACCUMULATOR (A)       14         INDEX REGISTER (X)       14                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3                                                                                                  | EXTERNAL MAPPING EXCEPTIONS       11         RAM       11 <b>CPU CORE</b> 13         REGISTERS       13         ACCUMULATOR (A)       14         INDEX REGISTER (X)       14         PROGRAM COUNTER (PC)       14                                                                                                                                                                                                                                                                                                                                                     |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2                                                                                                           | EXTERNAL MAPPING EXCEPTIONS11RAM11CPU CORE13REGISTERS13ACCUMULATOR (A)14INDEX REGISTER (X)14PROGRAM COUNTER (PC)14STACK POINTER (SP)14                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3                                                                                                  | EXTERNAL MAPPING EXCEPTIONS11RAM11CPU CORE13REGISTERS13ACCUMULATOR (A)14INDEX REGISTER (X)14PROGRAM COUNTER (PC)14STACK POINTER (SP)14CONDITION CODE REGISTER (CCR)14                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2                                                                         | EXTERNAL MAPPING EXCEPTIONS11RAM11CPU CORE13REGISTERS13ACCUMULATOR (A)14INDEX REGISTER (X)14PROGRAM COUNTER (PC)14STACK POINTER (SP)14CONDITION CODE REGISTER (CCR)14ADDRESSING MODES15                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                                                                | EXTERNAL MAPPING EXCEPTIONS11RAM11CPU CORE13REGISTERS13ACCUMULATOR (A)14INDEX REGISTER (X)14PROGRAM COUNTER (PC)14STACK POINTER (SP)14CONDITION CODE REGISTER (CCR)14ADDRESSING MODES15IMMEDIATE15                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2                                                                         | EXTERNAL MAPPING EXCEPTIONS11RAM11CPU CORE13REGISTERS13ACCUMULATOR (A)14INDEX REGISTER (X)14PROGRAM COUNTER (PC)14STACK POINTER (SP)14CONDITION CODE REGISTER (CCR)14ADDRESSING MODES15                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2<br>3.2.1                                                                | EXTERNAL MAPPING EXCEPTIONS11RAM11CPU CORE13REGISTERS13ACCUMULATOR (A)14INDEX REGISTER (X)14PROGRAM COUNTER (PC)14STACK POINTER (SP)14CONDITION CODE REGISTER (CCR)14ADDRESSING MODES15IMMEDIATE15                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                                     | EXTERNAL MAPPING EXCEPTIONS       11         RAM       11 <b>CPU CORE</b> 13         REGISTERS       13         ACCUMULATOR (A)       14         INDEX REGISTER (X)       14         PROGRAM COUNTER (PC)       14         STACK POINTER (SP)       14         CONDITION CODE REGISTER (CCR)       14         ADDRESSING MODES       15         IMMEDIATE       15         DIRECT       15         RELATIVE       15                                                                                                                                                   |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2<br>3.2.1<br>3.2.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5          | EXTERNAL MAPPING EXCEPTIONS       11         RAM       11 <b>CPU CORE</b> 13         REGISTERS       13         ACCUMULATOR (A)       14         INDEX REGISTER (X)       14         PROGRAM COUNTER (PC)       14         STACK POINTER (SP)       14         CONDITION CODE REGISTER (CCR)       14         ADDRESSING MODES       15         IMMEDIATE       15         DIRECT       15         RELATIVE       15         INDEXED, NO OFFSET       16                                                                                                               |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2<br>3.2.1<br>3.2.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6 | EXTERNAL MAPPING EXCEPTIONS       11         RAM       11 <b>CPU CORE</b> 13         REGISTERS       13         ACCUMULATOR (A)       14         INDEX REGISTER (X)       14         PROGRAM COUNTER (PC)       14         STACK POINTER (SP)       14         CONDITION CODE REGISTER (CCR)       14         ADDRESSING MODES       15         IMMEDIATE       15         DIRECT       15         RELATIVE       15         INDEXED, NO OFFSET       16                                                                                                               |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2<br>3.2.1<br>3.2.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5          | EXTERNAL MAPPING EXCEPTIONS       11         RAM       11 <b>CPU CORE</b> 13         REGISTERS       13         ACCUMULATOR (A)       14         INDEX REGISTER (X)       14         PROGRAM COUNTER (PC)       14         STACK POINTER (SP)       14         CONDITION CODE REGISTER (CCR)       14         ADDRESSING MODES       15         IMMEDIATE       15         DIRECT       15         RELATIVE       15         INDEXED, NO OFFSET       16         INDEXED, 16-BIT OFFSET       16                                                                       |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2<br>3.2.1<br>3.2.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6 | EXTERNAL MAPPING EXCEPTIONS       11         RAM       11 <b>CPU CORE</b> 13         REGISTERS       13         ACCUMULATOR (A)       14         INDEX REGISTER (X)       14         PROGRAM COUNTER (PC)       14         STACK POINTER (SP)       14         CONDITION CODE REGISTER (CCR)       14         ADDRESSING MODES       15         IMMEDIATE       15         DIRECT       15         RELATIVE       15         INDEXED, NO OFFSET       16         INDEXED, 8-BIT OFFSET       16         INDEXED, 16-BIT OFFSET       16         BIT SET/CLEAR       16 |

| 2.1<br>2.2<br>SECTION 3<br>3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7          | EXTERNAL MAPPING EXCEPTIONS       11         RAM       11 <b>CPU CORE</b> 13         REGISTERS       13         ACCUMULATOR (A)       14         INDEX REGISTER (X)       14         PROGRAM COUNTER (PC)       14         STACK POINTER (SP)       14         CONDITION CODE REGISTER (CCR)       14         ADDRESSING MODES       15         IMMEDIATE       15         DIRECT       15         RELATIVE       15         INDEXED, NO OFFSET       16         INDEXED, 16-BIT OFFSET       16                                                                       |

# MC68HC05C0 Specific Firescale Semiconductor, Inc.

| SECTION<br>查询"HC05C0G |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                        | 19                                                                                                       |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                       | 4.1                                                                                                                                                       | HARDWARE CONTROLLED INTERRUPT SEQUENCE                                                                                                                                                                                                                                                                                                                 | 20                                                                                                       |

|                       | 4.2                                                                                                                                                       | SOFTWARE INTERRUPT (SWI)                                                                                                                                                                                                                                                                                                                               |                                                                                                          |

|                       | 4.3                                                                                                                                                       | EXTERNAL INTERRUPT<br>16-BIT TIMER INTERRUPT                                                                                                                                                                                                                                                                                                           |                                                                                                          |

|                       | 4.4<br>4.5                                                                                                                                                | SERIAL COMMUNICATIONS INTERFACE INTERRUPT.                                                                                                                                                                                                                                                                                                             |                                                                                                          |

|                       | 4.6                                                                                                                                                       | MULTI-FUNCTION TIMER INTERRUPTS                                                                                                                                                                                                                                                                                                                        |                                                                                                          |

|                       | 4.7                                                                                                                                                       | KEYBOARD SCAN INTERRUPT                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

| SECTION               | 5                                                                                                                                                         | RESETS                                                                                                                                                                                                                                                                                                                                                 | 23                                                                                                       |

|                       | 5.1                                                                                                                                                       | POWER-ON RESET (POR)                                                                                                                                                                                                                                                                                                                                   | 23                                                                                                       |

|                       | 5.2                                                                                                                                                       | COMPUTER OPERATING PROPERLY (COP) RESET                                                                                                                                                                                                                                                                                                                | 24                                                                                                       |

|                       | 5.3                                                                                                                                                       | LOW-VOLTAGE RESET                                                                                                                                                                                                                                                                                                                                      |                                                                                                          |

|                       | 5.4                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |

|                       | 5.5                                                                                                                                                       | RESET PIN                                                                                                                                                                                                                                                                                                                                              | 24                                                                                                       |

| SECTION               | 6                                                                                                                                                         | LOW-POWER MODES                                                                                                                                                                                                                                                                                                                                        | 25                                                                                                       |

|                       | 6.1                                                                                                                                                       | STOP                                                                                                                                                                                                                                                                                                                                                   |                                                                                                          |

|                       | 6.1.1                                                                                                                                                     | STOP RECOVERY                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |

|                       | 6.2                                                                                                                                                       | WAIT                                                                                                                                                                                                                                                                                                                                                   | 25                                                                                                       |

| SECTION               | 7                                                                                                                                                         | INPUT/OUTPUT PORTS                                                                                                                                                                                                                                                                                                                                     | -                                                                                                        |

|                       | 7.1                                                                                                                                                       | PORT B                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                        |

|                       |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |

|                       | 7.2                                                                                                                                                       | PORT C                                                                                                                                                                                                                                                                                                                                                 |                                                                                                          |

|                       | 7.3                                                                                                                                                       | PORT D                                                                                                                                                                                                                                                                                                                                                 | 29                                                                                                       |

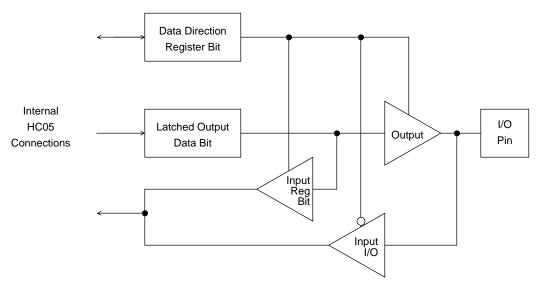

|                       | 7.3<br>7.4                                                                                                                                                | PORT D<br>INPUT/OUTPUT PROGRAMMING                                                                                                                                                                                                                                                                                                                     | 29<br>30                                                                                                 |

| SECTION               | 7.3<br>7.4                                                                                                                                                | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION                                                                                                                                                                                                                                                                                             | 29<br>30<br>. <b> 33</b>                                                                                 |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1                                                                                                                             | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION<br>EXPANDED BUS MODES                                                                                                                                                                                                                                                                       | 29<br>30<br>33                                                                                           |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1                                                                                                                    | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION<br>EXPANDED BUS MODES                                                                                                                                                                                                                                                                       | 29<br>30<br>33<br>33<br>33                                                                               |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2                                                                                                           | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION<br>EXPANDED BUS MODES<br>MUXED MODE<br>NON -MUXED MODE                                                                                                                                                                                                                                      | 29<br>30<br>33<br>33<br>33                                                                               |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2                                                                                                    | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION<br>EXPANDED BUS MODES<br>MUXED MODE<br>NON -MUXED MODE<br>CHIP SELECTS                                                                                                                                                                                                                      | 29<br>30<br>33<br>33<br>33<br>33<br>33                                                                   |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2<br>8.2.1                                                                                           | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION<br>EXPANDED BUS MODES<br>MUXED MODE<br>NON -MUXED MODE<br>CHIP SELECTS<br>PAGE-0 CHIP SELECT TYPE                                                                                                                                                                                           | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>33                                                             |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2                                                                                                    | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION<br>EXPANDED BUS MODES<br>MUXED MODE<br>NON -MUXED MODE<br>CHIP SELECTS                                                                                                                                                                                                                      | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>33<br>34                                                       |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2<br>8.2.1<br>8.2.2                                                                                  | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION<br>EXPANDED BUS MODES<br>MUXED MODE<br>NON -MUXED MODE<br>CHIP SELECTS<br>PAGE-0 CHIP SELECT TYPE<br>GENERAL - PURPOSE CHIP SELECT TYPE                                                                                                                                                     | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>34<br>34                                                       |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3                                                                         | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION                                                                                                                                                                                                                                                                                             | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34                                     |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.3.1<br>8.3.1<br>8.3.2                                              | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION<br>EXPANDED BUS MODES<br>MUXED MODE<br>NON -MUXED MODE<br>CHIP SELECTS<br>PAGE-0 CHIP SELECT TYPE<br>GENERAL - PURPOSE CHIP SELECT TYPE<br>A15 CHIP SELECT<br>CONFIGURATION REGISTER (CNFGR)<br>STPEN - STOP ENable<br>STREC - STOP RECovery                                                | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>34                               |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.3.3<br>8.3.1<br>8.3.2<br>8.3.3                                     | PORT D<br>INPUT/OUTPUT PROGRAMMING<br>SYSTEM CONFIGURATION<br>EXPANDED BUS MODES<br>MUXED MODE<br>NON -MUXED MODE.<br>CHIP SELECTS<br>PAGE-0 CHIP SELECT TYPE<br>GENERAL - PURPOSE CHIP SELECT TYPE<br>A15 CHIP SELECT<br>CONFIGURATION REGISTER (CNFGR)<br>STPEN - STOP ENable<br>STREC - STop RECovery<br>COPEN - Computer Operating Properly ENable | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>34<br>34                         |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4                              | PORT D<br>INPUT/OUTPUT PROGRAMMING                                                                                                                                                                                                                                                                                                                     | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34             |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.3.2<br>8.3.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5          | PORT D<br>INPUT/OUTPUT PROGRAMMING                                                                                                                                                                                                                                                                                                                     | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34 |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.3.2<br>8.3.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5<br>8.3.6 | PORT D<br>INPUT/OUTPUT PROGRAMMING                                                                                                                                                                                                                                                                                                                     | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>35<br>35       |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.3.2<br>8.3.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5          | PORT D<br>INPUT/OUTPUT PROGRAMMING                                                                                                                                                                                                                                                                                                                     | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>35<br>35 |

| SECTION               | 7.3<br>7.4<br><b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5<br>8.3.6<br>8.3.7          | PORT D<br>INPUT/OUTPUT PROGRAMMING                                                                                                                                                                                                                                                                                                                     | 29<br>30<br>33<br>33<br>33<br>33<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>35<br>35<br>35 |

# Freescale Semiconductor Gros Specification Rev. 1.2

| 查询"HC05C0G           |                | KSEN - Keyboard Scan ENable                                                  |     |

|----------------------|----------------|------------------------------------------------------------------------------|-----|

|                      |                | · · · · · · · · · · · · · · · · · · ·                                        |     |

|                      | 8.4.4          | Keyboard Scan Edge/Level                                                     |     |

|                      | 8.4.5          | IRQF - Interrupt ReQuest Flag                                                |     |

|                      | 8.4.6<br>8.4.7 | IRQEN - Interrupt ReQuest ENable                                             |     |

|                      | 8.4.8          | IRQA - Interrupt ReQuest Acknowledge<br>IRQEL - Interrupt ReQuest Edge/Level |     |

|                      | 0.4.0          |                                                                              | 57  |

| SECTION 9            | 9 AI           | DDRESS/DATA BUS INTERFACE                                                    | 39  |

|                      | 9.1            | MODE SELECTION                                                               |     |

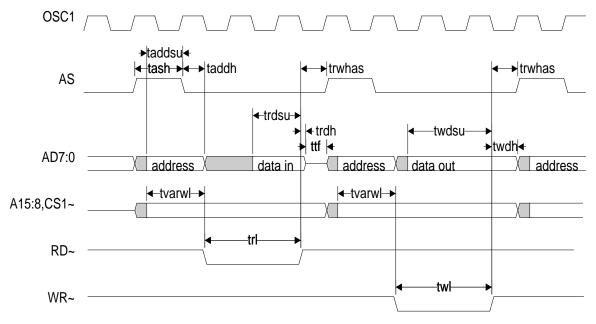

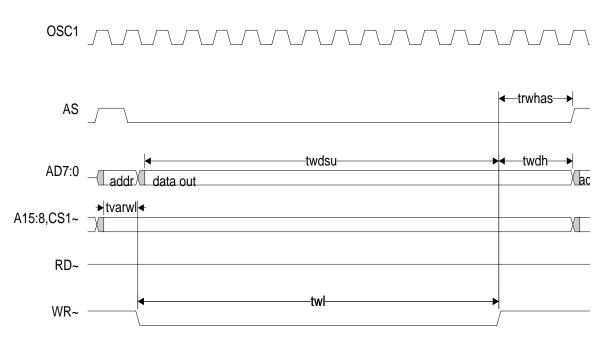

|                      | 9.2            | MUXED MODE BUS TIMING                                                        |     |

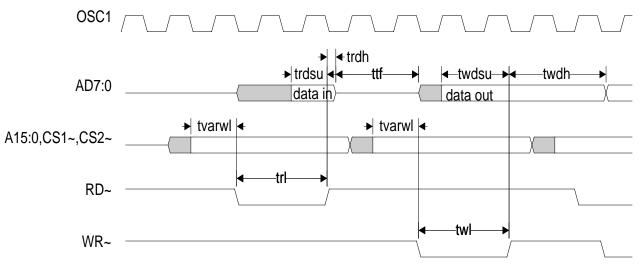

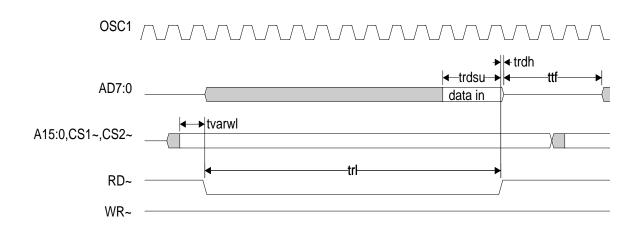

|                      | 9.3            | NON-MUXED MODE BUS TIMING                                                    |     |

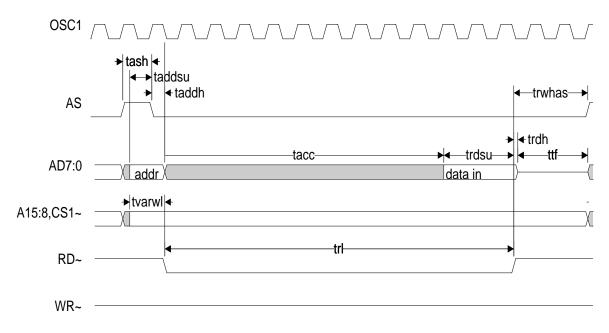

|                      | 9.4            | CLOCK STRETCHED BUS TIMING                                                   |     |

|                      | 9.4.1          | MUXED MODE CLOCK STRETCHED READ CYCLE                                        |     |

|                      | 9.4.2          | MUXED MODE CLOCK STRETCHED WRITE CYCLE                                       | 42  |

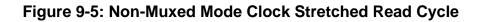

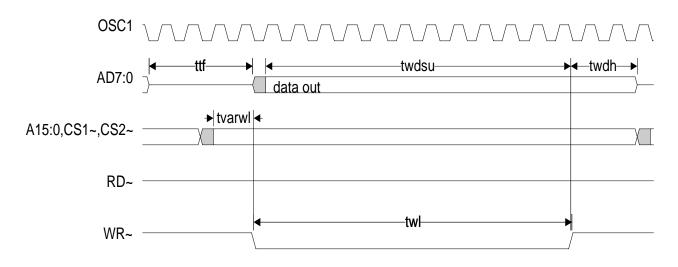

|                      | 9.4.3          | NON-MUXED MODE CLOCK STRETCHED<br>READ CYCLE                                 | 43  |

|                      | 9.4.4          | NON-MUXED MODE CLOCK STRETCHED                                               | -10 |

|                      | 0.1.1          | WRITE CYCLE                                                                  | 43  |

|                      | 9.5            | BUS CYCLE CHARACTERISTICS                                                    | 45  |

|                      | 9.6            | ADDRESS/DATA BUS DURING WAIT AND STOP MODE                                   | 45  |

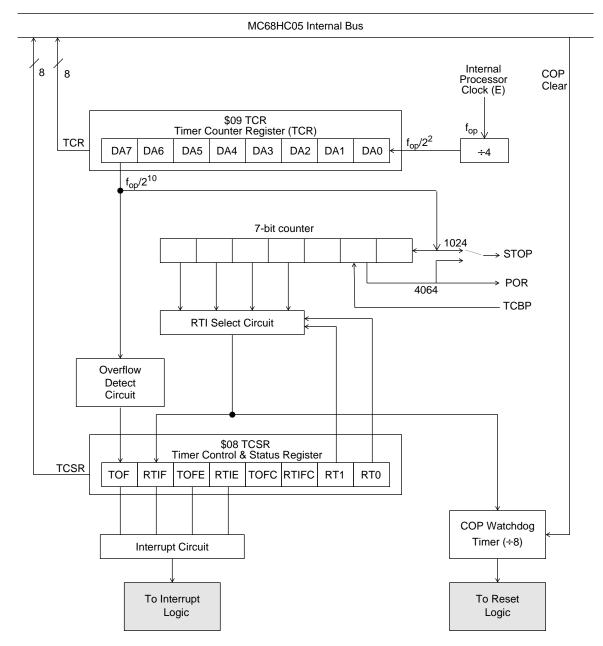

| SECTION <sup>·</sup> | 10 M           | ULTI-FUNCTION TIMER                                                          | 47  |

|                      | 10.1           | INTRODUCTION                                                                 |     |

|                      | 10.2           | TIMER CONTROL AND STATUS REGISTER (TCSR)                                     |     |

|                      | 10.2.1         | TOF - Timer Over Flow                                                        |     |

|                      | 10.2.2         | RTIF - Real Time Interrupt Flag                                              | 48  |

|                      | 10.2.3         | TOFE - Timer Over Flow Enable                                                |     |

|                      | 10.2.4         | RTIE - Real Time Interrupt Enable                                            | 49  |

|                      | 10.2.5         | TOFC - Timer Over Flow Flag Clear                                            |     |

|                      | 10.2.6         | RTIFC - Real Time Interrupt Flag Clear                                       |     |

|                      | 10.2.7         | RT1:RT0 - Real Time Interrupt Rate Select                                    |     |

|                      | 10.3           | TIMER COUNTER REGISTER (TCR)                                                 |     |

|                      | 10.4           | COMPUTER OPERATING PROPERLY (COP) WATCHDOG RESET                             |     |

|                      | 10.5           | TIMER DURING WAIT MODE                                                       |     |

|                      | 10.6           | TIMER DURING STOP MODE                                                       |     |

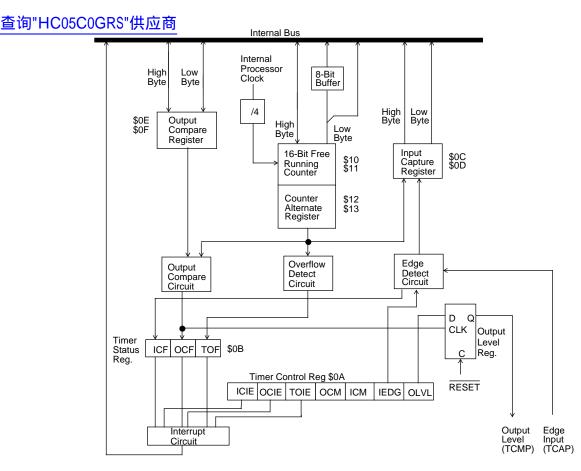

| SECTION <sup>·</sup> | 11 16          | B-BIT TIMER                                                                  | 53  |

| SECTION              | _              |                                                                              |     |

|                      | 11.1<br>11.2   |                                                                              |     |

|                      | 11.2           | COUNTER<br>OUTPUT COMPARE REGISTER                                           |     |

|                      | 11.3           | INPUT CAPTURE REGISTER                                                       |     |

|                      | 11.4           | TIMER CONTROL REGISTER (TCR)                                                 |     |

|                      | 11.6           | TIMER STATUS REGISTER (TSR)                                                  |     |

|                      | 11.7           | TIMER DURING WAIT MODE                                                       |     |

|                      | 11.8           | TIMER DURING STOP MODE                                                       |     |

|                      |                |                                                                              |     |

# MC68HC05C0 Specific Fireescale Semiconductor, Inc.

| SECTION 12<br>查询"HC05C0GR | 2 <u>S</u> E  | RIAL COMMUNICATIONS INTERFACE                       | 61  |

|---------------------------|---------------|-----------------------------------------------------|-----|

|                           | 3 供应商<br>12.1 | OVERVIEW AND FEATURES                               | 61  |

|                           | 12.1.1        | SCI TWO-WIRE SYSTEM FEATURES                        |     |

| 1                         | 12.1.2        | SCI RECEIVER FEATURES                               |     |

| 1                         | 12.1.3        | SCI TRANSMITTER FEATURES                            |     |

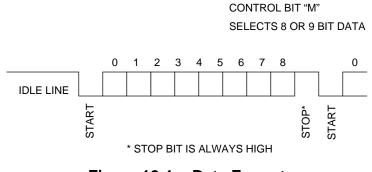

|                           | 12.2          | DATA FORMAT                                         | -   |

| 1                         | 12.3          | FUNCTIONAL DESCRIPTION                              |     |

|                           | 12.4          | RECEIVER                                            | -   |

| 1                         | 12.4.1        | SCI RECEIVER WAKE-UP FEATURE                        |     |

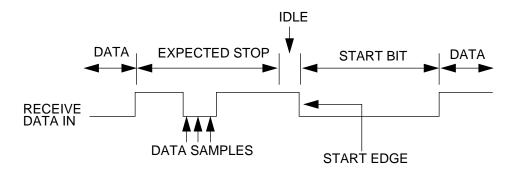

| 1                         | 12.4.1.1      | SCI RECEIVER IDLE WAKE-UP                           | 65  |

|                           | 12.4.1.2      | SCI RECEIVER ADDRESS MARK WAKE-UP                   |     |

|                           | 12.4.2        | RECEIVE DATA IN                                     | 65  |

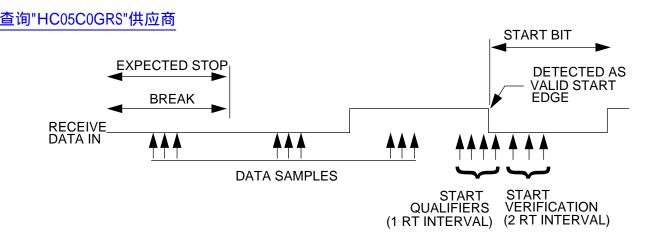

| 1                         | 12.4.3        | START BIT DETECTION FOLLOWING A FRAMING             | ~-  |

|                           |               |                                                     |     |

|                           | 12.5          |                                                     |     |

|                           | 12.5.1        |                                                     |     |

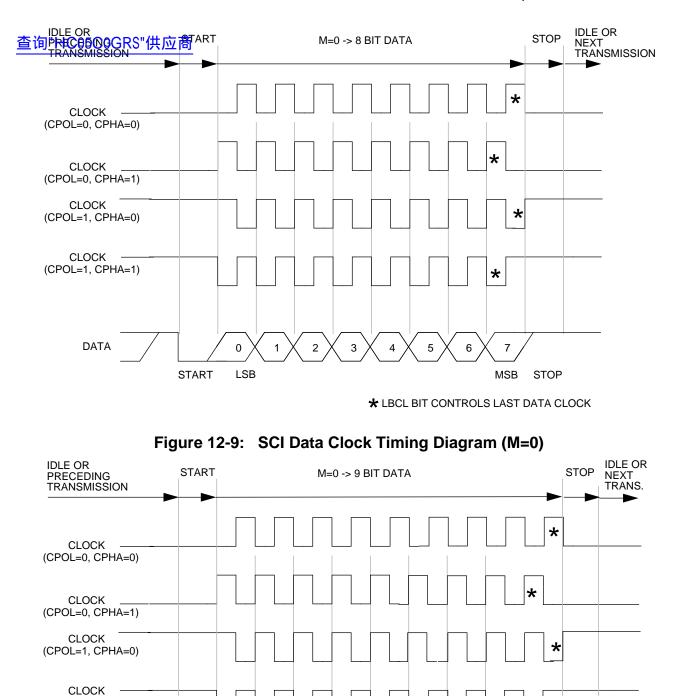

|                           | 12.5.2        | SCI SYNCHRONOUS TRANSMISSION                        |     |

|                           | 12.6          | REGISTERS<br>SERIAL COMMUNICATIONS DATA REGISTER    | 69  |

| 1                         | 12.6.1        | (SCDAT)                                             | 69  |

| 1                         | 12.6.2        | SERIAL COMMUNICATIONS CONTROL REGISTER 1            |     |

|                           |               | (SCCR1)                                             | 69  |

| 1                         | 12.6.3        | SERIAL COMMUNICATIONS CONTROL REGISTER 2<br>(SCCR2) | 74  |

|                           | 12.6.4        | SERIAL COMMUNICATIONS STATUS REGISTER               | • • |

|                           |               | (SCSR)                                              | 76  |

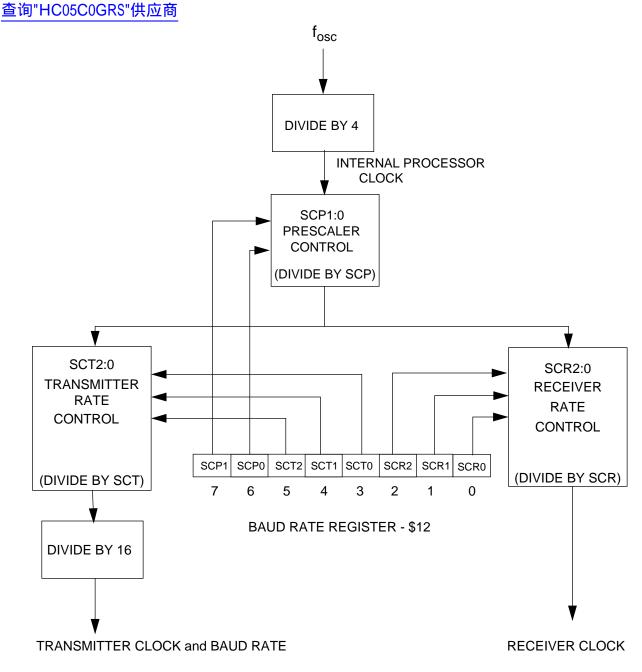

| 1                         | 12.6.5        | BAUD RATE REGISTER                                  | 78  |

| 1                         | 12.7          | SCI DURING WAIT MODE                                | 82  |

| 1                         | 12.8          | SCI DURING STOP MODE                                | 82  |

| SECTION 1                 | 3 EL          | ECTRICALS                                           | 83  |

| 1                         | 13.1          | MAXIMUM RATINGS                                     | 83  |

|                           |               | THERMAL CHARACTERISTICS                             |     |

|                           | 13.3          | DC ELECTRICAL CHARACTERISTICS                       |     |

|                           | 13.4          | CONTROL TIMING                                      | -   |

### 查询"HC05C0GRS"供应商

# LIST OF FIGURES

| Figure 1-1<br>Figure 1-2<br>Figure 1-3<br>Figure 1-4 | Block Diagram of the MC68HC05C0<br>40-Pin DIP Pinout of the MC68HC05C0<br>42-Pin SDIP Pinout of the MC68HC05C0<br>44-Pin PLCC Pinout of the MC68HC05C0 | 5<br>6 |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

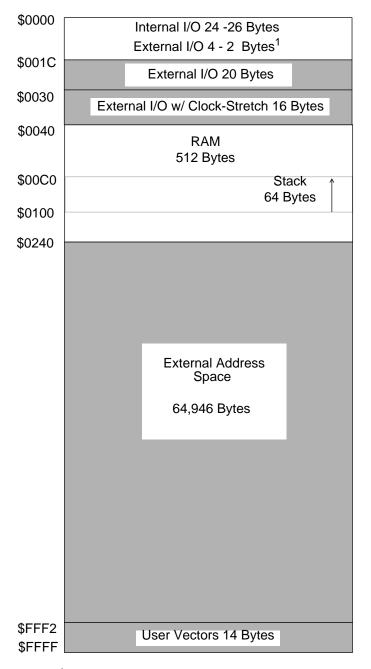

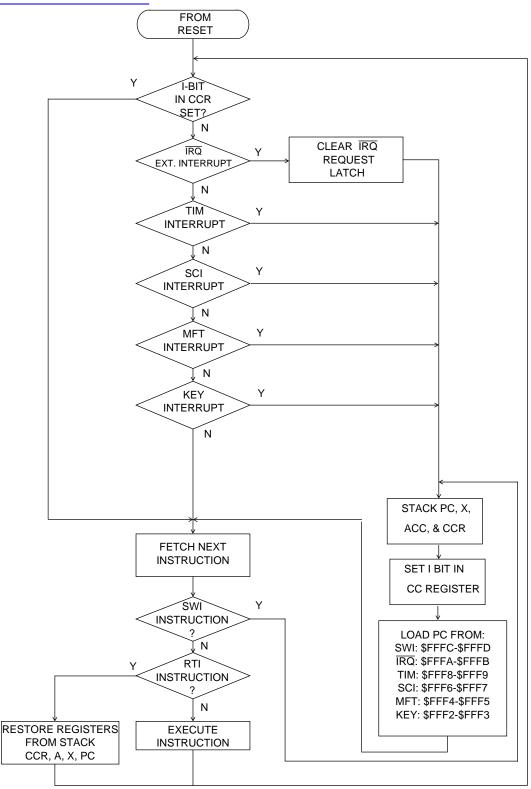

| Figure 2-1<br>Figure 2-2                             | The 64K Memory Map of the MC68HC05C0<br>I/O Registers for the MC68HC05C01                                                                              |        |

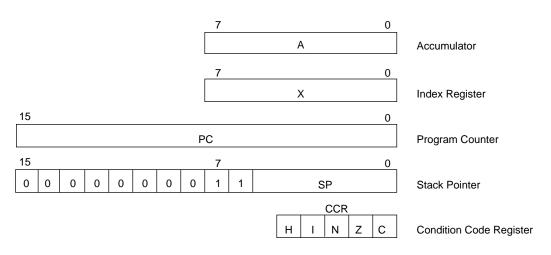

| Figure 3-1<br>Figure 3-2                             | Programming Model1<br>Stacking Order                                                                                                                   |        |

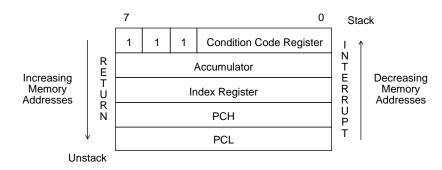

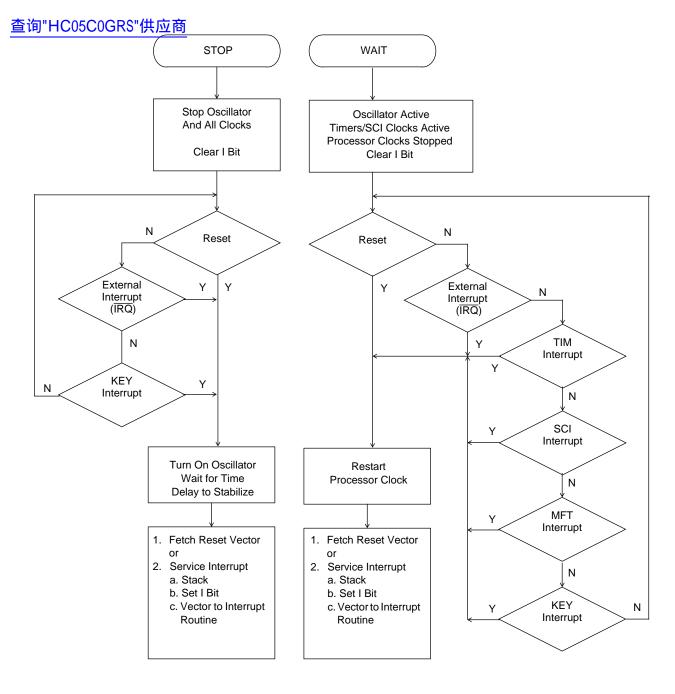

| Figure 4-1                                           | Interrupt Flowchart                                                                                                                                    | 22     |

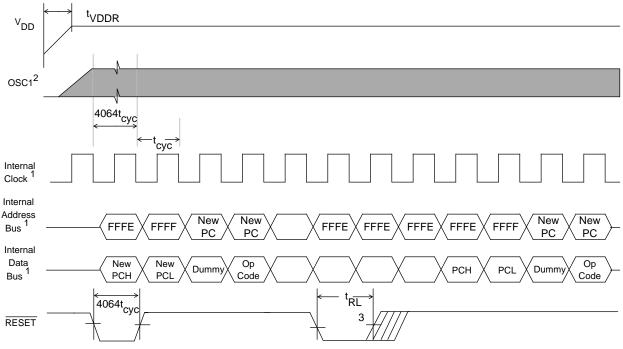

| Figure 5-1                                           | Power-On Reset and RESET2                                                                                                                              | 23     |

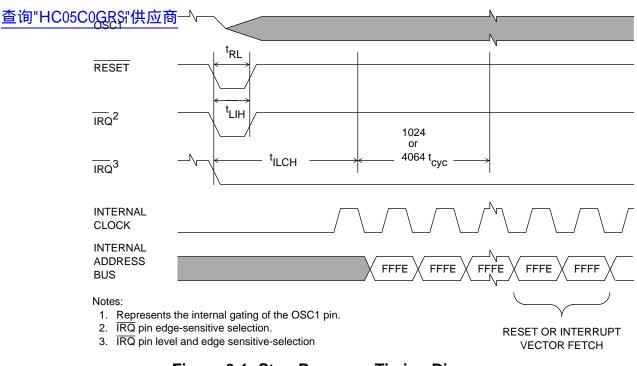

| Figure 6-1<br>Figure 6-2                             | Stop Recovery Timing Diagram                                                                                                                           |        |

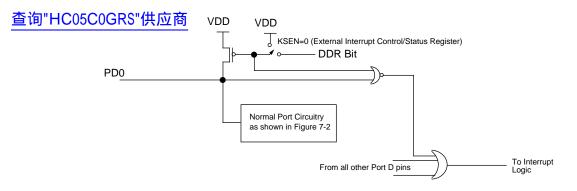

| Figure 7-1<br>Figure 7-2                             | Port D Interrupt Option                                                                                                                                |        |

| Figure 8-1<br>Figure 8-2                             | Configuration Register                                                                                                                                 |        |

| Figure 9-1                                           | Muxed Mode Timing                                                                                                                                      |        |

| Figure 9-2                                           | Non-Muxed Mode Timing                                                                                                                                  |        |

| Figure 9-3                                           | Muxed Mode Clock Stretched Read Cycle                                                                                                                  |        |

| Figure 9-4                                           | Muxed Mode Clock Stretched Write Cycle                                                                                                                 |        |

| Figure 9-5<br>Figure 9-6                             | Non-Muxed Mode Clock Stretched Read Cycle         4           Non-Muxed Mode Clock Stretched Read Cycle         4                                      |        |

| Figure 10-1                                          | Multi-Function Timer Block Diagram                                                                                                                     | 17     |

| Figure 10-2                                          | Timer Control and Status Register (TCSR)                                                                                                               | 18     |

| Figure 10-3                                          | Timer Counter Register                                                                                                                                 |        |

# MC68HC05C0 Specific Fire Scale Semiconductor, Inc.

| 7 | Figure 11-1  | "Timer Block Diagram                                     | 54 |

|---|--------------|----------------------------------------------------------|----|

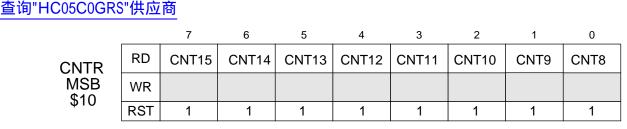

| E | Figure 11-2  | Timer Block Diagram<br>供应商<br>Timer Counter MSB Register | 55 |

|   | Figure 11-3  | Timer Counter LSB Register                               | 55 |

|   | Figure 11-4  | Timer Alternate Counter MSB Register                     | 55 |

|   | Figure 11-5  | Timer Alternate Counter LSB Register                     | 55 |

|   | Figure 11-6  | Timer Output Compare MSB Register                        | 56 |

|   | Figure 11-7  | Timer Output Compare LSB Register                        | 56 |

|   | Figure 11-8  | Timer Input Capture MSB Register                         | 57 |

|   | Figure 11-9  | Timer Input Capture LSB Register                         | 57 |

|   | Figure 11-10 | Timer Control Register                                   | 57 |

|   | Figure 11-11 | Timer Status Register                                    | 59 |

|   |              |                                                          |    |

|   | Figure 12-1  | Data Format                                              | 62 |

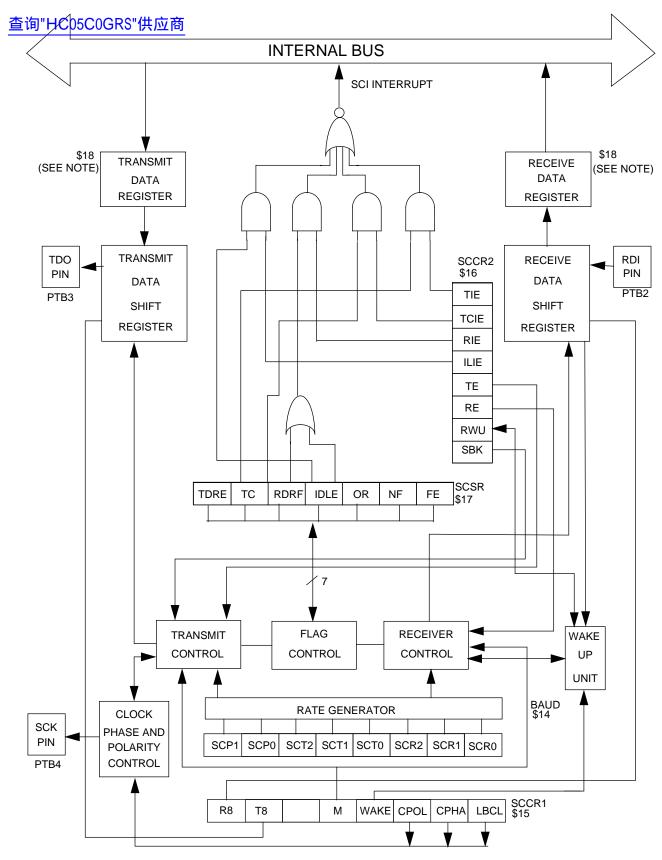

|   | Figure 12-2  | SCI Block Diagram                                        | 64 |

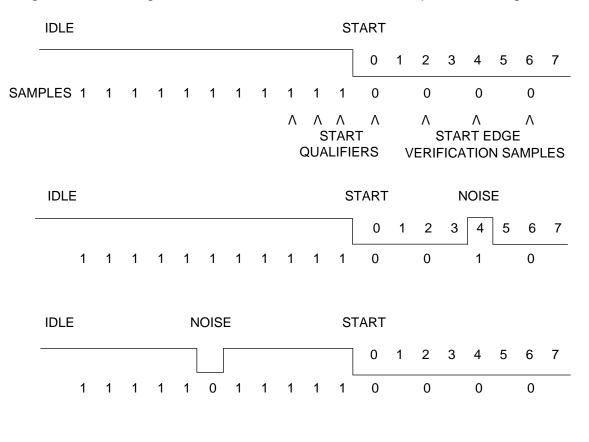

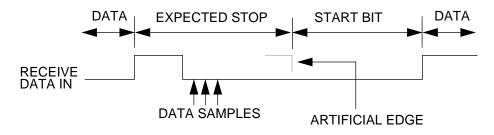

|   | Figure 12-3  | SCI Examples of Start Bit Recognition Technique          | 66 |

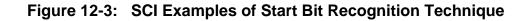

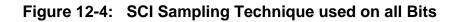

|   | Figure 12-4  | SCI Sampling Technique Used on all Bits                  | 66 |

|   | Figure 12-5  | SCI Artificial Start Following a Framing Error           | 67 |

|   | Figure 12-6  | SCI Start Bit Following a Break                          | 68 |

|   | Figure 12-7  | Serial Communications Data Register                      | 69 |

|   | Figure 12-8  | Serial Communications Control Register                   | 69 |

|   | Figure 12-9  | SCI Data Clock Timing Diagram (M=0)                      | 73 |

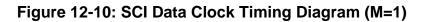

|   | Figure 12-10 | SCI Data Clock Timing Diagram (M=1)                      | 73 |

|   | Figure 12-11 | Serial Communications Control Register 2                 | 74 |

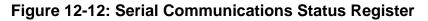

|   | Figure 12-12 | Serial Communications Status Register                    | 76 |

|   | Figure 12-13 | Serial Communications Baud Rate Register                 | 78 |

|   | Figure 12-14 | SCI Rate Generator Block Diagram                         | 81 |

|   |              |                                                          |    |

### 查询"HC05C0GRS"供应商

# LIST OF TABLES

| Table 4-1  | Vector Address for Interrupts and Reset                | 19 |

|------------|--------------------------------------------------------|----|

| Table 7-1  | I/O Pin Functions                                      | 30 |

| Table 8-1  | Chip Select Types                                      | 35 |

| Table 9-1  | Bus Modes                                              |    |

| Table 9-2  | Muxed Mode Timing                                      | 40 |

| Table 9-3  | Non-Muxed Mode Timing                                  | 41 |

| Table 9-4  | Clock Stretched Muxed Mode Timing                      |    |

| Table 9-5  | Clock Stretched Non-Muxed Mode Timing                  |    |

| Table 10-1 | RTI Rates                                              |    |

| Table 10-2 | Minimum COP Reset Times                                | 51 |

| Table 12-1 | Method of Receiver Wake-Up                             | 71 |

| Table 12-2 | SCI Clock on SCK Pin                                   | 72 |

| Table 12-3 | Prescaler Highest Baud Rate Frequency Output           |    |

| Table 12-4 | Transmit Baud Rate Output for a Given Prescaler Output |    |

MC68HC05C0 Specific Firescale Semiconductor, Inc.

查询"HC05C0GRS"供应商

### THIS PAGE INTENTIONALLY LEFT BLANK

# INTRODUCTION

### 1.1 GENERAL

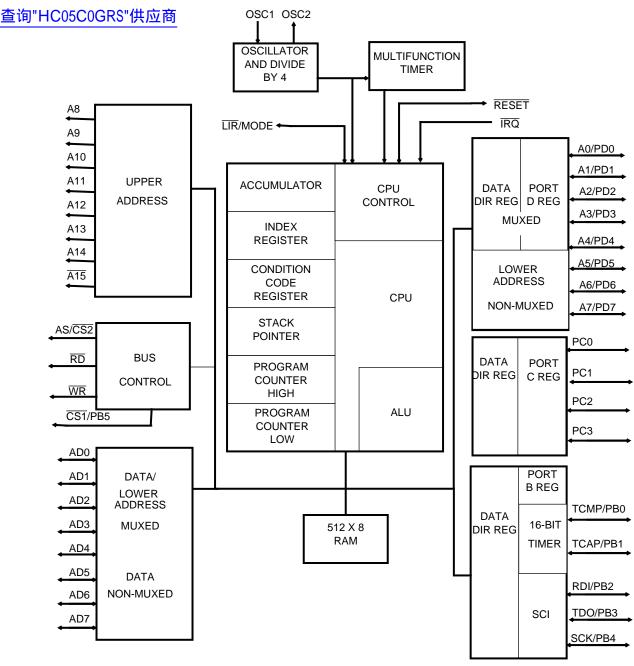

The MC68HC05C0 HCMOS Microcomputer is a member of the M68HC05 Family. This part is suitable for applications which require an external address and data bus. It provides a mode select for either a muxed or a non-muxed bus, and a clock stretching capability for slower peripherals. This 8-bit microcomputer unit (MCU) contains an on-chip oscillator, CPU, RAM, serial and parallel I/O, Multi-Function Timer, 16-Bit Timer, and a Low-Voltage Reset.

### 1.2 FEATURES

- HC05 Core

- 40 Pin PDIP, 42 Pin SDIP, and 44 Pin PLCC Packages

- Mode Select for Lower Byte Address/Data Muxed or Non-Muxed

- 4 MHz CPU Bus Rate for Non-Muxed Mode, 2 MHz for Muxed Mode

- 4 Bus Cycle Clock Stretching for Slow Peripherals

- 512 Bytes of On-Chip RAM

- 16-Bit Timer with Input Capture and Output Compare

- Up to 18 Bidirectional I/O Lines with 44 Pin PLCC Package

- Programmable Interrupt and Pullups on 8 I/O Lines (Keyboard Scan) with Enable, Acknowledge, Request, and Edge or Edge and Level Sensitivity

- External interrupt (IRQ) with Enable, Acknowledge, Request, and Edge or Edge and Level Sensitivity

- Low-Voltage Inhibit to Hold CPU in Reset (LVR)

- Power Saving STOP and WAIT Modes

- Internal Read Visibility and Load Instruction Register Capability for Emulation

- Serial Communications Interface (SCI) with Synchronous Master Transmit Capability

- Up to 3 Chip Selects

- Multi-Function Timer with Selectable Time-out COP Watchdog

- High Current Source and Sink Pin

### MC68HC05C0 Specific Fire Scale Semiconductor, Inc.

Figure 1-1: Block Diagram of the MC68HC05C0

### 1.3 MASK OPTIONS

There are no mask options. Instead a Configuration Register and an External Interrupt Control/Status Register are provided. See Section 8.3 CONFIGURATION REGISTER (CNFGR) for more details.

查预节户<sup>05C</sup>When 带函CU is used in a noisy environment, it is advisable that the Configuration Register be periodically monitored to ensure the integrity of the programmed options.

### 1.4 SIGNAL DESCRIPTION

## 1.4.1 V AND V SS

Power is supplied to the microcontroller using these two pins. VDD is the positive supply and VSS is ground.

### 1.4.2 **IRQ**

This active low input-only pin is the external interrupt. The  $\overline{IRQ}$  pin contains an internal Schmitt trigger as part of its input to improve noise immunity. An External Interrupt Control/Status Register provides a one-time writable (at reset) choice of interrupt triggering sensitivity. This register also provides enable, request and acknowledge bits for the  $\overline{IRQ}$ . See Section 4 INTERRUPTS for more information.

### 1.4.3 OSC1, OSC2

These pins provide control input for an on-chip clock oscillator circuit. A crystal, a ceramic resonator, or an external signal connects to these pins providing a system clock. The oscillator frequency is four times the internal bus rate.

### 1.4.4 **RESET**

This active low bidirectional control pin is used as an input to reset the MCU to a known start-up state. The RESET pin contains an internal Schmitt trigger as part of its input to improve noise immunity. RESET is also an open-drain output to indicate that any of four possible internal reset conditions occurred. See Section 5 RESETS for more information.

### 1.4.5 A15,A14-A8

These eight dedicated lines constitute the upper address byte.  $\overline{A15}$  is active low and divides the memory map into two 32K regions. In this manner,  $\overline{A15}$  can be used as a chip select for program memory without the need of an inverter. See Section 9 ADDRESS/DATA BUS INTERFACE for the timing and a detailed description of the address bus.

### 1.4.6 AD7:0

These eight dedicated lines constitute the lower address or data byte. In Non-Muxed mode, these eight lines become data bits D7-D0. In Muxed mode, address and data are multiplexed together. See Section 9 ADDRESS/DATA BUS INTERFACE for the timing and a detailed description of the address/data bus.

### MC68HC05C0 Specific Fireescale Semiconductor, Inc.

# 1.4.7 AS (ADDRESS STROBE)/ CS2 查询"HC05C0GRS"供应商

In Muxed mode, this pin is the active high Address Strobe, which is used to indicate the presence of the lower address byte on the muxed address/data bus. See Section 9 ADDRESS/DATA BUS INTERFACE for the timing and a detailed description of the address strobe. In Non-Muxed mode, this active low pin becomes an active low chip select. See Section 8 SYSTEM CONFIGURATION for more information on the chip selects.

#### 1.4.8 RD

This active low output pin is used to drive an external peripheral during an external read cycle. It can also indicate an internal read cycle if Internal Read Visibility is selected in the Configuration Register. See Section 9 ADDRESS/DATA BUS INTERFACE for the timing and a detailed description of the RD signal.

#### 1.4.9 WR