## 3G HD/SD SDI Dual Output Low Power Extended Reach Adaptive Cable Equalizer

## **General Description**

The LMH0395 3 Gbps HD/SD SDI Dual Output Low Power Extended Reach Adaptive Cable Equalizer is designed to equalize data transmitted over cable (or any media with similar dispersive loss characteristics). The equalizer operates over a wide range of data rates from 125 Mbps to 2.97 Gbps and supports SMPTE 424M, SMPTE 292M, SMPTE 344M, SMPTE 259M, and DVB-ASI standards.

The LMH0395 provides extended cable reach with ultra low power consumption. The equalizer includes active sensing circuitry that ensures robust performance and enhanced immunity to variations in the input signal launch amplitude. The LMH0395 offers power management to further reduce power consumption when no input signal is present.

The LMH0395 has two differential serial data outputs, increasing flexibility and eliminating the need for a fanout buffer on the output in many applications. The outputs may be independently enabled and controlled. The output drivers offer programmable de-emphasis for up to 40" of FR4 trace losses.

The LMH0395 supports two modes of operation. In pin mode, the LMH0395 operates with control pins to set its operating state. In SPI mode, an optional SPI serial interface can be used to access and configure multiple LMH0395 devices in a daisy-chain configuration. This allows programming the output common mode voltage and swing, output de-emphasis level, input launch amplitude, and power management settings, as well as access to a cable length indicator and all pin mode features.

### Features

- SMPTE 424M, SMPTE 292M, SMPTE 344M, SMPTE 259M, and DVB-ASI compliant

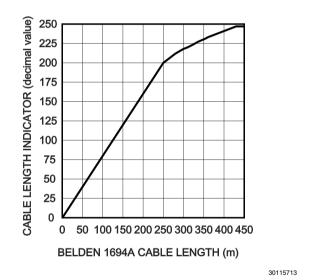

- Equalizes up to 200 meters of Belden 1694A at 2.97 Gbps, up to 220 meters of Belden 1694A at 1.485 Gbps, or up to 400 meters of Belden 1694A at 270 Mbps

- Ultra low power consumption: 140 mW (dual outputs), 115 mW (single output)

- Dual differential outputs; second output can be independently powered down

- Power save mode with auto sleep control (17 mW typical power consumption in power save mode)

- Output de-emphasis to compensate for FR4 board trace losses

- Digital and analog programmable MUTE<sub>REF</sub> threshold control

- Optional SPI register access

- Wide range of data rates: 125 Mbps to 2.97 Gbps

- Internally terminated 100Ω LVDS outputs with programmable output common mode voltage and swing

- Programmable launch amplitude optimization

- Cable length indicator

- Single 2.5V supply operation

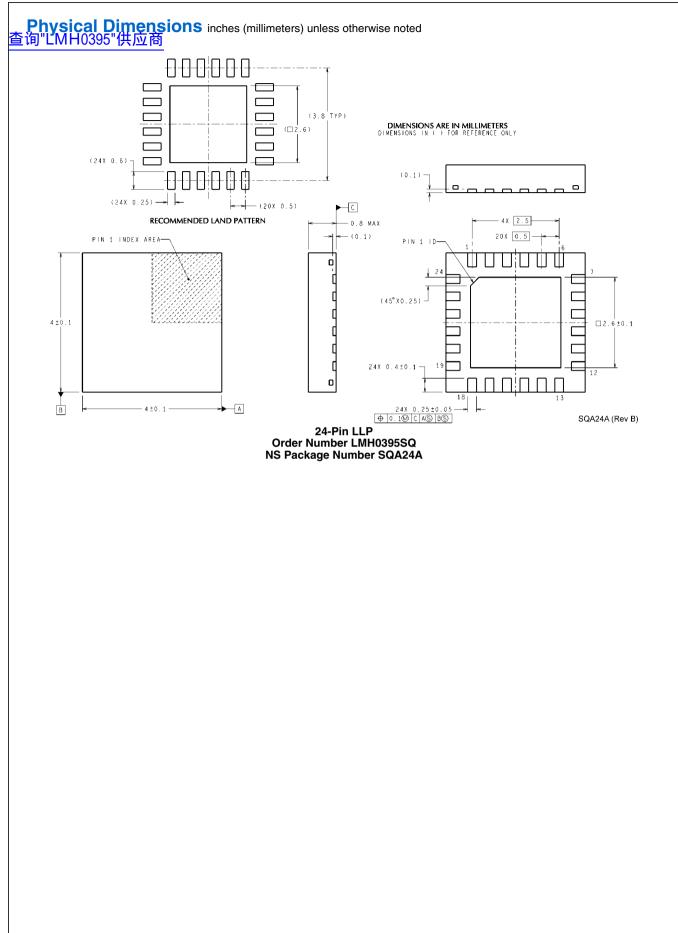

- 24-pin LLP package

- Industrial temperature range: -40°C to +85°C

## **Applications**

- SMPTE 424M, SMPTE 292M, SMPTE 344M, and SMPTE 259M serial digital interfaces

- Broadcast Video routers, switchers, and distribution amplifiers

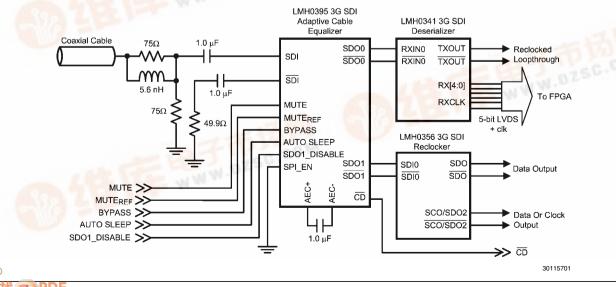

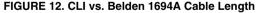

## **Typical Application (Pin Mode)**

df.dzsc.com

#

| Supply Voltage             | 3.1V                           |

|----------------------------|--------------------------------|

| Input Voltage (all inputs) | -0.3V to V <sub>CC</sub> +0.3V |

| Storage Temperature Range  | –65°C to +150°C                |

| Junction Temperature       | +125°C                         |

| Package Thermal Resistance |                                |

| θ <sub>JA</sub> 24-pin LLP | +40°C/W                        |

| θ <sub>JC</sub> 24-pin LLP | +6°C/W                         |

| ESD Rating (HBM)           | ≥±6 kV                         |

| ESD Rating (MM)            | ≥±300V                         |

| ESD Rating (CDM)           | ≥±2 kV                         |

|                            |                                |

## Recommended Operating Conditions

| Supply Voltage (V <sub>CC</sub> – V <sub>EE</sub> ) | 2.5V ±5%       |

|-----------------------------------------------------|----------------|

| Input Coupling Capacitance                          | 1.0 μF         |

| AEC Capacitor (Connected between                    |                |

| AEC+ and AEC-)                                      | 1.0 µF         |

| Operating Free Air Temperature (T <sub>A</sub> )    | -40°C to +85°C |

## **DC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (Note 2, Note 3).

| Symbol             | Parameter                                                                 | Conditions                                        | Reference           | Min      | Тур  | Max             | Units             |

|--------------------|---------------------------------------------------------------------------|---------------------------------------------------|---------------------|----------|------|-----------------|-------------------|

| V <sub>IH</sub>    | Input Voltage High Level                                                  |                                                   | Logic Inputs        | 1.7      |      | V <sub>cc</sub> | V                 |

| V <sub>IL</sub>    | Input Voltage Low Level                                                   |                                                   |                     | $V_{EE}$ |      | 0.7             | V                 |

| $V_{SDI}$          | Input Voltage Swing                                                       | 0m cable length, (Note 5)                         | SDI, <u>SDI</u>     | 720      | 800  | 880             | mV <sub>P-P</sub> |

| V <sub>CMIN</sub>  | Input Common Mode Voltage                                                 |                                                   |                     |          | 1.65 |                 | V                 |

| V <sub>SSP-P</sub> | Differential Output Voltage, P-P                                          | 100 $\Omega$ load, default register               | SDO0, SDO0          | 500      | 700  | 900             | mV <sub>P-P</sub> |

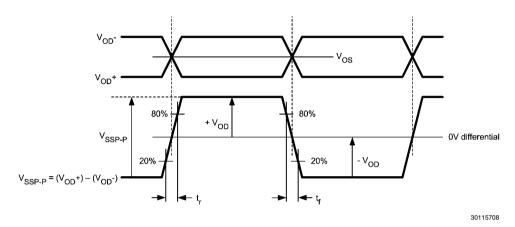

| V <sub>OD</sub>    | Differential Output Voltage                                               | settings ( <i>Note 6</i> ), <i>Figure 1</i>       | SDO1, SDO1          | 250      | 350  | 450             | mV                |

| $\Delta V_{OD}$    | Change in Magnitude of V <sub>OD</sub> for<br>Complimentary Output States |                                                   |                     |          |      | 50              | mV                |

| V <sub>OS</sub>    | Offset Voltage                                                            |                                                   |                     | 1.1      | 1.2  | 1.35            | V                 |

| $\Delta V_{OS}$    | Change in Magnitude of V <sub>OS</sub> for<br>Complimentary Output States |                                                   |                     |          |      | 50              | mV                |

| I <sub>OS</sub>    | Output Short Circuit Current                                              |                                                   |                     |          |      | 30              | mA                |

|                    | MUTE <sub>REF</sub> DC Voltage (floating)                                 |                                                   | MUTE <sub>REF</sub> |          | 1.3  |                 | V                 |

|                    | MUTE <sub>REF</sub> Range                                                 |                                                   |                     |          | 0.8  |                 | V                 |

| V <sub>OH</sub>    | Output Voltage High Level                                                 | I <sub>OH</sub> = -2 mA                           | CD, MISO            | 2.0      |      |                 | V                 |

| V <sub>OL</sub>    | Output Voltage Low Level                                                  | $I_{OL} = +2 \text{ mA}$                          |                     |          |      | 0.2             | V                 |

| I <sub>CC</sub>    | Supply Current                                                            | Normal operation, dual outputs ( <i>Note 7</i> )  |                     |          | 55   | 74              | mA                |

|                    |                                                                           | Normal operation, single output ( <i>Note 7</i> ) |                     |          | 45   | 63              | mA                |

|                    |                                                                           | Power save mode                                   |                     |          | 7    | 10              | mA                |

| Symbol                          | Parameter                        | Conditions                                                   | Reference                              | Min | Тур  | Max  | Units |

|---------------------------------|----------------------------------|--------------------------------------------------------------|----------------------------------------|-----|------|------|-------|

| BR <sub>MIN</sub>               | Minimum Input Data Rate          |                                                              | SDI, <u>SDI</u>                        |     | 125  |      | Mbps  |

| BR <sub>MAX</sub>               | Maximum Input Data Rate          |                                                              | 7                                      |     |      | 2970 | Mbps  |

|                                 | Jitter for Various Cable Lengths | 2.97 Gbps, Belden 1694A,<br>0-100 meters ( <i>Note 8</i> )   |                                        |     |      | 0.2  | UI    |

|                                 |                                  | 2.97 Gbps, Belden 1694A,<br>100-140 meters ( <i>Note 8</i> ) |                                        |     |      | 0.3  | UI    |

|                                 |                                  | 2.97 Gbps, Belden 1694A,<br>140-180 meters ( <i>Note 8</i> ) |                                        |     |      | 0.5  | UI    |

|                                 |                                  | 2.97 Gbps, Belden 1694A,<br>180-200 meters                   |                                        |     | 0.55 |      | UI    |

|                                 |                                  | 1.485 Gbps, Belden 1694A,<br>0-200 meters ( <i>Note 8</i> )  |                                        |     |      | 0.2  | UI    |

|                                 |                                  | 1.485 Gbps, Belden 1694A,<br>200-220 meters                  |                                        |     | 0.3  |      | UI    |

|                                 |                                  | 270 Mbps, Belden 1694A,<br>0-400 meters ( <i>Note 8</i> )    |                                        |     |      | 0.3  | UI    |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise Time, Fall Time      | 20% – 80%, 100Ω load,<br>( <i>Note 4</i> ), <i>Figure 1</i>  | SDO0, <u>SDO0</u><br>SDO1, <u>SDO1</u> |     | 80   | 130  | ps    |

|                                 | Mismatch in Rise/Fall Time       | (Note 4)                                                     |                                        |     | 2    | 15   | ps    |

| t <sub>os</sub>                 | Output Overshoot                 | (Note 4)                                                     | ]                                      |     | 1    | 5    | %     |

| RL <sub>IN</sub>                | Input Return Loss                | 5 MHz - 1.5 GHz, ( <i>Note 9</i> )                           | SDI, <u>SDI</u>                        | 15  |      |      | dB    |

|                                 |                                  | 1.5 GHz - 3.0 GHz, ( <i>Note 9</i> )                         | ] [                                    | 10  |      |      | dB    |

| R <sub>IN</sub>                 | Input Resistance                 | single-ended                                                 | [                                      |     | 1.5  |      | kΩ    |

| C <sub>IN</sub>                 | Input Capacitance                | single-ended                                                 | ] [                                    |     | 0.7  |      | pF    |

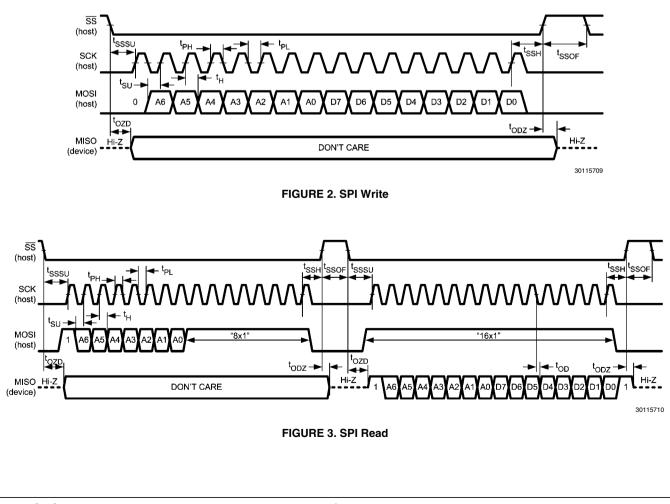

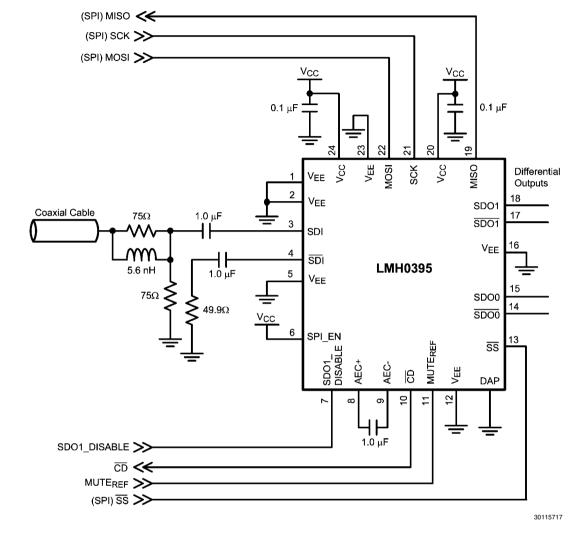

## **SPI Interface AC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (Note 3).

| Symbol            | Parameter                     | Conditions         | Reference | Min | Тур | Max | Units           |

|-------------------|-------------------------------|--------------------|-----------|-----|-----|-----|-----------------|

| Recomm            | nended Input Timing Requireme | ents               | ·         |     |     | •   |                 |

| f <sub>scк</sub>  | SCK Frequency                 |                    | SCK       |     |     | 20  | MHz             |

| t <sub>PH</sub>   | SCK Pulse Width High          | Figure 2, Figure 3 |           | 40  |     |     | % SCK<br>period |

| t <sub>PL</sub>   | SCK Pulse Width Low           |                    |           | 40  |     |     | % SCK<br>period |

| t <sub>su</sub>   | MOSI Setup Time               | Figure 2, Figure 3 | MOSI      | 4   |     |     | ns              |

| t <sub>H</sub>    | MOSI Hold Time                |                    |           | 4   |     |     | ns              |

| t <sub>SSSU</sub> | SS Setup Time                 | Figure 2, Figure 3 | SS        | 14  |     |     | ns              |

| t <sub>SSH</sub>  | SS Hold Time                  |                    |           | 4   |     |     | ns              |

| t <sub>SSOF</sub> | SS Off Time                   |                    |           | 1   |     |     | SCK<br>period   |

| Switchir          | g Characteristics             | 1                  |           |     |     |     |                 |

| t <sub>opz</sub>  | MISO Driven-to-Tristate Time  | Figure 3           | MISO      |     |     | 20  | ns              |

| t <sub>OZD</sub>  | MISO Tristate-to-Driven Time  |                    |           |     |     | 10  | ns              |

| t <sub>op</sub>   | MISO Output Delay Time        |                    |           |     |     | 15  | ns              |

Note 1: "Absolute Maximum Ratings" are those parameter values beyond which the life and operation of the device cannot be guaranteed. The stating herein of these maximums shall not be construed to imply that the device can or should be operated at or beyond these values. The table of "Electrical Characteristics" specifies acceptable device operating conditions.

Note 2: Current flow into device pins is defined as positive. Current flow out of device pins is defined as negative. All voltages are stated referenced to  $V_{EE} = 0$  Volts.

Note 3: Typical values are stated for V<sub>CC</sub> = +2.5V and T<sub>A</sub> = +25°C.

The Appendication is the managed by characterization.

Note 5: The LMH0395 can be optimized for different launch amplitudes via the SPI.

Note 6: The differential output voltage and offset voltage are adjustable via the SPI.

Note 7: Typical I<sub>CC</sub> is measured with a 2.97 Gbps input signal.

Note 8: Based on design and characterization data over the full range of recommended operating conditions of the device. Jitter is measured in accordance with SMPTE RP 184, SMPTE RP 192, and the applicable serial data transmission standard: SMPTE 424M, SMPTE 292M, or SMPTE 259M.

Note 9: Input return loss is dependent on board design. The LMH0395 exceeds this specification on the SD395 evaluation board with a return loss network consisting of a 5.6 nH inductor in parallel with a 75 $\Omega$  series resistor on the input.

## **Timing Diagrams**

FIGURE 1. LVDS Output Voltage, Offset, and Timing Parameters

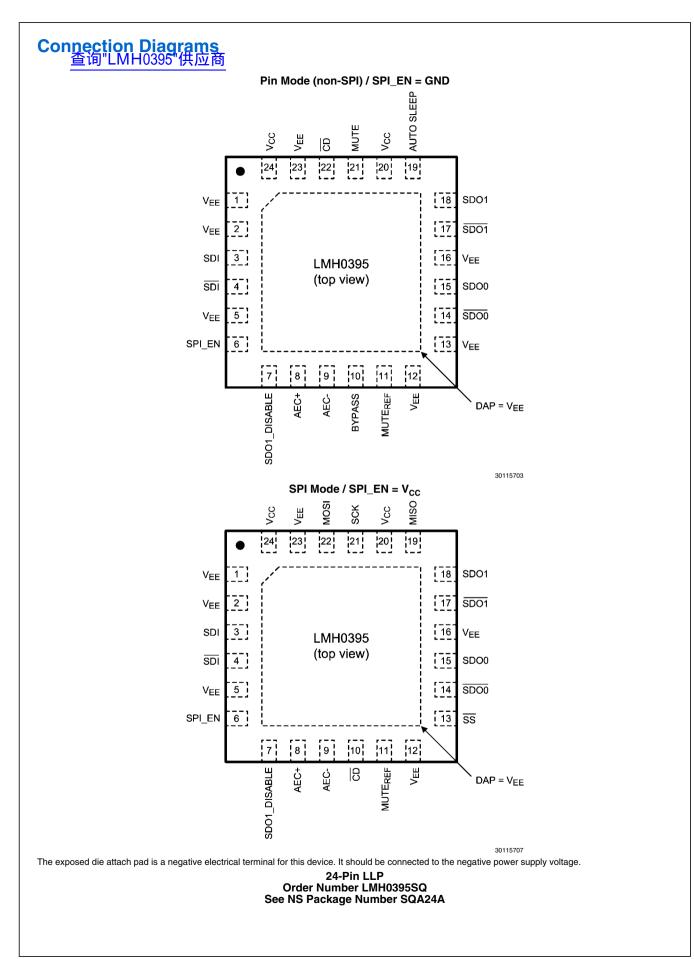

| <u>- LIVIF</u><br>Pin | 10395 1 <del>八/空</del> 谷]<br>Name | I/O, Type   | le (non-SPI) / SPI_EN = GND Description                                                                                                                                                                                                                                  |

|-----------------------|-----------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | V <sub>EE</sub>                   | Ground      | Negative power supply (ground).                                                                                                                                                                                                                                          |

| 2                     | V <sub>EE</sub>                   | Ground      | Negative power supply (ground).                                                                                                                                                                                                                                          |

| 3                     | SDI                               | I, SDI      | Serial data true input.                                                                                                                                                                                                                                                  |

| 4                     | SDI                               | I, SDI      | Serial data complement input.                                                                                                                                                                                                                                            |

| 5                     | V <sub>EE</sub>                   | Ground      | Negative power supply (ground)                                                                                                                                                                                                                                           |

| 6                     | SPI_EN                            | I, LVCMOS   | SPI register access enable. This pin has an internal pulldown.<br>H = SPI register access mode.<br>L = Pin mode.                                                                                                                                                         |

| 7                     | SDO1_DISABLE                      | I, LVCMOS   | Output driver 1 (SDO1, SDO1) disable. This pin has an internal pullup.<br>H (or no connection) = Output driver 1 is in a high impedance state.<br>L = Output driver 1 is enabled.                                                                                        |

| 8                     | AEC+                              | I/O, Analog | AEC loop filter external capacitor (1µF) positive connection (capacitor is optiona                                                                                                                                                                                       |

| 9                     | AEC-                              | I/O, Analog | AEC loop filter external capacitor (1µF) negative connection (capacitor is optiona                                                                                                                                                                                       |

| 10                    | BYPASS                            | I, LVCMOS   | Equalization bypass. This pin has an internal pulldown.<br>H = Equalization is bypassed (no equalization occurs).<br>L = Normal operation.                                                                                                                               |

| 11                    | MUTE <sub>REF</sub>               | I, Analog   | Mute reference input. Sets the threshold for $\overline{CD}$ and (with $\overline{CD}$ tied to MUTE) determines the maximum cable to be equalized before muting. MUTE <sub>REF</sub> may either unconnected or connected to ground for normal $\overline{CD}$ operation. |

| 12                    | V <sub>EE</sub>                   | Ground      | Negative power supply (ground).                                                                                                                                                                                                                                          |

| 13                    | V <sub>EE</sub>                   | Ground      | Negative power supply (ground).                                                                                                                                                                                                                                          |

| 14                    | SDO0                              | O, LVDS     | Serial data output 0 complement.                                                                                                                                                                                                                                         |

| 15                    | SDO0                              | O, LVDS     | Serial data output 0 true.                                                                                                                                                                                                                                               |

| 16                    | V <sub>EE</sub>                   | Ground      | Negative power supply (ground).                                                                                                                                                                                                                                          |

| 17                    | SDO1                              | O, LVDS     | Serial data output 1 complement.                                                                                                                                                                                                                                         |

| 18                    | SDO1                              | O, LVDS     | Serial data output 1 true                                                                                                                                                                                                                                                |

| 19                    | AUTO SLEEP                        | I, LVCMOS   | Auto Sleep. AUTO SLEEP has precedence over MUTE and BYPASS. This pin<br>has an internal pullup.<br>H = When no input signal is detected, the device will power down and the output<br>will be in a high impedance state.<br>L = Device will not enter auto power down.   |

| 20                    | V <sub>cc</sub>                   | Power       | Positive power supply (+2.5V).                                                                                                                                                                                                                                           |

| 21                    | MUTE                              | I, LVCMOS   | Output mute. CD may be tied to this pin to inhibit the output when no input sign<br>is present. MUTE has precedence over BYPASS. This pin has an internal<br>pulldown.<br>H = Outputs are forced to a constant logic high state.<br>L = Outputs are enabled.             |

| 22                    | CD                                | O, LVCMOS   | Carrier detect.<br>H = No input signal detected.<br>L = Input signal detected.                                                                                                                                                                                           |

| 23                    | V <sub>EE</sub>                   | Ground      | Negative power supply (ground).                                                                                                                                                                                                                                          |

| 24                    | V <sub>CC</sub>                   | Power       | Positive power supply (+2.5V).                                                                                                                                                                                                                                           |

| DAP                   | V <sub>EE</sub>                   | Ground      | Connect exposed DAP to negative power supply (ground).                                                                                                                                                                                                                   |

## Pin 叠窗qriptiog95 供应器 Mode / SPI\_EN = V<sub>CC</sub>

| Pin | Name                | I/O, Type   | Description                                                                                          |

|-----|---------------------|-------------|------------------------------------------------------------------------------------------------------|

| 1   | V <sub>EE</sub>     | Ground      | Negative power supply (ground).                                                                      |

| 2   | V <sub>EE</sub>     | Ground      | Negative power supply (ground).                                                                      |

| 3   | SDI                 | I, SDI      | Serial data true input.                                                                              |

| 4   | SDI                 | I, SDI      | Serial data complement input.                                                                        |

| 5   | V <sub>EE</sub>     | Ground      | Negative power supply (ground).                                                                      |

| 6   | SPI_EN              | I, LVCMOS   | SPI register access enable. This pin has an internal pulldown.                                       |

|     |                     |             | H = SPI register access mode.                                                                        |

|     |                     |             | L = Pin mode.                                                                                        |

| 7   | SDO1_DISABLE        | I, LVCMOS   | Output driver 1 (SDO1, SDO1) disable. This pin has an internal pullup.                               |

|     |                     |             | H (or no connection) = Output driver 1 is in a high impedance state.                                 |

|     |                     |             | L = Output driver 1 is enabled.                                                                      |

| 8   | AEC+                | I/O, Analog | AEC loop filter external capacitor $(1\mu F)$ positive connection (capacitor is optional).           |

| 9   | AEC-                | I/O, Analog | AEC loop filter external capacitor (1 $\mu$ F) negative connection (capacitor is optional).          |

| 10  | CD                  | O, LVCMOS   | Carrier detect.                                                                                      |

|     |                     |             | H = No input signal detected.                                                                        |

|     |                     |             | L = Input signal detected.                                                                           |

| 11  | MUTE <sub>REF</sub> | I, Analog   | Mute reference input. Sets the threshold for $\overline{CD}$ and (with $\overline{CD}$ tied to MUTE) |

|     |                     |             | determines the maximum cable to be equalized before muting. MUTE <sub>REF</sub> may be               |

|     |                     |             | either unconnected or connected to ground for normal CD operation.                                   |

| 12  | V <sub>EE</sub>     | Ground      | Negative power supply (ground).                                                                      |

| 13  | SS (SPI)            | I, LVCMOS   | SPI slave select. This pin has an internal pullup.                                                   |

| 14  | SDO0                | O, LVDS     | Serial data output 0 complement.                                                                     |

| 15  | SDO0                | O, LVDS     | Serial data output 0 true.                                                                           |

| 16  | V <sub>EE</sub>     | Ground      | Negative power supply (ground).                                                                      |

| 17  | SDO1                | O, LVDS     | Serial data output 1 complement.                                                                     |

| 18  | SDO1                | O, LVDS     | Serial data output 1 true.                                                                           |

| 19  | MISO (SPI)          | O, LVCMOS   | SPI Master Input / Slave Output. LMH0395 control data transmit.                                      |

| 20  | V <sub>CC</sub>     | Power       | Positive power supply (+2.5V).                                                                       |

| 21  | SCK (SPI)           | I, LVCMOS   | SPI serial clock input. This pin has an internal pulldown.                                           |

| 22  | MOSI (SPI)          | I, LVCMOS   | SPI Master Output / Slave Input. LMH0395 control data receive. This pin has an                       |

|     |                     |             | internal pulldown.                                                                                   |

| 23  | V <sub>EE</sub>     | Ground      | Negative power supply (ground).                                                                      |

| 24  | V <sub>cc</sub>     | Power       | Positive power supply (+2.5V).                                                                       |

|     | V <sub>EE</sub>     | Ground      | Connect exposed DAP to negative power supply (ground).                                               |

##

30115702

## **Device Operation**

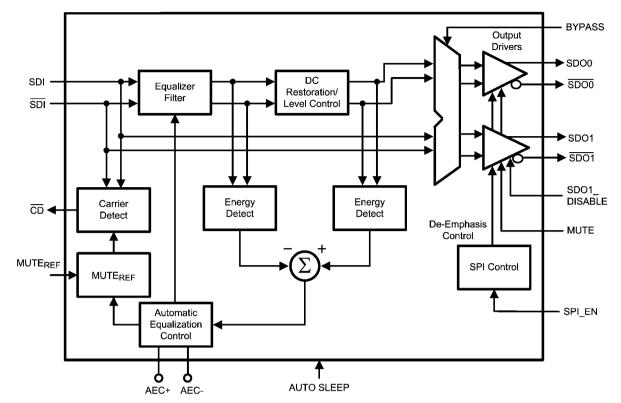

#### **BLOCK DESCRIPTION**

The **Equalizer Filter** block is a multi-stage adaptive filter. If Bypass is high, the equalizer filter is disabled.

The **DC Restoration / Level Control** block receives the differential signals from the equalizer filter block. This block incorporates a self-biasing DC restoration circuit to fully DC restore the signals. If Bypass is high, this function is disabled.

The signals before and after the DC Restoration / Level Control block are used to generate the **Automatic Equalization Control (AEC)** signal. This control signal sets the gain and bandwidth of the equalizer filter.

The **Carrier Detect** block generates the carrier detect signal based on the SDI input and an adjustment from the **Mute Reference** block.

The **SPI Control** block uses the MOSI, MISO, SCK, and <del>SS</del> signals in SPI mode to control the SPI registers. SPI\_EN selects between SPI mode and pin mode. In pin mode, SPI\_EN is driven logic low.

The **Output Drivers** produce SDO0,  $\overline{\text{SDO0}}$ , SDO1, and  $\overline{\text{SDO1}}$ .

#### MUTE REFERENCE (MUTE<sub>REF</sub>)

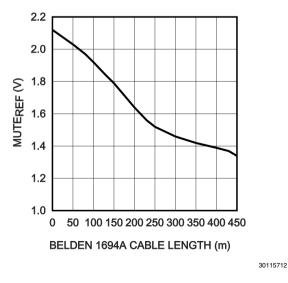

The mute reference sets the threshold for  $\overline{CD}$  and (with  $\overline{CD}$  tied to MUTE) determines the amount of cable to equalize before automatically muting the outputs. This is set by applying a voltage inversely proportional to the length of cable to equalize. The applied voltage must be greater than the MUTE<sub>REF</sub> floating voltage (typically 1.3V) in order to change the  $\overline{CD}$  threshold. As the applied MUTE<sub>REF</sub> voltage is in-

creased, the amount of cable that can be equalized before carrier detect is de-asserted and the outputs are muted is decreased. MUTE<sub>REE</sub> may be left unconnected or connected to ground for normal CD operation. Optionally, the LMH0395 allows the mute reference to be set digitally via SPI register 03h. *Figure 4* shows the minimum MUTE<sub>REF</sub> input voltage required to force carrier detect to inactive vs. Belden 1694A cable length. The results shown are valid for Belden 1694A cable lengths of 0-200m at 2.97 Gbps, 0-220m at 1.485 Gbps, and 0-450m at 270 Mbps.

FIGURE 4. MUTE<sub>REF</sub> vs. Belden 1694A Cable Length

#### CARRIER DETECT (CD) AND MUTE

Carrier查爾尼亞語名 (中國語名) (其內爾語) is present at the LMH0395 input. This signal is logical OR operation of internal energy detector and MUTE<sub>REF</sub> setting (if used). Internal energy detector detects energy across different data rates. If MUTE<sub>REF</sub> is used, the carrier detect threshold will be altered accordingly. OD provides a high voltage when no signal is present at the LMH0395 input. CD is low when a valid input signal is detected.

MUTE can be used to manually mute or enable the output drivers. Applying a high input to MUTE will mute the LMH0395 outputs by forcing the output to a logic 1. Applying a low input will force the outputs to be active.

In pin mode, CD and MUTE may be tied together to automatically mute the output when no input signal is present.

#### AUTO SLEEP

The auto sleep mode allows the LMH0395 to power down when no input signal is detected. If the AUTO SLEEP pin is set high, the LMH0395 goes into a deep power save mode when no signal is detected. The device powers on again once an input signal is detected. If the AUTO SLEEP pin is set low, the LMH0395 will always be on and will not enter power save mode. The auto sleep functionality can be turned off by setting AUTO SLEEP low or tying this pin to ground. An additional auto sleep setting available in SPI mode can be used to force the equalizer to power down regardless of whether there is an input signal or not. Auto sleep has precedence over mute and bypass modes.

In auto sleep mode, the time to power down the equalizer when the input signal is removed is less than 200  $\mu$ s and should not have any impact on the system timing requirements. The device will wake up automatically once an input signal is detected, and the delay between signal detection and full functionality of the equalizer is negligible (about 5 ms). The overall system will be limited only by the settling time constant of the equalizer adaptation loop.

#### **INPUT INTERFACING**

The LMH0395 accepts either differential or single-ended input. The input must be AC coupled. The *Typical Application (Pin Mode)* diagram shows the typical configuration for a single-ended input. The unused input must be properly terminated as shown.

The LMH0395 can be optimized for different launch amplitudes via the SPI (see *LAUNCH AMPLITUDE OPTIMIZA-TION* in the *SPI Register Access* section).

The LMH0395 correctly handles equalizer pathological signals for standard definition and high definition serial digital video, as described in SMPTE RP 178 and RP 198, respectively.

#### **OUTPUT INTERFACING**

The LMH0395 dual output differential pairs, SDO0,  $\overline{SDO0}$ , SDO1, and  $\overline{SDO1}$  are internally terminated 100 $\Omega$  LVDS out-

puts. These outputs can be DC coupled to most common differential receivers.

The default output common mode voltage ( $V_{OS}$ ) is 1.2V. The output common mode voltage may be adjusted via the SPI in 200 mV increments, from 0.8V to 1.2V (see *OUTPUT DRIVER ADJUSTMENTS AND DE-EMPHASIS SETTING* in the *SPI Register Access* section). When the output common mode is supply referenced, the common mode voltage is about 1.35V (for 700 mV<sub>P-P</sub> differential swing). This adjustable output common mode voltage offers flexibility for interfacing to many types of receivers.

The default differential output swing  $(V_{SSP-P})$  is 700 mV<sub>P.P.</sub> The differential output swing may be adjusted via the SPI. Valid options are 400, 600, 700, or 800 mV<sub>P.P</sub> (see *OUTPUT DRIVER ADJUSTMENTS AND DE-EMPHASIS SETTING* in the *SPI Register Access* section).

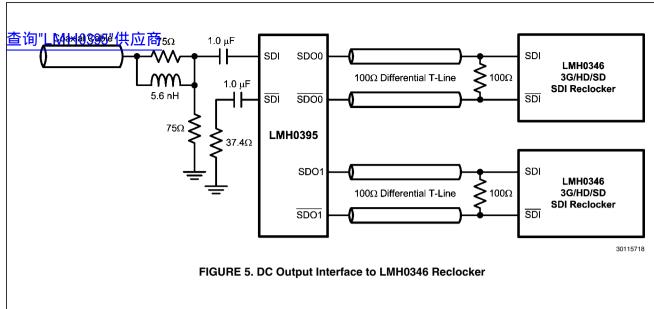

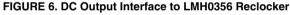

The LMH0395 output should be DC coupled to the input of the receiving device as long as the common mode ranges of both devices are compatible.  $100\Omega$  differential transmission lines should be used to connect between the LMH0395 outputs and the input of the receiving device where possible. *Figure 5* shows an example of a DC-coupled interface between the LMH0395 and LMH0346 SDI reclocker. All that is required is the  $100\Omega$  differential termination as shown. The resistor should be placed as close as possible to the LMH0346 input. If desired, this network may be terminated with two  $50\Omega$  resistors and a center tap capacitor to ground in place of the signal  $100\Omega$  resistor.

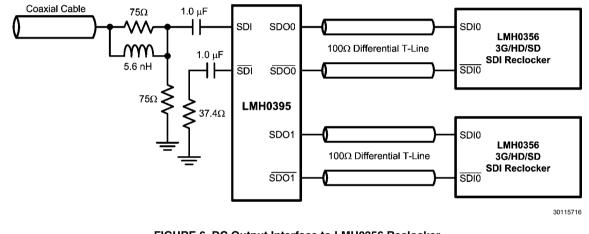

*Figure 6* shows an example of a DC-coupled interface between the LMH0395 and LMH0356 SDI reclocker. The LMH0356 inputs have 50 $\Omega$  internal terminations (100 $\Omega$  differential) to terminate the transmission line, so no additional components are required.

The LMH0395 may be AC coupled to the receiving device when necessary. For example, the LMH0395 outputs are not strictly compatible with 2.5V CML and thus should not be connected via  $50\Omega$  resistors to 2.5V. If the input common mode range of the receiving device is not compatible with the output common mode range of the LMH0395, then AC coupling is required. Following the AC coupling capacitors, the signal may have to be biased at the input of the receiving device.

The LMH0395 output drivers are equipped with programmable output de-emphasis to minimize inter-symbol interference caused by the loss dispersion from driving signals across PCB traces (see *OUTPUT DRIVER ADJUSTMENTS AND DE-EMPHASIS SETTING* in the *SPI Register Access* section). De-emphasis works with all combinations of output common mode voltage and output voltage swing settings to support DC coupling to the receiving device.

## **SPI Register Access**

Setting SPI\_EN high enables the optional SPI register access mode. In SPI mode, the LMH0395 provides register access to all of its features along with a cable length indicator, programmable output de-emphasis, programmable output common mode voltage and swing, digital MUTE<sub>REF</sub>, and launch amplitude optimization. There are eight supported 8-bit registers in the device (see *Table 1*). The LMH0395 supports SPI daisy-chaining among an unlimited number of LMH0395 devices.

#### SPI Transaction Overview

Each SPI transaction to a single device is 16-bits long. The transaction is initiated by driving  $\overline{SS}$  low, and completed by returning  $\overline{SS}$  high. The 16-bit MOSI payload consists of the read/write command ("1" for reads and "0" for writes), the seven address bits of the device register (MSB first), and the eight data bits (MSB first). The LMH0395 MOSI input data is latched on the rising edge of SCK, and the MISO output data is sourced on the falling edge of SCK.

In order to facilitate daisy-chaining, the prior SPI command, address, and data are shifted out on the MISO output as the current command, address, and data are shifted in on the MOSI input. For SPI writes, the MISO output is typically ignored as "Don't Care" data. For SPI reads, the MISO output provides the requested read data (after 16 periods of SCK). The MISO output is active when  $\overline{SS}$  low, and tri-stated when  $\overline{SS}$  is high.

#### SPI Write

The SPI write is shown in *Figure 2*. The SPI write is 16 bits long. The 16-bit MOSI payload consists of a "0" (write command), seven address bits, and eight data bits. The  $\overline{SS}$  signal is driven low, and the 16 bits are sent to the LMH0395's MOSI input. After the SPI write,  $\overline{SS}$  must return high. The prior SPI command, address, and data shifted out on the MISO output during the SPI write is shown as "Don't Care" on the MISO output in *Figure 2*.

#### SPI Read

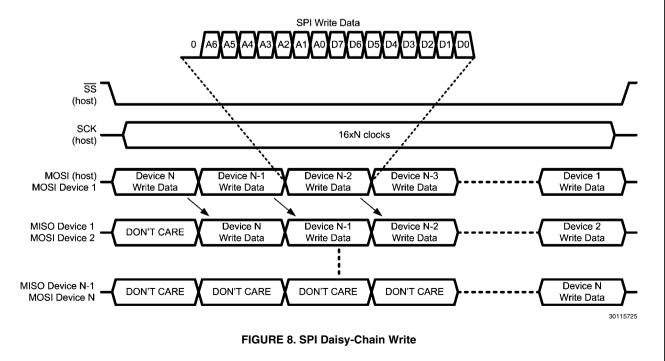

The SPI read is shown in *Figure 3*. The SPI read is 32 bits long, consisting of a 16-bit read transaction followed by a 16-bit dummy read transaction to shift out the read data on the MISO output. The first 16-bit MOSI payload consists of a "1" (read command), seven address bits, and eight "1"s which are ignored. The second 16-bit MOSI payload consists of 16 "1"s which are ignored but necessary in order to shift out the requested read data on the MISO output. The SS signal is driven low, and the first 16 bits are sent to the LMH0395's MOSI input. The prior SPI command, address, and data are

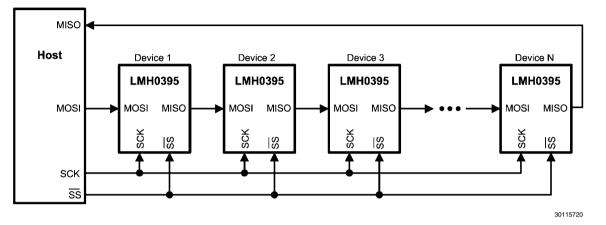

shifted out on the MISO output during the first 16-bit transaction, and any typically ignore diffine is shown as "Don't Care" on the MISO output in Figure 3. SS must return high and then is driven low again before the second 16 bits (all "1"s) are sent to the LMH0395's MOSI input. Once again, the prior SPI command, address, and data are shifted out on the MISO output, but this data now includes the requested read data. The read data is available on the MISO output during the second 8 bits of the 16-bit dummy read transaction, as shown by D7-D0 in *Figure 3.*  The LMH0395 SPI controller supports daisy-chaining the serial data between an unlimited number of LMH0395 devices. Each LMH0395 device is directly connected to the SCK and SS pins on the host. However, only the first LMH0395 device in the chain is connected to the host's MOSI pin, and only the last device in the chain is connected to the host's MISO pin. The MISO pin of each intermediate LMH0395 device in the chain is connected to the MOSI pin of the next LMH0395 device, creating a serial shift register. This daisy-chain architecture is shown in *Figure 7*.

#### SPI Daisy-Chain Operation

FIGURE 7. SPI Daisy Chain System Architecture

In a daisy-chain configuration of N LMH0395 devices, the host conceptually sees a shift register of length 16xN. Therefore the length of <u>SPI</u> transactions (as previously described) is 16xN bits, and <del>SS</del> must be asserted for 16xN clock cycles for each SPI transaction.

#### SPI Daisy-Chain Write

Figure 8 shows the SPI daisy-chain write for a daisy-chain of N devices. The  $\overline{SS}$  signal is driven low and SCK is toggled for 16xN clocks. The 16xN bit MOSI payload (sent to Device 1 in

the daisy-chain) consists of the 16-bit SPI write data for Device N (the last device in the chain), followed by the write data for Device N-1, Device N-2, etc., ending with the write data for Device 1 (the first device in the chain). The 16-bit SPI write data for each device consists of a "0" (write command), seven address bits, and eight data bits. After the SPI daisy-chain write,  $\overline{SS}$  must return high and then the write occurs for all devices in the daisy-chain.

#### SPI Daisy-Chain Read

LMH0395

**in ULM blogg of Asymptotic Sector** Asymptotic Sector and Sector a

ending with the read data for Device 1 (the first device in the chain). The 16-bit SPI read data for each device consists of a "1" (read command), seven address bits, and eight "1"s (which are ignored). After the first 16xN bit transaction,  $\overline{SS}$  must return high (to latch the data) and then is driven low again before the second 16xN bit transaction of all "1"s is sent to the MOSI input. The requested read data is shifted out on MISO starting with the data for Device N and ending with the data for Device 1. After this transaction,  $\overline{SS}$  must return high.

#### FIGURE 9. SPI Daisy-Chain Read

#### SPI Daisy-Chain Read and Write Example

The following example further clarifies LMH0395 SPI daisychain operation. Assume a daisy-chain of three LMH0395 devices (Device 1, Device 2, and Device 3), with Device 1 as the first device in the chain and Device 3 as the last device in the chain, as shown by the first three devices in *Figure 7*. Since there are three devices in the daisy-chain, each SPI transaction is 48-bits long.

This example shows an SPI operation combining SPI reads and writes in order to accomplish the following three tasks:

- 1. Write 0x22 to register 0x01 of Device 1 in order to set the output swing of output driver 0 to 400 mV\_{P-P}.

- 2. Read the contents of register 0x00 of Device 2.

- 3. Write 0x10 to register 0x00 of Device 3 in order to force the sleep mode.

*Figure 10* shows the two 48-bit SPI transactions required to complete these tasks (the bits are shifted in left to right).

| 48-bit SPI Transaction #1 |              |           |                                                 |                              |                                                                                     |                                                                                                   |                                                                                                                     |                                                                                                                                       | -                                                        |                                                                                                                                                                                                                         | 4                                                                                                                                                    | o-Dit a                                                                                                                                                       | SPI Tran                                                                                                                                                                                                                                                    | saction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | #2                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------|--------------|-----------|-------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Device                   | 3)           |           | (Device                                         | 2)                           |                                                                                     | (Device                                                                                           | : 1)                                                                                                                |                                                                                                                                       |                                                          | (Device                                                                                                                                                                                                                 | 3)                                                                                                                                                   |                                                                                                                                                               | (Device                                                                                                                                                                                                                                                     | 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                           | (Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Addr                      | Data         | R/W       | Addr                                            | Data                         | R/W                                                                                 | Addr                                                                                              | Data                                                                                                                |                                                                                                                                       | R/W                                                      | Addr                                                                                                                                                                                                                    | Data                                                                                                                                                 | R/W                                                                                                                                                           | Addr                                                                                                                                                                                                                                                        | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W                                                                                                                                                                                                                                       | Addr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x01                      | 0x22         | 1         | 0x00                                            | 0xFF                         | 0                                                                                   | 0x00                                                                                              | 0x10                                                                                                                |                                                                                                                                       | 1                                                        | 0x7F                                                                                                                                                                                                                    | 0xFF                                                                                                                                                 | 1                                                                                                                                                             | 0x7F                                                                                                                                                                                                                                                        | 0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                         | 0x7F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| хх                        | хх           | х         | хх                                              | xx                           | х                                                                                   | хх                                                                                                | хх                                                                                                                  |                                                                                                                                       | 0                                                        | 0x01                                                                                                                                                                                                                    | 0x22                                                                                                                                                 | 1                                                                                                                                                             | 0x00                                                                                                                                                                                                                                                        | <u>0x88</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                         | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | Addr<br>0x01 | 0x01 0x22 | Addr     Data     R/W       0x01     0x22     1 | AddrDataR/WAddr0x010x2210x00 | Addr     Data     R/W     Addr     Data       0x01     0x22     1     0x00     0xFF | Addr     Data     R/W     Addr     Data     R/W       0x01     0x22     1     0x00     0xFF     0 | Addr     Data     R/W     Addr     Data     R/W     Addr       0x01     0x22     1     0x00     0xFF     0     0x00 | Addr     Data     R/W     Addr     Data     R/W     Addr     Data       0x01     0x22     1     0x00     0xFF     0     0x00     0x10 | AddrDataR/WAddrDataR/WAddrData0x010x2210x000xFF00x000x10 | Addr         Data         R/W         Addr         Data         R/W         Addr         Data         R/W           0x01         0x22         1         0x00         0xFF         0         0x00         0x10         1 | Addr     Data     R/W     Addr     Data     R/W     Addr     Data       0x01     0x22     1     0x00     0xFF     0     0x00     0x10     1     0x7F | Addr     Data     R/W     Addr     Data     R/W     Addr     Data       0x01     0x22     1     0x00     0xFF     0     0x00     0x10     1     0x7F     0xFF | Addr         Data         R/W         Addr         Data         R/W         Addr         Data         R/W           0x01         0x22         1         0x00         0xFF         0         0x00         0x10         1         0x7F         0xFF         1 | Addr         Data         R/W         Addr         Data         Low         Low | Addr     Data     R/W     Addr     Data     R/W     Addr     Data     R/W     Addr     Data     R/W     Addr     Data       0x01     0x22     1     0x00     0xFF     0     0x00     0x10     1     0x7F     0xFF     1     0x7F     0xFF | Addr         Data         R/W           0x01         0x22         1         0x00         0x10         1         0x7F         0x7F         0xFF         1         0x7F         0x7F | Addr     Data     R/W     Addr     < |

#### FIGURE 10. SPI Daisy-Chain Read and Write Example

The following occurs at the end of the first transaction:

1. Write 0x22 to register 0x01 of Device 1.

- 2. Latch the data from register 0x00 of Device 2.

- 3. Write 0x10 to register 0x00 of Device 3.

In the second transaction, three dummy reads (each consisting of 1查行) ane shiftertin, and there ad data from Device 2 (with value 0x88) appears on MISO in the 25th through 32nd clock cycles. of dummy reads with a known data value (such as 0x5A). For an SPI daisy-chain of N LMH0395 devices, the known data value will appear on the host's MISO pin after N+1 writes. Assuming a daisy-chain of three LMH0395 devices, the result of this operation is shown in *Figure 11*.

#### SPI Daisy-Chain Length Detection

A useful operation for the host may be to detect the length of the daisy-chain. This is a simple matter of shifting in a series

|                | R/W | Addr | Data        |

|----------------|-----|------|------|-----|------|------|-----|------|------|-----|------|-------------|

| MOSI<br>(host) | 1   | 0x7F | 0x5A        |

| MISO<br>(host) | х   | xx   | xx   | x   | xx   | xx   | x   | xx   | xx   | 1   | 0x7F | <u>0x5A</u> |

30115729

#### FIGURE 11. SPI Daisy-Chain Length Detection

## OUTPUT DRIVER ADJUSTMENTS AND DE-EMPHASIS SETTING

The output driver swing (amplitude), offset voltage (common mode voltage), and de-emphasis level are adjustable via SPI register 01h. The output driver to control with SPI register 01h (either output driver 0 or output driver 1) can be selected via bit 2 of SPI register 00h.

The output swing is adjustable via bits [7:6] of SPI register 01h. The default value for these register bits is "10" for a peak to peak differential output voltage of 700 mV<sub>P-P</sub>. The output swing can be set for 400 mV<sub>P-P</sub>, 600 mV<sub>P-P</sub>, 700 mV<sub>P-P</sub>, or 800 mV<sub>P-P</sub>.