# M2118 FAMILY 16,384 x 1 BIT DYNAMIC RAM

MILITARY

| Al Al Al                 | M2118-4 | M2118-7 |

|--------------------------|---------|---------|

| Maximum Access Time (ns) | 120     | 150     |

| Read, Write Cycle (ns)   | 270     | 320     |

| Read-Modify Cycle (ns)   | 320     | 410     |

- Single +5V Supply, ±10% Tolerance

- HMOS Technology

- Low Power: 150 mW Max. Operating 11 mW Max. Standby

- Low V<sub>pp</sub> Current Transients

- All Inputs, Including Clocks, TTL Compatible

- CAS Controlled Output is

Three-State, TTL Compatible

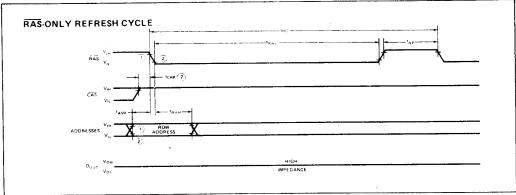

- RAS Only Refresh

- 128 Refresh Cycles Required Every 2ms

- Allows Negative Overshoot

V<sub>IL</sub> min = -2V

- Military Temperature Range -55° to +85°C (T<sub>c</sub>)

- Not Recommended for New Designs

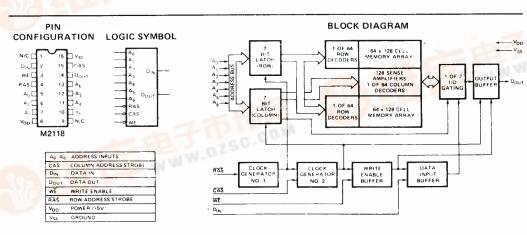

The Intel® M2118 is a 16,384 word by 1-bit Dynamic MOS RAM designed to operate from a single +5V power supply. The M2118 is fabricated using HMOS—a production proven process for high performance, high reliability, and high storage density.

The M2118 uses a single transistor dynamic storage cell and advanced dynamic circuitry to achieve high speed with low power dissipation. The circuit design minimizes the current transients typical of dynamic RAM operation. These low current transients contribute to the high noise immunity of the M2118 in a system environment.

Multiplexing the 14 address bits into the 7 address input pins allows the M2118 to be packaged in the industry standard 16-pin DIP. The two 7-bit address words are latched into the M2118 by the two TTL clocks, Row Address Strobe (RAS) and Column Address Strobe (CAS). Non-critical timing requirements for RAS and CAS allow use of the address multiplexing technique while maintaining high performance.

The M2118 three-state output is controlled by CAS, independent of RAS. After a valid read or read-modify-write cycle, data is latched on the output by holding CAS low. The data out pin is returned to the high impedance state by returning CAS to a high state.

The single transistor storage cell requires refreshing for data retention. Refreshing is accomplished by performing RASonly refresh cycles, or normal read or write cycles on the 128 address combinations of A<sub>0</sub> through A<sub>6</sub> during a 2ms period. A write cycle will refresh stored data on all bits of the selected row except the bit which is addressed.

### **M2118 FAMILY**

## APSOLUTE MAXIMEM RATINGS+

| Case Temperature Under Bias        | 65°C to +95°C   |

|------------------------------------|-----------------|

| Storage Temperature                | -65°C to +150°C |

| Voltage on any Pin Relative to Vss |                 |

| Data Out Current                   | 50mA            |

| Power Dissination                  | 1 0W            |

#### \*COMMENT

Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to ab-solute maximum rating conditions for extended periods may affect device reliability.

### D.C. AND OPERATING CHARACTERISTICS [1]

$T_c^4 = -55$ °C to +85°C,  $V_{DD} = 5V \pm 10$ %,  $V_{SS} = 0V$ , unless otherwise noted.

|                  |                                                            |      | Limits  |     |      |                                                                        |       |

|------------------|------------------------------------------------------------|------|---------|-----|------|------------------------------------------------------------------------|-------|

| Symbol           | Parameter                                                  | Min  | Typ [2] | Max | Unit | Test Conditions                                                        | Notes |

| Hull             | Input Load Current (any input)                             |      | 0.1     | 10  | μА   | VIN=VSS to VDD                                                         |       |

| IILOI            | Output Leakage Current for<br>High Impedance State         |      | 0.1     | 10  | μА   | Chip Deselected: CAS at V <sub>IH</sub> , V <sub>OUT</sub> = 0 to 5.5V |       |

| IDD1             | V <sub>DD</sub> Supply Current, Standby                    |      | 1.2     | 2   | mA   | CAS and RAS at ViH                                                     |       |

| I <sub>DD2</sub> | V <sub>DD</sub> Supply Current, Operating                  |      | 21      | 25  | mA   | M2118-4, t <sub>RC</sub> = t <sub>RCMIN</sub>                          | 3     |

|                  |                                                            |      | 19      | 23  | mA   | M2118-7, t <sub>RC</sub> = t <sub>RCMIN</sub>                          | 3     |

| IDD3             | V <sub>DD</sub> Supply Current; RAS-Only                   |      | 14      | 16  | mA   | M2118-4, t <sub>RC</sub> = t <sub>RCMIN</sub>                          | 3     |

|                  | Cycle                                                      |      | 12      | 14  | mA   | M2118-7, t <sub>RC</sub> = t <sub>RCMIN</sub>                          | 3     |

| IDD5             | V <sub>DD</sub> Supply Current, Standby,<br>Output Enabled |      | 2       | 4   | mA   | CAS at VIL. RAS at VIH                                                 | 3     |

| VIL              | Input Low Voltage (all inputs)                             | -2.0 | Ī       | 0.8 | ٧    |                                                                        | I     |

| ViH              | Input High Voltage (all inputs)                            | 2.4  |         | 7.0 | V    |                                                                        |       |

| Vol              | Output Low Voltage                                         |      |         | 0.4 | V    | I <sub>OL</sub> = 4.2mA                                                |       |

| Vон              | Output High Voltage                                        | 2.4  | T       |     | ٧    | I <sub>QH</sub> = -5mA                                                 |       |

#### NOTES:

1. All voltages referenced to  $V_{SS}$ . 2. Typical values are for  $T_A=25\,^{\circ}\text{C}$  and nominal supply voltages.

3. I<sub>DD</sub> is dependent on output loading when the device output is selected. Specified I<sub>DDMAX</sub> is measured with the output

4. Case temperatures are "instant on."

### CAPACITANCE[1]

$T_C^2 = 25^{\circ}C$ ,  $V_{DD} = 5V \pm 10^{\circ}$ ,  $V_{SS} = 0V$ , unless otherwise noted.

| Symbol | Parameter              | Тур | Max | Unit |

|--------|------------------------|-----|-----|------|

| Ci1    | Address, Data In       | 3   | 5   | pF   |

| Ci2    | RAS, CAS, WE, Data Out | 4   | 7   | pF   |

- 1. Capacitance measured with Boonton Meter or effective capacitance calculated from the equation:

- $C = \frac{I\Delta t}{\Delta V}$  with  $\Delta V$  equal to 3 volts and power supplies at nominal levels.

- 2. Case temperatures are "instant on."

### 查询C2CHM(体应TeriSTICS[1,2,3]

$T_C^{10} = -55^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{DD} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted. i.

### READ, WRITE, READ-MODIFY-WRITE AND REFRESH CYCLES

|        | Parameter                           | M2   | 118-4 | M2118-7 |      |      |         |

|--------|-------------------------------------|------|-------|---------|------|------|---------|

| Symbol |                                     | Min. | Max.  | Min.    | Max. | Unit | Notes   |

| TRAC   | Access Time From RAS                |      | 120   |         | 150  | ns   | 4,5     |

| ICAC   | Access Time From CAS                |      | 65    |         | 80   | ns   | 4,5,6   |

| THEF   | Time Between Refresh                |      | 2     |         | 2    | ms   |         |

| tap    | RAS Precharge Time                  | 120  |       | 135     |      | ns   | İ       |

| topn   | CAS Precharge Time Inon-page cycles | 55   |       | 70_     |      | ns   |         |

| tCRP   | CAS to RAS Precharge Time           | 0    |       | 0       |      | ns   | ļ       |

| taco   | RAS to CAS Delay Time               | 25   | 55    | 25      | 70   | ns   | 7       |

| 1RSH   | RAS Hold Time                       | 85   |       | 105     |      | ns   |         |

| tcsH   | CAS Hold Time                       | 120  |       | 165     |      | ns   |         |

| TASA   | Row Address Set-Up Time             | 0    |       | 0       |      | ns   |         |

| trah   | Row Address Hold Time               | 15   |       | 15      |      | ns   |         |

| tasc   | Column Address Set-Up Time          | 0    |       | 0       |      | ns   | <u></u> |

| tCAH   | Column Address Hold Time            | 15   |       | 20      |      | ns   |         |

| tar    | Column Address Hold Time, to RAS    | 70   |       | 90      |      | ns   |         |

| tτ     | Transition Time (Rise and Fall)     | 3    | 50    | 3       | 50   | ns   | 8       |

| torr   | Output Buffer Turn Off Delay        | 0    | 50    | 0       | 60   | ns   |         |

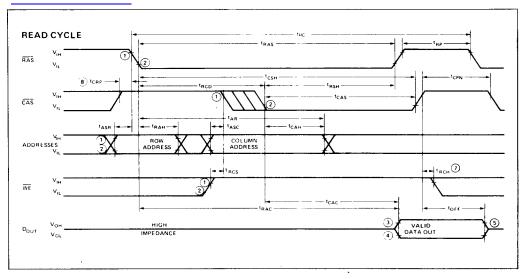

#### READ AND REFRESH CYCLES

| tac  | Random Read Cycle Time   | 270       | 320 |       | ns |  |

|------|--------------------------|-----------|-----|-------|----|--|

| tras | RAS Pulse Width          | 140 10000 | 175 | 10000 | ns |  |

| tcas | CAS Pulse Width          | 65 10000  | 95  | 10000 | ns |  |

| tacs | Read Command Set-Up Time | 0         | 0   |       | กร |  |

| tach | Read Command Hold Time   | 0         | 0   |       | ns |  |

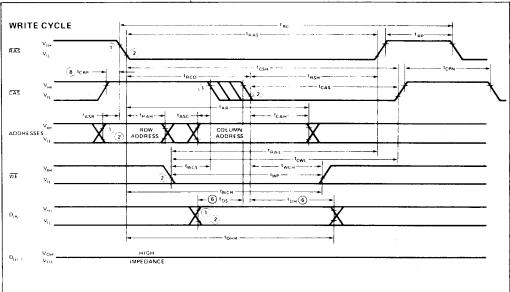

### WRITE CYCLE

| tac  | Random Write Cycle Time         | 270       | 320       | ns | <u> </u> |

|------|---------------------------------|-----------|-----------|----|----------|

| TRAS | RAS Pulse Width                 | 140 10000 | 175 10000 | ns |          |

| tcas | CAS Pulse Width                 | 65 10000  | 95 10000  | ns |          |

| twcs | Write Command Set-Up Time       | 0         | 0         | ns | 9        |

| twch | Write Command Hold Time         | 30        | 45        | ns | <u> </u> |

| twca | Write Command Hold Time, to RAS | 85        | 115       | ns |          |

| twp  | Write Command Pulse Width       | 30        | 50        | ns | <u> </u> |

| trwL | Write Command to RAS Lead Time  | 65        | 110       | ns |          |

| tcwL | Write Command to CAS Lead Time  | 50        | 100       | ns | <u></u>  |

| tos  | Data-In Set-Up Time             | 0         | 0         | ns | L        |

| tpH  | Data-In Hold Time               | 30        | 45        | ns |          |

| tons | Data-In Hold Time, to RAS       | 85        | 115       | ns |          |

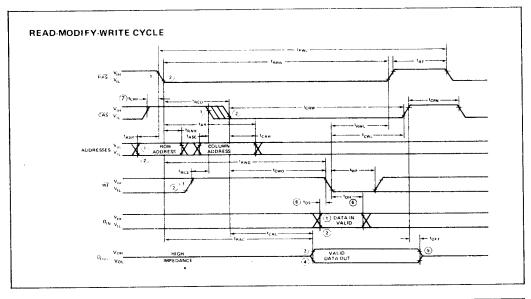

### **READ-MODIFY-WRITE CYCLE**

| tawc | Read-Modify-Write Cycle Time | 320 |       | 410 |       | ns |   |

|------|------------------------------|-----|-------|-----|-------|----|---|

| teew | RMW Cycle RAS Pulse Width    | 190 | 10000 | 265 | 10000 | ns |   |

| tcaw | RMW Cycle CAS Pulse Width    | 120 | 10000 | 185 | 10000 | ns |   |

| tawp | RAS to WE Delay              | 120 |       | 150 |       | ns | 9 |

| towp | CAS to WE Delay              | 65  |       | 80  |       | ns | 9 |

### NOTES:

- 1. All voltages referenced to V<sub>SS</sub>.

2. Eight cycles are required after power up or prolonged periods (greater than 2ms) of RAS inactivity before proper device operation is achieved. Any 8 cycles which perform refresh are adequate for this purpose.

- this purpose. 3. A.C. Characteristics assume  $I_T=5$ ns. 4. Assume that  $I_{RCD} \in I_{RCD}(max)$ . If  $I_{RCD}$  is greater than  $I_{RCD}$  (max.) then  $I_{RAC}$  will increase by the amount that  $I_{RCD}$  exceeds  $I_{RCD}$  (max.). 5. Load= 2 TTL loads and 100pF

- Assumes t<sub>RCD</sub>≥t<sub>RCD</sub> (max.).

- t<sub>BCD</sub>(max.) is specified as a reference point only. If t<sub>BCD</sub> is less than t<sub>BCD</sub> (max.) access time is t<sub>BCD</sub> + t<sub>BCD</sub>. If t<sub>BCD</sub> is greater than t<sub>BCD</sub> (max.) access time is t<sub>BCD</sub> + t<sub>BCD</sub>.

t<sub>T</sub> is measured between V<sub>IH</sub> (min.) and V<sub>IL</sub> (max.).

t<sub>WCS</sub> + t<sub>CWD</sub> and t<sub>BWD</sub> are specified as reference points only. If t<sub>WCS</sub> > t<sub>WCS</sub> (min.) the cycle is an early write cycle and the data out pin will remain high impedance throughout the entire cycle. If t<sub>CWD</sub> > t<sub>CWD</sub> (min.) the cycle is a read-modifywrite cycle and the data out will contain the data read from the selected address. If neither of the above conditions is satisfied the selected address. If neither of the above conditions is satisfied, the condition of the data out is indeterminate.

- 10. Case temperatures are "instant on.

3-34

### w查ver20fings共应商

1.2 VIH MIN AND VIL MAX ARE REFERENCE LEVELS FOR MEASURING TIMING OF INPUT SIGNALS

<sup>12</sup> V<sub>14</sub> MIN, AND V<sub>11</sub> MAX ARE REFERENCE LEVELS FOR MEASURING TIMING OF INDOIS 3/MALS 34 V<sub>104</sub> MIN, AND V<sub>11</sub> MAX ARE REFERENCE LEVELS FOR MEASURING TIMING OF D<sub>OUT</sub> 5 (OFF IS MEASURED TO I<sub>OUT</sub> < II<sub>1</sub>, OI 6 (OFF IS MEASURED TO I<sub>OUT</sub> < II<sub>1</sub>, OI 6 (OFF IS MEASURED TO I<sub>OUT</sub> < II<sub>1</sub>, OI 6 (OFF IS MEASURED TO THE TRAILING EDGE OF CAS OR MAS WHICHEVER OCCURS FIRST 1 RICH IS REFERENCED TO THE TRAILING EDGE OF CAS OR MAS WHICHEVER OCCURS FIRST 1 (OFF REQUIREMENT IS ONLY APPLICABLE FOR RAS CAS CYCLES PRECEDED BY A CAS ONLY OFF COLOR OF THE MEASURED COLOR OF THE MEASUR

## 查减收给6份数应商

NOTES 1.2 VIH MIN AND VIL MAX ARE REFERENCE LEVELS FOR MEASURING TIMING OF INPUT SIGNALS.

3.4 VOH MIN AND VIO, MAX ARE REFERENCE LEVELS FOR MEASURING TIMING OF DOILT 5. TOFF IS MEASURED TO JOUR 5 [1]C.

6 TOS AND JOH ARE REFERENCED TO CAS OR WE, WHICHEVER OCCURS LAST

- 7 top REQUIREMENT IS ONLY APPLICABLE FOR RASICAS CYCLES PRECEDED BY A CAS-ONLY CYCLE I.e., FOR SYSTEMS WHERE CAS HAS NOT BEEN DECODED WITH RASI