# 74VHC942 300 Baud Modem (+5V, -5V Supply)

### **General Description**

The 74VHC942 is a full duplex low speed modem. It provides a 300 baud bidirectional serial interface for data communication over telephone lines and other narrow bandwidth channels. It is Bell 103 compatible.

The 74VHC942 utilizes advanced silicon-gate CMOS technology. Switched capacitor techniques are used to perform analog signal processing.

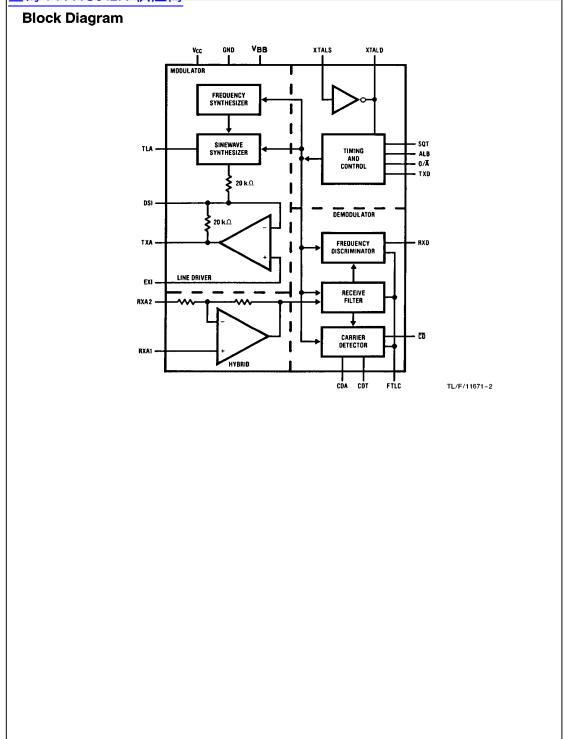

#### MODULATOR SECTION

The modulator contains a frequency synthesizer and a sine wave synthesizer. It produces a phase coherent frequency shift keyed (FSK) output.

#### LINE DRIVER AND HYBRID SECTION

The line driver and hybrid are designed to facilitate connection to a  $600\Omega$  phone line. They can perform two-to-fourwire conversion and drive the line at a maximum of 0 dBm.

#### DEMODULATOR SECTION

The demodulator incorporates anti-aliasing filters, a receive filter, limiter, discriminator, and carrier detect circuit. The nine pole receive filter provides 60 dB of transmitted tone rejection. The discriminator is fully balanced for stable operation.

| F | е | a | t | u | r | e | S |  |

|---|---|---|---|---|---|---|---|--|

|   |   |   |   |   |   |   |   |  |

- ±5V supplies ■ Drives 600Ω at 0 dBm

- All filters on chip

- Transmit level adjustment compatible with universal service order code

PRELIMINARY

October 1995

- TTL and CMOS compatible logic

- All inputs protected against static damage

- Low power consumption

- Full duplex answer or originate operation

- Analog loopback for self test Power down mode

- Direct pin and function replacement for the 74HC942

#### Applications

- Built-in low speed modems

- Remote data collection

- Radio telemetry

- Credit verification

- Stand-alone modems

- Point-of-sale terminals

- Tone signalling systems

- Remote process control

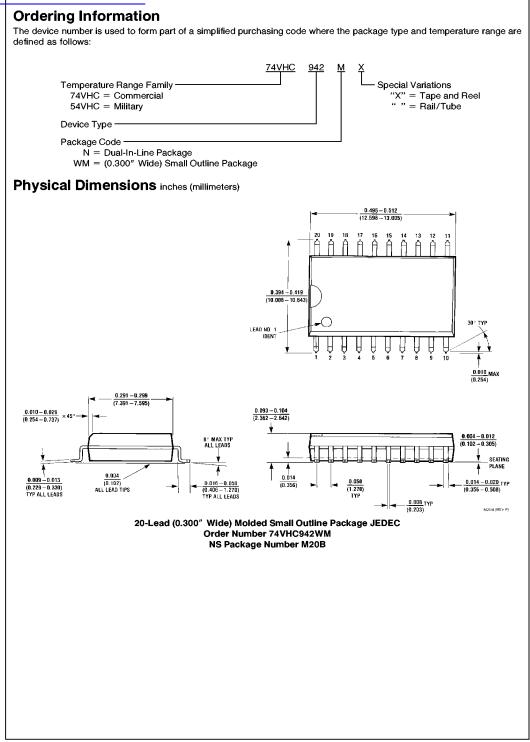

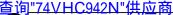

| Commercial | Package Number | Package Description                     |

|------------|----------------|-----------------------------------------|

| 74VHC942WM | M20B           | 20-Lead Molded JEDEC SOIC (0.300" Wide) |

| 74VHC942N  | N20A           | 20-Lead Molded DIP                      |

Note: Surface mount packages are also available on Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

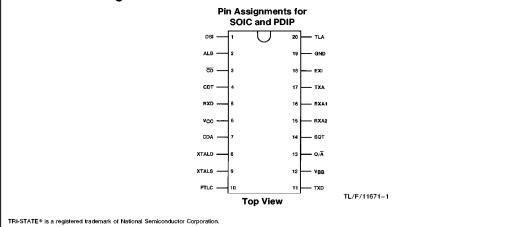

### **Connection Diagram**

© 1995 National Semiconductor Corporation TL/F/11671

RRD-B30M125/Printed in U. S. A

#### **Description of Pin Functions** Pin Pin Name Function Name Function No. No. DSI Driver Summing Input: This may be used to 1 receive filter. It may thus be used to evalutransmit externally generated tones such as ate filter performance. This pin may also be dual tone multifrequency (DTMF) dialing sigdriven to evaluate the demodulator. RXA1 nals. and RXA2 must be grounded during this 2 ALB Analog Loop Back: A logic high on this pin test. causes the modulator output to be connect-For normal modem operation FTLC is AC ed to the demodulator input so that data is grounded via a 0.1 $\mu$ F bypass capacitor. looped back through the entire chip. This is TXD Transmitted Data: This is the data input. 11 used as a chip self test. If ALB and SQT are 12 $V_{BB}$ Negative Supply: The recommended supply simultaneously held high the chip powers is -5V. down. O/Ā Originate/Answer mode select: When logic CD 13 з Carrier Detect: This pin goes to a logic low high this pin selects the originate mode of when carrier is sensed by the carrier detect operation. circuit. 14 SQT Squelch Transmitter: This disables the mod-CDT Carrier Detect Timing: A capacitor on this 4 ulator when held high. The EXI input repin sets the time interval that the carrier mains active. If SQT and ALB are simultamust be present before the $\overline{CD}$ goes low. neously held high the chip powers down. 5 RXD Received Data: This is the data output pin. 15 RXA2 Receive Analog #2: RXA2 and RXA1 are 6 $V_{\text{CC}}$ Positive Supply Pin: A + 5V supply is recomanalog inputs. When connected as recommended. mended they produce a $600\Omega$ hybrid. CDA Carrier Detect Adjust: This is used for ad-7 16 RXA1 Receive Analog #1: See RXA2 for details. justment of the carrier detect threshold. Car-Transmit Analog: This is the output of the rier detect hysteresis is set at 3 dB. 17 TXA 8 XTALD Crystal Drive: XTALD and XTALS connect line driver. to a 3.5795 MHz crystal to generate a crys-EXI External Input: This is a high impedance in-18 tal locked clock for the chip. If an external put to the line driver. This input may be used circuit requires this clock XTALD should be to transmit externally generated tones. sensed. If a suitable clock is already avail-When not used for this purpose it should be able in the system, XTALD can be driven. grounded. XTALS Crystal Sense: Refer to Pin 8 for details. 9 GND Ground: This defines the chip 0V. 19 Filter Test/Limiter Capacitor: This is con-10 FTLC 20 TLA Transmit Level Adjust: A resistor from this nected to a high impedance output of the pin to V<sub>CC</sub> sets the transmit level.

З

### <u>查询"74VHC942N"供应商</u>

### **Functional Description**

#### INTRODUCTION

A modem is a device for transmitting and receiving serial data over a narrow bandwidth communication channel. The 74VHC942 uses frequency shift keying (FSK) of an audio frequency tone. The tone may be transmitted over the switched telephone network and other voice grade channels. The 74VHC942 is also capable of demodulating FSK signals. By suitable tone allocation and considerable signal processing the 74VHC942 is capable of transmitting and receiving data simultaneously.

The tone allocation by the 74VHC942 and other Bell 103 compatible modems is shown in Table I. The terms "originate" and "answer" which define the frequency allocation come from use with telephones. The modem on the end of the line which initiates the call is called the originate modem. The other modem is the answer modem.

| TABLE I. BELL 103 Allo | ocation |

|------------------------|---------|

|------------------------|---------|

| Data  | Originate | Modem   | Answer Modem |         |  |

|-------|-----------|---------|--------------|---------|--|

| Data  | Transmit  | Receive | Transmit     | Receive |  |

| Space | 1070 Hz   | 2025 Hz | 2025 Hz      | 1070 Hz |  |

| Mark  | 1270 Hz   | 2225 Hz | 2225 Hz      | 1270 Hz |  |

#### THE LINE INTERFACE

The line interface section performs two to four wire conversion and provides impedance matching between the modem and the phone line.

#### THE LINE DRIVER

The line driver is a power amplifier for driving the line. If the modem is operating as an originate modem, the second harmonics of the transmitted tones fall close to the frequencies of the received tones and degrade the received signal to noise ratio (SNR). The line driver must thus produce low second harmonic distortion.

#### THE HYBRID

The voltage on the telephone line is the sum of the transmitted and received signals. The hybrid subtracts the transmitted voltage from the voltage on the telephone line. If the telephone line was matched to the hybrid impedance, the output of the hybrid would be only the received signal. This rarely happens because telephone line characteristic impedances vary considerably. The hybrid output is thus a mixture of transmitted and received signals.

#### THE DEMODULATOR SECTION

#### The Receive Filter

The demodulator recovers the data from the received signals. The signal from the hybrid is a mixture of transmitted signal, received signals and noise. The first stage of the receive filter is an anti-alias filter which attenuates high frequency noise before sampling occurs. The signal then goes to the second stage of the receive filter where the transmitted tones and other noise are filtered from the received signal. This is a switched capacitor nine-pole filter providing at least 60 dB of transmitted tone rejection. This also provides high attenuation at 60 Hz, a common noise component.

#### The Discriminator

The first stage of the discriminator is a hard limiter. The hard limiter removes from the received signal any amplitude modulation which may bias the demodulator toward a mark or a space. It compares the output of the receive filter to the voltage on the 0.1  $\mu F$  capacitor on the FTLC pin.

The hard limiter output connects to two parallel bandpass filters in the discriminator. One filter is tuned to the mark frequency and the other to the space frequency. The outputs of these filters are rectified, filtered and compared. If the output of the mark path exceeds the output of the space path the RXD output goes high. The opposite case sends RXD low.

The demodulator is implemented using precision switched capacitor techniques. The highly critical comparators in the limiter and discriminator are auto-zeroed for low offset.

#### **Carrier Detector**

The output of the discriminator is meaningful only if there is sufficient carrier being received. This is established in the carrier detection circuit which measures the signal on the line. If this exceeds a certain level for a preset period (adjustable by the CDT pin) the  $\overline{CD}$  output goes low indicating that carrier is present. Then the carrier detect threshold is lowered by 3 dB. This provides hysteresis ensuring the  $\overline{CD}$  output remains stable. If carrier is lost  $\overline{CD}$  goes high after the preset delay and the threshold is increased by 3 dB.

#### MODULATOR SECTION

The modulator consists of a frequency synthesizer and a sine wave synthesizer. The frequency produces one of four tones depending on the  $O/\overline{A}$  and TXD pins. The frequencies are synthesized to high precision using a crystal oscillator and variable dual modulus counter. The counters used respond quickly to data changes, introducing negligible bit jitter while maintaining phase coherence.

The sine wave synthesizer uses switched capacitors to "look up" the voltages of the sine wave. This sampled signal is then further processed by switched capacitor and continuous filters to ensure the high spectral purity required by FCC regulations.

| Absolute Maximum                                         | Ratings (Notes 1 & 2)             | Recommended Op                                                 | peratir | ng              |       |

|----------------------------------------------------------|-----------------------------------|----------------------------------------------------------------|---------|-----------------|-------|

| Supply Voltage (V <sub>CC</sub> )                        | -0.5 to +7.0V                     | Conditions                                                     |         | -               |       |

| Supply Voltage (V <sub>BB</sub> )                        | +0.5 to -7.0V                     |                                                                | Min     | Max             | Units |

| DC Input Voltage (V <sub>IN</sub> )                      | $V_{BB}$ – 1.5 to $V_{CC}$ + 1.5V | Supply Voltage (V <sub>CC</sub> )                              | 4.5     | 5.5             | V     |

| DC Output Voltage (V <sub>OUT</sub> )                    | $V_{BB}$ – 0.5 to $V_{CC}$ + 0.5V | Supply Voltage (V <sub>BB</sub> )                              | -4.5    | -5.5            | V     |

| Clamp Diode Current (I <sub>IK</sub> , I <sub>OK</sub> ) | ±20 mA                            | DC Input or Output Voltage                                     | 0       | V <sub>CC</sub> | V     |

| DC Output Current, per pin (IOUT                         | ·) ±25 mA                         | (V <sub>IN</sub> , V <sub>OUT</sub> )                          |         |                 |       |

| DC V <sub>CC</sub> or GND Current, per pin               | (I <sub>CC</sub> ) ±50 mA         | Operating Temp. Range (T <sub>A</sub> )                        |         |                 |       |

| Storage Temperature Range (Te                            | GTG) −65°C to +150°C              | 74VHC                                                          | -40     | +85             | °C    |

| Power Dissipation (P <sub>D</sub> )<br>(Note 3)          | 600 mW                            | Input Rise or Fall Times<br>(t <sub>r</sub> , t <sub>f</sub> ) |         | 500             | ns    |

| S.O. Package only                                        | 500 mW                            | Crystal frequency                                              |         | 3.579           | MHz   |

| Lead Temp. (T <sub>L</sub> )<br>(Soldering 10 seconds)   | 260°C                             |                                                                |         |                 |       |

### **DC Electrical Characteristics**

| Symbol                            | Parameter                                                  | Conditions                                                                                                              | 74VHC<br>T = 25°C |                              | 74VHC<br>T = −40 to 85°C    | Units  |

|-----------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------|-----------------------------|--------|

| -                                 |                                                            |                                                                                                                         | Тур               | Guara                        | nteed Limits                |        |

| VIH                               | Minimum High Level<br>Input Voltage                        |                                                                                                                         |                   | 3.15                         | 3.15                        | V      |

| VIL                               | Maximum Low Level<br>Input Voltage                         |                                                                                                                         |                   | 1.1                          | 1.1                         | V      |

| V <sub>OH</sub>                   | Minimum High Level<br>Output Voltage                       | $V_{IN} = V_{IL} \text{ or } V_{IL}$ $ I_{OUT}  = 20 \ \mu\text{A}$ $ I_{OUT}  = 4.0 \text{ mA}, V_{CC} = 4.5 \text{V}$ | V <sub>CC</sub>   | V <sub>CC</sub> -0.1<br>3.98 | V <sub>CC</sub> -0.1<br>3.7 | v<br>v |

| V <sub>OL</sub>                   | Maximum Low Level<br>Voltage                               | $V_{IN} = V_{IH} \text{ or } V_{IL}$ $ I_{OUT}  = 20 \ \mu\text{A}$ $ I_{OUT}  = 4.0 \text{ mA}, V_{CC} = 4.5 \text{V}$ |                   | 0.1<br>0.26                  | 0.1<br>0.4                  | v<br>v |

| I <sub>IN</sub>                   | Maximum Input<br>Cu <b>rr</b> ent                          | $V_{IN} = V_{CC}$ or GND                                                                                                |                   | ±0.1                         | ± 1.0                       | μΑ     |

| I <sub>OZ</sub>                   | Output TRI-STATE®<br>Leakage Current<br>RXD and CD Outputs | ALB=SQT=V <sub>CC</sub>                                                                                                 |                   |                              | ±5                          | μΑ     |

| I <sub>CC</sub> , I <sub>BB</sub> | Maximum Quiescent<br>Supply Current                        | $V_{IH} = V_{CC}, V_{IL} = GND$<br>ALB or SQT = GND<br>Transmit Level = -9 dBm                                          | 8.0               | 12.0                         | 12.0                        | mA     |

| I <sub>CC</sub> , I <sub>BB</sub> | Power Down Supply Current                                  | $ALB = SQT = V_{CC}$ $V_{IH} = V_{CC}, V_{IL} = GND$                                                                    |                   |                              | 300                         | μΑ     |

Note 1: Absolute Maximum Ratings are those values beyond which damage to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temperature derating - plastic "N" package: -12 mW/°C from 65°C to 85°C.

# <u>查询"74VHC942N"供应商</u>

| Symbol         | Parameter                                                                                  | Co                    | nditions                                | Min           | Тур             | Max            | Unit       |

|----------------|--------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------|---------------|-----------------|----------------|------------|

| TRANSMI        | TTER                                                                                       |                       |                                         |               |                 |                |            |

| -<br>CE        | Carrier Frequency Error                                                                    |                       |                                         |               |                 | 4              | Hz         |

|                | Power Output                                                                               | $V_{CC} = 5.0V$       | $R_{TLA} = 0\Omega$                     | -3            | - 1.5           | 0              | dBn        |

|                |                                                                                            | $R_L = 1.2 k\Omega$   | $R_{TLA} = 5.49  k\Omega$               | - 12          | - 10.5          | -9             | dBn        |

|                | 2nd Harmonic Energy                                                                        |                       | $R_{TLA} = 0\Omega$                     |               | -62             | - 56           | dBn        |

| RECEIVE        | FILTER AND HYBRID                                                                          |                       |                                         |               |                 |                |            |

|                | Hybrid Input Impedance<br>(Pins 15 and 16)                                                 |                       |                                         | 50            |                 |                | kΩ         |

|                | FTLC Output Impedance                                                                      |                       |                                         | 5             | 10              | 50             | kΩ         |

|                | Adjacent Channel Rejection                                                                 |                       | TXA=GND or V <sub>CC</sub><br>t to RXA1 | 60            |                 |                | dB         |

| DEMODUL        | ATOR (INCORPORATING HYBR                                                                   | ID, RECEIVE FIL       | TER AND DISCRIMINA                      | ATOR)         |                 |                |            |

|                | Carrier Amplitude                                                                          |                       |                                         | -38           |                 | -9             | dBn        |

|                | Bit Jitter                                                                                 | Input :               | R = 30 dB<br>= -38 dBm<br>= 300 Baud    |               | 100             | 200            | μS         |

|                | Bit Bias                                                                                   | Alternating 1-0       | Pattern                                 |               | 5               | 10             | %          |

|                | Carrier Detect Trip Points                                                                 | CDA = 1.2V            | Off to On                               | -38           | -37             | -34            | dBn        |

|                |                                                                                            | $V_{\rm CC} = 5.0V$   | On to Off                               | -41           | -40             | -37            | dBr        |

|                | Carrier Detect Hysteresis                                                                  | V <sub>CC</sub> =5V   |                                         | 2             | 3               | 4              | dB         |

| better than th | ulator specifications apply to the 74VHC94<br>e 74VHC942 modulator.<br>ecification Circuit | 2 operating with a mo | dulator having frequency acc            | curacy, phase | jitter and harm | onic content ( | equal to a |

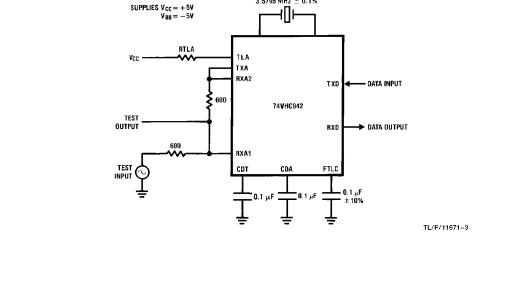

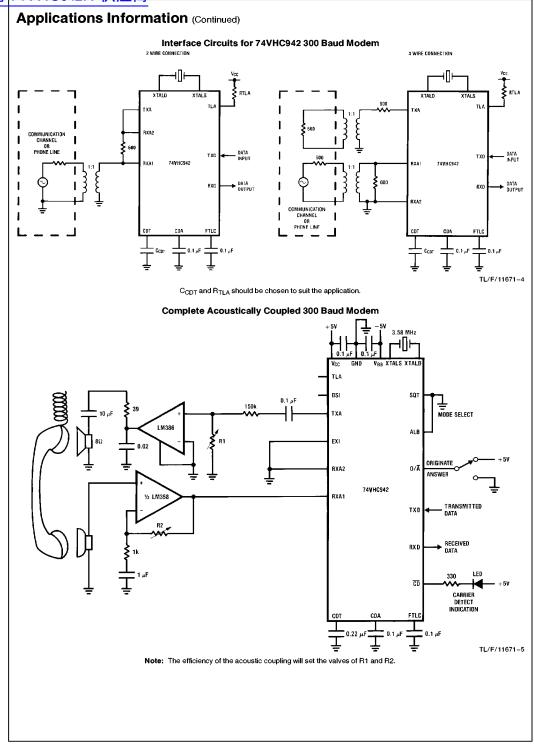

### Applications Information

#### TRANSMIT LEVEL ADJUSTMENT

The transmitted power levels of Table II refer to the power delivered to a 600 load from the external 600  $\Omega$  source impedance. The voltage on the load is half the TXA voltage. This should be kept in mind when designing interface circuits which do not match the load and source impedances. The transmit level is programmable by placing a resistor from TLA to VCC. With a 5.5k resistor the line driver transmits a maximum of -9 dBm. Since most lines from a phone installation to the exchange provide 3 dB of attenuation the maximum level reaching the exchange will be -12 dBm. This is the maximum level permitted by most telephone companies. Thus with this programming the 74VHC942 will interface to most telephones. This arrangement is called the "permissive arrangement." The disadvantage with the permissive arrangement is that when the loss from a phone to the exchange exceeds 3 dB, no compensation is made and SNR may be unnecessarily degraded.

SNR can be maximized by adjusting the transmit level until the level at the exchange reaches -12 dBm. This must be done with the cooperation of the telephone company. The programming resistor used is specific for a given installation and is often included in the telephone jack at the installation. The modem is thus programmable and can be used with any jack correctly wired. This arrangement is called the universal registered jack arrangement and is possible with the 74VHC942. The values of resistors required to program the 74VHC942 follow the most common code in use; the universal service order code. The required resistors are given in Table II.

#### TABLE II. Universal Service Order Code Resistor Values

| Transmit<br>Level<br>(dBm) | Programming<br>Resistor (R <sub>TLA</sub> )<br>(Ohms)                                          |  |  |  |  |  |

|----------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| - 12                       | Open                                                                                           |  |  |  |  |  |

| -11                        | 19,800                                                                                         |  |  |  |  |  |

| - 10                       | 9,200                                                                                          |  |  |  |  |  |

| -9                         | 5,490                                                                                          |  |  |  |  |  |

| -8                         | 3,610                                                                                          |  |  |  |  |  |

| -7                         | 2,520                                                                                          |  |  |  |  |  |

| -6                         | 1,780                                                                                          |  |  |  |  |  |

| -5                         | 1,240                                                                                          |  |  |  |  |  |

| -4                         | 866                                                                                            |  |  |  |  |  |

| -3                         | 562                                                                                            |  |  |  |  |  |

| -2                         | 336                                                                                            |  |  |  |  |  |

| -1                         | 150                                                                                            |  |  |  |  |  |

| 0                          | 0                                                                                              |  |  |  |  |  |

|                            | Level<br>(dBm)<br>- 12<br>- 11<br>- 10<br>- 9<br>- 8<br>- 7<br>- 6<br>- 5<br>- 5<br>- 4<br>- 3 |  |  |  |  |  |

#### CARRIER DETECT THRESHOLD ADJUSTMENT

The carrier detect threshold is directly proportional to the voltage on CDA. This pin is connected internally to a high impedance source. This source has a nominal Thevenin equivalent voltage of 1.2V and output impedance of 100 k $\Omega$ . By forcing the voltage on CDA the carrier detect threshold may be adjusted. To find the voltage required for a given threshold the following equation may be used;

$V_{CDA} = 244 \times V_{ON}$  $V_{CDA} = 345 \times V_{OFF}$

### CARRIER DETECT TIMING ADJUSTMENT

CDT: A capacitor on Pin 4 sets the time interval that the carrier must be present before CD goes low. It also sets the time interval that carrier must be removed before CD returns high. The relevant timing equations are:

$T_{\overline{CDL}} \cong 6.4 \times C_{\overline{CDT}}$  for  $\overline{CD}$  going low

$T_{\overline{CDH}} \cong 0.54 \times C_{CDT}$  for  $\overline{CD}$  going high

Where T<sub>CDL</sub> & T<sub>CDH</sub> are in seconds, and C<sub>CDT</sub> is in  $\mu$ F.

#### **DESIGN PRECAUTIONS**

Power supplies to digital systems may contain high amplitude spikes and other noise. To optimize performance of the 74VHC942 operating in close proximity to digital systems, supply and ground noise should be minimized. This involves attention to power supply design and circuit board layout. Power supply decoupling close to the device is recommended. Ground loops should be avoided. For further discussion of these subjects see the Audio/Radio Handbook published by National Semiconductor Corporation.

# 查询"<u>74VHC942N"供应商</u>

Powered by ICminer.com Electronic-Library Service CopyRight 2003