National Semiconductor

## LM1818 Electronically Switched Audio Tape System

### **General Description**

Features

- Electronic record/play switching

- 85 dB power supply rejection

- Motional peak level meter circuitry

- Low noise preamplifier circuitry

3.5V to 18V supply operation

- Solved ray supply operation

Provision for external low noise input transistor

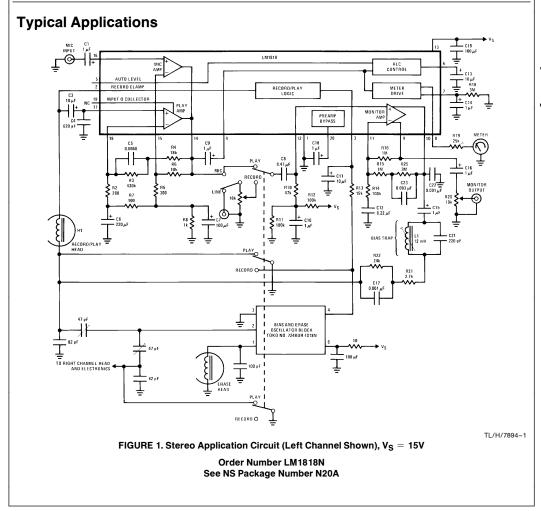

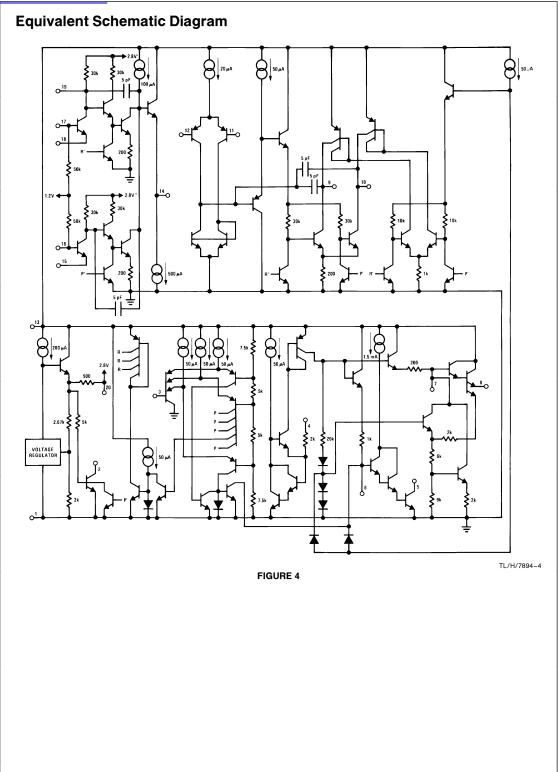

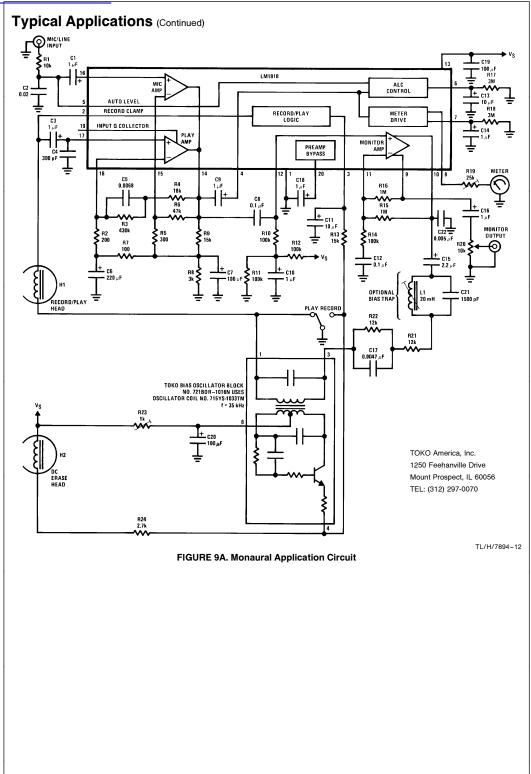

active electronics necessary for building a tape recorder deck (excluding the bias oscillator). The electronic functions on the chip include: a microphone and playback preamplifier, record and playback amplifiers, a meter driving circuit, and an automatic input level control circuit. The IC features complete internal electronic switching between the record and playback modes of operation. The multipole switch used in previous systems to switch between record and playback modes is replaced by a single pole switch, thereby allowing for more flexibility and reliability in the recorder design.\*

The LM1818 is a linear integrated circuit containing all of the

\*Monaural operation, Figure 9.

© 1995 National Semiconductor Corporation TL/H/7894

RRD-B30M115/Printed in U. S. A.

LM1818 Electronically Switched Audio Tape System

April 1987

| Absolute Maximum R                  | atings                |                                       |                                |

|-------------------------------------|-----------------------|---------------------------------------|--------------------------------|

| If Military/Aerospace specified     | devices are required, | Operating Temperature                 | $0^{\circ}C$ to $+70^{\circ}C$ |

| please contact the National         |                       | Junction Temperature                  | 150°C                          |

| Office/Distributors for availabilit | y and specifications. | Minimum Voltage on Any Pin            | -0.1 V <sub>DC</sub>           |

| Supply Voltage                      | 18V                   | Maximum Voltage on Pins 2 and 5       | 0.1 V <sub>DC</sub>            |

| Package Dissipation, (Note 1)       | 1560 mW               | Maximum Current Out of Pin 14         | 5 mA <sub>DC</sub>             |

| Storage Temperature                 | -65°C to +150°C       | Lead Temperature (Soldering, 10 sec.) | 260°C                          |

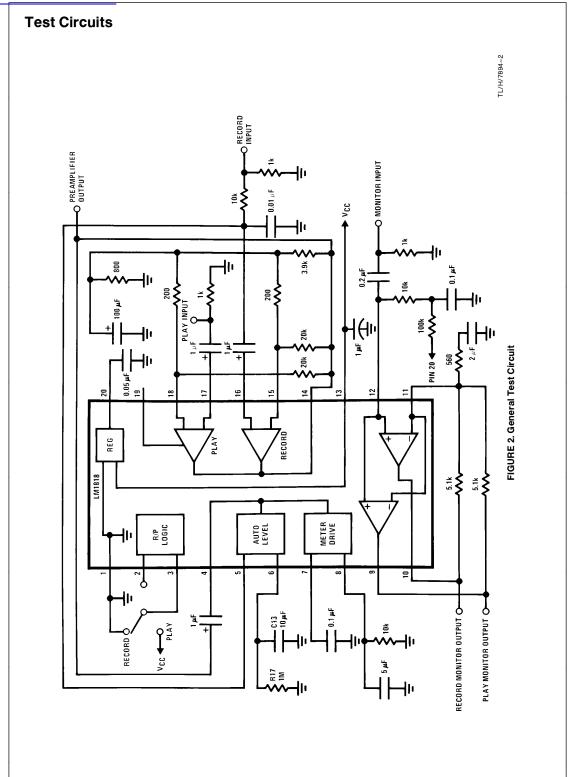

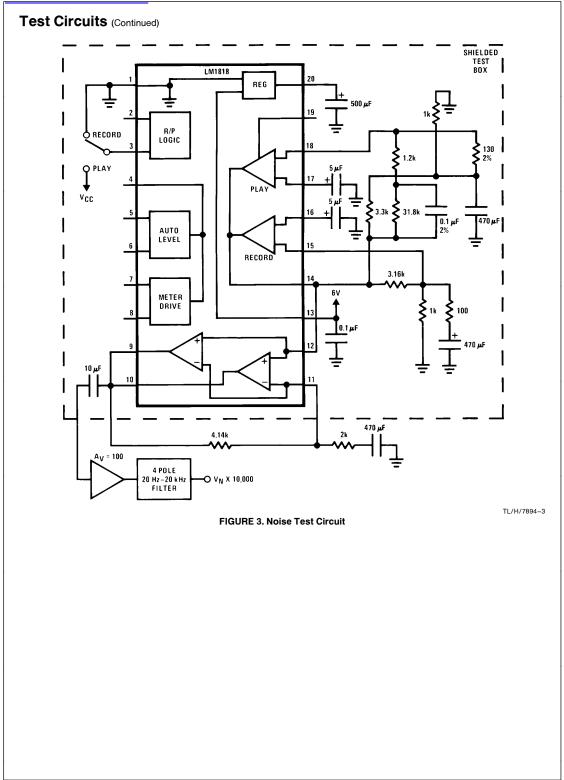

## **Electrical Characteristics** $V_{CC} = 6V$ , $T_A = 25^{\circ}C$ , See Test Circuits (*Figures 2* and *3*)

| Parameter                                                                          | Conditions                                                                                           | Min         | Тур            | Max            | Units           |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------|----------------|----------------|-----------------|

| Operating Supply Voltage Range                                                     |                                                                                                      | 3.5         |                | 18             | V <sub>DC</sub> |

| Supply Current                                                                     | Test Circuit <i>(Figure 2)</i>                                                                       |             | 5              | 12             | mA              |

| Turn-ON Time                                                                       | Externally Programmable                                                                              | 50          | 400            |                | ms              |

| Playback Signal to Noise                                                           | DIN Eq. (3180 and 120 $\mu s$ ), 20–20 kHz, $R_S=$ 0, Unweighted, $V_{REF}=$ 1 mV at 400 Hz          |             | 74             |                | dB              |

| Record Signal to Noise                                                             | Flat Gain, 20–20 kHz, R <sub>S</sub> =0,<br>ALC OFF, V <sub>REF</sub> = 1 mV<br>at 1 kHz, Unweighted |             | 69             |                | dB              |

| Fast Turn-ON Charging Current                                                      | Pins 16 and 17                                                                                       |             | 200            |                | μΑ              |

| Record and Playback Preamplifier<br>Open Loop Voltage Gain                         | f = 100 Hz                                                                                           |             | 100            |                | dB              |

| Preamplifier Input Impedance                                                       | Pin 16 or Pin 17                                                                                     |             | 50             |                | kΩ              |

| Preamplifier Input Referred PSRR                                                   | 1 kHz — Flat Gain                                                                                    |             | 85             |                | dB              |

| Bias Voltage on Pin 18 in Play Mode<br>or Pin 15 in Record Mode                    |                                                                                                      |             | 0.5            |                | v               |

| Monitor Amplifier Input<br>Bias Current                                            | Pins 11 and 12                                                                                       |             | 0.5            |                | μA              |

| Monitor Amplifier Open<br>Loop Voltage Gain                                        | Record or Playback, f = 100 Hz                                                                       |             | 80             |                | dB              |

| Monitor Output Current Capability                                                  | Pins 9 and 10, Source Current Available                                                              | 400         | 750            |                | μA              |

| Monitor Amplifier Output Swing                                                     | $R_L = 10k$ , AC Load                                                                                | 1.2         | 1.65           |                | Vrms            |

| THD, All Amplifiers                                                                | At 1 kHz, 40 dB Closed Loop Gain                                                                     |             | 0.05           |                | %               |

| Record-Playback Switching Time                                                     | As in Test Circuit                                                                                   |             | 50             |                | ms              |

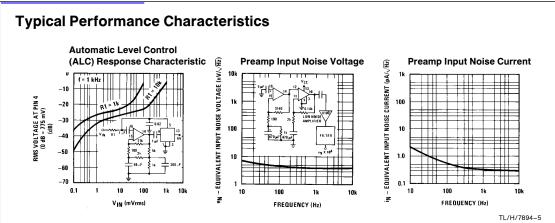

| Input ALC Range                                                                    | $\Delta V_{IN}$ for $\Delta V_{OUT} = 8 \text{ dB}$                                                  |             | 40             |                | dB              |

| Input Voltage on ALC Pin for<br>Start of ALC Action                                |                                                                                                      |             | 25             |                | mVrm            |

| ALC Input Impedance                                                                |                                                                                                      |             | 2              |                | kΩ              |

| ALC Attack Time                                                                    | $C13 = 10 \ \mu F$                                                                                   |             | 7              |                | ms              |

| ALC Decay Time                                                                     | R17 = $\infty$ , C13 = 10 $\mu$ F                                                                    |             | 30             |                | sec             |

| Meter Output Gain                                                                  | 100 mVrms at 1 kHz into Pin 4                                                                        |             | 800            |                | mV <sub>D</sub> |

| Meter Output Current Capability                                                    |                                                                                                      | 2           |                |                | mA <sub>D</sub> |

| Note 1: For operation in ambient temperatures ab<br>of 80°C/W junction to ambient. | ove 25°C, the device must be derated based on a 150°C m                                              | aximum junc | tion temperatu | re and a thern | nal resistan    |

3

# 查询"<u>LM1818"供应商</u>

### **Application Hints**

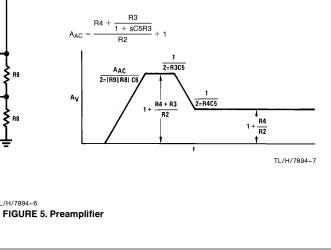

#### PREAMPLIFIERS (Figure 5)

0<sup>20</sup>

19 1 2

18

0.5 VDC

R2

0<sup>16</sup>

50k

1.2V

There are 2 identical preamplifiers with 1 common output pin on the IC. One amplifies low level inputs such as a microphone in the record mode and another amplifies the signal from the playback head in the playback mode. The amplifiers use a common capacitor, C6, to set the low frequency pole of the closed loop responses. On the playback amplifier, the collector of the input device is made available so that an external low noise device can be connected in critical applications. When using an external low noise transistor, pins 17 and 18 of the IC are shorted together to ensure that the internal input transistor is turned OFF and the external transistor's collector is tied to pin 19. The input and feedback connections are now made to the external input

зv

V+(QUIESCENT) = 0.5 VDC

PLAY O

REC

and have a typical open loop gain of 100 dB. R8 and R9 enable C6 to be quickly charged and set the DC gain. Internal biasing provides a DC voltage independent of temperature at pin 17 so that the preamplifier DC output will remain relatively constant with temperature. Supply decoupling is provided by an internal regulator. Additional decoupling can be added for the input stages by increasing the size of the capacitor on pin 20 of the IC. A fast charging circuit is connected to the preamplifiers' input capacitors (pins 16 and 17) to decrease the turn-ON time. Larger input capacitors decrease the noise by reducing the source impedance at lower frequencies where 1/f noise current produces an input noise voltage. The input resistance of the preamplifiers is typically 50 k $\Omega$ .

transistor. The amplifiers are stable for all gains above 5

#### Quiescent DC Output Voltage

$\left(1 + \frac{R9}{R8}\right)$  (0.5-50×10<sup>-6</sup>R2)V if R2+R3>10 R<sub>E</sub>

where

$$R_E = \frac{R8R9}{R8 + R9}$$

AC Voltage Gain

► V<sub>CC</sub>

A REC

6

TL/H/7894-6

### Application Hints (Continued)

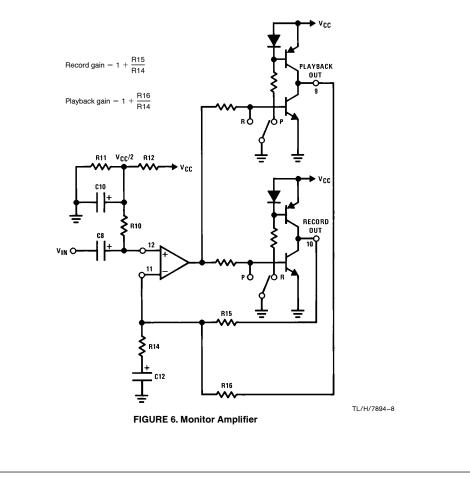

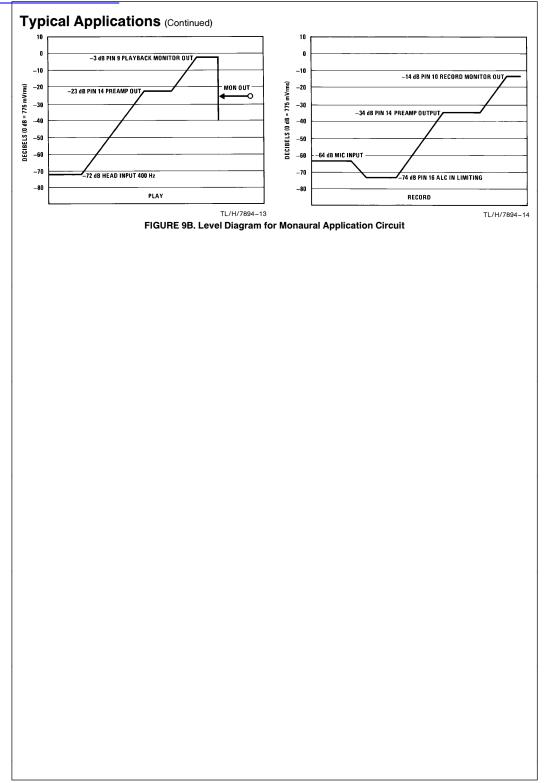

#### MONITOR AND RECORD AMPLIFIERS (Figure 6)

The monitor and record amplifiers share common input and feedback connections but have separate outputs. During playback, the input signal is amplified and appears only at the playback monitor output. Because the outputs are separate, different feedback components can be used and, as a result, totally different responses can be set. The amplifiers are stable for all closed loop gains above 3 and have an open loop gain of typically 80 dB. The outputs are capable of supplying a minimum of 400  $\mu$ A into a load and swing within 500 mV of either V<sub>CC</sub> or ground. If more than 400  $\mu$ A is needed to drive a load, an external pull-up resistor on the output of these amplifiers can increase the load driving capability.

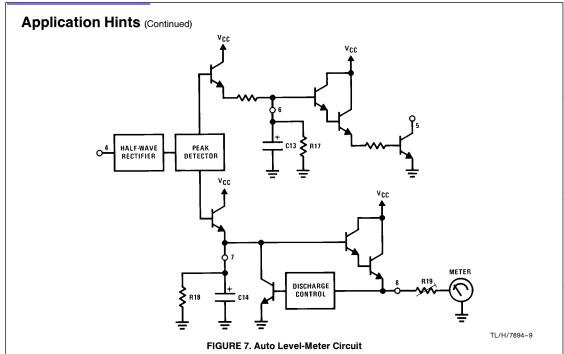

#### AUTOMATIC LEVEL CONTROL—ALC (Figure 7)

The automatic level control provides a constant output level for a wide range of record source input levels. The ALC works on the varying impedance characteristic of a saturated transistor. The impedance of the saturated transistor forms a voltage divider with the source impedance of a series resistor (R1 in *Figure 9*). The input signal is decreased as the ALC transistor is increasingly forward biased. The ALC transistor will be forward biased when the preamplifiers's AC output (pin 14), coupled to the combination ALC-meter drive input (pin 4) reaches 40 mV peak (25 mVrms). The gain of the ALC loop is such that a preamp input signal increase of 10 dB will result in a 2 dB increase on the AC output of the preamplifier. If greater than 25 mVrms is desired at the output of the preamp output coupling capacitor and the ALC input (pin 4). The input impedance of the ALC circuit is 2 k\Omega; therefore, if a 2 k\Omega series resistor is added, ALC action will begin at 50 mVrms.

The ALC memory capacitor connected to pin 6 has the additional function of amplifier anti-pop control; for this reason, it is necessary that a capacitor be connected to pin 6 even if ALC is not used.

#### METER DRIVING—MOTIONAL PEAK LEVEL RESPONSE (Figure 7)

The meter drive output (pin 8) is capable of supplying 1-2 mA at a filtered DC voltage that is typically equal to 10 times the RMS value of the signal applied to the ALC-meter drive input (pin 4). The RC network connected to pin 7 of the IC determines the memory constant of the meter circuit. It is therefore possible to store the peak input signal by giving this RC network a long time constant, or read the instantaneous signal level by giving this RC network a very short time constant (i.e., no capacitor). This memory capacitor is discharged within the integrated circuit at a discharge rate related to the DC level on the meter output pin. When the

meter output pin is between 0 V<sub>DC</sub> and 0.7 V<sub>DC</sub> there is a 50  $\mu$ A discharge current; when the pin is between 0.7V and 1.1V there is no internal discharge current; and when the voltage on pin 8 is greater than 1.1V there is a discharge equivalent to a 3.3k resistor across the memory capacitor. These different discharge rates allow the meter circuit to display fast, accurate responses on the lower portion of the meter display, slow responses in the higher portion of the meter display, and rapid discharge when the voltage is above the maximum reading the meter can display. The resistor in series with the meter can be adjusted such that the previously mentioned responses coincide with the proper points (0 VU and +3 VU) on the meter scale.

### Application Hints (Continued)

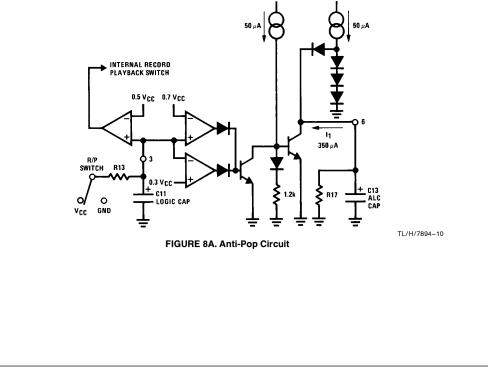

#### Anti-Pop Circuitry (Figure 8)

The capacitor on pin 3 is used in a time delay system in conjunction with C13, the ALC capacitor, to suppress pops when switching between record and playback. Figure 8 illustrates how this is done. The output amplifier, either record or playback, is shut off prior to switching and carefully rebiased after switching takes place. It is therefore required that a proper ratio is selected between the ALC capacitor and the logic input RC time constant. The ALC capacitor must be discharged to 0.7V within the time it takes the logic input capacitor to: 1) charge from  $V_{CC}/2$  to 0.7  $V_{CC}$  when switching from record to playback, or 2) discharge from  $V_{CC}/2$  to  $0.3 V_{CC}$  when switching from playback to record. These times would normally be similar; however, the ALC capacitor can be charged to a different initial value depending upon the input to the ALC circuit. The maximum value to which the ALC memory capacitor will normally charge is 3.2V, therefore, the maximum time allowed for discharging C13 is aiven by:

t1 =

$$\frac{(C13 \times \Delta V)}{I_1}$$

= C13  $\frac{(3.2V - 0.7V)}{350 \,\mu A}$

= C13 × 7.2 × 104

If C13 = 10  $\mu$ F, t1 = 72 ms

ow poccessory to determine the minimum value

It is now necessary to determine the minimum value for the R/P logic capacitor. This is done by computing the time between the 2 voltage switching points using the exponential equations for a single RC network.

$$\begin{aligned} t2 &= \text{R13 C11 In} \left[ \frac{\text{V}_{\text{CC}}}{0.3 \text{ V}_{\text{CC}}} \right] - \\ \text{R13 C11 In} \left[ \frac{\text{V}_{\text{CC}}}{0.5 \text{ V}_{\text{CC}}} \right] = 0.51 \text{ R13 C11} \end{aligned}$$

To be sure that C13 is completely discharged, let  $t_2 > t_1$ .

R13 C11 >

$$\frac{t1}{0.51} = \frac{(72 \text{ ms})}{0.51} = 141 \text{ ms}$$

If C11 = 10 µF, R13 = 15 kΩ

d he kent to a value less than 50 kO to in

R13 should be kept to a value less than 50 k $\Omega$  to insure that bias current existing from pin 3 does not cause an offset voltage above 200 mV. Typically this bias current is less than 3  $\mu A.$

#### Record Playback Switch

When the voltage on pin 3 of the IC is greater than 0.5 V<sub>CC</sub>, the internal record-playback switch switches into the playback mode. During playback the record preamplifier remains partially biased but the input signal to this preamp does not appear at the preamplifier output. In addition, during the playback mode, the record monitor output (pin 9) is disabled and the ALC circuit operates to minimize the signal into the record preamp input. The meter circuit is operational in the playback as well as the record mode. Similarly, during the record mode, the playback preamp input is ignored and the playback monitor output is disabled. In addition, a pin is available to hold one side of the record head at ground potential while sinking up to 500  $\mu$ A of AC bias and record current.

# <u>查询"LM1818"供应商</u>

| R/P<br>Switch                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN 3<br>LOGIC<br>CAP                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                            |

| PIN 6<br>Alc cap                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                            |

| PREAMP<br>Output<br>Pin 14                                                                                                                                        | SWITCHING<br>OCCURS<br>MONITOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | hp-m-lp-di-                                                                                                                                                                                                                                                                                                                                                                                |

| PLAY<br>MONITOR<br>OUTPUT<br>PIN 9                                                                                                                                | vcc/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                            |

| External Co                                                                                                                                                       | FIGURE 8B. Waveform for Anti-Pop Circuit<br><b>mponents</b> (Refer to <i>Figure 9</i> , Monaural Application Circuit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TL/H/7894-                                                                                                                                                                                                                                                                                                                                                                                 |

| Component                                                                                                                                                         | External Component Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Normal Range<br>of Value                                                                                                                                                                                                                                                                                                                                                                   |

| R1                                                                                                                                                                | Used in conjunction with varying impedance of pin 5, forming a resistor divider<br>network to reduce input level in automatic level control circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 500Ω–20 kΩ                                                                                                                                                                                                                                                                                                                                                                                 |

| C2                                                                                                                                                                | Forms a noise reduction system by varying bandwidth as a function of the changing impedance on pin 5. With a small input signal, the bandwidth is reduced by R1 and C2. As the input level increases, so does the bandwidth.                                                                                                                                                                                                                                                                                                                                                                  | 0.01 μF–0.5 μF                                                                                                                                                                                                                                                                                                                                                                             |

| C1, C3                                                                                                                                                            | Coupling capacitors. Because these are part of the source impedance, it is<br>important to use the larger values to keep low frequency source impedance at<br>a minimum.                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.5 μF–10 μF                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100 pF-300 pF                                                                                                                                                                                                                                                                                                                                                                              |

| C4                                                                                                                                                                | Radio frequency interference roll-off capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                            |

| R2<br>R3<br>R4                                                                                                                                                    | Radio frequency interference roll-off capacitor<br>Playback response equalization. C5 and R3 form a pole in the amplifier<br>response at 50 Hz. C5 and R4 form a zero in the response at 1.3 kHz for<br>120 $\mu$ s equalization and 2.3 kHz for 70 $\mu$ s equalization.                                                                                                                                                                                                                                                                                                                     | 50Ω-200Ω<br>47 kΩ-3.3 ΜΩ<br>2 kΩ-200 kΩ                                                                                                                                                                                                                                                                                                                                                    |

| R2<br>R3<br>R4<br>C5<br>R5                                                                                                                                        | Playback response equalization. C5 and R3 form a pole in the amplifier response at 50 Hz. C5 and R4 form a zero in the response at 1.3 kHz for                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47 kΩ−3.3 MΩ                                                                                                                                                                                                                                                                                                                                                                               |

| R2<br>R3<br>R4<br>C5<br>R5<br>R6<br>R7<br>R8<br>R9<br>C6                                                                                                          | Playback response equalization. C5 and R3 form a pole in the amplifier response at 50 Hz. C5 and R4 form a zero in the response at 1.3 kHz for 120 $\mu$ s equalization and 2.3 kHz for 70 $\mu$ s equalization.                                                                                                                                                                                                                                                                                                                                                                              | 47 kΩ-3.3 MΩ<br>2 kΩ-200 kΩ<br>50Ω-200Ω<br>5 kΩ-200 kΩ<br>0-2 kΩ<br>200Ω-5 kΩ<br>1 kΩ-30 kΩ                                                                                                                                                                                                                                                                                                |

| C4 C4 C4 C5 C5 C6 C7 C8 C4 C4 C4 C5 C4 C6 C7 C6 C6 C7 C6 C6 C7 C7 C6 C7 C6 C7 C6 C7 | <ul> <li>Playback response equalization. C5 and R3 form a pole in the amplifier response at 50 Hz. C5 and R4 form a zero in the response at 1.3 kHz for 120 μs equalization and 2.3 kHz for 70 μs equalization.</li> <li>Microphone preamplifier gain equalization</li> <li>DC feedback path. Provides a low impedance path to the negative input in order to sink the 50 μA negative input amplifier current. C6, R9, R7 and C7 provide isolation from the output so that adequate gain can be obtained at 20</li> </ul>                                                                     | $\begin{array}{c} 47 \ \text{k}\Omega - 3.3 \ \text{M}\Omega \\ 2 \ \text{k}\Omega - 200 \ \text{k}\Omega \\ \hline \\ 50\Omega - 200\Omega \\ 5 \ \text{k}\Omega - 200 \ \text{k}\Omega \\ \hline \\ 0 - 2 \ \text{k}\Omega \\ 200\Omega - 5 \ \text{k}\Omega \\ 1 \ \text{k}\Omega - 30 \ \text{k}\Omega \\ 200 \ \mu\text{F} - 1000 \ \mu\text{F} \end{array}$                          |

| R2<br>R3<br>R4<br>C5<br>R5<br>R6<br>R7<br>R8<br>R9<br>C6<br>C7                                                                                                    | <ul> <li>Playback response equalization. C5 and R3 form a pole in the amplifier response at 50 Hz. C5 and R4 form a zero in the response at 1.3 kHz for 120 μs equalization and 2.3 kHz for 70 μs equalization.</li> <li>Microphone preamplifier gain equalization</li> <li>DC feedback path. Provides a low impedance path to the negative input in order to sink the 50 μA negative input amplifier current. C6, R9, R7 and C7 provide isolation from the output so that adequate gain can be obtained at 20 Hz. This 2-pole technique also provides fast turn-ON settling time.</li> </ul> | $\begin{array}{c} 47 \text{ k}\Omega - 3.3 \text{ M}\Omega \\ 2 \text{ k}\Omega - 200 \text{ k}\Omega \\ \hline \\ 50\Omega - 200\Omega \\ 5 \text{ k}\Omega - 200 \text{ k}\Omega \\ \hline \\ 0 - 2 \text{ k}\Omega \\ 200\Omega - 5 \text{ k}\Omega \\ 1 \text{ k}\Omega - 30 \text{ k}\Omega \\ 200 \ \mu\text{F} - 1000 \ \mu\text{F} \\ \hline \\ 0 - 100 \ \mu\text{F} \end{array}$ |

# 查询"<u>LM1818"供应商</u>

| Component                | External Component Function                                                                                                                                                 | Normal Range<br>of Value                            |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| C11<br>R13               | Exponentially falling or rising signal on pin 3 determines sequencing, time<br>delay, and operational mode of the record/play anti-pop circuitry. See anti-<br>pop diagram. | 0–10 μF<br>0–50 kΩ                                  |

| R14<br>R15<br>R16<br>C12 | R16, R14 and C12 determine monitor amplifier response in the play mode.<br>R15, R14 and C12 determine monitor amplifier response in the record mode.                        | 1k–100k<br>30 kΩ–3 MΩ<br>30 kΩ–3 MΩ<br>0.1 μF–20 μF |

| C13<br>R17               | Determines decay response on ALC characteristic and reduces amplifier pop                                                                                                   | 5 μF−20μF<br>100k−∞                                 |

| C14<br>R18               | Determines time constant of meter driving circuitry                                                                                                                         | 0.1 μF−10 μF<br>100k−∞                              |

| R19                      | Meter sensitivity adjust                                                                                                                                                    | 10 kΩ−100 kΩ                                        |

| C15                      | Record output DC blocking capacitor                                                                                                                                         | 1 μF–10 μF                                          |

| C16                      | Play output DC blocking capacitor                                                                                                                                           | 0.1 μF–10 μF                                        |

| C17<br>R21<br>R22        | Changes record output response to approximate a constant current output in<br>conjunction with record head impedance resulting in proper recording<br>equalization          | 500 pF–0.1μF<br>5 kΩ–100 kΩ<br>5 kΩ–100 kΩ          |

| C18                      | Preamplifier supply decoupling capacitor. Note that large value capacitor will<br>increase turn-ON time                                                                     | 0.1 μF–500 μF                                       |

| C19                      | Supply decoupling capacitor                                                                                                                                                 | 100 μF–1000 μF                                      |

| C20                      | Decouples bias oscillator supply                                                                                                                                            | 10 μF–500μF                                         |

| R23                      | Allows bias level adjustment                                                                                                                                                | 0–1 kΩ                                              |

| R24                      | Adjusts DC erase current in DC erase machines (for AC erase, see "Stereo Application Circuit," <i>Figure 1</i> )                                                            |                                                     |

| L1<br>C21                | Optional bias trap                                                                                                                                                          | 1 mH–30 mH<br>100 pF–2000 pF                        |

| C22                      | Bias Roll-Off                                                                                                                                                               | 0.001 μF–0.01 μF                                    |

| H1                       | Record/play head                                                                                                                                                            | 100Ω–500Ω;<br>70 mH–300 mH                          |

| H2                       | Erase head (DC type, AC optional)                                                                                                                                           | 10Ω-300Ω                                            |

# 查询"<u>LM1818"供应商</u>

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications