|                | -     |       |               |      |                  |         |                 |      | REVIS | IONS |     |             |       |    |         |               |     |         |       |    |

|----------------|-------|-------|---------------|------|------------------|---------|-----------------|------|-------|------|-----|-------------|-------|----|---------|---------------|-----|---------|-------|----|

| L <b>查</b> 询"5 | 962-9 | 96791 | 01 <b>Q</b> Y | ′C"供 | 应商               | DESCR   | RIPTIO          | N    |       |      |     |             | 0     |    | (R-MO-D | )A)           |     | APP     | ROVE  | 2  |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       | •  |

|                |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

| REV            | Τ     |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

| SHEET          | 55    | 56    | 57            | 58   | 59               | 60      | 61              | 62   | 63    | 64   |     |             |       |    |         |               |     |         |       |    |

| REV            |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

| SHEET          | 35    | 36    | 37            | 38   | 39               | 40      | 41              | 42   | 43    | 44   | 45  | 46          | 47    | 48 | 49      | 50            | 51  | 52      | 53    | 54 |

| REV            |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

| SHEET          | 15    | 16    | 17            | 18   | 19               | 20      | 21              | 22   | 23    | 24   | 25  | 26          | 27    | 28 | 29      | 30            | 31  | 32      | 33    | 34 |

| REV STATUS     |       |       |               | REV  | /                |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

| OF SHEETS      |       |       |               | SHE  | ET               |         | 1               | 2    | 3     | 4    | 5   | 6           | 7     | 8  | 9       | 10            | 11  | 12      | 13    | 14 |

| PMIC N/A       |       |       |               |      | PARE             |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

|                |       |       |               | Tho  | omas M           | I. Hess |                 |      |       |      |     | DEFE        |       |    |         | NTER<br>110 4 |     | MBU     | 5     |    |

| STA            |       |       |               | CHE  | CKED             | BY      |                 |      |       |      |     |             |       |    | , = •   |               | _   |         |       |    |

| MICRO          |       |       | Т             |      | omas M           |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

| DR/            | WIN   | ١G    |               |      | 001/27           |         |                 |      |       | MIC  | 800 | IRCUI       | יים ד |    | 214     |               |     | F18.4⊂7 | ע אור |    |

| THIS DRAWI     |       |       | BLE           |      | ROVEI<br>nica L. |         | ng              |      |       |      |     | SOR,        |       |    |         |               |     |         |       |    |

| FOR U<br>DEPA  | SE BY |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

| AND AGE        | NCIES | OF TH |               | DRA  | WING             |         | DVAL [<br>16-10 | DATE |       |      |     | <del></del> |       |    |         |               |     |         |       |    |

| UEFARIME       |       | UEFEN | IJE           |      |                  |         |                 |      |       | SIZE | _   |             |       |    |         | 59            | 962 | -967    | 791   |    |

| AMSC           | N/A   |       |               | REV  | ISION            | LEVEL   |                 |      |       |      | 1   | 6           | 726   | 8  | L       |               |     |         |       |    |

|                |       |       |               |      |                  |         |                 |      |       | SHE  | ET  | 1           |       | OF | 6       | А             |     |         |       |    |

|                |       |       |               | 1    |                  |         |                 |      |       |      |     | 1           |       |    | 0       | 4             |     |         |       |    |

| DSCC FORM 22   |       |       |               |      |                  |         |                 |      |       |      |     |             |       |    |         |               |     |         |       |    |

M 9004708 0031680 951 MM

....

DSCC FORM 2233 APR 97

DISTRIBUTION STATEMENT A. Approved for public release distribution is unlimited.

5962-E186-97

....

Powered by ICminer.com Electronic-Library Service CopyRight 2003

#### 1. SCOPE 查 这些56627967042016 beutensativo product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN. 1.2 PIN. The PIN is as shown in the following example: 5962 96791 01 M X Х Federal RHA Device Device Case Lead stock class designator class type outline finish designator (see 1.2.1) (see 1.2.2) designator (see 1.2.4) (see 1.2.5) (see 1.2.3) V Drawing number 1.2.1 RHA designator. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device. 1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows: Device type Generic number **Circuit function** 01 320C80-50 Multimedia video processor 1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows: **Device class** Device requirements documentation М Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A Q or V Certification and gualification to MIL-PRF-38535 1.2.4 <u>Case outline(s)</u>. The case outline(s) are as designated in MIL-STD-1835 and as follows: **Outline** letter Descriptive designator **Terminals** Package style P-CK х 305 Pin grid array Y (See figure 1) 320 1/ Ceramic quad flatpack with nonconductive tie bar 1.2.5 Lead finish. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M. 1/ This case outline contains capacitor pads located on top of the package. The terminals are referenced clockwise starting at the index corner. See Figure 2 for terminal values. SIZE STANDARD 5962-96791 Α **MICROCIRCUIT DRAWING** DEFENSE SUPPLY CENTER COLUMBUS **REVISION LEVEL** SHEET COLUMBUS, OHIO 43216 2 DSCC FORM 2234 **APR** 97

9004708 0031681 898 🛲

| COLUMBUS, OHIO 43216                                                                                                                                                                                          |                     | REVISION LEVEL             | SHEET<br>3             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------|------------------------|

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS                                                                                                                                            | SIZE<br>A           |                            | 5962-96791             |

| 2/ Values will be added when they become available.                                                                                                                                                           |                     |                            | 1                      |

| 1/ Stresses above the absolute maximum rating may cause maximum levels may degrade performance and affect re                                                                                                  |                     | age to the device. Extende | ed operation at the    |

| (Unless otherwise indicated, copies of the specification, Standardization Document Order Desk, 700 Robbins Avenue,                                                                                            |                     |                            | able from the          |

| MIL-HDBK-103 - List of Standard Microcircuit Dra<br>MIL-HDBK-780 - Standard Microcircuit Drawings.                                                                                                            | wings (SMD's).      |                            |                        |

| MILITARY                                                                                                                                                                                                      |                     |                            |                        |

| HANDBOOKS                                                                                                                                                                                                     |                     |                            | • .                    |

| MIL-STD-883 - Test Methods and Procedures for<br>MIL-STD-973 - Configuration Management.<br>MIL-STD-1835 - Microcircuit Case Outlines.                                                                        | r Microelectronics. |                            |                        |

| MILITARY                                                                                                                                                                                                      |                     |                            |                        |

| STANDARDS                                                                                                                                                                                                     |                     |                            |                        |

| MIL-PRF-38535 - Integrated Circuits, Manufactur                                                                                                                                                               | ring, General Spec  | cification for.            |                        |

| MILITARY                                                                                                                                                                                                      |                     |                            |                        |

| SPECIFICATION                                                                                                                                                                                                 |                     |                            |                        |

| 2.1 <u>Government specification, standards, and handbooks</u> . The of this drawing to the extent specified herein. Unless otherwis issue of the Department of Defense Index of Specifications an solitation. | e specified, the is | sues of these documents a  | re those listed in the |

| 2. APPLICABLE DOCUMENTS                                                                                                                                                                                       | _                   |                            |                        |

| Fault coverage measurement of manufacturing<br>logic tests (MIL-STD-883, test method 5012)                                                                                                                    | XX percent 2/       |                            |                        |

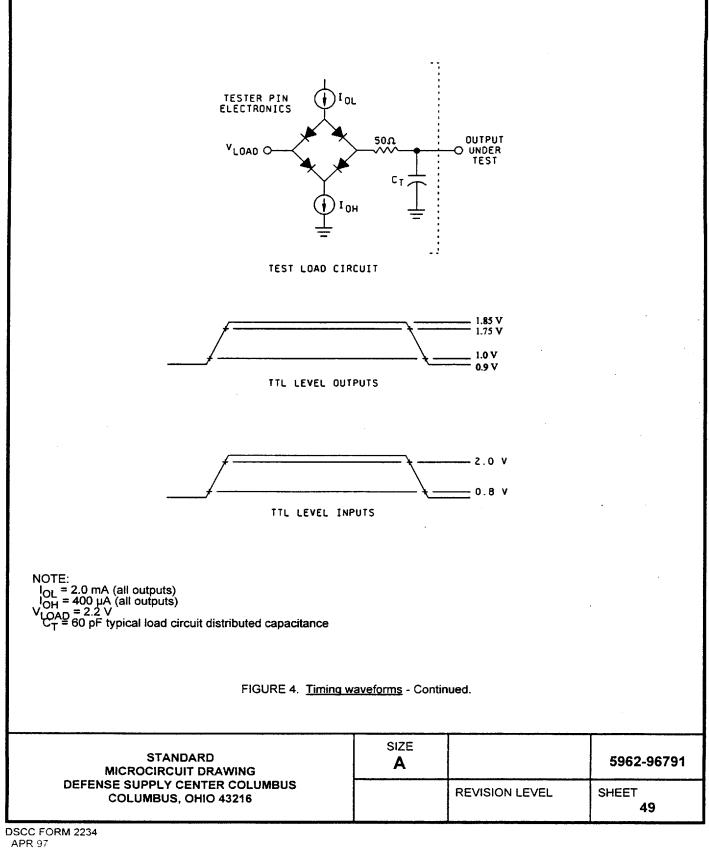

| Low level output current (I <sub>OL</sub> )                                                                                                                                                                   | 2 mA                |                            |                        |

| Case operating temperature range (T <sub>C</sub> )                                                                                                                                                            | <b>-400 μ</b> Α     | °C                         |                        |

| 1.4 <u>Recommended operating conditions</u> .<br>Supply voltage range (V <sub>DD</sub> )<br>Supply voltage range (V <sub>SS</sub> )                                                                           | 0 V dc to 0 V d     | ic .                       |                        |

| Maximum power dissipation (P <sub>D</sub> )<br>Junction temperature (T <sub>J</sub> )                                                                                                                         |                     |                            |                        |

| Case X                                                                                                                                                                                                        | <b>2°C/W</b>        |                            |                        |

| Storage temperature range (T <sub>STG</sub> )<br>Thermal resistance, junction-to-case (θ <sub>IC</sub> )                                                                                                      | 55°C to +150        | °C                         |                        |

| Supply voltage range (V <sub>DD</sub> ).<br>查询"56版记·级超40组码4 O <sub>U</sub> 从应商<br>Output voltage range (V <sub>OUT</sub> )                                                                                    | -0.3 V dc to +      | 4.0 V dc<br>4.0 V dc       |                        |

| 1.3 <u>Absolute maximum ratings</u> . <u>1</u> /<br>Supply voltage range (V <sub>DD</sub> )                                                                                                                   | -0.3 V do to +      | 4.0 V dc                   |                        |

۰.

DSCC FORM 2234 APR 97

## 🔳 9004708 0031682 724 🖿

2.2 <u>Non-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents which are DOD adopted are those listed in the issue of the DODISS cited in the Solicitation. Unless otherwise specified, the issues of documents not listed in the DODISS are the issues of the documents cited in the solicitation (see 6.2).

INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS (IEEE)

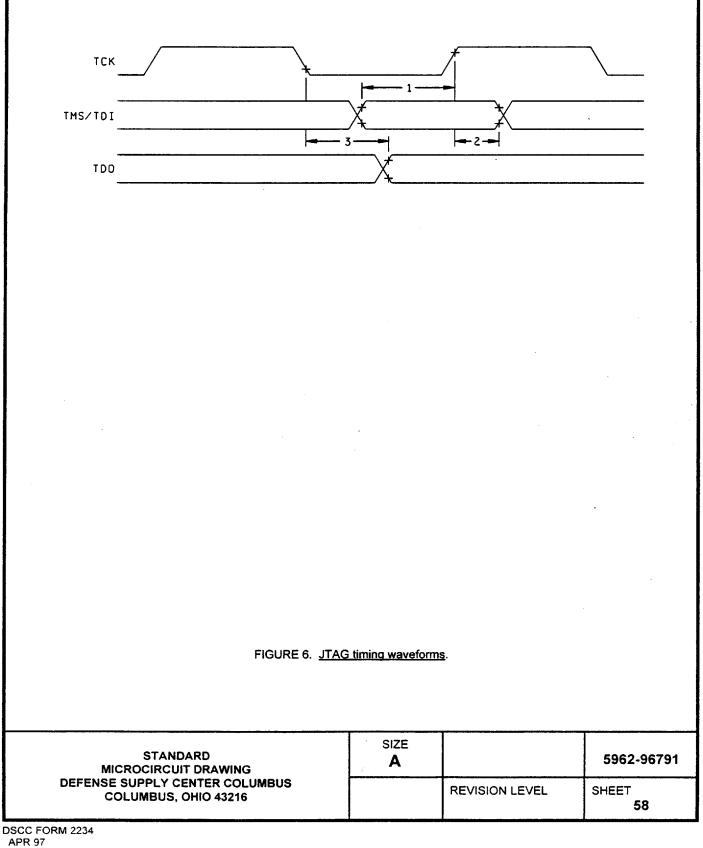

IEEE Standard 1149.1 - IEEE Standard Test Access Port and Boundary Scan Architecture.

(Applications for copies should be addressed to the Institute of Electrical and Electrons Engineers, 445 Hoes Lane, Piscataway, NJ 08854-4150.)

(Non-Government standards and other publications are normally available from the organizations which prepare or distribute the documents. These documents also may be available in or through libraries or other informational services.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

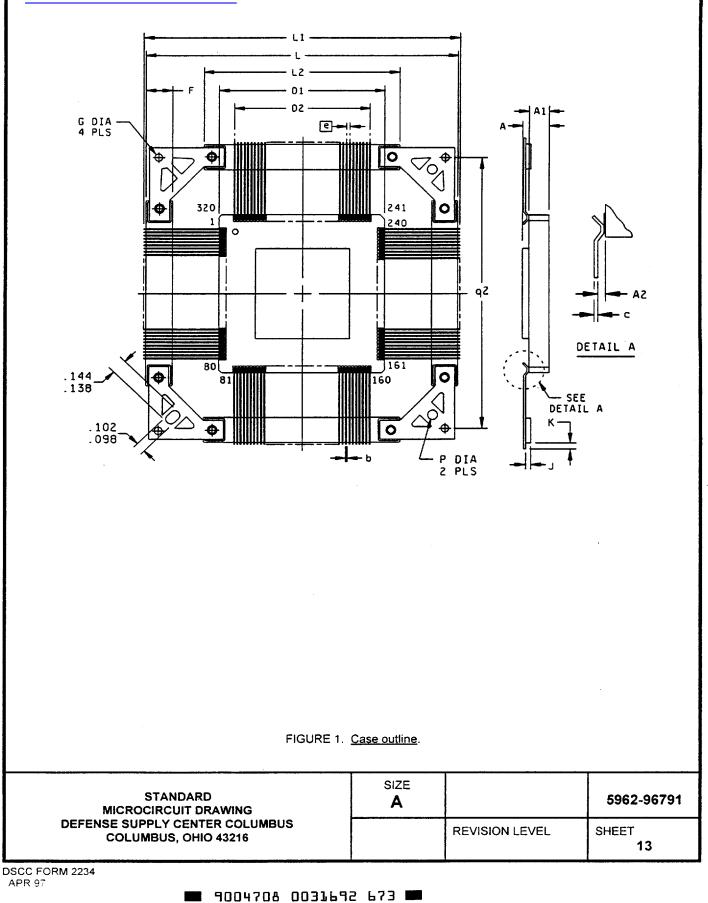

3.2.1 <u>Case outline(s)</u>. The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

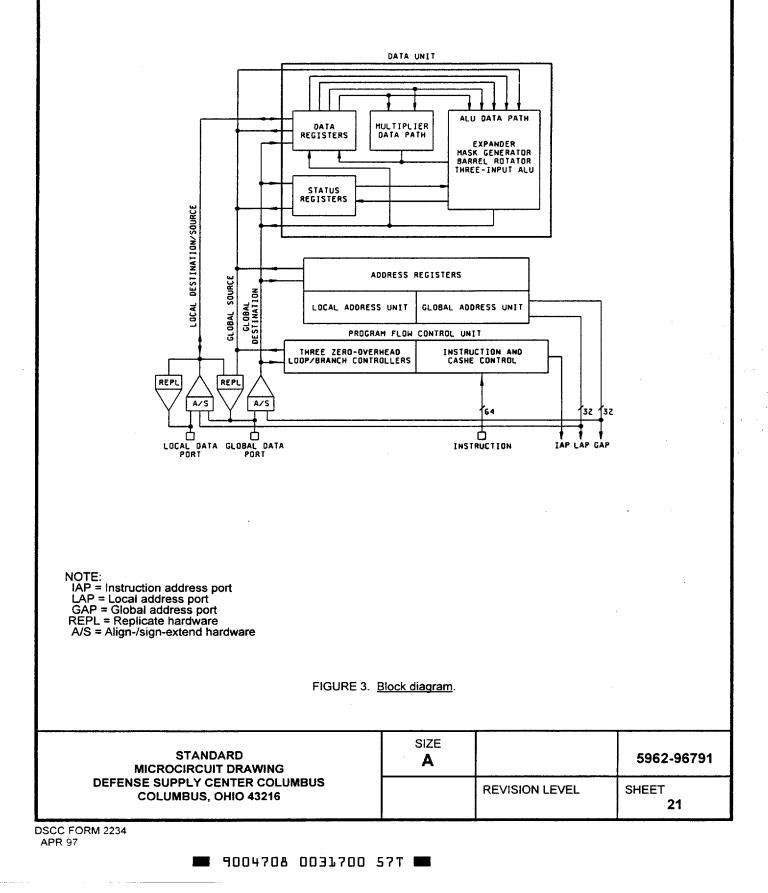

3.2.3 Block diagram. The block diagram shall be as specified on figure 3.

3.2.4 <u>Radiation exposure circuit</u>. The radiation exposure circuit shall be as specified when available.

3.2.5 Boundary scan instruction code. For device 01 the boundary scan instruction codes shall be as specified on figure 5.

3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-HDBK-103. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

| STANDARD<br>MICROCIRCUIT DRAWING                       | SIZE<br>A |                | 5962-96791 |

|--------------------------------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216 |           | REVISION LEVEL | SHEET<br>4 |

DSCC FORM 2234 APR 97

#### 9004708 0031683 660 🔳

3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

3.8 <u>Notification of change for device class M</u>. For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-973.

3.9 <u>Verification and review for device class M</u>. For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 105 (see MIL-PRF-38535, appendix A).

3.11 IEEE 1149.1 compliance. Device type 01 shall be compliant with IEEE 1149.1.

| STANDARD<br>MICROCIRCUIT DRAWING                       | SIZE<br>A |                | 5962-96791 |

|--------------------------------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216 |           | REVISION LEVEL | SHEET<br>5 |

DSCC FORM 2234 APR 97

90047080031684 ST7 🎟

| 本治115000-00704040                                  |                                  | TABLE I. <u>Electrical perforr</u>                            | nance characte | eristics. |                                    |                      |       |

|----------------------------------------------------|----------------------------------|---------------------------------------------------------------|----------------|-----------|------------------------------------|----------------------|-------|

| ─ <u>查询"5962=9679101C</u><br>                      | 们 C 1共加<br>Symbol                |                                                               | Group A        | Device    | L                                  | imits                | Unit  |

|                                                    |                                  | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified | subgroups      | type      | Min                                | Max                  |       |

| High level input voltage                           | V <sub>IH</sub>                  |                                                               | 1,2,3          | All       | 2                                  | V <sub>DD</sub> +0.3 | V     |

| Low level input voltage                            | ∨ <sub>IL</sub>                  |                                                               | 1,2,3          | All       | -0.3                               | 0.8                  | V     |

| High level output voltage                          | V <sub>OH</sub>                  | V <sub>DD</sub> = min, I <sub>OH</sub> = max                  | 1,2,3          | All       | 1.85                               |                      | V     |

| Low level output voltage                           | V <sub>OL</sub>                  | V <sub>DD</sub> = max, I <sub>OL</sub> = max                  | 1,2,3          | All       |                                    | 0.9                  | V     |

| Output current, leakage<br>(high-impedance)        | I <sub>O</sub>                   | V <sub>DD</sub> = max, V <sub>O</sub> = 2.8 V                 | 1,2,3          | All       |                                    | 20                   | μΑ    |

| (except EMU0, &<br>EMU1)                           |                                  | V <sub>DD</sub> = max, V <sub>O</sub> = 0.6 V                 |                |           |                                    | -20                  |       |

| Input current (except<br>TCK, TDI, & TMS,<br>TRST) | lı                               | V <sub>I</sub> = V <sub>SS to</sub> V <sub>DD</sub>           | 1,2,3          | Ali       |                                    | ±20                  | μA    |

| Supply current <u>1</u> /                          | IDD                              | V <sub>DD</sub> = max, 50 MHz                                 | 1,2,3          | All       |                                    | 2.5                  | A     |

| Input capacitance                                  | C <sub>I</sub>                   | See 4.4.1c                                                    | 4              | All       |                                    | 15                   | pF    |

| Output capacitance                                 | co                               | See 4.4.1c                                                    | 4              | All       |                                    | 15                   | pF    |

| Functional test                                    |                                  | See 4.4.1b                                                    | 7,8            | All       |                                    |                      | -     |

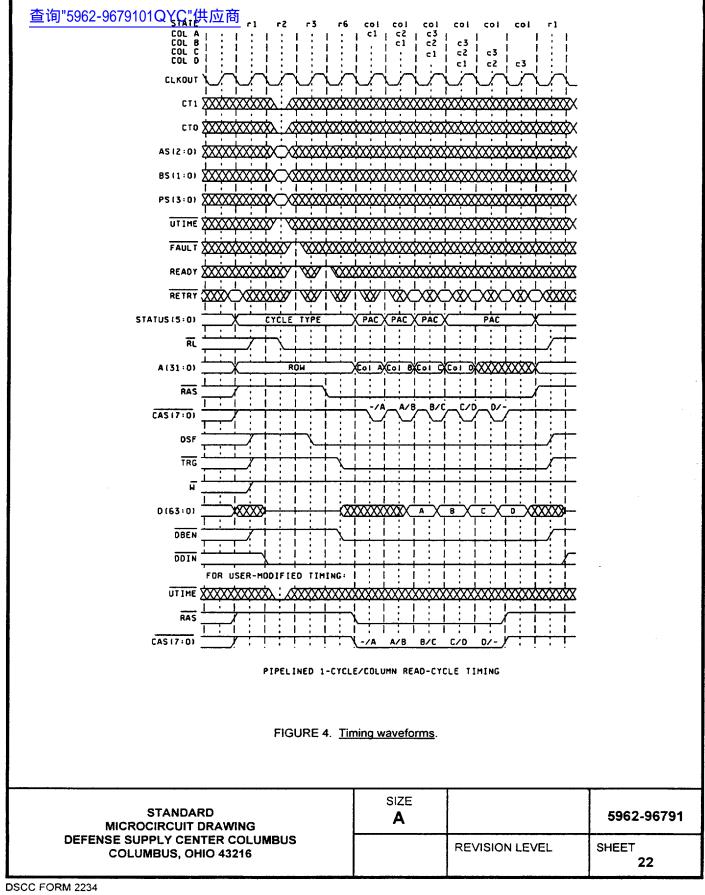

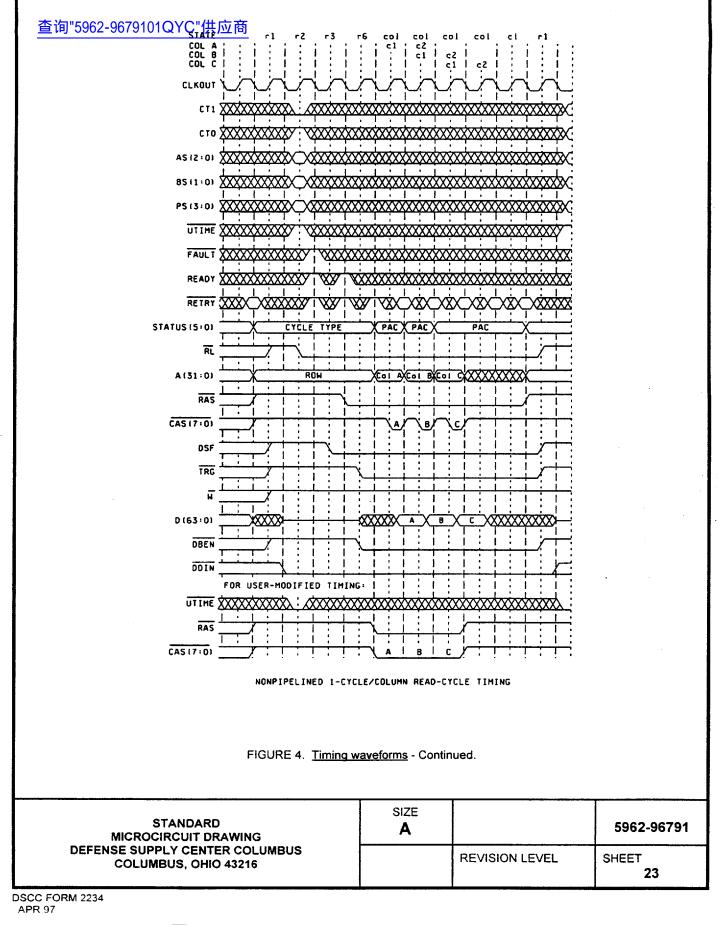

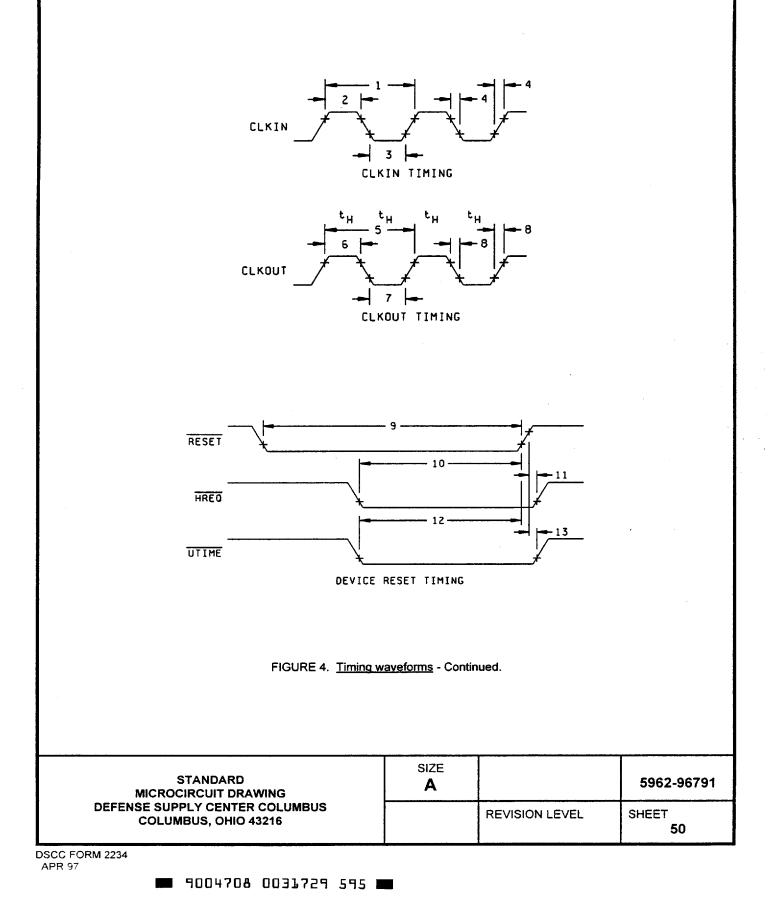

| Period of CLKIN (t <sub>H</sub> )                  | 1                                | (t <sub>C(CKI)</sub>                                          | 9,10,11        | All       | -10                                |                      | ns    |

| Pulse duration of CLKIN<br>high                    | 2                                |                                                               | 9,10,11        | All       | 4.2                                |                      | ns    |

| Pulse duration of CLKIN low                        | 3                                |                                                               | 9,10,11        | All       | 4.2                                |                      | ns    |

| Transition time of CLKIN <u>2</u> /                | 4                                |                                                               | 9,10,11        | All       |                                    | 1.5                  | ns    |

| Period of CLKOUT                                   | 5                                |                                                               | 9,10,11        | All       | 2t <sub>c(CKI)</sub><br><u>3</u> / |                      | ns    |

| Pulse duration of<br>CLKOUT high                   | 6                                |                                                               | 9,10,11        | All       | t <sub>H</sub> -4.5                |                      | ns    |

| Pulse duration of<br>CLKOUT low                    | 7                                |                                                               | 9,10,11        | All       | t <sub>H</sub> -4.5                |                      | ns    |

| Transition time of<br>CLKOUT                       | 8                                |                                                               | 9,10,11        | All       |                                    | 2.5 <u>2</u> /       | ns    |

| Duration of RESET<br>low                           | 9                                | Initial reset during<br>power-up                              | 9,10,11        | All       | 6t <sub>H</sub>                    |                      | ns    |

|                                                    |                                  | Reset during active operation                                 |                |           | 6t <sub>H</sub>                    |                      |       |

| See footnotes at end of tak                        | ole.                             |                                                               | -              |           |                                    |                      |       |

| MICROCI                                            | STANDARD<br>MICROCIRCUIT DRAWING |                                                               | SIZE<br>A      |           |                                    | 5962-                | 96791 |

| DEFENSE SUPPL<br>COLUMB                            | Y CENTER<br>US, OHIO 4           |                                                               |                | REVISION  | LEVEL                              | SHEET                | 6     |

9004708 0031685 433 📟

| <u>查询"5962-9679101</u><br>Test                                                                         | Symbol                                                 | Conditions <u>1</u> /                                         | Group A   | Device   | - i             | .imits               | Unit   |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|-----------|----------|-----------------|----------------------|--------|

|                                                                                                        |                                                        | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified | subgroups | type     | Min             | Max                  |        |

| Setup time of HREQ<br>low to RESET high<br>to configure self-<br>bootstrap mode                        | 10                                                     |                                                               | 9,10,11   | Ail      | 4t <sub>H</sub> |                      | ns     |

| Hold time FREQ low<br>to RESET high to<br>configure self-<br>bootstrap mode                            | 11                                                     |                                                               | 9,10,11   | All      | 0               |                      | ns     |

| Setup time of UTTME low<br>to RESET high to<br>configure big endian<br>operation                       | 12                                                     |                                                               | 9,10,11   | Ali      | <sup>4t</sup> H |                      | ns     |

| Hold time UTTME low<br>after RESET high to<br>configure big endian<br>operation                        | 13                                                     |                                                               | 9,10,11   | All      | 0               |                      | ns     |

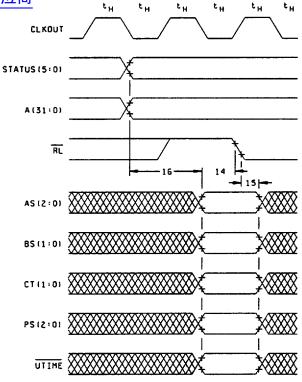

| Setup time, AS, BS,<br>CT, PS, and UTTME<br>valid to CLKOUT no<br>longer low                           | 14                                                     |                                                               | 9,10,11   | All      | 8               |                      | ns     |

| Hold time, AS, BS.<br>CT, PS, and UTTME<br>valid to CLKOUT high                                        | 15                                                     |                                                               | 9,10,11   | All      | 2               |                      | ns     |

| Access time, AS, BS,<br>CT, PS, and UTTME<br>valid after memory<br>identification (A,<br>STATUS) valid | 16                                                     |                                                               | 9,10,11   | All      |                 | 3t <sub>H</sub> -10  | ns     |

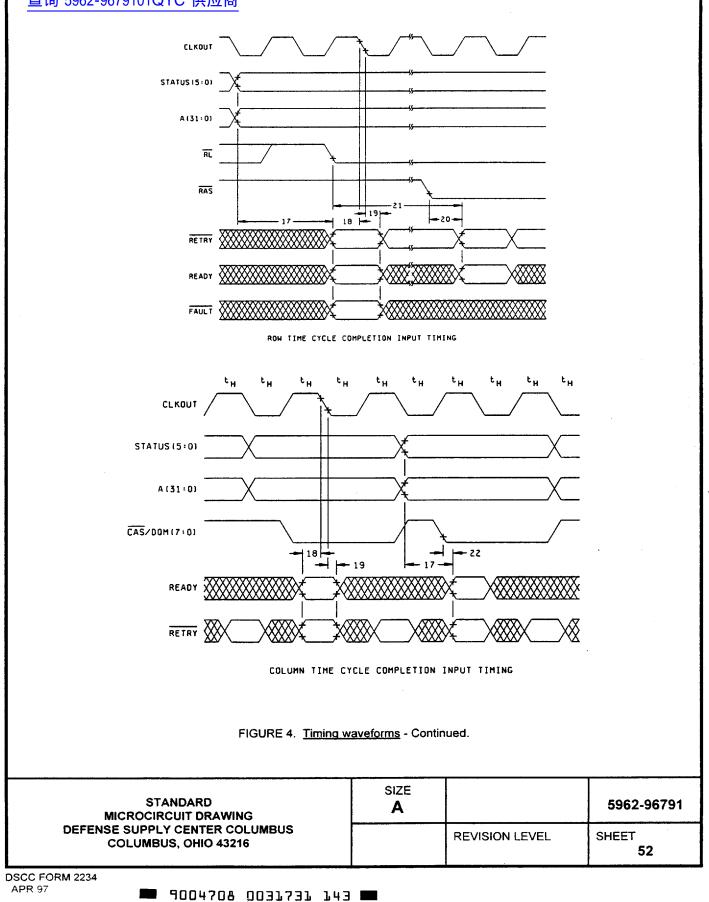

| Access time, RETRY,<br>READY, FAULT valid<br>after memory inden-<br>tification (A,<br>STATUS) valid    | 17                                                     |                                                               | 9,10,11   | All      |                 | nt <sub>H</sub> -8   | ns     |

| Setup time, RETRY,<br>READY, FAOLT valid<br>to CLKOUT no longer<br>high                                | 18                                                     |                                                               | 9,10,11   | All      | 7.5             |                      | ns     |

| Hold time, RETRY,<br>READY, FAULT valid<br>to CLKOUT low                                               | 19                                                     |                                                               | 9,10,11   | All      | 1.2             |                      | ns     |

| Access time RETRY,<br>READY, valid from<br>RAS low                                                     | 20                                                     |                                                               | 9,10,11   | Ali      |                 | nt <sub>H</sub> -7.5 | ns     |

| Access time RETRY,<br>READY, valid from<br>RC low                                                      | 21                                                     |                                                               | 9,10,11   | All      |                 | nt <sub>H</sub> -7.5 | ns     |

| ee footnotes at end of ta                                                                              | ıble.                                                  |                                                               |           |          |                 |                      |        |

|                                                                                                        | TANDARD                                                | WING                                                          | SIZE<br>A |          |                 | 5962                 | -96791 |

| DEFENSE SUPP                                                                                           | DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216 | COLUMBUS                                                      |           | REVISION |                 | SHEET                |        |

🔳 9004708 0031686 37T 🔳

| <del>一查询"5962-9679101C</del><br>Test                                           | Symbol | Conditions <u>1</u> /                                                    | Group A   | Device     | Li                   | mits                 | Unit  |

|--------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------|-----------|------------|----------------------|----------------------|-------|

|                                                                                |        | $-55^{\circ}C \le T_{C} \le +125^{\circ}C$<br>unless otherwise specified | subgroups |            | Min                  | Max                  |       |

| Access time, READY                                                             | 22     | 2cyc/col accesses                                                        | 9,10,11   | All        |                      | t <sub>H</sub> -12   | ns    |

| valid from CAS low                                                             |        | 3cyc/col accesses                                                        |           |            |                      | 2t <sub>H</sub> -8   |       |

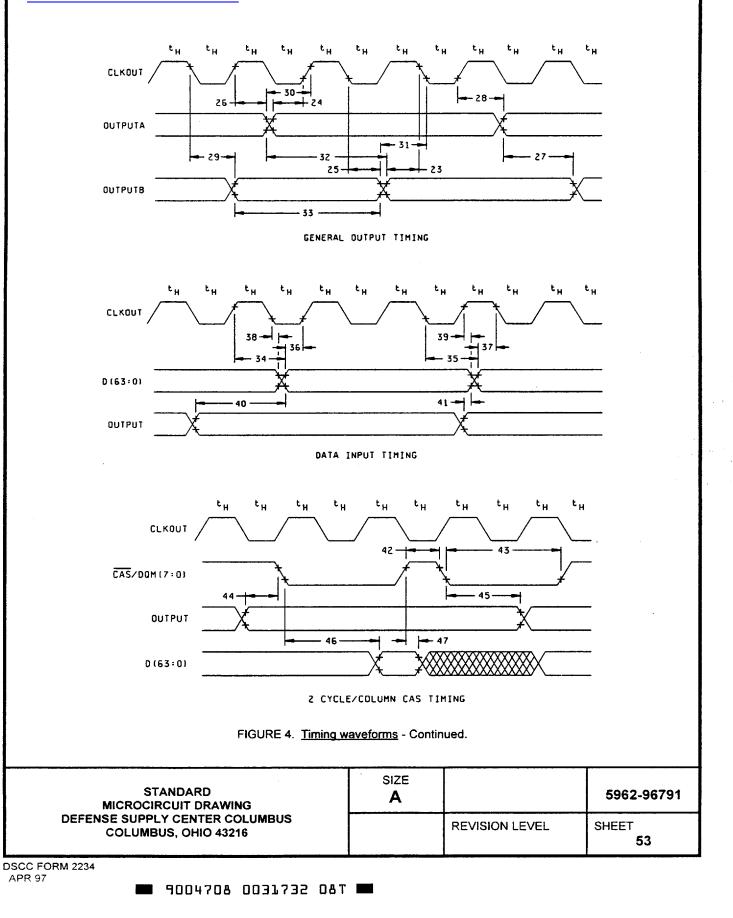

| Hold time, CLKOUT high                                                         | 23     | D(63:0)                                                                  | 9,10,11   | All        | nt <sub>H</sub> -5.6 |                      | ns    |

| after output valid                                                             |        | A(31:0), STATUS(5:0),<br>CAS/DQM(7:0), <u>4</u> /                        |           |            | nt <sub>H</sub> -5.0 |                      |       |

|                                                                                |        | DBEN, DDTN DSF, RAS<br>TRG/CAS ,W,RL                                     |           |            | nt <sub>H</sub> -4.3 |                      |       |

| Hold time, CLKOUT low                                                          | 24     | D(63:0)                                                                  | 9,10,11   | All        | nt <sub>H</sub> -5.6 |                      | ns    |

| after output valid                                                             |        | A(31:0), STATUS(5:0),<br>CAS/DQM(7:0), <u>4</u> /                        |           |            | nt <sub>H</sub> -5.0 |                      |       |

|                                                                                |        | DBEN, DDTN DSF, RAS<br>TRG/CAS ,W, RT                                    |           |            | nt <sub>H</sub> -4.3 |                      |       |

| Hold time, output valid<br>after CLKOUT low                                    | 25     |                                                                          | 9,10,11   | All        | nt <sub>H</sub> -5.5 |                      | ns    |

| Hold time, output valid after CLKOUT high                                      | 26     |                                                                          | 9,10,11   | All        | nt <sub>H</sub> -5.0 |                      | ns    |

| Hold time, output valid after output valid                                     | 27     | D(63:0)                                                                  | 9,10,11   | All        | nt <sub>H</sub> -6.5 |                      | ns    |

|                                                                                |        | A(31:0), STATUS(5:0),<br>CAS/DQM(7:0), <u>4</u> /                        | 9,10,11   |            | nt <sub>H</sub> -6.0 |                      |       |

|                                                                                |        | DBEN, DDTN DSF, RAS<br>TRG/CAS ,W, RL                                    | 9,10,11   |            | nt <sub>H</sub> -5.0 |                      |       |

| Delay time, CLKOUT no                                                          | 28     | D(63:0)                                                                  | 9,10,11   | All        |                      | nt <sub>H</sub> +6.5 | ns    |

| longer low to output<br>valid                                                  |        | A(31:0), STATUS(5:0),<br>CAS/DQM(7:0), <u>4</u> /                        |           |            |                      | nt <sub>H</sub> +5.5 | ]     |

|                                                                                |        | DBEN, DDTN DSF, RAS<br>TRG/CAS ,W, RL                                    |           |            |                      | nt <sub>H</sub> +5   |       |

| Delay time, CLKOUT no                                                          | 29     | D(63:0)                                                                  | 9,10,11   | All        |                      | nt <sub>H</sub> +6.5 | .ns   |

| longer high to output<br>valid                                                 |        | A(31:0), STATUS(5:0),<br>CAS/DQM(7:0), RT <u>4</u> /                     | ]         |            |                      | nt <sub>H</sub> +5.5 | ]     |

|                                                                                |        | DBEN, DDTN DSF, RAS<br>TRG/CAS ,W, RL                                    | ]         |            |                      | nt <sub>H</sub> +5   |       |

| See footnotes at end of tab                                                    | ble.   |                                                                          |           |            |                      |                      |       |

|                                                                                |        | WING                                                                     | SIZE<br>A |            | - <i></i>            | 5962-                | 96791 |

| MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216 |        | COLUMBUS                                                                 |           | REVISION L | EVEL                 | SHEET                |       |

-----

APR 97

9004708 0031687 206 🔳

-----

| 查询"5062_06701010                                         |                                                        | LE I. <u>Electrical performa</u><br>商                    | nce ch | aracteristics | - Continued. |                      |                      |       |

|----------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------|--------|---------------|--------------|----------------------|----------------------|-------|

| Test                                                     | Symbol                                                 | Conditions <u>1</u> /                                    |        | Group A       |              | L                    | imits                | Unit  |

|                                                          |                                                        | -55°C ≤ T <sub>C</sub> ≤ +125°<br>unless otherwise speci | fied   | subgroups     | s type       | Min                  | Max                  | 1     |

| Delay time, output no<br>longer valid to<br>CLKOUT high  | 30                                                     |                                                          |        | 9,10,11       | All          |                      | nt <sub>H</sub> +5.0 | ns    |

| Delay time, output no<br>longer valid to<br>CLKOUT low   | 31                                                     |                                                          |        | 9,10,11       | All          |                      | nt <sub>H</sub> +5.5 | ns    |

| Delay time, output no<br>longer valid to<br>output valid | 32                                                     | D(63:0)                                                  |        | 9,10,11       | All          |                      | nt <sub>H</sub> +6.5 | ns    |

|                                                          |                                                        | A(31:0), STATUS(5:0),<br>CAS/DQM(7:0), <u>4</u> /        |        |               |              |                      | nt <sub>H</sub> +6.0 |       |

|                                                          |                                                        | DBEN, DDTN DSF, 1<br>TRG/CAS, W, RL                      | RAS    |               |              |                      | nt <sub>H</sub> +5   |       |

| Pulse width, output                                      | 33                                                     | D(63:0)                                                  |        | 9,10,11       | All          | nt <sub>H</sub> -6.5 |                      | ns    |

| valid                                                    |                                                        | A(31:0), STATUS(5:0),<br>CAS/DQM(7:0), <u>4</u> /        |        |               |              | nt <sub>H</sub> -6.0 |                      |       |

|                                                          |                                                        | DBEN, DDTN DSF, 1<br>TRG/CAS ,W, RL                      | RAS    |               |              | nt <sub>H</sub> -5.0 |                      |       |

| Access time, CLKOUT<br>high to D(63:0) valid             | 34                                                     |                                                          |        | 9,10,11       | All          |                      | nt <sub>H</sub> -5.3 | ns    |

| Access time, CLKOUT<br>low to D(63:0) valid              | 35                                                     |                                                          |        | 9,10,11       | All          |                      | nt <sub>H</sub> -6.5 | ns    |

| Setup time, D(63:0)<br>valid to CLKOUT no<br>longer low  | 36                                                     |                                                          |        | 9,10,11       | All          | 6.1                  |                      | ns    |

| Setup time, D(63:0)<br>valid to CLKOUT no<br>longer high | 37                                                     |                                                          | -      | 9,10,11       | All          | 6.1                  |                      | ns    |

| Hold time, D(63:0)<br>valid to CLKOUT no<br>longer low   | 38                                                     |                                                          |        | 9,10,11       | All          | 2                    |                      | ns    |

| Hold time, D(63:0)<br>valid to CLKOUT no<br>longer high  | 39                                                     |                                                          |        | 9,10,11       | All          | 2                    |                      | ns    |

| Access time, output<br>valid to D(63:0)<br>inputs valid  | 40                                                     | A(31:0), STATUS(5:0),<br>CAS/DQM(7:0) <u>4</u> /, RL     |        | 9,10,11       | All          |                      | nt <sub>H</sub> -7   | ns    |

|                                                          |                                                        | DBEN, DDTN DSF, F<br>TRG/CAS ,W                          | RAS    |               |              |                      | nt <sub>H</sub> -6.5 |       |

| Hold time, D(63:0)<br>valid after output valid           | 41 <u>5</u> /                                          | RAS, CAS/DQM(7:0)                                        |        | 9,10,11       | All          | 3                    |                      | ns    |

|                                                          |                                                        | A(31:0)                                                  |        |               |              | 3                    |                      |       |

| See footnotes at end of ta                               | ble.                                                   |                                                          |        |               |              |                      |                      |       |

| MICROCI                                                  | STANDARD<br>MICROCIRCUIT DRAWING                       |                                                          |        | SIZE<br>A     |              |                      | 5962-                | 96791 |

|                                                          | DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216 |                                                          |        |               | REVISION L   | .EVEL                | SHEET                | 9     |

· -- - · ----

...

# M 9004708 0031688 142 페

|                                                                            |                                                                                | LE I. Electrical performanc                                  | e characteristics | - Continued. |                      |                     |       |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------|--------------|----------------------|---------------------|-------|

| 查询"5962-9679101C<br>Test                                                   | ừ <del>℃"供应</del><br>│ <del>Symbol</del>                                       | Conditions 1/                                                | Group A           |              | Li                   | imits               | Unit  |

|                                                                            |                                                                                | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specifie | ed subgroup       | s type       | Min                  | Max                 | 1     |

| Pulse duration,<br>CAS/DQM high                                            | 42                                                                             |                                                              | 9,10,11           | All          | t <sub>H</sub> -2    |                     | ns    |

| Pulse duration,<br>CAS/DQM low                                             | 43                                                                             |                                                              | 9,10,11           | All          | 3t <sub>H</sub> -9.5 |                     | ns    |

| Hold time, CAS/DQM<br>high after output                                    | 44                                                                             | D(63:0)                                                      | 9,10,11           | Ali          | nt <sub>H</sub> -4.5 |                     | ns    |

| valid                                                                      |                                                                                | A(31:0), STATUS(5:0),<br>CAS/DQM(7:0),                       |                   |              | nt <sub>H</sub> -4.0 |                     |       |

|                                                                            |                                                                                | DBEN, DDTN DSF, RA<br>TRG/CAS, W, RL                         | 45                |              | nt <sub>H</sub> -3.0 |                     |       |

| Hold time, output valid<br>CAS/DQM low                                     | 45                                                                             |                                                              | 9,10,11           | All          | nt <sub>H</sub> -9.5 |                     | ns    |

| Access time, data valid<br>from CAS/DQM low                                | 46                                                                             |                                                              | 9,10,11           | All          |                      | 3t <sub>H</sub> -12 | ns    |

| Hold time, data valid after CAS/DQM high                                   | 47                                                                             |                                                              | 9,10,11           | All          | 2                    |                     | ns    |

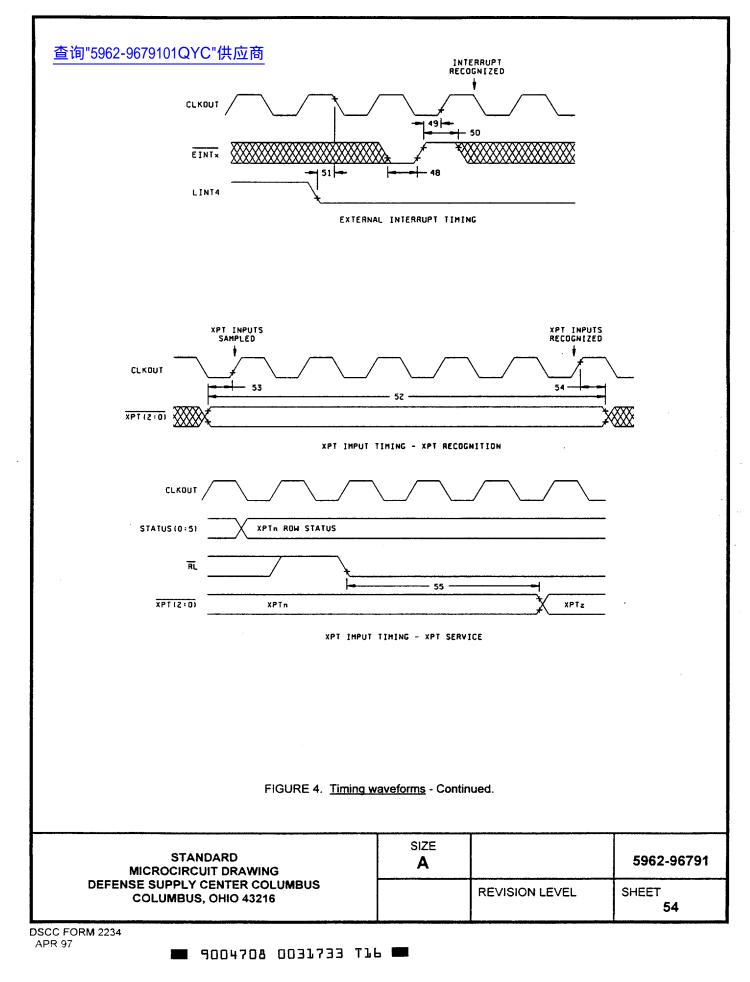

| Pulse duration, EINTx<br>low <u>7</u> /                                    | 48                                                                             | <u>6</u> /                                                   | 9,10,11           | All          | 6                    |                     | ns    |

| Setup time, EINTx<br>high before CLKOUT<br>no longer low <u>8</u> /        | 49                                                                             | <u>6</u> /                                                   | 9,10,11           | All          | 9.5                  |                     | ns .  |

| Pulse duration, EINTx high <u>7</u> /                                      | 50                                                                             | <u>6</u> /                                                   | 9,10,11           | All          | 6                    |                     | ns    |

| Setup time, <u>LTNTx</u><br>low before CLKOUT<br>no longer high <u>8</u> / | 51                                                                             | <u>6</u> /                                                   | 9,10,11           | All          | 9.5                  |                     | ns    |

| Pulse duration, XPTx<br>valid <u>9</u> /                                   | 52                                                                             |                                                              | 9,10,11           | All          | 12t <sub>H</sub>     |                     | ns    |

| Setup time, XPT (2:0)<br>valid before CLKOUT<br>no longer low <u>10</u> /  | 53                                                                             |                                                              | 9,10,11           | All          | 12                   |                     | ns    |

| Hold time, XPT(2:0)<br>valid after CLKOUT<br>high                          | 54                                                                             |                                                              | 9,10,11           | All          | 5                    |                     | ns    |

| Hold time, XPT (2:0)<br>valid after RL low<br><u>11</u> /                  | 55                                                                             |                                                              | 9,10,11           | All          |                      | 6t <sub>H</sub>     | ns    |

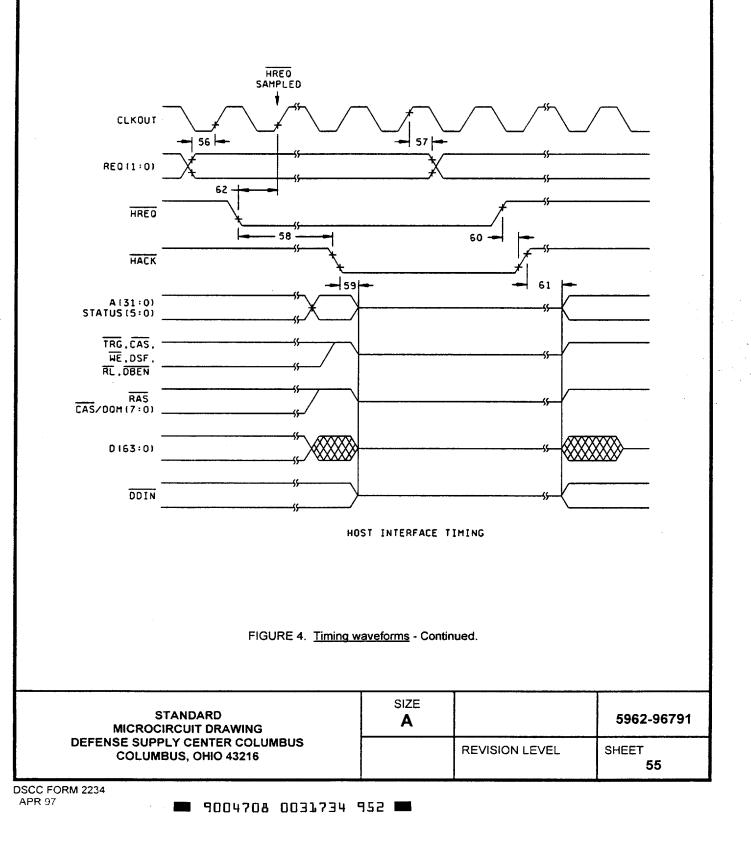

| Setup time REQ1 - REQ0<br>valid to CLKOUT no longer<br>low                 | 56                                                                             |                                                              | 9,10,11           | All          | t <sub>H</sub> -7    |                     | ns    |

| Hold time, REQ(1:0)<br>valid after CLKOUT<br>high                          | 57                                                                             |                                                              | 9,10,11           | All          | t <sub>H</sub> -7    |                     | ns    |

| Hold time, HACK high after HREQ low <u>9</u> /                             | 58                                                                             |                                                              | 9,10,11           | All          | 4t <sub>H</sub> -12  |                     | ns    |

| See footnotes at end of tal                                                | ble.                                                                           |                                                              |                   |              |                      |                     |       |

| _                                                                          | ANDARD                                                                         | WING                                                         | SIZE<br>A         |              |                      | 5962-               | 96791 |

|                                                                            | MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216 |                                                              |                   | REVISION L   | .EVEL                | SHEET               | 0     |

9004708 0031689 089 🖿

|                                                                                              | TAE                                                                                        | BLE I. Electrical performance of                              | haracteristics - | Continued. |                 |       |       |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|------------|-----------------|-------|-------|

| 查询"5962-9679101C                                                                             | コ<br>Y Cymbol                                                                              | 亿日<br>Conditions 1/                                           | Group A          | Device     | Li              | mits  | Unit  |

|                                                                                              |                                                                                            | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified | subgroups        | type       | Min             | Max   |       |

| Delay time, HACK low to output hi-z 7/                                                       | 59                                                                                         | All signals except D(63:0)                                    | 9,10,11          | All        |                 | 1     | ns    |

|                                                                                              |                                                                                            | D(63:0)                                                       |                  |            |                 | 1     |       |

| Delay time, HREQ high<br>to HACK no longer<br>low                                            | 60                                                                                         |                                                               | 9,10,11          | All        |                 | 10    | ns    |

| Delay time, HACK high to outputs driven <u>9</u> /                                           | 61                                                                                         |                                                               | 9,10,11          | All        | 6t <sub>H</sub> |       | ns    |

| Setup time, HREQ low<br>to CLKOUT no longer<br>low                                           | 62                                                                                         |                                                               | 9,10,11          | All        | 8.5             |       | ns    |

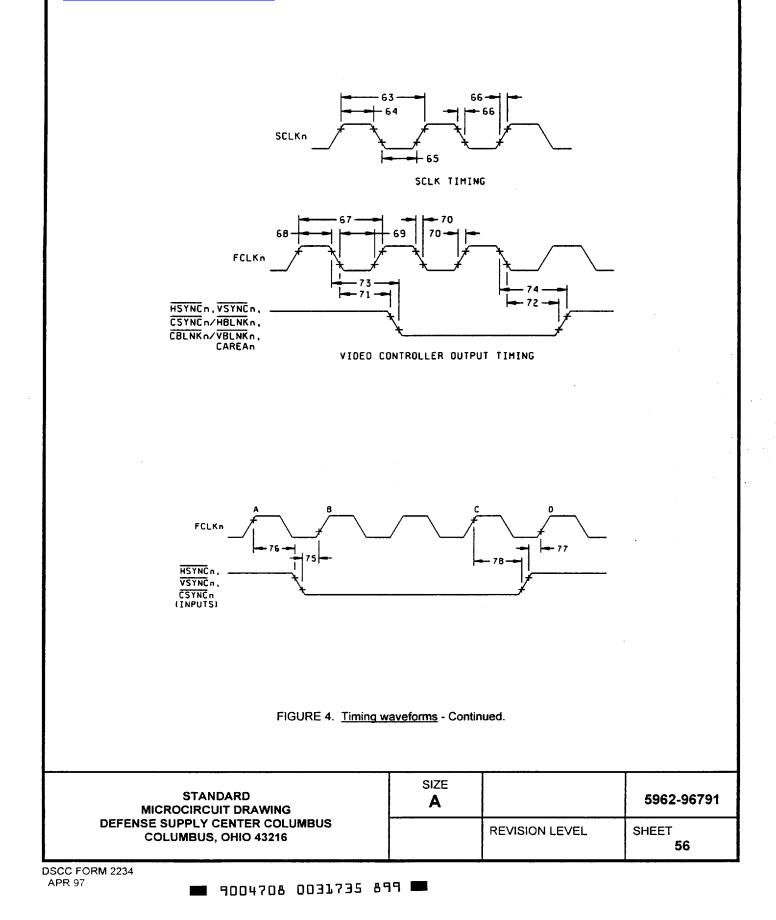

| SCLK period                                                                                  | 63                                                                                         |                                                               | 9,10,11          | All        | 13              |       | ns    |

| Pulse width, SCLK high                                                                       | 64                                                                                         |                                                               | 9,10,11          | All        | 5               |       | ns    |

| Pulse width, SCLK low                                                                        | 65                                                                                         |                                                               | 9,10,11          | All        | 5               |       | ns    |

| Transition time, SCLK<br>(rise and fall) <u>2</u> /                                          | 66                                                                                         |                                                               | 9,10,11          | All        |                 | 2     | ns    |

| FCLK period                                                                                  | 67                                                                                         |                                                               | 9,10,11          | Ali        | 25              |       | ns    |

| Pulse width, FCLK high                                                                       | 68                                                                                         |                                                               | 9,10,11          | All        | 8               |       | ns    |

| Pulse width, FCLK low                                                                        | 69                                                                                         |                                                               | 9,10,11          | All        | 8               |       | ns    |

| Transition time, FCLK<br>(rise and fall) <u>2</u> /                                          | 70                                                                                         |                                                               | 9,10,11          | All        |                 | 2     | ns    |

| Hold time, HSYNC,<br>VSYNC,<br>CSYNC/HBLNK<br>CBLNK/VBLNK or<br>CAREA high after FCLK<br>low | 71                                                                                         |                                                               | 9,10,11          | All        | 0               |       | ns    |

| Hold time, HSYNC,<br>VSYNC,<br>CSYNC/HBLNK<br>CBLNK/VBLNK or<br>CAREA low after FCLK<br>low  | 72                                                                                         |                                                               | 9,10,11          | All        | 0               |       | ns    |

| Delay time, FCLK low to<br>HSYNC, VSYNC,<br>CSYNC/HELNK<br>CELNK/VELNK or<br>CAREA low       | 73                                                                                         |                                                               | 9,10,11          | All        |                 | 20    | ns    |

| Delay time, FCLK low to<br>HSYNC, VSYNC,<br>CSYNC/HBLNK<br>CBLNK/VBLNK or<br>CAREA high      | 74                                                                                         |                                                               | 9,10,11          | All        |                 | 20    | ns    |

| See footnotes at end of ta                                                                   | ble.                                                                                       |                                                               |                  | -          |                 |       |       |

|                                                                                              | STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216 |                                                               | SIZE<br>A        |            |                 | 5962  | 96791 |

| DEFENSE SUPP                                                                                 |                                                                                            |                                                               |                  | REVISION   | EVEL            | SHEET | 11    |

■ 9004708 0031690 8TO ■

| ETB: 19/9962/96/79101CHYC 18/miles       Conditions 1/<br>subgroups       Group A<br>subgroups       Device<br>Processor       Limits       Unit         Setue time, FEYNEC<br>VEYNEC or CSYNC by<br>a FCLK no longer (on 12/2)       75       9,10,11       All       5       ns         Hold time, FEYNEC<br>VEYNEC or CSYNC by<br>a FCLK no longer (on 12/2)       76       9,10,11       All       7       ns         Setue time, FEYNEC<br>VEYNEC or CSYNC by<br>a fCLK no longer (on 12/2)       76       9,10,11       All       7       ns         Setue time, FEYNEC<br>VEYNEC or CSYNC by<br>after FCLK high 12/2       77       9,10,11       All       7       ns         Setue time, HEYNEC<br>VEYNEC or CSYNC by<br>after FCLK high 15/2       78       9,10,11       All       7       ns         JTAG       JTAG       JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                   | TABLE I.                                                                                                                       | Electrical performance cha                                                                                                                                                                                                                                              | aracteristics - C                                                                                                           | ontinued.                                                                            |                |       |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------|-------|------|

| Setue time. HSYNC<br>VSNNC or CSYNC bio<br>by FCLK notaget tow 12         75         9.10.11         All         5         ne           Heid time. HSYNC<br>VSNNC or CSYNC bio<br>after FCLK high 12         76         9.10.11         All         7         ne           Heid time. HSYNC<br>VSNNC or CSYNC bio<br>after FCLK high 12         76         9.10.11         All         7         ne           VSNNC or CSYNC bio<br>to FCLK hologet low 13         77         9.10.11         All         7         ne           VSNNC or CSYNC bio<br>to FCLK hologet low 14         9.10.11         All         7         ne           Hold time. HSYNC<br>WSNC or CSYNC bio<br>to FCLK high 12         78         9.10.11         All         7         ne           Hold time. HSYNC<br>WSNC or CSYNC bio<br>to FCLK high 12         JACG         9.10.11         All         20         ns           TMS/TDI beld from TCK high<br>to FCLK high 12         JACG         9.10.11         All         30         ns           1/ Unless otherwise specified. at lesting to be performed using worst-case test conditions. Lip is one half of the<br>output period. or equal to the input clock (parameter 1). C <sub>CCK</sub> is equal to parameter 1. AC timing waveforms<br>are as specified in figure 4.         Standard file           1/ Unless otherwise specified an standard by the<br>output period. or SAS, CASTOM(70) and A(31:0) transitions that cocur on CLKOUT edge coincident with input data<br>standard by logic and is not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 查询"5962-9679101QYC<br>Test                                                                                                                                                                                                                                                                                                                                                                                        | 供应商<br>Symbol                                                                                                                  | Conditions 1/                                                                                                                                                                                                                                                           | Group A                                                                                                                     |                                                                                      | L              | imits | Unit |

| VSYNC or CSYNC low<br>be FCLK notoger tow 12       Image: Comparison of the compari      |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                | unless otherwise specifie                                                                                                                                                                                                                                               | d                                                                                                                           | s type                                                                               | Min            | Max   | 1    |

| VSYNC or CSYNC ing and the second | VSYNC. or CSYNC low                                                                                                                                                                                                                                                                                                                                                                                               | 75                                                                                                                             |                                                                                                                                                                                                                                                                         | 9,10,11                                                                                                                     | All                                                                                  | 5              |       | ns   |