#### **General Description**

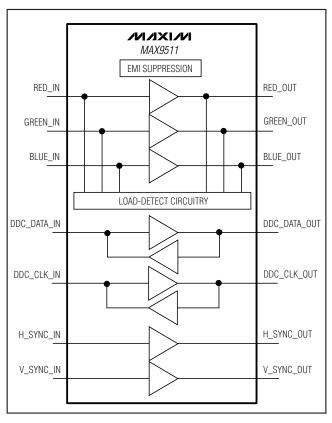

The MAX9511 provides a complete VGA interface between a graphics controller and/or docking station. The MAX9511 has output drivers with variable electromagnetic interference (EMI) suppression for graphics video and sync (RGBHV) signals and includes external load-detection circuitry.

The MAX9511 suppresses EMI emissions by limiting the slew rate (SR) rather than limiting bandwidth with fixed L-C filters. The SR controls the large-signal bandwidth without affecting the small-signal bandwidth, resulting in sharper video images, while reducing EMI. The SR of the MAX9511 provides tighter control than traditional passive L-C components, and allows the SR to track the resolution by varying an external resistor (RRX) rather than being fixed to a sub-optimal value.

The load-detection circuitry of the MAX9511 automatically detects and transmits a change in load status to the input stages when an external load (monitor, docking station, or projector) is connected. The MAX9511 is compatible with the load-detection circuitry on the digital-to-analog (DAC) outputs of most video graphics controllers. The output drivers provide 6dB of gain to compensate for the  $75\Omega$ back-termination resistors, which reduce transmission line reflections.

The RGBHV channels can be placed into shutdown to reduce power when no external load is connected.

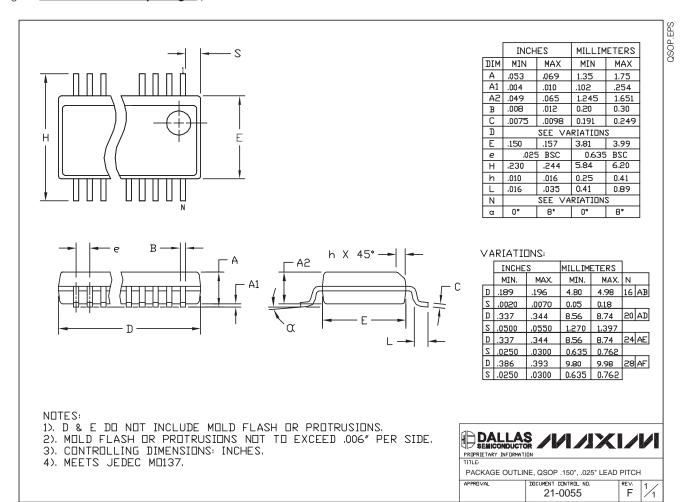

The MAX9511 operates from 3V and 5V supplies. The DDC circuitry performs bidirectional level translation from 3V to 5V logic levels. The MAX9511 is offered in a 24-pin QSOP package and is specified over the commercial 0°C to +70°C temperature range.

#### **Applications**

Notebook PCs (Laptops)

**Docking Stations**

Graphics Cards for Notebooks and Personal Computers

Personal Computer Motherboards with On-Board Video Graphics Controllers

Workstations

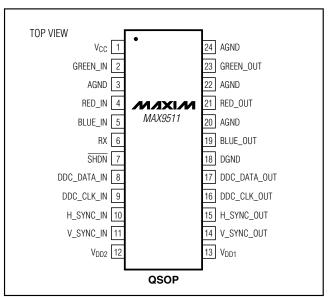

Pin Configuration appears at end of data sheet.

#### **Features**

- ♦ RGB Drivers with Adjustable Slew Rate for EMI Control

- ♦ H Sync and V Sync Drivers with Level Translation

- **♦** Bidirectional Level Translators for DDC Support

- ♦ Simultaneously Drives External Monitor/Projector and Docking Station without Analog RGB Switches-No Stub Reflections

- ♦ Eliminates Up to 34 External Components

- ♦ Small 24-Pin QSOP Package

#### **Ordering Information**

| PART        | TEMP RANGE   | PIN-<br>PACKAGE | PKG<br>CODE |

|-------------|--------------|-----------------|-------------|

| MAX9511CEG  | 0°C to +70°C | 24 QSOP         | E24-2       |

| MAX9511CEG+ | 0°C to +70°C | 24 QSOP         | E24-2       |

+Denotes a lead-free package.

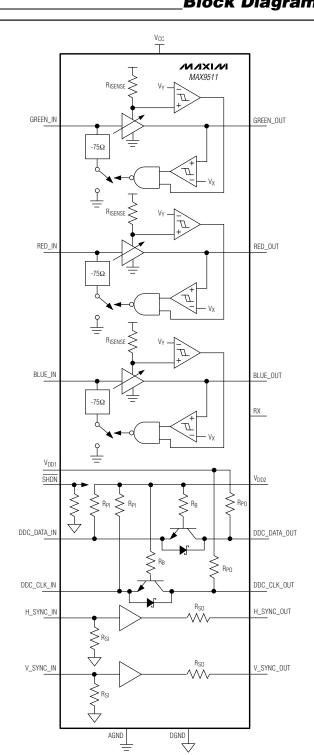

### **Simplified Block Diagram**

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to AGND0.3V to +6V                        | DDC   |

|-----------------------------------------------------------|-------|

| V <sub>DD1</sub> , V <sub>DD2</sub> to DGND0.3V to +6V    | to    |

| DGND to AGND0.1V to +0.1V                                 | DDC   |

| RED_IN, GREEN_IN, BLUE_IN to AGND0.3V to (VCC + 0.3V)     | to    |

| RED_OUT, GREEN_OUT, BLUE_OUT                              | DDC   |

| to AGND0.3V to (V <sub>CC</sub> + 0.3V)                   | to    |

| RX to AGND0.3V to (V <sub>CC</sub> + 0.3V)                | DDC   |

| H_SYNC_IN, V_SYNC_IN, SHDN                                | DDC   |

| to DGND0.3V to (V <sub>DD2</sub> + 0.3V)                  | Cont  |

| H_SYNC_OUT, V_SYNC_OUT                                    | 2     |

| to DGND0.3V to (V <sub>DD1</sub> + 0.3V)                  | Opei  |

| DDC_DATA_IN                                               | Stora |

| to DGND(DDC_DATA_OUT - 0.3V) to (V <sub>DD2</sub> + 0.3V) | Leac  |

| DDC_DATA_OUT to DGND(DDC_DATA_IN - 0.1V) to (V <sub>DD1</sub> + 0.3V)                          |

|------------------------------------------------------------------------------------------------|

| DDC_CLK_IN to DGND(DDC_CLK_OUT - 0.3V) to (V <sub>DD2</sub> + 0.3V)                            |

| DDC_CLK_OUT                                                                                    |

| to DGND(DDC_CLK_IN - 0.1V) to (V <sub>DD1</sub> + 0.3V) DDC_DATA_OUT to DDC_DATA_IN0.1V to +6V |

| DDC_CLK_OUT to DDC_CLK_IN0.1V to +6V Continuous Power Dissipation (T <sub>A</sub> = +70°C)     |

| 24-Pin QSOP (derate 9.5mW/°C above +70°C)762mW                                                 |

| Operating Temperature Range0°C to +70°C Storage Temperature Range65°C to +150°C                |

| Lead Temperature (soldering, 10s)+300°C                                                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC}=5V,\,V_{DD1}=5V,\,V_{DD2}=\overline{SHDN}=3V,\,R_L=150\Omega$  to AGND, DGND = AGND, RRX =  $7k\Omega$  to AGND, TA = 0°C to +70°C. Typical values are at TA = +25°C.)

| PARAMETER                              | SYMBOL             | CONDITIONS                                                           |                         | MIN  | TYP   | MAX  | UNITS |

|----------------------------------------|--------------------|----------------------------------------------------------------------|-------------------------|------|-------|------|-------|

|                                        | Vcc                | Inferred from PSRR Inferred from logic test Inferred from logic test |                         | 4.5  |       | 5.5  |       |

| Supply Voltage Range                   | V <sub>DD1</sub>   |                                                                      |                         | 4.5  |       | 5.5  | V     |

|                                        | $V_{\mathrm{DD2}}$ |                                                                      |                         | 2.3  |       | 3.6  |       |

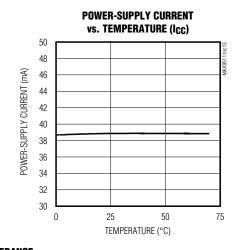

|                                        |                    | SHDN = V <sub>DD2</sub>                                              | $R_{RX} = 7k\Omega$     |      | 38    | 50   |       |

|                                        | Icc                |                                                                      | $R_{RX} = 36k\Omega$    |      | 25    | 35   |       |

|                                        |                    | SHDN = DGND                                                          |                         |      | 0.15  | 0.25 | mA    |

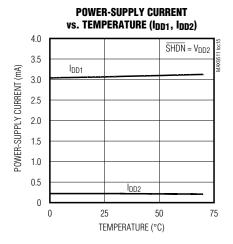

| Quiescent Supply Current               |                    | SHDN = V <sub>DD2</sub>                                              | SHDN = V <sub>DD2</sub> |      | 3     | 6    |       |

|                                        | I <sub>DD1</sub>   | SHDN = DGND                                                          |                         |      | 0.027 | 0.08 |       |

|                                        | I <sub>DD2</sub>   | SHDN = V <sub>DD2</sub>                                              |                         |      | 220   | 500  | μА    |

|                                        |                    | SHDN = DGND                                                          |                         |      | 26    | 40   |       |

| VIDEO                                  |                    |                                                                      |                         |      |       |      |       |

| Input Voltage Range                    | VIN                | Inferred from voltage gain                                           |                         | 0    | 0.7   | 0.9  | V     |

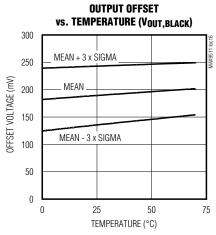

| Output Black Level Voltage             | Vout, BLACK        | RED_IN = GREEN_IN = BLUE_IN = AGND                                   |                         | 5    | 65    | 160  | mV    |

| Voltage Gain                           | Av                 | $0 \le V_{IN} \le 0.9V, R_L = 75\Omega$                              |                         | +1.9 | +2    | +2.1 | V/V   |

| Gain Matching                          | $\Delta A_{V}$     | $0 \le V_{IN} \le 0.9V, R_L = 75\Omega$                              |                         |      | 1     | 2    | %     |

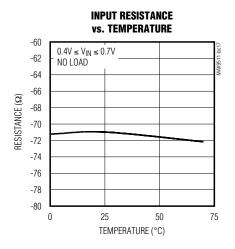

| Input Resistance                       | R <sub>IN</sub>    | $0 \le V_{IN} \le 1V$ , with load                                    |                         | 10   | 100   |      | kΩ    |

| input nesistance                       | MIN                | $0.4V \le V_{IN} \le 0.7V$ , no load                                 |                         | -85  | -74   | -62  | Ω     |

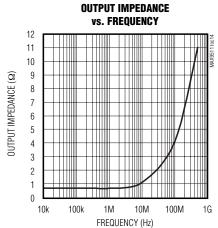

| Output Impedance                       | Zout               | f = 100kHz                                                           | f = 100kHz              |      | 0.64  |      | Ω     |

| Output Short-Circuit Current (To AGND) | lout               |                                                                      |                         |      | 40    |      | mA    |

| Load-Detection Voltage                 | V <sub>X_IN</sub>  | (Note 1)                                                             |                         |      |       | 0.2  | V     |

| Output Load Detection                  | R <sub>L_OUT</sub> | $V_{IN} = 0.4V$                                                      |                         | 180  |       |      | Ω     |

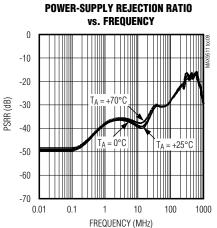

| Power-Supply Rejection                 | PSRR               | 4.5V ≤ V <sub>CC</sub> ≤ 5.5V, V <sub>IN</sub> = 0.5V                |                         | 40   | 57    |      | dB    |

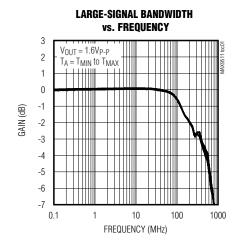

| Large-Signal Bandwidth                 |                    | $V_{OUT} = 1.6V_{P-P}, R_{RX} = 7k\Omega$                            |                         |      | 370   |      | MHz   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=5V,\,V_{DD1}=5V,\,V_{DD2}=\overline{SHDN}=3V,\,R_L=150\Omega \text{ to AGND, DGND}=AGND,\,R_{RX}=7k\Omega \text{ to AGND, }T_A=0^{\circ}\text{C to }+70^{\circ}\text{C}.$  Typical values are at  $T_A=+25^{\circ}\text{C}.)$

| PARAMETER                         | SYMBOL                                                        | CONDITIONS                                  |                                                                    | MIN                       | TYP   | MAX                       | UNITS             |

|-----------------------------------|---------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------|---------------------------|-------|---------------------------|-------------------|

| Ol D-t- (N-t 0, 0)                | 00                                                            | $R_{RX} = 36k\Omega$ , $T_A = +25^{\circ}C$ |                                                                    | 250                       | 330   | 450                       | \ // <sub>2</sub> |

| Slew Rate (Notes 2, 3)            | SR                                                            | $R_{RX} = 7k\Omega$ , $T_A = +25^{\circ}C$  |                                                                    | 900                       | 1100  | 1300                      | V/µs              |

| Settling Time                     | ts                                                            | (Notes 4, 5)                                |                                                                    |                           | 0     |                           | ns                |

| Undershoot/Overshoot              | tos, tus                                                      |                                             |                                                                    |                           | ±1    |                           | %                 |

| Linearity Error                   | LE                                                            | V <sub>IN</sub> = 700m                      | V <sub>P-P</sub> (Notes 6, 7)                                      |                           | 0.036 |                           | %                 |

| Peak Signal-to-Noise Ratio        | SNR                                                           | f = 100kHz t                                | o 100MHz, V <sub>IN</sub> = 700mV <sub>P-P</sub>                   |                           | 50    |                           | dB                |

| Channel-to-Channel Skew           | Δt                                                            | R to G to B                                 | (Note 3)                                                           |                           | 500   | 1100                      | ps                |

| Power-Supply Rejection<br>Ratio   | PSRR                                                          | f = 100kHz                                  |                                                                    |                           | 49    |                           | dB                |

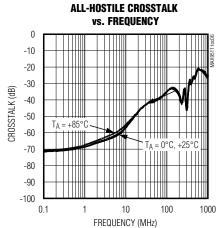

| Crosstalk                         |                                                               | All hostile, f                              | = 10MHz                                                            |                           | 55    |                           | dB                |

| Input Termination Switch<br>Delay | $\Delta$ tswd                                                 |                                             |                                                                    |                           | 70    |                           | ns                |

| LOGIC                             |                                                               |                                             |                                                                    |                           |       |                           |                   |

| Input Low Level                   | V <sub>IL</sub>                                               | H_SYNC_IN                                   | N, V_SYNC_IN and SHDN                                              |                           |       | 0.3 x<br>V <sub>DD2</sub> | V                 |

| Input High Level                  | VIH                                                           | H_SYNC_IN, V_SYNC_IN and SHDN               |                                                                    | 0.7 x<br>V <sub>DD2</sub> |       |                           | V                 |

| Output Low Level                  | V <sub>OL</sub>                                               | $I_{OL} = 4mA$                              | H_SYNC_OUT, VH_SYNC_IN = DGND<br>V_SYNC_OUT, VV_SYNC_IN = DGND     |                           |       | 0.55                      |                   |

|                                   |                                                               | I <sub>OL</sub> = 50µA                      | DDC_DATA_IN, VDDC_DATA_OUT = DGND  DDC_CLK_IN, VDDC_CLK_OUT = DGND |                           |       | 0.4                       | V                 |

|                                   |                                                               | I <sub>OL</sub> = 3mA                       | DDC_DATA_OUT, VDDC_DATA_IN = DGND  DDC_CLK_OUT, VDDC_CLK_IN = DGND |                           |       | 0.5                       |                   |

|                                   |                                                               | I <sub>OH</sub> = 4mA                       | H_SYNC_OUT, VH_SYNC_IN = VDD2  V_SYNC_OUT, VV_SYNC_IN = VDD2       | V <sub>DD1</sub><br>- 1.5 |       |                           |                   |

| Output High Level                 | V <sub>OH</sub> I <sub>OH</sub> = 50μA I <sub>OH</sub> = 50μA |                                             | DDC_DATA_IN, VDDC_DATA_OUT = VDD1 DDC_CLK_IN, VDDC_CLK_OUT = VDD1  | V <sub>DD2</sub><br>- 0.4 |       |                           | V                 |

|                                   |                                                               | _                                           | DDC_DATA_OUT, VDDC_DATA_IN = VDD2 DDC_CLK_OUT, VDDC_CLK_IN = VDD2  | V <sub>DD1</sub><br>- 1.5 |       |                           |                   |

| SYNC Output Resistance            | Rso                                                           |                                             | •                                                                  | 35                        | 55    | 85                        | Ω                 |

| SHDN Pulldown Resistance          | R <sub>SD</sub>                                               |                                             |                                                                    | 225                       | 330   | 500                       | kΩ                |

| SYNC Input Resistance             | Rsi                                                           |                                             |                                                                    | 30                        | 47    | 70                        | kΩ                |

| DDO Dullum De -i-t                | Rpo                                                           | DDC_DATA                                    | A_OUT, DDC_CLK_OUT                                                 | 2                         | 3     | 4                         | Lo                |

| DDC Pullup Resistance             | Rpi                                                           | DDC_DATA_IN, DDC_CLK_IN                     |                                                                    |                           | 4.7   | 6.5                       | kΩ                |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=5V,\,V_{DD1}=5V,\,V_{DD2}=\overline{SHDN}=3V,\,R_L=150\Omega$  to AGND, DGND = AGND,  $R_{RX}=7k\Omega$  to AGND,  $T_A=0^{\circ}C$  to +70°C. Typical values are at  $T_A=+25^{\circ}C$ .)

| PARAMETER         | SYMBOL                         | CONDITIONS                                                                                                    |                                        |    | TYP  | MAX | UNITS |

|-------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|----|------|-----|-------|

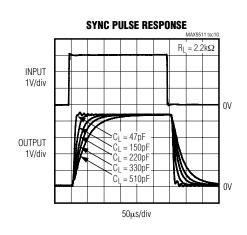

|                   |                                | All SYNC outputs                                                                                              | $C_{SYNC} = 47pF, T_A = +25^{\circ}C$  |    | 7    |     |       |

| Rise/Fall Time    | t <sub>R</sub> /t <sub>F</sub> | (Notes 2, 3)                                                                                                  | $C_{SYNC} = 470pF, T_A = +25^{\circ}C$ | 50 | 70   | 100 | ns    |

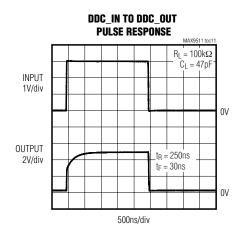

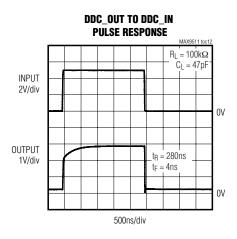

|                   |                                | DDC only, C <sub>L</sub> = 47pF                                                                               |                                        |    | 400  |     |       |

| Propagation Delay | tplh, tphl                     | SYNC, C <sub>SYNC</sub> = 47pF, T <sub>A</sub> = +25°C (Notes 3, 8)                                           |                                        |    | 12   | 22  | ns    |

| Enable Time       |                                | $V_{IN} = 0.7 V_{P-P}$ , $\overline{SHDN}$ from DGND to $V_{DD2}$ , outputs settle to ±1% of final value      |                                        |    | 1200 |     | ns    |

| Disable Time      |                                | $V_{IN} = 0.7 V_{P-P}$ , $\overline{SHDN}$ from $V_{DD2}$ to DGND, outputs settle to $\pm 1\%$ of final value |                                        |    | 400  |     | ns    |

- **Note 1:** This is the voltage at which the input termination switches;  $V_{IN} > V_{X}|_{IN} =$  switch open,  $V_{IN} < V_{X}|_{IN} =$  switch closed.

- Note 2: Measured between the 10% to 90% points on rising or falling edge.

- Note 3: Not production tested. Guaranteed by design.

- Note 4: Measured from the END of overshoot/undershoot to ±5% of final value.

- **Note 5:**  $V_{IN} = 700 \text{mV}$  with a rise time >1ns.

- **Note 6:** Linearity error is the maximum difference between the actual and measured output of a video ramp. Done in accordance with VESA Test Procedure, Version 1, 6/11/2001.

- Note 7: Linearity error measured as percentage of full scale.

- Note 8: Propagation delay is the time difference between the VDD2 / 2 input crossing and the 1.4V output crossing.

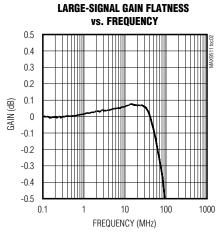

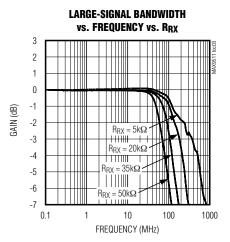

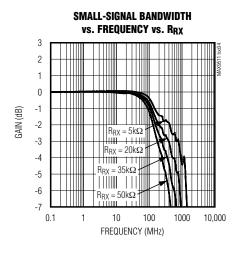

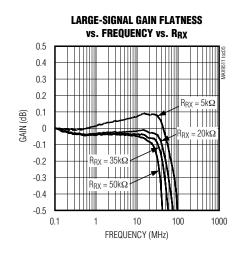

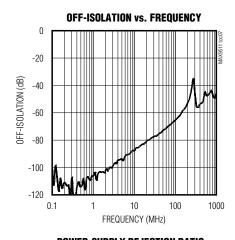

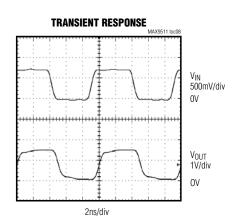

### Typical Operating Characteristics

$(V_{CC} = 5V, V_{DD1} = 5V, V_{DD2} = 3V, R_L = 150\Omega$  to AGND,  $R_{RX} = 7k\Omega$  to AGND,  $T_A = +25$ °C, unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 5V, V_{DD1} = 5V, V_{DD2} = 3V, R_L = 150\Omega$  to AGND,  $R_{RX} = 7k\Omega$  to AGND,  $T_A = +25$ °C, unless otherwise noted.)

### \_Typical Operating Characteristics (continued)

$(V_{CC} = 5V, V_{DD1} = 5V, V_{DD2} = 3V, R_L = 150\Omega$  to AGND,  $R_{RX} = 7k\Omega$  to AGND,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

### \_Typical Operating Characteristics (continued)

$(V_{CC} = 5V, V_{DD1} = 5V, V_{DD2} = 3V, R_L = 150\Omega$  to AGND,  $R_{RX} = 7k\Omega$  to AGND,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

### **Pin Description**

| PIN           | NAME             | FUNCTION                                                                                      |

|---------------|------------------|-----------------------------------------------------------------------------------------------|

| 1             | V <sub>C</sub> C | Analog Power Supply                                                                           |

| 2             | GREEN_IN         | Green Video Input                                                                             |

| 3, 20, 22, 24 | AGND             | Analog Ground                                                                                 |

| 4             | RED_IN           | Red Video Input                                                                               |

| 5             | BLUE_IN          | Blue Video Input                                                                              |

| 6             | RX               | Slew-Rate Control. Connect an external resistor from RX to AGND.                              |

| 7             | SHDN             | Active-Low Shutdown. For normal operation connect to VDD2. SHDN is internally pulled to DGND. |

| 8             | DDC_DATA_IN      | DDC Data Input. Defaults to V <sub>DD2</sub> through an internal pullup resistor.             |

| 9             | DDC_CLK_IN       | DDC Clock Input. Defaults to V <sub>DD2</sub> through an internal pullup resistor.            |

| 10            | H_SYNC_IN        | Horizontal SYNC Input. Defaults to AGND through an internal pulldown resistor.                |

| 11            | V_SYNC_IN        | Vertical SYNC Input. Defaults to AGND through an internal pulldown resistor.                  |

| 12            | V <sub>DD2</sub> | SYNC/DDC 3V Supply                                                                            |

| 13            | V <sub>DD1</sub> | SYNC/DDC 5V Supply. Supplies 5V to SYNC and DDC output circuitry.                             |

| 14            | V_SYNC_OUT       | Vertical Sync Output                                                                          |

| 15            | H_SYNC_OUT       | Horizontal Sync Output                                                                        |

| 16            | DDC_CLK_OUT      | DDC Clock Output. Defaults to VDD1 through an internal pullup resistor.                       |

| 17            | DDC_DATA_OUT     | DDC Data Output. Defaults to V <sub>DD1</sub> through an internal pullup resistor.            |

| 18            | DGND             | Digital Ground                                                                                |

| 19            | BLUE_OUT         | Blue Video Output                                                                             |

| 21            | RED_OUT          | Red Video Output                                                                              |

| 23            | GREEN_OUT        | Green Video Output                                                                            |

#### **Block Diagram**

#### **Detailed Description**

The MAX9511 solves several difficult problems in interfacing a video graphics controller to a VGA port and/or the docking station connector. First, there is a trade-off between video quality and EMI. The usual method for reducing EMI is to insert a fixed-frequency LC  $\pi$ -filter between the video DAC output and the connector. Given the large component variation of the capacitors and inductors, the frequency response is sharply reduced to meet EMI requirements. As a result, video quality suffers making sharp transitions in the video soft. The MAX9511 video drivers have a variable slew rate, which limits electromagnetic emissions and can be adjusted by an external resistor. As a result, the slew rate of the MAX9511 can be varied to reduce electromagnetic emissions at a given resolution, maximizing video quality. Since the slew rate is variable and set by a resistor instead of fixed by capacitors and inductors, video performance and electromagnetic emissions are consistent during production.

The MAX9511 also has horizontal and vertical sync output drivers, bidirectional level translators for DDC support, and external load-detection circuits that correctly transfer information about the external load to the video graphics controller.

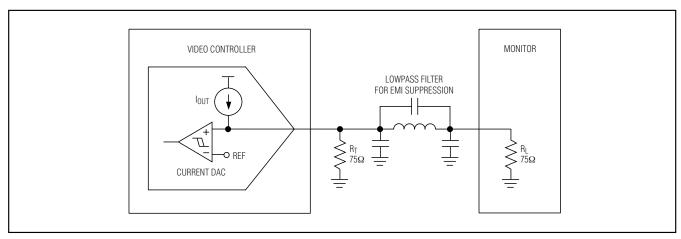

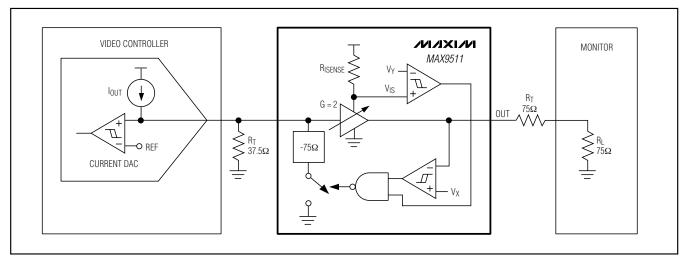

#### **Load Detection**

Most notebook computers implement a power-saving load-detection circuit that disables the external monitor output when no monitor is plugged into the rear panel VGA connector as shown in Figure 1. Upon startup or on command, the video controller generates a sequence of detection pulses out of the current DAC shown, that results in an output voltage of above 315mV when an external monitor (RL) is connected, and above 630mV when disconnected. If the monitor is disconnected at the time of the pulse, the comparator inside the notebook trips and disables the video. When the monitor is plugged in, the resulting pulse will not trip the comparator and the video is enabled.

If the lowpass filter is simply replaced with an amplifier. the monitor termination RL is isolated from the video controller and the conventional load-detection scheme does not work.

For this reason, the MAX9511 includes the load-detection circuit. When R<sub>I</sub> is connected (i.e., the monitor is plugged in) to the output of the MAX9511, the internal load-detection circuit disconnects the synthesized -75 $\Omega$  resistor from the input. The resulting  $37.5\Omega$  resistance at the DAC output indicates to the DAC's internal load-detection circuit that the monitor is plugged in. Removing RL (i.e., disconnecting the monitor) causes the MAX9511's load-detection circuit to connect the synthesized -75 $\Omega$

Figure 1. Conventional Load-Detection Scheme

Figure 2. Load-Detection Scheme with MAX9511

resistor to the input. This results in an equivalent impedance of  $75\Omega$  at the DAC output, which indicates to the video controller's internal load-detection circuit that the load is disconnected and the video controller shuts down the video output. Figure 2 and Table 1 demonstrate how the MAX9511 load-detection circuit operates in conjunction with the video controller load detection.

#### **Output Video Signal Level Shift**

The video signal at the MAX9511 output is shifted upwards by approximately 240mV from the input to keep the output stage of the video driver in a linear region of operation. At the connector, the video signal is attenuated by 6dB, canceling the 6dB gain of the video driver. The 240mV level shift is also attenuated by

6dB, and hence the actual video signal seen by the load is only 120mV higher than the video signal at the input of the MAX9511. Monitors and other display devices AC-couple the input signal so the 120mV level shift should not affect the displayed video image.

# Table 1. Function of Load-Detection Scheme

| AMPLIFIER OUTPUT               | MAX9511<br>INTERNAL<br>SWITCH | RESISTANCE<br>AT DAC<br>OUTPUT |  |

|--------------------------------|-------------------------------|--------------------------------|--|

| Connected to External Load     | Open                          | 37.5Ω                          |  |

| Not Connected to External Load | Closed                        | 75Ω                            |  |

#### **Vertical and Horizontal SYNC**

The MAX9511 has separate, noninverting, vertical and horizontal sync buffers. Both sync inputs can level-shift an input as low as 2.3V to a 5V output. Both sync drivers have hysteresis at their input to prevent "chatter" in their outputs. The sync output drivers have a  $55\Omega$  (typ) output impedance (Rso) to match the cable impedance used for vertical and horizontal sync in most applications. Both sync inputs are pulled to DGND through a  $47k\Omega$  resistor if the controller's SYNC source goes high impedance, or if the inputs are left floating, avoiding ambiguous output conditions.

EMI can result from rapid transitions of the sync or the video signals. To reduce the rise and fall times of the sync signal, additional capacitance may be added to the sync outputs. Adding additional capacitance may require "recentering" the display.

#### **Display Data Channel (DDC)**

The MAX9511 bidirectional display data channel (DDC) level translator allows for a lower voltage video controller logic to operate with a higher voltage external monitor logic. Power supplied at  $V_{DD2}$  defines the DDC input voltage thresholds while power supplied at  $V_{DD1}$  defines the DDC output thresholds. Two Schottky-clamped npn transistors shift the lower level DDC inputs to higher logic-level outputs.

DDC\_CLK\_OUT and DDC\_DATA\_OUT are pulled to V<sub>DD1</sub> by internal pullup resistors to prevent ambiguous conditions when left floating. At shutdown, DDC inputs can still respond to external commands.

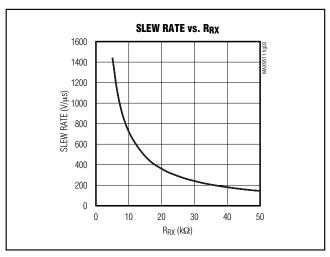

#### Slew-Rate Limiting

The MAX9511 outputs are slew-rate limited to reduce EMI. Slew-rate limiting affects the large-signal bandwidth (LSBW) more than the small-signal bandwidth (SSBW), and can be scaled according to the following formula:

$$LSBW(-3dB) = \frac{SR}{2 \times \pi \times V_{OUT}}$$

where  $V_{OUT}$  is the output signal's peak-to-peak voltage and LSBW(-3dB) is the -3dB bandwidth.

The slew rate of the MAX9511 is controlled by a resistor between RX and AGND. The resistor (R<sub>RX</sub>) can be varied to optimize the EMI suppression to the display resolution while preserving the display quality. The R<sub>RX</sub> range is approximately  $7k\Omega$  for maximum slew rate and  $50k\Omega$  for minimum slew rate (see Figure 3). Slew-rate limiting can be approximated by:

$$SR = 1030 \left( \frac{7000}{R_{BX}} \right) (V/\mu s)$$

Figure 3. Slew Rate vs. RRX

#### Shutdown

The MAX9511 features a low-power shutdown mode for battery-powered/portable applications. Shutdown reduces the quiescent current of the video and sync drivers. Connecting  $\overline{SHDN}$  to ground (DGND) disables the outputs and places the MAX9511 into a low-power shutdown mode.  $\overline{SHDN}$  has a  $330k\Omega$  (typ) internal pulldown resistor to DGND. Connect  $\overline{SHDN}$  to VDD2 for normal operation.

### \_Applications Information

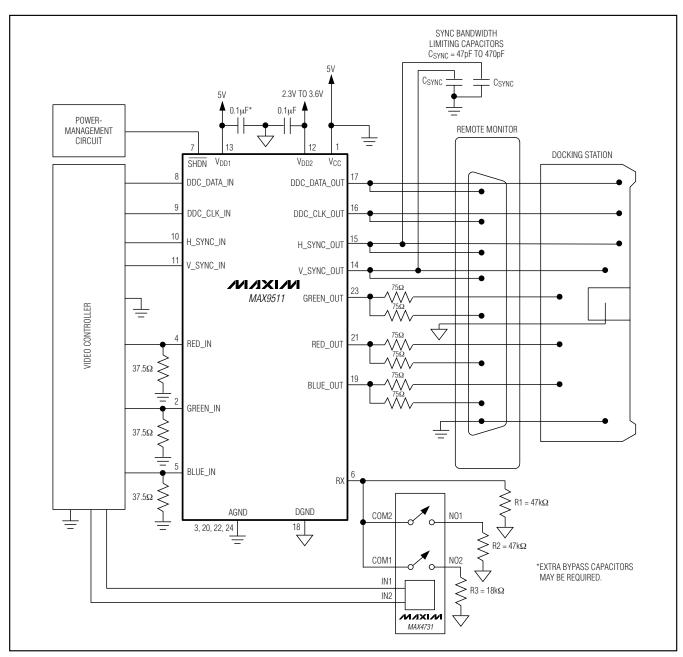

#### Customizing Slew Rates for Different Resolutions

When the MAX9511 connects to devices of different resolutions, different slew rates should be used. The slew rate of the MAX9511 is adjustable by varying RRX between  $7k\Omega$  and  $50k\Omega$ . By selecting a valid RRX value for a resolution, the MAX9511 minimizes the EMI and optimizes the video output quality. Shown are two configurations to adjust slew rates using different RRX values for different video resolutions.

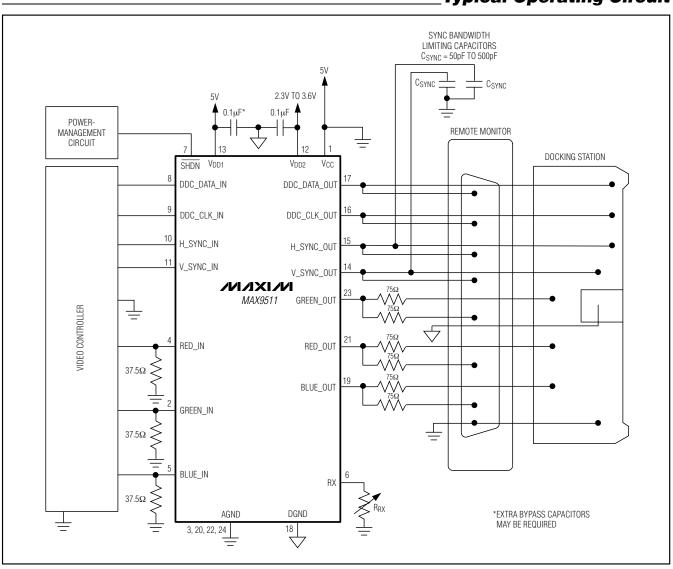

Figure 4 shows how to customize slew rates for three resolutions. This circuit provides three predetermined slew rates by paralleling resistors to create three RRX values. The combination is controlled by a digital command from the video controller through a switch. This requires that the sample clock rates used by different resolutions are close. The sync bandwidth-limiting capacitors (CSYNC) are set for the highest resolution.

Figure 4. Three Resolution Slew-Rate Control

Figure 4 showcases the setup for three commonly used resolutions:  $1600 \times 1200$ ,  $1280 \times 1024$ , and  $1024 \times 768$ . Since the resolution change is relatively slow, the switch does not have to be fast. The impedance of the switch does not need to be low compared to R<sub>RX</sub>. When using a high-impedance switch, the resistance

from the switch should be included to calculate R<sub>RX</sub>. The MAX4731 50 $\Omega$  SPST analog switch shown in the figure is used with three external resistors to get R<sub>RX</sub> values of 10k $\Omega$ , 23.5k $\Omega$ , and 47k $\Omega$  for 1600 x 1200, 1280 x 1024, and 1024 x 768 resolutions, respectively.

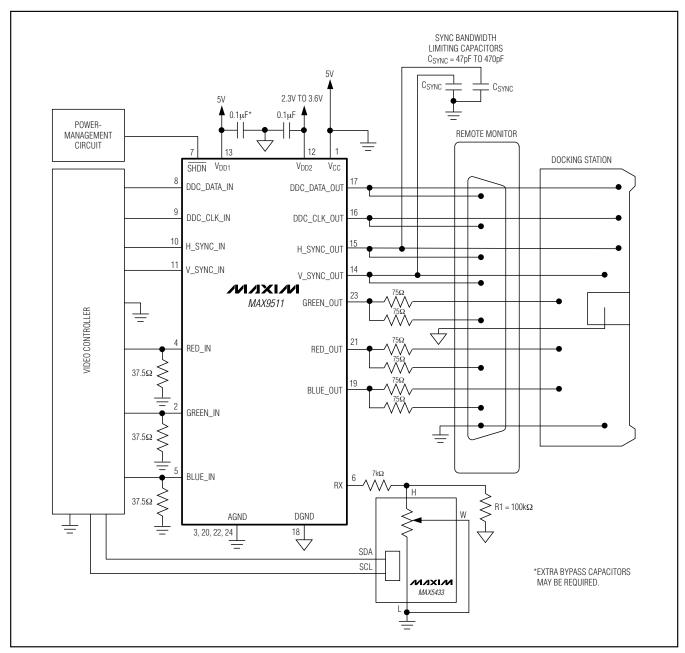

Figure 5. Slew-Rate Control with a Digital Potentiometer

The circuit in Figure 5 uses a MAX5433 digital potentiometer to provide more flexibility in customizing slew rates. An  $100k\Omega$  external trim resistor is placed in paral-

lel with the  $100k\Omega$  MAX5433 to limit the maximum value of RRX to  $50k\Omega$ . This setup provides 33 levels of RRX values through the I<sup>2</sup>C control ports at the MAX5433.

#### **Power Supplies**

The MAX9511 operates with a 4.5V to 5.5V power supply for video (RGBHV), while DDC and SYNC operate from 2.3V to 3.6V and 4.5V to 5.5V supplies.

#### **SYNC Bandwidth-Limiting Capacitors**

The output impedance, Rso, of the MAX9511 and an additional capacitance (Csync) can form a lowpass filter that reduces the jitter of the sync output signal. With Rso ( $55\Omega$  typ) sync output impedance, the -3dB point of the lowpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{SO} C_{SYNC}}$$

Choose Csync so f-3dB is well above the highest frequency of interest.

#### Power-Supply Bypassing and Ground Management

The MAX9511's high-frequency performance requires proper layout and bypassing. For best performance, place components as close to the device as possible.

Digital or AC transient signals on AGND can create noise at the outputs. Return AGND to the lowest impedance ground available. Bypass the analog supply (VCC) with a 4.7µF capacitor paralleled with a 0.22µF and 0.001µF capacitor to AGND, placed as close to the device as possible. Bypass the digital supplies (VDD1, VDD2) with a 0.1µF capacitor to DGND, placed as close to the device as possible. Careful PC board ground layout minimizes crosstalk between the outputs.

### Pin Configuration

#### **Chip Information**

TRANSISTOR COUNT: 353 PROCESS: BIPOLAR

### **Typical Operating Circuit**

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### \_Revision History

Pages changed at Rev 3: 1, 6, 13, 15

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600