## **High Efficiency Charge Pump Converter**

The NCP5603 is an integrated circuit dedicated to the medium power White LED applications. The power conversion is achieved by means of a charge pump structure, using two external ceramic capacitors, making the system extremely tiny. The device supplies a constant voltage to the load from a low battery voltage source. It is particularly suited for the High Efficiency LED used in low cost, low power applications, with high extended battery life.

#### **Features**

- Wide Battery Supply Voltage Range:  $2.7 < V_{CC} < 5.5 \text{ V}$

- Automatic Operating Mode 1X, 1.5X and 2X Improves Efficiency

- Dimmable Output Current

- Up to 350 mA Output Pulsed Current

- Selectable Output Voltage

- High Efficiency Up To 90%

- Supports 2.5 kV ESD, Human Body Model

- Supports 200 V Machine Model ESD

- Low 40 mA Short Circuit Current

- Pb-Free Package is Available

#### **Applications**

- High Power LED

- Back Light Display

- High Power Flash

#### ON Semiconductor®

http://onsemi.com

#### MARKING DIAGRAM

DFN10 MN SUFFIX CASE 485C

5603 = Specific Device Code A = Assembly Location L = Wafer Lot

L = Wafer Lot Y = Year W = Work Week ■ = Pb–Free Package

#### **PIN CONNECTIONS**

| V <sub>out</sub> | [1] | 10 | C2P |

|------------------|-----|----|-----|

| C1P              | 2   | 9  | C1N |

| $V_{\text{bat}}$ | 3   | 8  | GND |

| Fsel             | 4   | 7  | C2N |

| Vsel             | 5   | 6  | EN  |

(Top View)

#### ORDERING INFORMATION

| Device       | Package                 | Shipping <sup>†</sup> |

|--------------|-------------------------|-----------------------|

| NCP5603MNR2  | QFN10, 3x3              | 3000/ Tape & Reel     |

| NCP5603MNR2G | QFN10, 3x3<br>(Pb-Free) | 3000/ Tape & Reel     |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

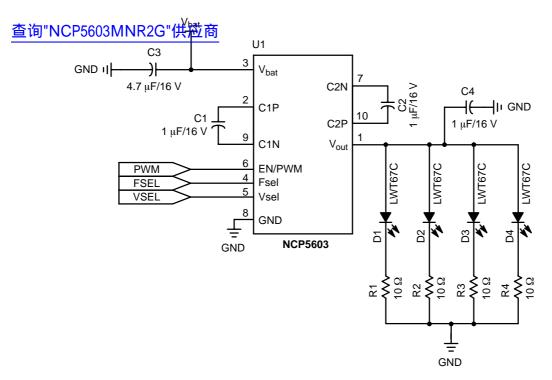

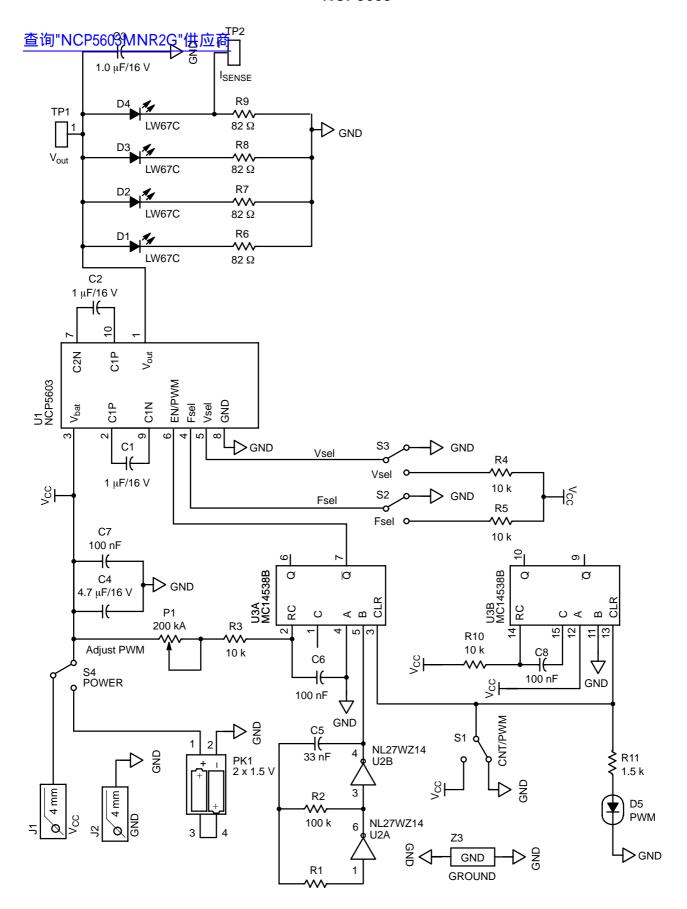

Figure 1. Typical Application

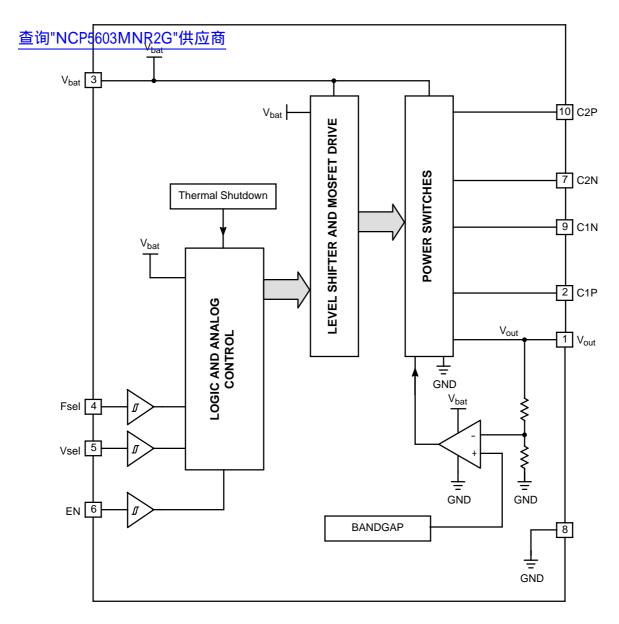

Figure 2. Block Diagram

#### **智順FUNCFION DESCRIPTION**应商

|     | 查明 WCP5005HPVREG I YYY I I I I I I I I I I I I I I I I |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|--------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin | Symbol                                                 | Type           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1   | V <sub>out</sub>                                       | OUTPUT, PWR    | This pin supplies the regulated voltage to the external LED. Since high current transients are present in this pin, care must be observed to avoid voltage spikes in the system. Good high frequency layout technique must be observed.                                                                                                                                                                                                                                             |

| 2   | C1N                                                    | POWER          | One side of the external charge pump capacitor ( $C_{FLY}$ ) is connected to this pin, associated with C1P, pin 9. Using low ESR ceramic capacitor is recommended to optimize the Charge Pump efficiency.                                                                                                                                                                                                                                                                           |

| 3   | $V_{bat}$                                              | POWER          | This pin shall be connected to the power source, and must be decoupled to Ground by a low ESR capacitor (2.2 $\mu$ F/6.3 V ceramic or better (see Note 1)).                                                                                                                                                                                                                                                                                                                         |

| 4   | Fsel                                                   | INPUT, Digital | This pin is used to program the operating frequency: Fsel = $0 \rightarrow$ Fop = 262 kHz Fsel = $1 \rightarrow$ Fop = 650 kHz                                                                                                                                                                                                                                                                                                                                                      |

| 5   | Vsel                                                   | INPUT, Digital | This pin setup the output voltage: $Vsel = 0 \rightarrow V_{out} = 4.5 \text{ V}$ $Vsel = 1 \rightarrow V_{out} = 5.0 \text{ V}$                                                                                                                                                                                                                                                                                                                                                    |

| 6   | EN/PWM                                                 | INPUT, Digital | This pin controls the activity of the NCP5603 chip:  EN/PWM = Low → the chip is deactivated, the load is disconnected  EN/PWM = High → the chip is activated and the load is connected to the regulated output current.  The NCP5603 can operate either in a continuous mode (EN/PWM = High), or can be controlled by a PWM pulse applied to EN/PWM to dim the output light. When EN/PWM is Low, the external load is disconnected from the converter, providing a very low standby |

|     |                                                        |                | current. The pull down built–in resistance makes sure the chip is deactivated even if the EN/PWM pin is disconnected (see Note 2).                                                                                                                                                                                                                                                                                                                                                  |

| 7   | C2N                                                    | POWER          | One side of the external charge pump capacitor (C <sub>FLY</sub> ) is connected to this pin, associated with C2P, pin 10. Using low ESR ceramic capacitor is recommended to optimize the Charge Pump efficiency.                                                                                                                                                                                                                                                                    |

| 8   | GND                                                    | GROUND         | This pin combines the Signal ground and the Power ground and must be connected to the system ground. Using good quality ground plane is mandatory to avoid spikes on the logic signal lines.                                                                                                                                                                                                                                                                                        |

| 9   | C1P                                                    | POWER          | One side of the external charge pump capacitor (C <sub>FLY</sub> ) is connected to this pin, associated with C1N, pin 2. Using low ESR ceramic capacitor is recommended to optimize the Charge Pump efficiency.                                                                                                                                                                                                                                                                     |

| 10  | C2P                                                    | POWER          | One side of the external charge pump capacitor is connected to this pin, associated with C2N, pin 7. Using low ESR ceramic capacitor is recommended to optimize the Charge Pump efficiency.                                                                                                                                                                                                                                                                                         |

Using ceramic 16 V working voltage capacitors is recommended to compensate the DC bias effect encountered with such type of capacitors.

Any external impedance connected to pin 6 shall be 10 kΩ or higher.

### **增码MUMPSATINGSN**R2G"供应商

| Rating                                                                                                      | Symbol                              | Value                                | Unit       |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------|------------|

| Power Supply Voltage                                                                                        | V <sub>bat</sub>                    | 7.0                                  | V          |

| Power Supply Current                                                                                        | I <sub>bat</sub>                    | 800                                  | mA         |

| Digital Input Pins                                                                                          | V <sub>in</sub>                     | -0.5 V < Vbat < Vbat +0.5 V < 6.0 V  | V          |

| Digital Input Pins                                                                                          | lin                                 | ±5.0                                 | mA         |

| Output Voltage                                                                                              | V <sub>out</sub>                    | 5.5                                  | V          |

| ESD Capability (Note 3) Human Body Model Machine Model                                                      | V <sub>ESD</sub>                    | 2.5<br>200                           | kV<br>V    |

| QFN10, 3x3 Package Power Dissipation @ Tamb = +85°C Thermal Resistance, Junction-to-Air (R <sub>θJA</sub> ) | P <sub>DS</sub><br>R <sub>θJA</sub> | 580<br>68.5                          | mW<br>°C/W |

| Operating Ambient Temperature Range                                                                         | T <sub>A</sub>                      | -40 to +85                           | °C         |

| Operating Junction Temperature Range                                                                        | TJ                                  | -40 to +125                          | °C         |

| Maximum Junction Temperature                                                                                | T <sub>Jmax</sub>                   | +150                                 | °C         |

| Storage Temperature Range                                                                                   | T <sub>stg</sub>                    | -65 to +150                          | °C         |

| Latchup Current Maximum Rating                                                                              |                                     | 100 mA per JEDEC standard, JESD78    |            |

| Moisture Sensitivity Level (MSL)                                                                            |                                     | 1 per IPC/JEDEC standard, J-STD-020A |            |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

- This device series contains ESD protection and exceeds the following tests:

Human Body Model (HBM) ±2.5 kV per JEDEC Standard: JESD22–A114

Machine Model (MM) ±200 V per JEDEC Standard: JESD22–A115.

The maximum package power dissipation limit must not be exceeded.

**ELECTRICAL CHARACTERISTICS:** 2.85 V < Vbat < 5.5 V (-40°C to +85°C ambient temperature, unless otherwise noted).

| Characteristic                                                                                                                                                                                                                                                                                                                              | Pin     | Symbol            | Min              | Тур                  | Max                     | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|------------------|----------------------|-------------------------|------|

| Power Supply                                                                                                                                                                                                                                                                                                                                | 3       | $V_{bat}$         | 2.85             | _                    | 5.5                     | V    |

| Quiescent Current @ V <sub>bat</sub> = 3.7 V, I <sub>out</sub> = 0 μA<br>@ Pulsed Clock Fop = 262 kHz<br>@ Pulsed Clock Fop = 650 kHz<br>@ Continuous Clock Fop = 262 kHz<br>@ Continuous Clock Fop = 650 kHz                                                                                                                               | 3       | Iqsc              | -<br>-<br>-<br>- | -<br>-<br>1.0<br>2.1 | 0.8<br>1.2<br>-<br>-    | mA   |

| Shutdown Current @ $I_{out} = 0$ mA, EN/PWM = L @ $2.85 < V_{bat} < 4.2$ V @ $V_{bat} = 5.5$ V                                                                                                                                                                                                                                              | 3       | I <sub>stdb</sub> |                  | -<br>-               | 2.5<br>4.0              | μA   |

| Output Voltage Regulation  @ Vsel = 1, 2.85 V < V <sub>bat</sub> < 4.5 V  @ Vsel = 0, 2.85 V < V <sub>bat</sub> < 4.5 V                                                                                                                                                                                                                     | 3       | V <sub>out</sub>  | 4.75<br>4.275    | 5.0<br>4.5           | 5.25<br>4.725           | V    |

| Continuous DC Load Current (Note 7)<br>Cin = $1.0 \mu F$ , $C_{FLY} = 1.0 \mu F$ , Cout = $1.0 \mu F$<br>@ Vsel = $1, 3.2 \text{ V} < V_{bat} < 4.5 \text{ V}$<br>@ Vsel = $0, 3.2 \text{ V} < V_{bat} < 5.5 \text{ V}$<br>@ Vsel = $1, 2.85 \text{ V} < V_{bat} < 4.5 \text{ V}$<br>@ Vsel = $1, 2.85 \text{ V} < V_{bat} < 5.5 \text{ V}$ | 3       | I <sub>out</sub>  |                  | -<br>-<br>-          | 160<br>200<br>80<br>120 | mA   |

| Pulsed Output Current<br>Cin = 10 $\mu$ F, C <sub>FLY</sub> = 1.0 $\mu$ F, Cout = 10 $\mu$ F, V <sub>bat</sub> = 3.6 V<br>Pwidth = 500 ms, -40°C < T <sub>A</sub> < +65°C                                                                                                                                                                   | 3       | I <sub>FLH</sub>  | -                | 350                  | -                       | mA   |

| Output Continuous Short Circuit Current, Vout = 0 V                                                                                                                                                                                                                                                                                         | 3       | Isch              | _                | 40                   | 100                     | mA   |

| Operating Frequency (Note 5)  @ Fsel = 0, 2.85 V < V <sub>bat</sub> < 4.5 V  @ Fsel = 1, 2.85 V < V <sub>bat</sub> < 4.5 V                                                                                                                                                                                                                  |         | Fop               | 210<br>500       | 262<br>650           | 320<br>1000             | kHz  |

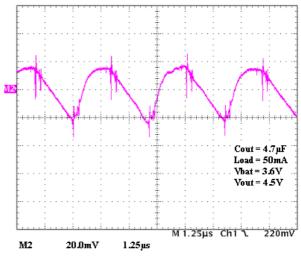

| Output Voltage Ripple (Note 6)  Fop = 262 kHz, $I_{out}$ = 60 mA (Note 7)  @ $C_{out}$ = 1.0 $\mu$ F  @ $C_{out}$ = 4.7 $\mu$ F                                                                                                                                                                                                             | 3       | V <sub>PP</sub>   |                  | 150<br>25            | -<br>60                 | mV   |

| Digital Input High Level                                                                                                                                                                                                                                                                                                                    | 4, 5, 6 | V <sub>IH</sub>   | 1.3              | -                    | -                       | V    |

| Digital Input Low level                                                                                                                                                                                                                                                                                                                     | 4, 5, 6 | $V_{IL}$          | -                | -                    | 0.4                     | V    |

| Output Power Efficiency  @ $V_{bat} = 3.3 \text{ V}$ , $V_{out} = 5.0 \text{ V}$ , $I_{out} = 60 \text{ mA}$ , Fop = 262 kHz  @ $V_{bat} = 3.9 \text{ V}$ , $V_{out} = 5.0 \text{ V}$ , $I_{out} = 160 \text{ mA}$ , Fop = 650 kHz                                                                                                          |         | Рη                | -<br>-           | 75<br>84             | -<br>-                  | %    |

| Thermal Shut Down Protection<br>Hysteresis                                                                                                                                                                                                                                                                                                  |         | T <sub>HSD</sub>  | -<br>-           | 160<br>20            | -<br>-                  | °C   |

<sup>5.</sup> Temperature range guaranteed by design, not production tested.

Smaller footprint associated to lower working voltages (10 V or 6.3 V, size 0805 or 0602) can be used, but care must be observed to prevent DC bias effect on the capacitance final value. See capacitor manufacturer data sheets.

<sup>7.</sup> Ceramic X7R, ESR <  $100~m\Omega$ , SMD type capacitors are mandatory to achieve the  $l_{out}$  specifications. Depending upon the PCB layout, it might be necessary to use two  $2.2~\mu$ F/6.3 V/ceramic capacitors in parallel, yielding an improved  $V_{out}$  noise over the temperature range. On the other hand, care must be observed to take into account the DC bias impact on the capacitance value. See ceramic capacitor manufacturer data sheets.

<sup>8.</sup> Digital inputs undershoot < – 0.30 V to ground, Digital inputs overshoot < 0.30 V to  $V_{bat}$ .

#### 查询"NCP5603MNR2G"供应商

#### TYPICAL CHARACTERISTICS

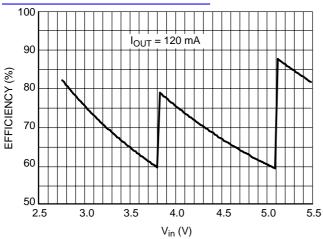

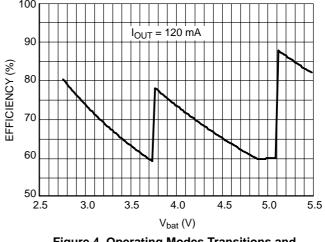

Figure 3. Operating Modes Transitions and Output Power Efficiency @  $V_{out}$  = 4.5 V/262 kHz

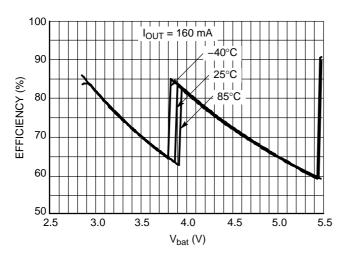

Figure 4. Operating Modes Transitions and Output Power Efficiency @  $V_{out}$  = 4.5 V/650 kHz

Figure 5. Operating Modes Transitions and Output Power Efficiency @  $V_{out}$  = 5.0 V/650 kHz

Figure 6. Typical Output Voltage Ripple

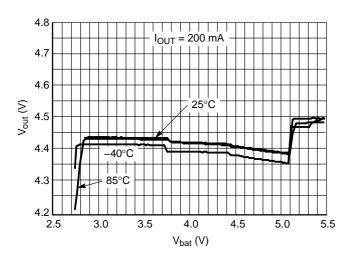

Figure 7. Typical Output Voltage Line Regulation

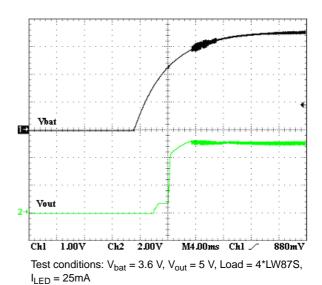

Figure 8. Output Voltage Startup from Scratch

#### **TYPICAL CHARACTERISTICS**

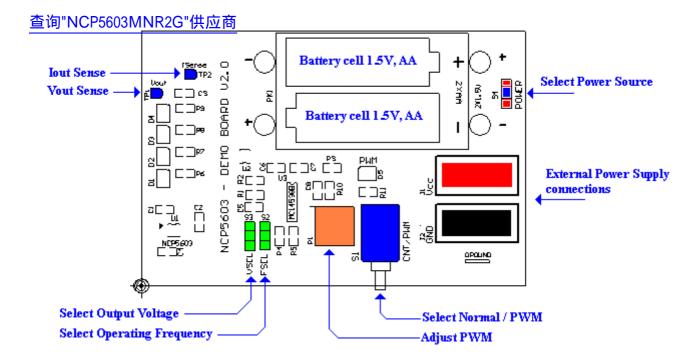

Test conditions:  $V_{bat} = 3.6 \text{ V}, V_{out} = 5 \text{ V}, Load = 4*LW87S}, I_{LED} = 25\text{mA}$

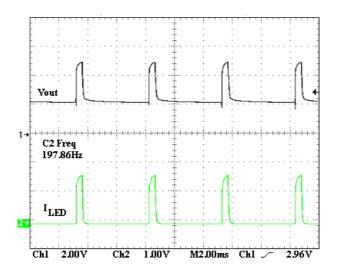

Figure 9. Typical PWM Dimming

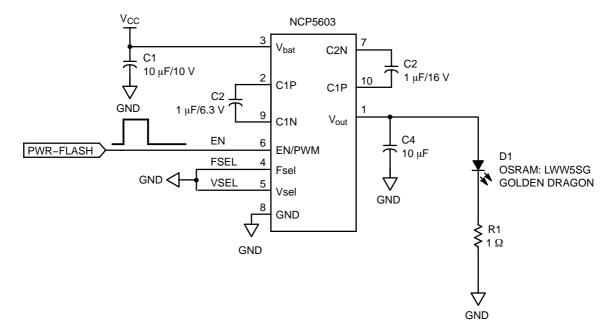

Figure 10. Typical High Power Flash Circuit

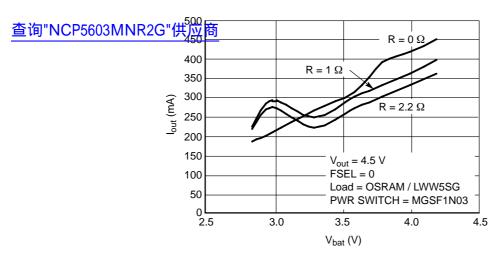

Figure 11. NCP5603 Output Current

**Table 1. Ceramic Preferred Capacitors**

| Manufacturer | Type/Series     | Format | Value         |

|--------------|-----------------|--------|---------------|

| TDK          | C3216X5R1C475MT | 1206   | 4.7 μF / 16 V |

| TDK          | C2012X5R1C225MT | 0805   | 2.2 μF / 16 V |

| TDK          | C2012X5R1C105MT | 0805   | 1.0 μF / 16 V |

Figure 12. Evaluation Board Schematic Diagram

Figure 13. Evaluation Board: Silk View (Top View)

#### 查询"NCP5603MNR2G"供应商

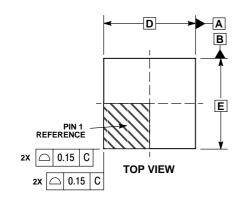

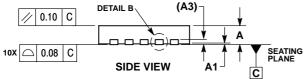

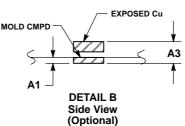

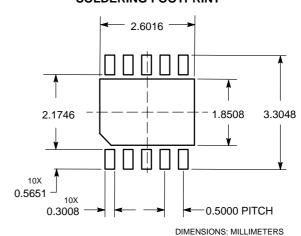

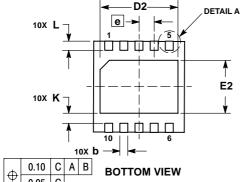

#### PACKAGE DIMENSIONS

### DFN10 **MN SUFFIX**

CASE 485C-01 **ISSUE A**

# (Optional)

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL.

- 0.25 AND 0.30 MM FROM TERMINAL.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

TERMINAL b MAY HAVE MOLD COMPOUND MATERIAL ALONG SIDE EDGE. MOLD FLASHING MAY NOT EXCEED 30 MICRONS ONTO BOTTOM SURFACE OF TERMINAL b.

DETAILS A AND B SHOW OPTIONAL VIEWS FOR END OF TERMINAL LEAD AT EDGE OF PACKAGE

| _   | -           |      |  |

|-----|-------------|------|--|

|     | MILLIMETERS |      |  |

| DIM | MIN         | MAX  |  |

| Α   | 0.80        | 1.00 |  |

| A1  | 0.00        | 0.05 |  |

| A3  | 0.20 REF    |      |  |

| b   | 0.18        | 0.30 |  |

| D   | 3.00 BSC    |      |  |

| D2  | 2.45        | 2.55 |  |

| Е   | 3.00 BSC    |      |  |

| E2  | 1.75        | 1.85 |  |

| е   | 0.50 BSC    |      |  |

| K   | 0.19 TYP    |      |  |

| L   | 0.35        | 0.45 |  |

| L1  | 0.00        | 0.03 |  |

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### 查询"NCP5603MNR2G"供应商

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use a components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082–1312 USA Phone: 480–829–7710 or 800–344–3860 Toll Free USA/Canada Fax: 480–829–7709 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.