# Compandor

The NE570 is a versatile low cost dual gain control circuit in which either channel may be used as a dynamic range compressor or expandor. Each channel has a full–wave rectifier to detect the average value of the signal, a linerarized temperature–compensated variable gain cell, and an operational amplifier.

The NE570 is well suited for use in cellular radio and radio communications systems, modems, telephone, and satellite broadcast/receive audio systems.

#### Features

- Complete Compressor and Expandor in One IC

- Temperature Compensated

- Greater than 110 dB Dynamic Range

- Operates Down to 6.0 V<sub>DC</sub>

- System Levels Adjustable with External Components

- Distortion may be Trimmed Out

- Pb–Free Packages are Available\*

#### Applications

- Cellular Radio

- Telephone Trunk Comandor

- High Level Limiter

- Low Level Expandor Noise Gate

- Dynamic Noise Reduction Systems

- Voltage–Controlled Amplifier

- Dynamic Filters

#### MAXIMUM RATINGS

| Rating                                  | Symbol          | Value    | Unit            |

|-----------------------------------------|-----------------|----------|-----------------|

| Maximum Operating Voltage               | V <sub>CC</sub> | 24       | V <sub>DC</sub> |

| Operating Ambient Temperature Range     | T <sub>A</sub>  | 0 to +70 | °C              |

| Operating Junction Temperature          | TJ              | 150      | °C              |

| Power Dissipation                       | PD              | 400      | mW              |

| Thermal Resistance, Junction-to-Ambient | $R_{\theta JA}$ | 105      | °C/W            |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# **ON Semiconductor®**

http://onsemi.com

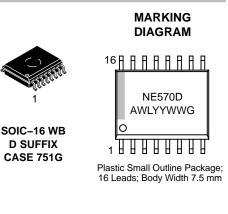

A = Assembly Location WL = Wafer Lot

- YY = Year

- WW = Work Week

### G = Pb–Free Package

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

# 習NFWNCT10NDESCR格TION

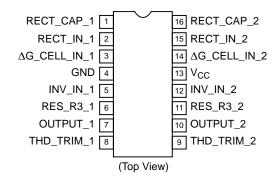

| Pin | Symbol          | Description                               |

|-----|-----------------|-------------------------------------------|

| 1   | RECT CAP 1      | External Capacitor Pinout for Rectifier 1 |

| 2   | RECT IN 1       | Rectifier 1 Input                         |

| 3   | ∆G CELL IN 1    | Variable Gain Cell 1 Input                |

| 4   | GND             | Ground                                    |

| 5   | INV. IN 1       | Inverted Input 1                          |

| 6   | RES. R3 1       | R3 Pinout 1                               |

| 7   | OUTPUT 1        | Output 1                                  |

| 8   | THD TRIM 1      | Total Harmonic Distortion Trim 1          |

| 9   | THD TRIM 2      | Total Harmonic Distortion Trim 2          |

| 10  | OUTPUT 2        | Output 2                                  |

| 11  | RES. R3 2       | R3 Pinout 2                               |

| 12  | INV. IN 2       | Inverted Input 2                          |

| 13  | V <sub>CC</sub> | Positive Power Supply                     |

| 14  | ∆G CELL IN 2    | Variable Gain Cell 2 Input                |

| 15  | RECT IN 2       | Rectifier 2 Input                         |

| 16  | RECT CAP 2      | External Capacitor Pinout for Rectifier 2 |

## **ELECTRICAL CHARACTERISTICS** V<sub>CC</sub> = +15 V, T<sub>A</sub> = 25 °C; unless otherwise stated.

| Characteristic                                                                                           | Test Conditions                                                                                                                                 | Symbol           | Min  | Тур          | Max             | Unit     |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|--------------|-----------------|----------|

| Supply Voltage                                                                                           |                                                                                                                                                 | V <sub>CC</sub>  | 6.0  | -            | 24              | V        |

| Supply Current                                                                                           | No Signal                                                                                                                                       | I <sub>CC</sub>  | _    | 4.3          | 4.8             | mA       |

| Output Current Capability                                                                                |                                                                                                                                                 | I <sub>OUT</sub> | ±20  | -            | -               | mA       |

| Output Slew Rate                                                                                         |                                                                                                                                                 | SR               | _    | ±0.5         | -               | V/μs     |

| Gain Cell Distortion (Note 1)                                                                            | Untrimmed                                                                                                                                       |                  | _    | 0.3          | 1.0             | %        |

|                                                                                                          | Trimmed                                                                                                                                         |                  | _    | 0.05         | _               | %        |

| Resistor Tolerance                                                                                       |                                                                                                                                                 |                  | _    | ±5           | ±15             | %        |

| Internal Reference Voltage                                                                               |                                                                                                                                                 |                  | 1.7  | 1.8          | 1.9             | V        |

| Output DC Shift (Note 2)                                                                                 | Untrimmed                                                                                                                                       |                  | _    | ±90          | ±150            | mV       |

| Expandor Output Noise                                                                                    | No signal, 15 Hz to 20 kHz<br>(Note 3)                                                                                                          |                  | -    | 20           | 45              | μV       |

| Unity Gain Level (Note 4)                                                                                |                                                                                                                                                 |                  | -1.0 | 0            | +1.0            | dBm      |

| Gain Change (Notes 1 and 5)                                                                              | $T_A = 0^{\circ}C$ to +70°C                                                                                                                     |                  | -    | ±0.1         | ±0.2            | dB       |

| Reference Drift (Note 5)                                                                                 | $T_A = 0^{\circ}C$ to +70°C                                                                                                                     |                  | _    | ±5.0         | ±10             | mV       |

| Resistor Drift (Note 5)                                                                                  | $T_A = 0^{\circ}C$ to +70°C                                                                                                                     |                  | -    | +8.0, -5.0   | -               | %        |

| Tracking Error (measured relative to value at unity gain) equals $[V_0 - V_0$ (unity gain)] dB - V_2 dBm | Rectifier Input V <sub>CC</sub> = +6.0 V<br>V <sub>2</sub> = +6.0 dBm, V <sub>1</sub> = 0 dB<br>V <sub>2</sub> = -30 dBm, V <sub>1</sub> = 0 dB |                  |      | ±0.2<br>+0.2 | _<br>_0.5, +1.0 | dB<br>dB |

| Channel Separation                                                                                       |                                                                                                                                                 |                  | -    | 60           | -               | dB       |

1. Measured at 0 dBm, 1.0 kHz. 2. Expandor AC input change from no signal to 0 dBm. 3. Input to V<sub>1</sub> and V<sub>2</sub> grounded. 4. 0 dB = 775 mV<sub>RMS</sub>. 5. Relative to value at  $T_A = 25^{\circ}C$ .

# **CIRCUIT DESCRIPTION**

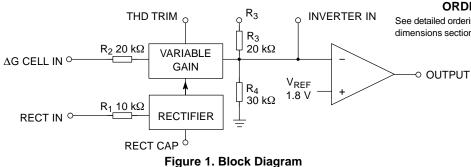

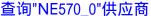

The NES70 compandor building blocks, as shown in the block diagram, are a full-wave rectifier, a variable gain cell, an operational amplifier and a bias system. The arrangement of these blocks in the IC result in a circuit which can perform well with few external components, yet can be adapted to many diverse applications.

The full-wave rectifier rectifies the input current which flows from the rectifier input, to an internal summing node which is biased at VREF. The rectified current is averaged on an external filter capacitor tied to the CRECT terminal, and the average value of the input current controls the gain of the variable gain cell. The gain will thus be proportional to the average value of the input signal for capacitively-coupled voltage inputs as shown in the following equation. Note that for capacitively-coupled inputs there is no offset voltage capable of producing a gain error. The only error will come from the bias current of the rectifier (supplied internally) which is less than  $0.1 \,\mu$ A.

or

$$G \propto \frac{|V_{IN}| avg}{R_1}$$

$G \propto \frac{|V_{IN} - V_{REF}| avg}{R_1}$

The speed with which gain changes to follow changes in input signal levels is determined by the rectifier filter capacitor. A small capacitor will yield rapid response but will not fully filter low frequency signals. Any ripple on the gain control signal will modulate the signal passing through the variable gain cell. In an expander or compressor application, this would lead to third harmonic distortion, so there is a trade-off to be made between fast attack and decay times and distortion. For step changes in amplitude, the change in gain with time is shown by this equation.

$$\begin{split} G(t) &= (G_{initial} - G_{final}) e^{\frac{-\tau}{\tau}} + G_{final} \\ \tau &= 10 k\Omega \times C_{RECT} \end{split}$$

The variable gain cell is a current-in, current-out device with the ratio  $I_{OUT}/I_{IN}$  controlled by the rectifier.  $I_{IN}$  is the current which flows from the  $\Delta G$  input to an internal summing node biased at VREF. The following equation applies for capacitively-coupled inputs. The output current, I<sub>OUT</sub>, is fed to the summing node of the op amp.

$$I_{IN} = \frac{V_{IN} - V_{REF}}{R_2} = \frac{V_{IN}}{R_2}$$

A compensation scheme built into the  $\Delta G$  cell compensates for temperature and cancels out odd harmonic

distortion. The only distortion which remains is even harmonics, and they exist only because of internal offset voltages. The THD trim terminal provides a means for nulling the internal offsets for low distortion operation.

The operational amplifier (which is internally compensated) has the non-inverting input tied to V<sub>REF</sub>, and the inverting input connected to the  $\Delta G$  cell output as well as brought out externally. A resistor, R<sub>3</sub>, is brought out from the summing node and allows compressor or expander gain to be determined only by internal components.

The output stage is capable of  $\pm 20$  mA output current. This allows a +13 dBm (3.5 V<sub>RMS</sub>) output into a 300  $\Omega$  load which, with a series resistor and proper transformer, can result in +13 dBm with a 600  $\Omega$  output impedance.

A bandgap reference provides the reference voltage for all summing nodes, a regulated supply voltage for the rectifier and  $\Delta G$  cell, and a bias current for the  $\Delta G$  cell. The low tempco of this type of reference provides very stable biasing over a wide temperature range.

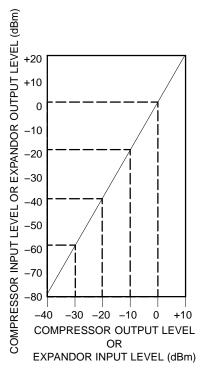

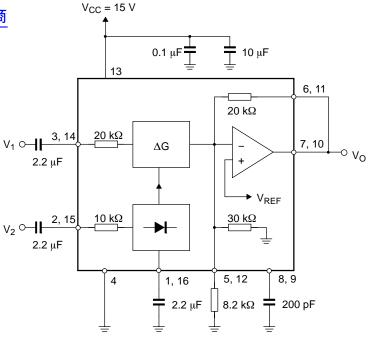

The typical performance characteristics illustration shows the basic input-output transfer curve for basic compressor or expander circuits.

Figure 2. Basic Input–Output Transfer Curve

**NE570**

Figure 3. Typical Test Circuit

#### INTRODUCTION

Much interest has been expressed in high performance electronic gain control circuits. For non–critical applications, an integrated circuit operational transconductance amplifier can be used, but when high–performance is required, one has to resort to complex discrete circuitry with many expensive, well–matched components. This paper describes an inexpensive integrated circuit, the NE570 Compandor, which offers a pair of high performance gain control circuits featuring low distortion (<0.1 %), high signal–to–noise ratio (90 dB), and wide dynamic range (110 dB).

#### **CIRCUIT BACKGROUND**

The NE570 Compandor was originally designed to satisfy the requirements of the telephone system. When several telephone channels are multiplexed onto a common line, the resulting signal-to-noise ratio is poor and companding is used to allow a wider dynamic range to be passed through the channel. Figure 4 graphically shows what a compandor can do for the signal-to-noise ratio of a restricted dynamic range channel. The input level range of +20 dB to -80 dB is shown undergoing a 2-to-1 compression where a 2.0 dB input level change is compressed into a 1.0 dB output level change by the compressor. The original 100 dB of dynamic range is thus compressed to a 50 dB range for transmission through a restricted dynamic range channel. A complementary expansion on the receiving end restores the original signal levels and reduces the channel noise by as much as 45 dB. The significant circuits in a compressor or expander are the rectifier and the gain control element. The phone system requires a simple full–wave averaging rectifier with good accuracy, since the rectifier accuracy determines the (input) output level tracking accuracy. The gain cell determines the distortion and noise characteristics, and the phone system specifications here are very loose. These specs could have been met with a simple operational transconductance multiplier, or OTA, but the gain of an OTA is proportional to temperature and this is very undesirable. Therefore, a linearized transconductance multiplier was designed which is insensitive to temperature and offers low noise and low distortion performance. These features make the circuit useful in audio and data systems as well as in telecommunications systems.

Figure 4. Restricted Dynamic Range Channel

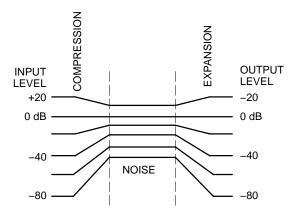

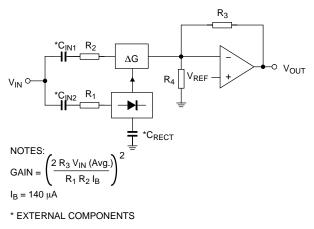

## BASIC CIRCUIT HOOK-UP AND OPERATION Figure 5 shows the block diagram of one half of the chip,

Figure 5 shows the Block diagram of one half of the chip, (there are two identical channels on the IC). The full–wave averaging rectifier provides a gain control current,  $I_G$ , for the variable gain ( $\Delta G$ ) cell. The output of the  $\Delta G$  cell is a current which is fed to the summing node of the operational amplifier. Resistors are provided to establish circuit gain and set the output DC bias.

Figure 5. Chip Block Diagram (1 of 2 Channels)

The circuit is intended for use in single power supply systems, so the internal summing nodes must be biased at some voltage above ground. An internal band gap voltage reference provides a very stable, low noise 1.8 V reference denoted  $V_{REF}$ . The non-inverting input of the op amp is tied to  $V_{REF}$ , and the summing nodes of the rectifier and  $\Delta G$  cell (located at the right of  $R_1$  and  $R_2$ ) have the same potential. The THD\_TRIM pin is also at the  $V_{REF}$  potential.

Figure 6 shows how the circuit is hooked up to realize an expander. The input signal,  $V_{IN}$ , is applied to the inputs of both the rectifier and the  $\Delta G$  cell. When the input signal drops by 6.0 dB, the gain control current will drop by a factor of 2, and so the gain will drop 6 dB. The output level at  $V_{OUT}$  will thus drop 12 dB, giving us the desired 2-to-1 expansion.

Figure 6. Basic Expander

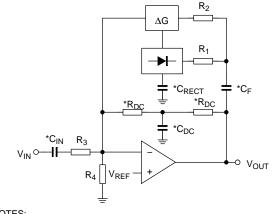

Figure 7 shows the hook–up for a compressor. This is essentially an expander placed in the feedback loop of the op amp. The  $\Delta G$  cell is set–up to provide AC feedback only, so a separate DC feedback loop is provided by the two R<sub>DC</sub> and C<sub>DC</sub>. The values of R<sub>DC</sub> will determine the DC bias at the output of the op amp. The output will bias to:

$$V_{OUT} DC = \left(1 + \frac{R_{DC1} + R_{DC2}}{R_4}\right) V_{REF}$$

$$V_{OUT} DC = \left(1 + \frac{R_{DC TOT}}{30 \text{ k}\Omega}\right) 1.8 \text{ V}$$

The output of the expander will bias up to:

$$V_{OUT} DC = \left(1 + \frac{R_3}{R_4}\right) V_{REF}$$

$$V_{OUT} DC = \left(1 + \frac{20 \text{ k}\Omega}{30 \text{ k}\Omega}\right) 1.8 \text{ V} = 3.0 \text{ V}$$

The output will bias to 3.0 V when the internal resistors are used. External resistors may be placed in series with R3, (which will affect the gain), or in parallel with R4 to raise the DC bias to any desired value.

NOTES:

$$GAIN = \left(\frac{R_1 R_2 I_B}{2 R_3 V_{IN}(avg.)}\right)^{\frac{1}{2}}$$

I<sub>B</sub> = 140 μA \* EXTERNAL COMPONENTS

#### Figure 7. Basic Compressor

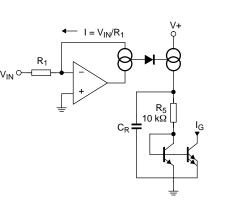

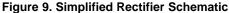

CIRCUIT DETAILS-RECTIFIER Figure 8 shows the concept behind the full-wave averaging rectifier. The input current to the summing node of the op amp,  $V_{IN}/R_1$ , is supplied by the output of the op amp. If we can mirror the op amp output current into a unipolar current, we will have an ideal rectifier. The output current is averaged by R<sub>5</sub>, C<sub>R</sub>, which set the averaging time constant, and then mirrored with a gain of 2 to become IG, the gain control current.

Figure 9 shows the rectifier circuit in more detail. The op amp is a one-stage op amp, biased so that only one output device is on at a time. The non-inverting input, (the base of  $Q_1$ ), which is shown grounded, is actually tied to the internal  $1.8 \text{ V} \text{ V}_{\text{REF}}$ . The inverting input is tied to the op amp output, (the emitters of Q<sub>5</sub> and Q<sub>6</sub>), and the input summing resistor R1. The single diode between the bases of  $Q_5$  and  $Q_6$  assures that only one device is on at a time. To detect the output current of the op amp, we simply use the collector currents of the output devices  $Q_5$  and  $Q_6$ .  $Q_6$  will conduct when the input swings positive and Q5 conducts when the input swings negative. The collector currents will be in error by the  $\alpha$  of Q<sub>5</sub> or Q<sub>6</sub> on negative or positive signal swings,

respectively. ICs such as this have typical NPN  $\beta$ 's of 200 and PNP  $\beta$ 's of 40. The  $\alpha$ 's of 0.995 and 0.975 will produce errors of 0.5% on negative swings and 2.5% on positive swings. The 1.5% average of these errors yields a mere 0.13 dB gain error.

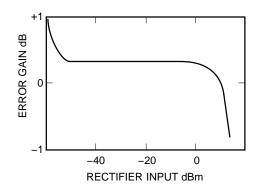

At very low input signal levels the bias current of  $Q_2$ , (typically 50 nA), will become significant as it must be supplied by Q5. Another low level error can be caused by DC coupling into the rectifier. If an offset voltage exists between the V<sub>IN</sub> input pin and the base of Q<sub>2</sub>, an error current of V<sub>OS</sub>/R<sub>1</sub> will be generated. A mere 1.0 mV of offset will cause an input current of 100 nA, which will produce twice the error of the input bias current. For highest accuracy, the rectifier should be coupled capacitively. At high input levels the  $\beta$  of the PNP Q<sub>6</sub> will begin to suffer, and there will be an increasing error until the circuit saturates. Saturation can be avoided by limiting the current into the rectifier input to 250 µA. If necessary, an external resistor may be placed in series with R1 to limit the current to this value. Figure 10 shows the rectifier accuracy versus input level at a frequency of 1.0 kHz.

**Figure 8. Rectifier Concept**

Figure 10. Rectifier Accuracy

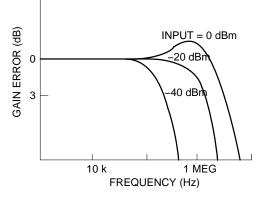

At very high frequencies, the response of the rectifier will fall off. The roll-off will be more pronounced at lower input levels due to the increasing amount of gain required to switch between  $Q_5$  or  $Q_6$  conducting. The rectifier frequency response for input levels of 0 dBm, -20 dBm, and -40 dBm is shown in Figure 11. The response at all three levels is flat to well above the audio range.

Figure 11. Rectifier Frequency Response vs. Input Level

#### VARIABLE GAIN CELL

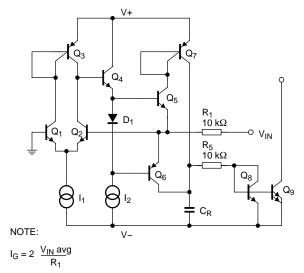

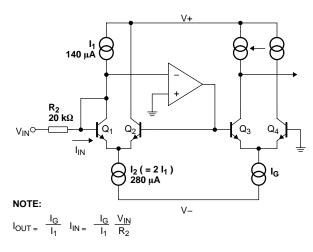

Figure 12 is a diagram of the variable gain cell. This is a linearized two–quadrant transconductance multiplier.  $Q_1$ ,  $Q_2$  and the op amp provide a predistorted drive signal for the gain control pair,  $Q_3$  and  $Q_4$ . The gain is controlled by  $I_G$  and a current mirror provides the output current.

Figure 12. Simplified  $\Delta G$  Cell Schematic

The op amp maintains the base and collector of  $Q_1$  at ground potential (V<sub>REF</sub>) by controlling the base of  $Q_2$ . The input current  $I_{IN}$  (=  $V_{IN}/R_2$ ) is thus forced to flow through  $Q_1$  along with the current  $I_1$ , so  $I_{C1} = I_1 + I_{IN}$ . Since  $I_2$  has been set at twice the value of  $I_1$ , the current through  $Q_2$  is:

$$2 - (I_1 + I_{IN}) = I_1 - I_{IN} = I_{C2}$$

The op amp has thus forced a linear current swing between  $Q_1$  and  $Q_2$  by providing the proper drive to the base of  $Q_2$ . This drive signal will be linear for small signals, but very non-linear for large signals, since it is compensating for the non-linearity of the differential pair,  $Q_1$  and  $Q_2$ , under large signal conditions.

The key to the circuit is that this same predistorted drive signal is applied to the gain control pair,  $Q_3$  and  $Q_4$ . When two differential pairs of transistors have the same signal applied, their collector current ratios will be identical regardless of the magnitude of the currents. This gives us:

$$\frac{I_{C1}}{I_{C2}} = \frac{I_{C4}}{I_{C3}} = \frac{I_1 + I_{IN}}{I_1 - I_{IN}}$$

plus the relationships  $I_G = I_{C3} + I_{C4}$  and  $I_{OUT} = I_{C4} - I_{C3}$  will yield the multiplier transfer function,

$$I_{OUT} = \frac{I_G}{I_1} I_{IN} = \frac{V_{IN}I_G}{R_2I_1}$$

This equation is linear and temperature–insensitive, but it assumes ideal transistors.

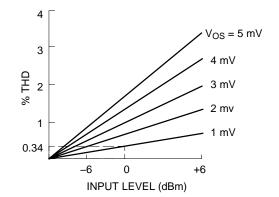

Figure 13.  $\Delta$ G Cell Distortion vs. Offset Voltage

If the transistors are not perfectly matched, a parabolic, non–linearity is generated, which results in second harmonic distortion. Figure 13 gives an indication of the magnitude of the distortion caused by a given input level and offset voltage. The distortion is linearly proportional to the magnitude of the offset and the input level. Saturation of the gain cell occurs at a +8.0 dBm level. At a nominal operating level of 0 dBm, a 1.0 mV offset will yield 0.34% of second harmonic distortion. Most circuits are somewhat better than

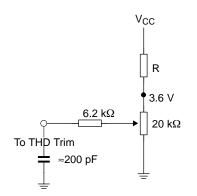

this, which means our overall offsets are typically about mV. The distortion is not affected by the magnitude of the gain control current, and it does not increase as the gain is changed. This second harmonic distortion could be eliminated by making perfect transistors, but since that would be difficult, we have had to resort to other methods. A trim pin has been provided to allow trimming of the internal offsets to zero, which effectively eliminated second harmonic distortion. Figure 14 shows the simple trim network required.

Figure 14. THD Trim Network

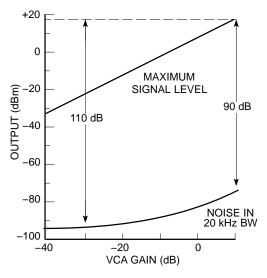

Figure 15 shows the noise performance of the  $\Delta G$  cell. The maximum output level before clipping occurs in the gain cell is plotted along with the output noise in a 20 kHz bandwidth. Note that the noise drops as the gain is reduced for the first 20 dB of gain reduction. At high gains, the signal to noise ratio is 90 dB, and the total dynamic range from maximum signal to minimum noise is 110 dB.

Figure 15. Dynamic Range

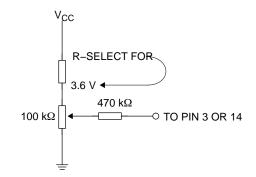

Control signal feedthrough is generated in the gain cell by imperfect device matching and mismatches in the current sources,  $I_1$  and  $I_2$ . When no input signal is present, changing  $I_G$  will cause a small output signal. The distortion trim is effective in nulling out any control signal feedthrough, but in general, the null for minimum feedthrough will be different than the null in distortion. The control signal feedthrough can be trimmed independently of distortion by tying a current source to the  $\Delta G$  input pin. This effectively trims  $I_1$ . Figure 16 shows such a trim network.

Figure 16. Control Signal Feedthrough

#### OPERATIONAL AMPLIFIER

The main op amp shown in the chip block diagram is equivalent to a 741 with a 1.0 MHz bandwidth. Figure 17 shows the basic circuit. Split collectors are used in the input pair to reduce  $g_M$ , so that a small compensation capacitor of just 10 pF may be used. The output stage, although capable of output currents in excess of 20 mA, is biased for a low quiescent current to conserve power. When driving heavy loads, this leads to a small amount of crossover distortion.

Figure 17. Operational Amplifier

# ORDERING INFORMATION

| Device    | Package<br>Plastic Small Outline Package;<br>16 Leads; Body Width 7.5 mm | Temperature Range | Shipping <sup>†</sup> |

|-----------|--------------------------------------------------------------------------|-------------------|-----------------------|

| NE570D    | SOIC-16 WB                                                               | 0°C to +70°C      | 47 Units / Rail       |

| NE570DG   | SOIC-16 WB<br>(Pb-Free)                                                  | 0°C to +70°C      | 47 Units / Rail       |

| NE570DR2  | SOIC-16 WB                                                               | 0°C to +70°C      | 1000 Tape & Reel      |

| NE570DR2G | SOIC-16 WB<br>(Pb-Free)                                                  | 0°C to +70°C      | 1000 Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# 查询"NE570\_0"供应商

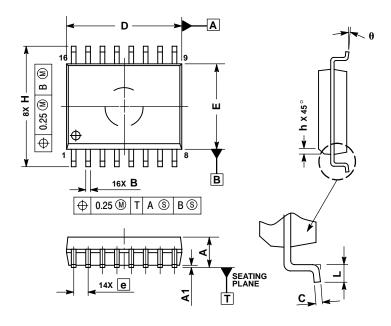

SOIC-16 WB CASE 751G-03 ISSUE C

NOTES:

- DIMENSIONS ARE IN MILLIMETERS. INTERPRET DIMENSIONS AND TOLERANCES 1. 2.

- PER ASME Y14.5M, 1994. DIMENSIONS D AND E DO NOT INLCUDE

- 3

- MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE. 4 MAANIMUM MUCLID FRO TROUGHOND TEA SID DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM 5. MATERIAL CONDITION.

|     | MILLIMETERS |       |  |

|-----|-------------|-------|--|

| DIM | MIN         | MAX   |  |

| Α   | 2.35        | 2.65  |  |

| A1  | 0.10        | 0.25  |  |

| В   | 0.35        | 0.49  |  |

| С   | 0.23        | 0.32  |  |

| D   | 10.15       | 10.45 |  |

| Е   | 7.40        | 7.60  |  |

| е   | 1.27 BSC    |       |  |

| н   | 10.05       | 10.55 |  |

| h   | 0.25        | 0.75  |  |

| L   | 0.50        | 0.90  |  |

| q   | 0 °         | 7 °   |  |

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

ON Semiconductor Website: www.onsemi.com Order Literature: http://www.onsemi.com/orderlit

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

For additional information, please contact your local Sales Representative

NE570/D