# 23.9 R2"供应商

# **Low-Standby High Performance PWM Controller**

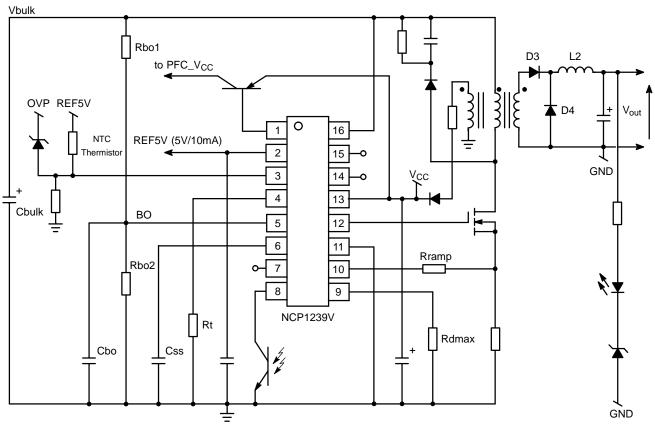

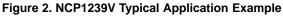

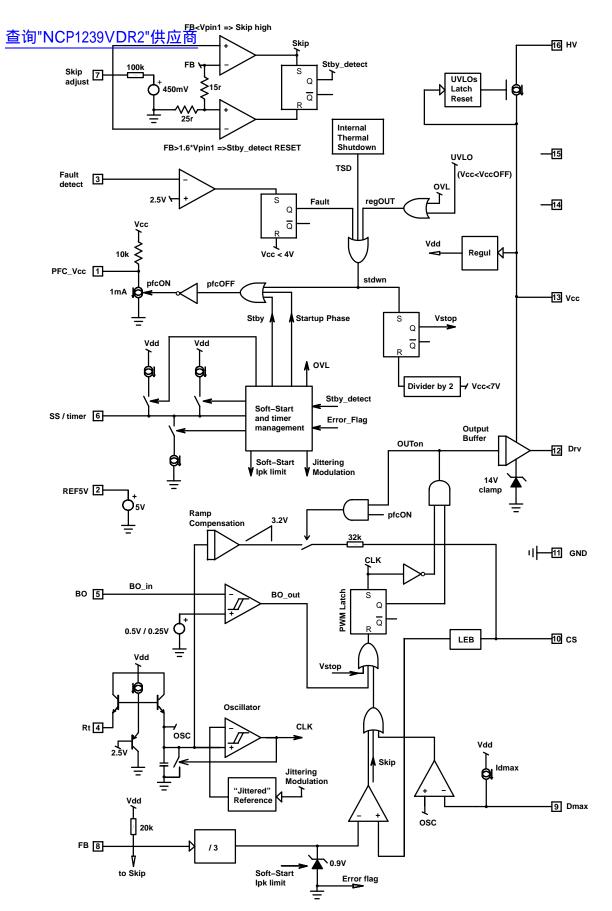

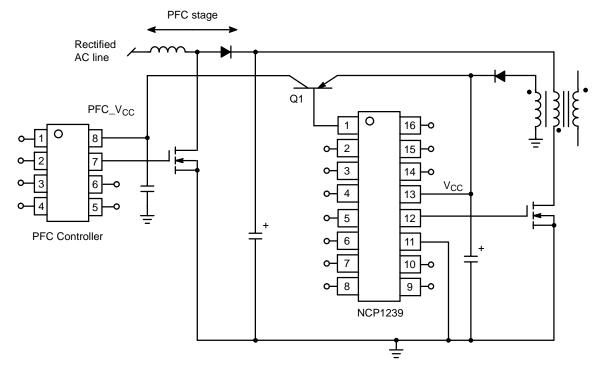

Housed in SO-16 the NCP1239 represents a major leap toward ultra-compact Switch Mode Power Supplies specifically tailored for medium to high power off-line applications, e.g. notebook adapters. The NCP1239 offers everything needed to build a rugged and efficient power supply, including a dedicated event management to drive a Power Factor Correction (PFC) front-end circuitry. The circuit disables the front-end PFC stage while still in fault or standby conditions by interrupting the PFC controller powering for improved no-load consumption figures. As soon as normal operating mode recovers, the NCP1239 feeds back the PFC that wakes-up.

When power demand is low, the IC automatically enters the so-called skip-cycle mode and provides excellent efficiency at light loads. Because this occurs at a user adjustable low peak current, no acoustic noise takes place.

#### Features

- Current–Mode Operation with Internal Ramp Compensation

- Internal High–Voltage Current Source for loss–less Startup

- Adjustable Skip–Cycle Capability

- Selectable Soft-Start Period

- Internal Frequency Dithering for Improved EMI Signature

- Go-to-Standby Signal for PFC Front-Stage

- Large V<sub>CC</sub> Operation from 12.2 V to 36 V

- 500 mV Overcurrent Limit

- 500 mA/-800 mA Peak Current Capability

- 5 V/10 mA Pinned-out Reference Voltage

- Adjustable Switching Frequency up to 250 kHz.

- Overload Protection Independent of the Auxiliary V<sub>CC</sub>

- Adjustable Over Power Compensation (NCP1239F)

- Programmable Maximum Duty Cycle (NCP1239V)

- Pb-Free Packages are Available\*

#### **Typical Applications**

- High Power AC/DC Adapters for Notebooks etc.

- Offline Battery Chargers

- Telecom and PC Power Supplies

- Flyback Applications (NCP1239F) and Forward Applications (NCP1239V)

#### MARKING DIAGRAM

Ν

| NCP1239xD | = Device Code       |

|-----------|---------------------|

| х         | = F or V            |

| А         | = Assembly Location |

| WL        | = Wafer Lot         |

| Y         | = Year              |

| WW        | = Work Week         |

| G         | = Pb-Free Package   |

#### = Pb-Free Package

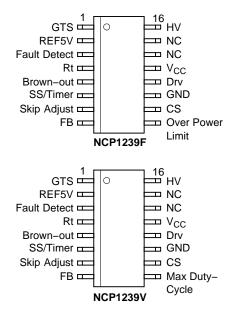

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

See detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.

# MAXIMUM BATINGSDR2"供应商

| Ra                                             | Rating                                                                     |                 |            |    |

|------------------------------------------------|----------------------------------------------------------------------------|-----------------|------------|----|

| Power Supply Voltage                           |                                                                            | V <sub>CC</sub> | 36         | V  |

| Pins 1 to 10 (except Vref Pin) Maximum Voltage |                                                                            |                 | -0.3, +10  | V  |

| Maximum Voltage on Pin 16 (HV)                 |                                                                            | 500             | V          |    |

| Thermal Resistance, Junction-to-Air, SOI       | $R_{	hetaJA}$                                                              | 145             | °C/W       |    |

| Maximum Junction Temperature                   | TJ <sub>MAX</sub>                                                          | 150             | °C         |    |

| Storage Temperature Range                      |                                                                            | -60 to +150     | °C         |    |

| ESD Capability, HBM Model (All Pins exce       | pt HV)                                                                     |                 | 2          | kV |

| ESD Capability                                 | Machine Model (All Pins except $V_{CC}$ )<br>Machine Model ( $V_{CC}$ Pin) |                 | 200<br>160 | V  |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

# **ELECTRICAL CHARACTERISTICS** (For typical values $T_J = 25^{\circ}C$ , for min/max values $T_J = 0^{\circ}C$ to +125°C, $V_{pin16} = 48$ V, $V_{CC} = 20$ V unless otherwise noted.)

| Symbol               | Rating                                                                                               | Pin | Min  | Тур        | Мах        | Uni |

|----------------------|------------------------------------------------------------------------------------------------------|-----|------|------------|------------|-----|

| upply Sectio         | n                                                                                                    |     |      |            | •          | -   |

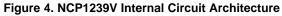

| V <sub>CCON</sub>    | Turn-on Threshold Level, V <sub>CC</sub> Going up                                                    | 13  | 15.5 | 16.4       | 17.5       | V   |

| V <sub>CCOFF</sub>   | Minimum Operating Voltage after Turn-on                                                              | 13  | 10.5 | 11.2       | 12.2       | V   |

| HYST1                | Difference (V <sub>CCON</sub> – V <sub>CCOFF</sub> )                                                 | 13  | 4.5  | 5.1        | -          | V   |

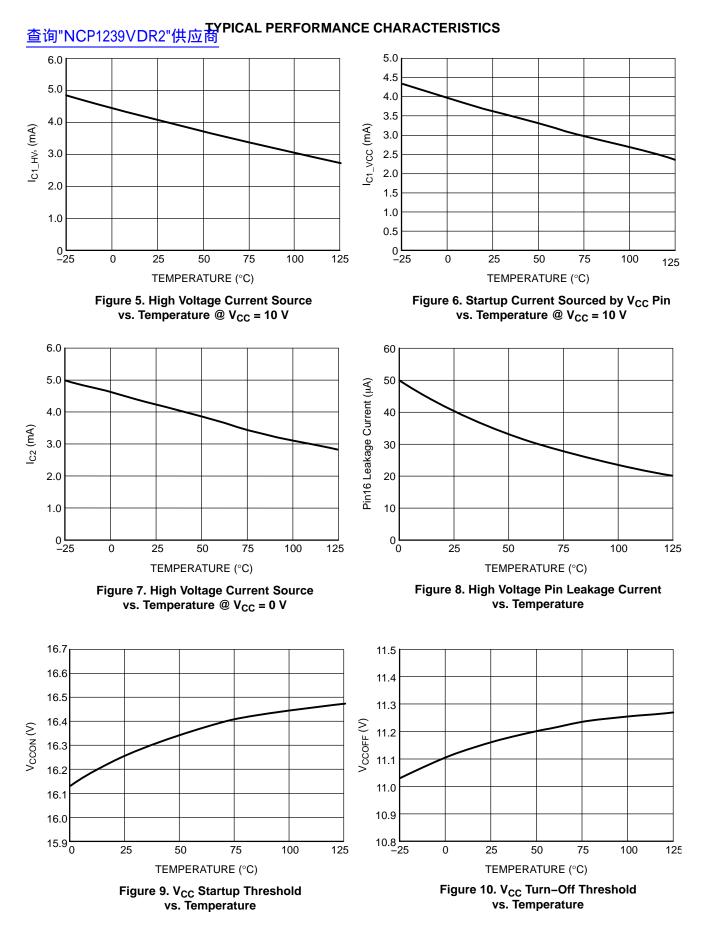

| V <sub>CCLATCH</sub> | V <sub>CC</sub> Decreasing Level at which the Latch–off Phase ends                                   | 13  | 6.5  | 6.9        | 7.2        | V   |

| V <sub>CCRESET</sub> | V <sub>CC</sub> Level at which the Internal Logic gets reset                                         | 13  | -    | 4.0        | -          | V   |

| I <sub>CC1</sub>     | Internal IC Consumption, no output load on Pin 12 (@I <sub>Rt</sub> = 20 μA)<br>NCP1239F<br>NCP1239V | 13  |      | 2.1<br>2.6 | 3.0<br>4.0 | mA  |

| I <sub>CC2a</sub>    | Internal IC Consumption, 1 nF output load on Pin 12<br>NCP1239F (65 kHz)<br>NCP1239V (118 kHz)       | 13  |      | 3.1<br>4.2 | 3.8<br>6.5 | mA  |

| I <sub>CC2b</sub>    | Internal IC Consumption, 1 nF output load on Pin 12<br>NCP1239F (100 kHz)<br>NCP1239V (182 kHz)      |     |      | 3.9<br>5.5 | 5.0<br>8.5 | mA  |

| I <sub>CC2c</sub>    | Internal IC Consumption, 1 nF output load on Pin 12<br>NCP1239F (130 kHz)<br>NCP1239V (236 kHz)      |     |      | 4.6<br>6.7 | 5.9<br>9.6 | mA  |

| I <sub>CC3</sub>     | Internal IC Consumption, latchoff phase<br>(NCP1239F and NCP1239V)                                   | 13  | -    | 0.40       | 0.75       | mA  |

| ternal Startu        | ip Current Source                                                                                    |     | •    | •          |            |     |

| I <sub>C1_hv</sub>   | hv High–Voltage Current Source (sunk by Pin 16), V <sub>CC</sub> = 10 V                              |     | 2.0  | 4.0        | 5.3        | mA  |

| I <sub>C1_VCC</sub>  | Startup Charge Current flowing out of the V <sub>CC</sub> Pin, V <sub>CC</sub> =10 V                 | 13  | 1.8  | 3.6        | 4.5        | mA  |

| I <sub>C2</sub>      | High–Voltage Current Source, V <sub>CC</sub> = 0                                                     | 16  | _    | 4.2        | -          | mA  |

| • • • • • • • • • • • • • • • • • • • • |                                                                       |   |            |            |            |    |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------------|---|------------|------------|------------|----|--|--|--|

| REF5V                                   | Reference Voltage<br>@ No load on Pin 2<br>@ I <sub>pin2</sub> = 5 mA | 2 | 4.7<br>4.6 | 5.0<br>4.9 | 5.2<br>5.1 | V  |  |  |  |

| Iref                                    | Current Capability                                                    | 2 | 5.0        | 10         | 1          | mA |  |  |  |

# **EXAMPLE 1** (For typical values $T_J = 25^{\circ}$ C, for min/max values $T_J = 0^{\circ}$ C to +125°C, $V_{pin16} = 48$ V, $V_{CC} = 20$ V unless otherwise noted.)

| Symbol                                                                                                                         | Symbol Rating                                                                                                                               |       | Min           | Тур           | Max           | Unit   |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|---------------|---------------|--------|--|

| Drive Output                                                                                                                   |                                                                                                                                             |       |               |               |               |        |  |

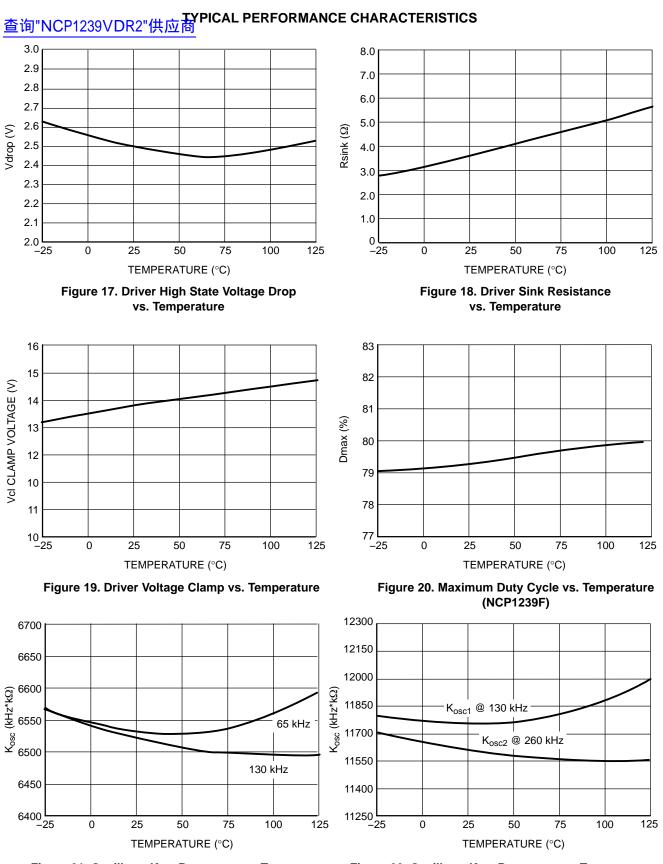

| Vcl                                                                                                                            | Output Voltage Positive Clamp                                                                                                               | 12    | 11.5          | 13.6          | 16            | V      |  |

| T <sub>rise</sub>                                                                                                              | Output Voltage Rise-Time @ CL = 1 nF, 10-90% of output signal                                                                               | 12    | -             | 40            | _             | ns     |  |

| T <sub>fall</sub>                                                                                                              | Output Voltage Fall-Time @ CL = 1 nF, 10-90% of output signal                                                                               | 12    | -             | 25            | _             | ns     |  |

| V <sub>source</sub>                                                                                                            | High State Voltage Drop @ $I_{pin12}$ = 3 mA and V <sub>CC</sub> = 12 V                                                                     | 12    | -             | 2.5           | 3.3           | V      |  |

| I <sub>source</sub>                                                                                                            | Source Current Capability (@ V <sub>pin12</sub> = 0 V)                                                                                      | 12    | -             | 500           | -             | mA     |  |

| R <sub>OL</sub>                                                                                                                | Sink Resistance @ V <sub>pin12</sub> =1 V                                                                                                   | 12    | -             | 3.8           | 7.5           | Ω      |  |

| I <sub>sink</sub>                                                                                                              | I <sub>sink</sub> Sink Current Capability (@ V <sub>pin12</sub> = 10 V)                                                                     |       |               |               | -             | mA     |  |

| Oscillator                                                                                                                     | ·                                                                                                                                           |       |               |               |               |        |  |

| fsw                                                                                                                            | Recommended Switching Frequency Range                                                                                                       | 12    | 25            | -             | 250           | kHz    |  |

| Vosc                                                                                                                           | Vosc Pin 4 Voltage @ Rt = 100 k $\Omega$                                                                                                    |       | -             | 1.6           | -             | V      |  |

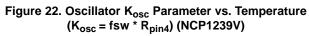

| Kosc                                                                                                                           | Product (Switching Frequency times the Rt Pin 4 resistance) (Note 1)<br>@ 65 kHz and 130 kHz (NCP1239F)<br>@ 118 kHz and 236 kHz (NCP1239V) |       | 6050<br>11000 | 6500<br>11800 | 6950<br>12600 | kHz*kΩ |  |

| $\Delta fsw$                                                                                                                   | Internal Modulation Swing, in percentage of fsw                                                                                             |       | -             | ±3.5          | -             | %      |  |

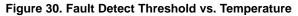

| Dmax                                                                                                                           | Maximum Duty-Cycle                                                                                                                          |       | 75.5          | 80.0          | 83.0          | %      |  |

| Current Limita                                                                                                                 | tion                                                                                                                                        |       | •             | •             |               |        |  |

| I <sub>Limit</sub>                                                                                                             | Maximum Internal Set-Point                                                                                                                  | 10    | 0.84          | 0.90          | 0.95          | V      |  |

| T <sub>DEL_CS</sub>                                                                                                            | Propagation Delay from V <sub>pin10</sub> > I <sub>Limit</sub> to gate turned off<br>(Pin 12 loaded by 1 nF)                                |       | -             | 130           | 220           | ns     |  |

| T <sub>LEB-65kHz</sub>                                                                                                         | EB-65kHz Leading Edge Blanking Duration (Pins 9 and 10) @ 65 kHz (NCP1239F)                                                                 |       | _             | 420           | _             | ns     |  |

| T <sub>LEB-130kHz</sub>                                                                                                        | Leading Edge Blanking Duration (Pins 9 and 10) @ 130 kHz (NCP1239F)                                                                         | 9, 10 | _             | 230           | _             | ns     |  |

| T <sub>LEB-118kHz</sub>                                                                                                        | Leading Edge Blanking Duration (Pin 10) @ 118 kHz (NCP1239V)                                                                                | 10    | -             | 320           | _             | ns     |  |

| T <sub>LEB-236kHz</sub>                                                                                                        | Leading Edge Blanking Duration (Pin 10) @ 236 kHz (NCP1239V)                                                                                | 10    | _             | 170           | _             | ns     |  |

| Over Power Li                                                                                                                  | mit (NCP1239F)                                                                                                                              |       | U             | 1             | 1             |        |  |

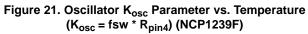

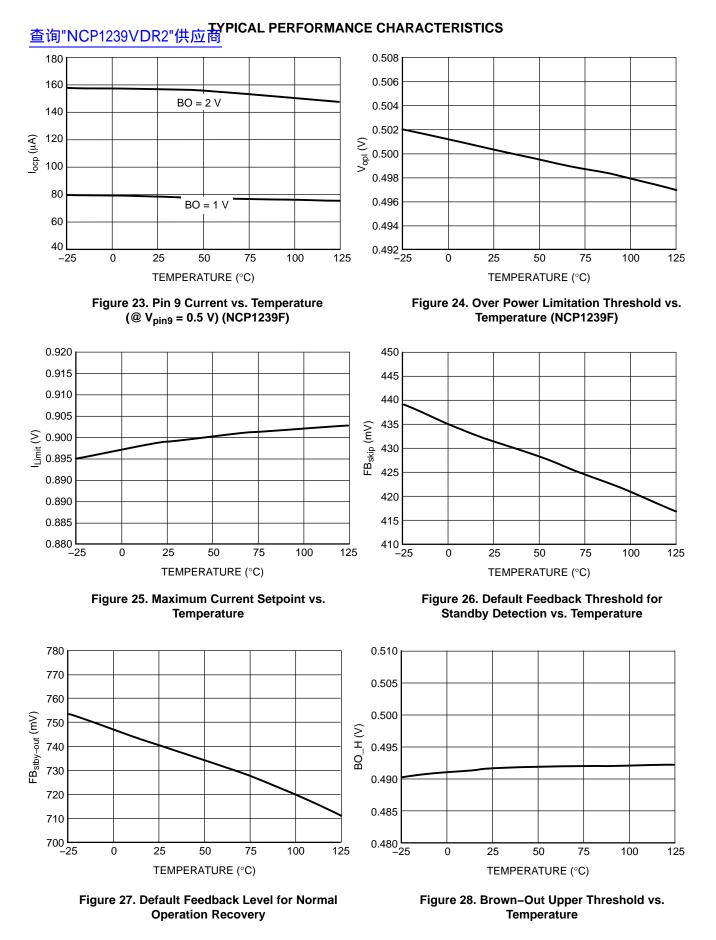

| l <sub>ocp</sub>                                                                                                               | Internal Current Source of the Over Power Limit Pin<br>@ 1 V on Pin 5 and $V_{pin9} = 0.5 V$<br>@ 2 V on Pin 5 and $V_{pin9} = 0.5 V$       | 9     | 60<br>120     | 80<br>160     | 100<br>185    | μΑ     |  |

| V <sub>opl</sub>                                                                                                               | · · · · · · · · · · · · · · · · · · ·                                                                                                       |       | 0.48<br>0.47  | 0.50<br>0.50  | 0.52<br>0.52  | V      |  |

| T <sub>DEL_OCP</sub> Propagation Delay from V <sub>pin9</sub> > V <sub>opl</sub> to gate turned off<br>(Pin 12 loaded by 1 nF) |                                                                                                                                             | 9     | -             | 130           | 220           | ns     |  |

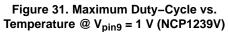

| Maximum Duty                                                                                                                   | y–Cycle (Dmax) Control (NCP1239V)                                                                                                           | -     | -             | -             | -             | -      |  |

| I <sub>Dmax</sub>                                                                                                              | Pin 9 Current Source @ V <sub>pin9</sub> = 1.0 V and V <sub>pin9</sub> = 2.0 V                                                              | 9     | 46            | 55            | 63            | μΑ     |  |

| D <sub>max</sub>                                                                                                               | Maximum Duty Cycle @ 118 kHz and V <sub>pin9</sub> = 1.0 V                                                                                  | 9     | 20            | 24            | 29            | %      |  |

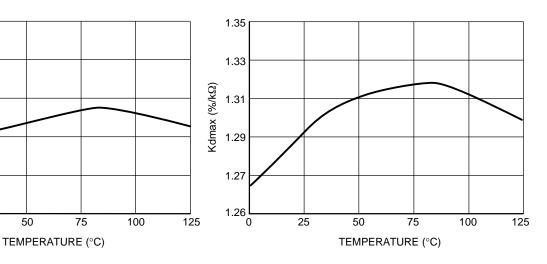

| K <sub>Dmax</sub> Dmax Coefficient @ 118 kHz and V <sub>pin9</sub> = 1.0 V (Note 2)                                            |                                                                                                                                             | 9     | 1.10          | 1.30          | 1.53          | %/kΩ   |  |

around this nominal value (±3.5% variation).

K<sub>Dmax</sub> is the proportionality coefficient that links the maximum duty-cycle to the Pin 9 resistor: Dmax = K<sub>Dmax</sub>\*R<sub>pin9</sub>. K<sub>Dmax</sub> is defined in the "Maximum Duty-Cycle Limitation" section of the operating description.

# **ELECTRICAL2604 CACTERISTIGS** (For typical values $T_J = 25^{\circ}$ C, for min/max values $T_J = 0^{\circ}$ C to +125°C, $V_{pin16} = 48$ V, $V_{CC} = 20$ V unless otherwise noted.)

| Symbol                                                            | Rating                                                                                                                        | Pin | Min     | Тур       | Max     | Unit |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----------|---------|------|

| Soft-Start and                                                    | Timer                                                                                                                         |     |         |           |         |      |

| I <sub>ch</sub>                                                   | Soft-Start or Jittering charge current @ V <sub>pin6</sub> = 2.4 V                                                            | 6   | 60      | 95        | 110     | μΑ   |

| I <sub>disch</sub>                                                | Jittering Discharge Current @ V <sub>pin6</sub> = 2.4 V                                                                       | 6   | 77      | 107       | 137     | μΑ   |

| Vjitter                                                           | Jittering Saw-Tooth Lower Threshold                                                                                           | 6   | 1.67    | 1.80      | 1.89    | V    |

| V <sub>jitter</sub> H                                             | Jittering Saw-Tooth Upper Threshold                                                                                           | 6   | 2.85    | 3.00      | 3.20    | V    |

| V <sub>timer</sub> L                                              | Timer Peak Threshold                                                                                                          | 6   | 4.0     | 4.3       | 4.6     | V    |

| I <sub>timerC</sub>                                               | Timer Charge Current @ $V_{pin6}$ = 3.5 V and Pin 8 open                                                                      | 6   | 3.9     | 5.2       | 6.4     | μA   |

| I <sub>timerD</sub>                                               | Timer Discharge Current @ $V_{pin6}$ = 3.5 V and Pin 8 open                                                                   | 6   | -       | 400       | -       | μA   |

| Feedback Sect                                                     | ion                                                                                                                           |     |         |           |         |      |

| Rup                                                               | Internal Pullup Resistor                                                                                                      | 8   | -       | 20        | -       | kΩ   |

| lfb                                                               | Source Current @ V <sub>pin8</sub> = 0.5 V                                                                                    | 8   | -       | 200       | -       | μΑ   |

| Iratio                                                            | Pin 8 to current Setpoint division ratio                                                                                      | -   | -       | 3.0       | -       | -    |

| Internal Ramp                                                     | Compensation                                                                                                                  |     | •       | •         | •       |      |

| R <sub>ramp</sub>                                                 | Internal Resistor                                                                                                             | 10  | -       | 32        | -       | kΩ   |

| V <sub>ramp</sub> Internal Saw–Tooth Amplitude                    |                                                                                                                               | 10  | -       | 3.2       | -       | V    |

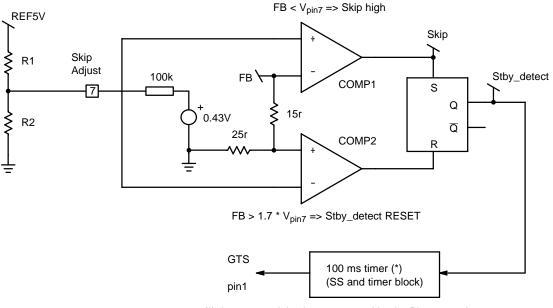

| Skipping Mode                                                     | e and Standby Management                                                                                                      |     |         |           |         |      |

| Rgts                                                              | Pin 1 output impedance in standby state (Pin 8 grounded, $V_{pin6}$ > 4.5 V) @ $V_{CC}$ = 12.5 V                              | 1   | 4.0     | 8.0       | 18      | kΩ   |

| Igts                                                              | Igts Sink Current Source in Normal Mode<br>@ V <sub>pin8</sub> = 2 V, Pin 7 open @ V <sub>CC</sub> - V <sub>pin1</sub> =0.7 V |     | 0.6     | 1.0       | _       | mA   |

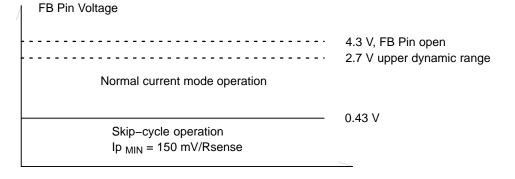

| FB–skip                                                           | Default Feedback Level for Skip–Cycle Operation and Standby<br>Detection                                                      | 7   | 380     | 430       | 480     | mV   |

| FB_stby-out                                                       | Default Feedback Level to Leave Standby                                                                                       | 7   | 650     | 740       | 810     | mV   |

| V <sub>stby-out</sub> /V <sub>skip</sub>                          | Ratio leave standby Setpoint to skip-cycle Setpoint                                                                           |     | 1.5     | 1.7       | 1.9     | _    |

| R <sub>pin7</sub>                                                 | Internal Pin 7 Impedance                                                                                                      | 7   | -       | 110       | -       | kΩ   |

|                                                                   | Pin 7 to Skipping Setpoint ratio                                                                                              |     | -       | 3.0       | -       | _    |

| Brown-Out De                                                      | tection                                                                                                                       |     | <b></b> | <b></b>   | <b></b> |      |

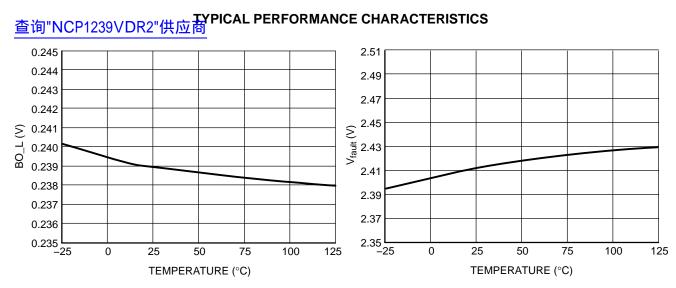

| BO <sub>thH</sub>                                                 | Brown-Out Detection Upper Threshold                                                                                           | 5   | 0.45    | 0.50      | 0.55    | V    |

| BO <sub>thL</sub>                                                 | Brown–Out Detection Low Threshold                                                                                             | 5   | 0.20    | 0.24      | 0.28    | V    |

| BO <sub>hyst</sub>                                                | Brown–Out Hysteresis                                                                                                          | 5   | 0.20    | 0.26      | 0.30    | V    |

| Protections                                                       |                                                                                                                               |     | •       | •         | •       |      |

| TSD Thermal Shutdown:<br>Thermal Shutdown Threshold<br>Hysteresis |                                                                                                                               |     |         | 140<br>30 |         | °C   |

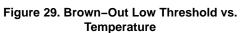

| Vfault                                                            | Fault Detection Threshold                                                                                                     | 3   | 2.2     | 2.4       | 2.6     | V    |

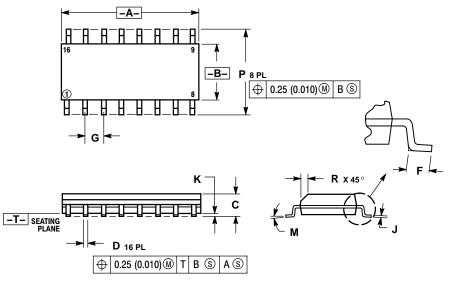

#### **ORDERING INFORMATION**

| Device       | Package              | Shipping <sup>†</sup> |

|--------------|----------------------|-----------------------|

| NCP1239FDR2  | SOIC-16              | 2500 / Tape & Reel    |

| NCP1239FDR2G | SOIC-16<br>(Pb-Free) | 2500 / Tape & Reel    |

| NCP1239VDR2  | SOIC-16              | 2500 / Tape & Reel    |

| NCP1239VDR2G | SOIC-16<br>(Pb-Free) | 2500 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# BINE WICTION BESCEIPTED TO

| Pin No. | Pin Name                          | R之门共办任网<br>Function                                                                     | Pin Description                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-----------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GTS                               | Shuts the PFC down in standby                                                           | The standby detection block changes Pin 1 state in accordance to the mode (standby or normal mode). Pin1 is designed to drive an external pnp transistor that connects or disconnects the NCP1239's $V_{CC}$ to the PFC's.                                                                                                                                                             |

| 2       | REF5V                             | A 5V reference voltage                                                                  | This pin helps to internally bias the controller but can also be used to power surrounding logic gates for any purposes. The typical output current is 10 mA. This voltage source is disabled during the circuit startup and latched–off phases. A 100 nF filtering capacitor must be placed between Pin 2 and ground.                                                                 |

| 3       | Fault Detect                      | Enables to permanently shutdown the part                                                | If the Pin 3 voltage exceeds 2.4 V, the circuit is permanently shut down. This pin can be used to monitor the voltage across a thermistor in order to protect the application from excessive heating and/or to detect an overvoltage condition.                                                                                                                                        |

| 4       | Rt                                | Timing resistor                                                                         | Pin 4 resistor allows a precise frequency programming. The circuit is optimized to operate between 50 kHz and 150 kHz (NCP1239F) and between 100 kHz and 250 kHz (NCP1239V).                                                                                                                                                                                                           |

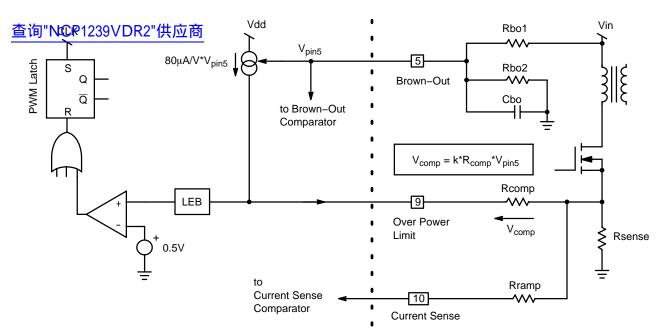

| 5       | Brown-Out                         | Brown–Out                                                                               | This pin receives a portion of the bulk capacitor to authorize operation above a certain level of mains only. It also serves to elaborate an offset voltage on Pin 9 used for Over Power Compensation.                                                                                                                                                                                 |

| 6       | SS/Timer                          | Performs soft-start and fault timeout                                                   | During Power on and fault conditions, the capacitor connected to this pin ensures a soft–start period. When a fault is detected, this pin is internally brought high by a current source. If 4.3 V are reached, the fault is confirmed and the circuit enters an auto–recovery burst mode, otherwise the pin goes back to a lower value and oscillates to perform frequency jittering. |

| 7       | Skip Adjust                       | Adjust skip level                                                                       | By adjusting the skip–cycle level, it is possible to fight against noisy transformers and modify the standby detection thresholds. Keep Pin 7 open to operate with the default levels (skip threshold setpoint: 140 mV, normal mode recovery setpoint: 250 mV).                                                                                                                        |

| 8       | FB                                | Feedback signal                                                                         | An opto-coupler collector pulls this pin low to regulate                                                                                                                                                                                                                                                                                                                               |

| 9       | Over Power<br>Limit<br>(NCP1239F) | Enables a precise peak<br>current clamp and then an<br>accurate Over Power<br>Detection | This pin delivers a current proportional to $V_{pin5}$ , an image of the high voltage rail.<br>Inserting a resistor between Pin 9 and the current sense resistor, an offset<br>proportional to the input voltage is built. Such offset compensates the circuit and<br>power switch propagation delays for an accurate power limitation in the whole input<br>voltage range.            |

| 9       | Max Duty–<br>Cycle<br>(NCP1239V)  | Enables to precisely<br>clamp the maximum<br>duty-cycle.                                | This terminal sources a constant current. Connect a resistor between Pin 9 and Ground to select the maximum duty-cycle.                                                                                                                                                                                                                                                                |

| 10      | CS                                | The current sense input                                                                 | This pin receives the primary current information via a sense element. By inserting a resistor in series with this pin, it becomes possible to introduce ramp compensation.                                                                                                                                                                                                            |

| 11      | Ground                            | The IC ground                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                      |

| 12      | Drv                               | Drives the MOSFET                                                                       | By offering up to +500 mA/–800 mA peak, this pin lets you drive large Qg MOSFET's. It is clamped to 16 V maximum not to exceed the maximum gate–source voltage of most power MOSFET's.                                                                                                                                                                                                 |

| 13      | V <sub>CC</sub>                   | Supplies the controller                                                                 | This pin accepts up to 36 V from an auxiliary winding.                                                                                                                                                                                                                                                                                                                                 |

| 14      | NC                                | -                                                                                       | Creepage distance.                                                                                                                                                                                                                                                                                                                                                                     |

| 15      | NC                                | _                                                                                       | Creepage distance.                                                                                                                                                                                                                                                                                                                                                                     |

| 16      | HV                                | The high-voltage startup                                                                | This pin connects to the bulk capacitor to generate the startup current.                                                                                                                                                                                                                                                                                                               |

24.5

24.3

24.1

23.9

23.7

23.5

0

25

Dmax (%)

Figure 32. Kdmax Coefficient vs. Temperature @ V<sub>pin9</sub> = 1 V (NCP1239V)

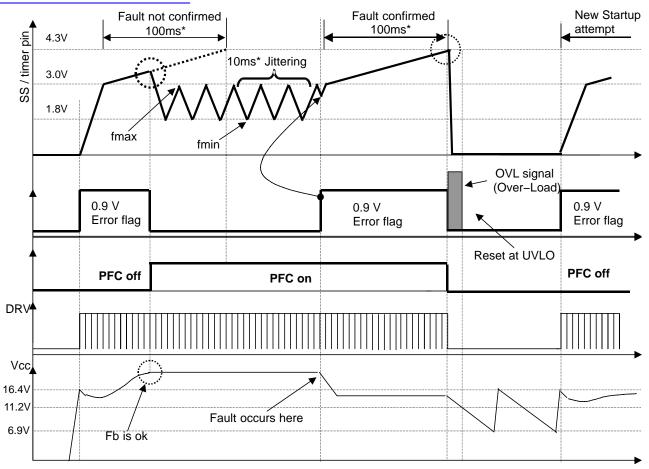

**Fault Management**

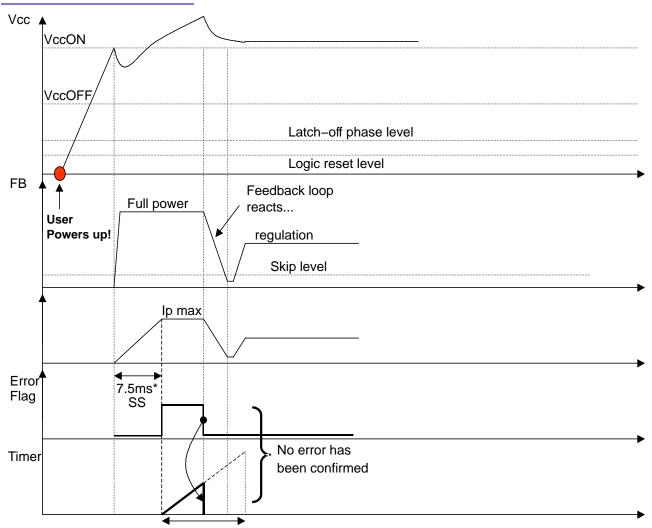

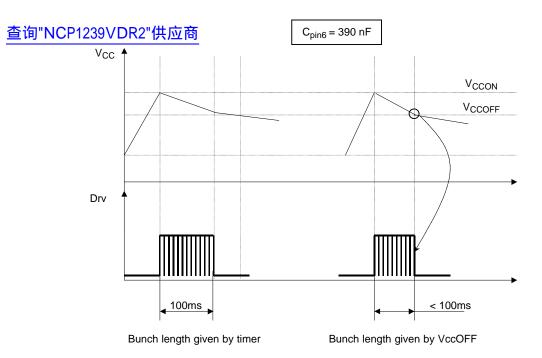

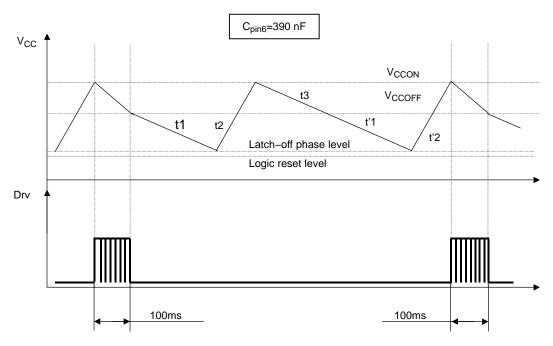

\*This time is programmed by the Pin 6 capacitor.  $C_{pin6}$  = 390 nF nearly sets the following intervals: - Soft–Start Time (T<sub>ss</sub>):7.5 ms - Jittering Period (T<sub>jittering</sub>): 10 ms - Fault Detection Delay (T<sub>delay</sub>): 100 ms More generally, the times approximately depend on  $C_{pin6}$  as follows: - T<sub>ss</sub> = 7.5 ms \*  $C_{pin6}$  / 390 nF - T<sub>jittering</sub> =10 ms \*  $C_{pin6}$  / 390 nF - T<sub>delay</sub> =100 ms \*  $C_{pin6}$  / 390 nF

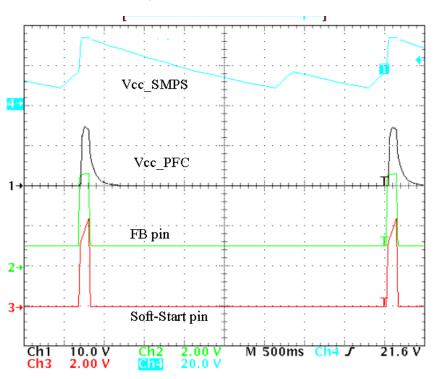

Figure 33. Fault Management

\*This time is programmed by the Pin 6 capacitor.  $C_{pin6} = 390 \text{ nF}$  nearly sets the following intervals: - Soft-Start Time ( $T_{ss}$ ):7.5 ms - Jittering Period ( $T_{jittering}$ ): 10 ms - Fault Detection Delay ( $T_{delay}$ ): 100 ms More generally, the times approximately depend on  $C_{pin6}$  as follows: -  $T_{ss} = 7.5 \text{ ms} * C_{pin6} / 390 \text{ nF}$ -  $T_{jittering} = 10 \text{ ms} * C_{pin6} / 390 \text{ nF}$ -  $T_{delay} = 100 \text{ ms} * C_{pin6} / 390 \text{ nF}$

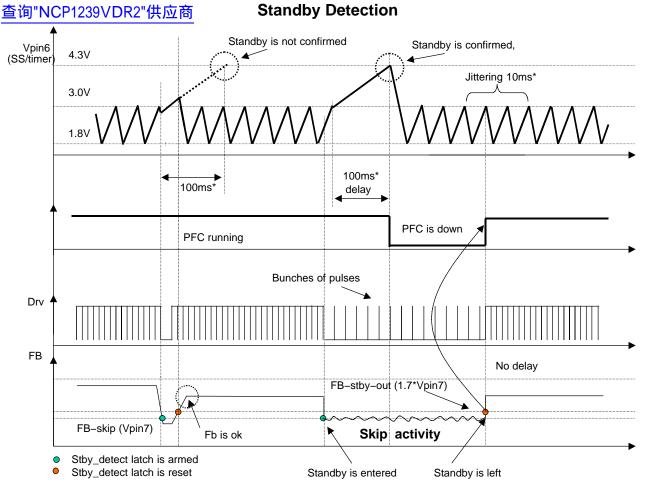

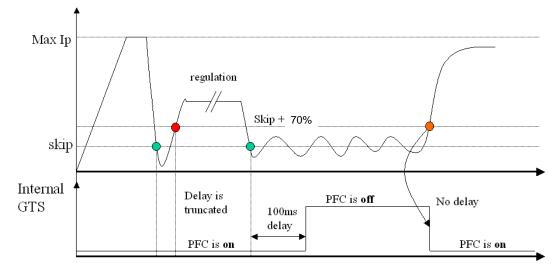

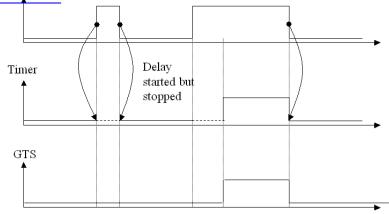

Figure 34. Standby Detection

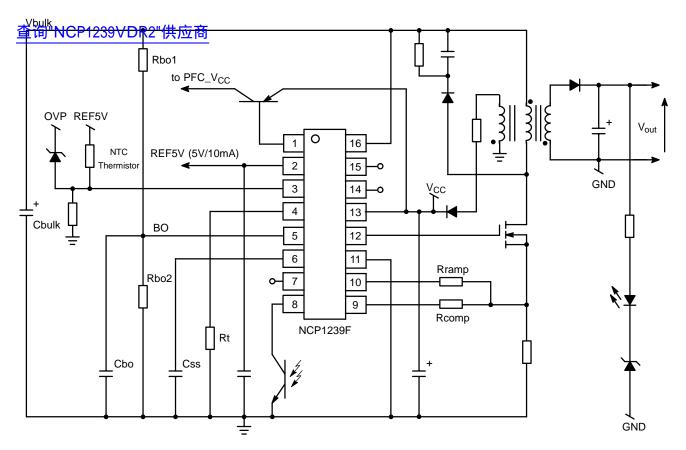

### 查询"NCP1239VDR2"供应商

#### APPLICATION INFORMATION

The NCP1239 includes all necessary features to help building a rugged and safe switch-mode power supply. The following details the major benefits brought by implementing the NCP1239 controller:

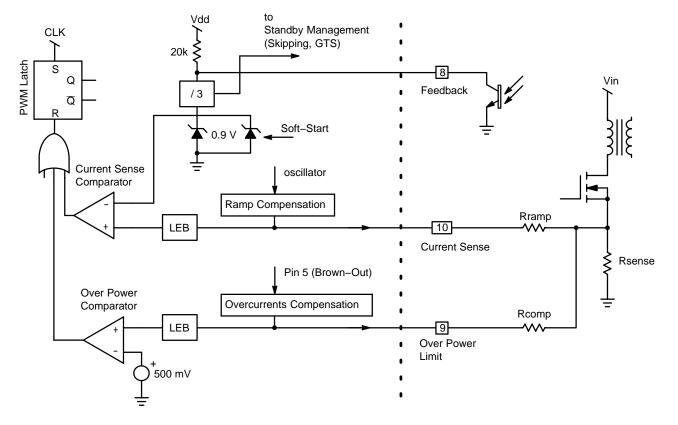

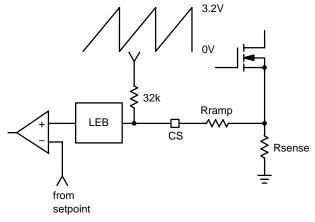

*Current-mode operation with internal ramp compensation:* implementing peak current mode control, the NCP1239 offers an internal ramp compensation signal that can easily be summed up to the sensed current. Subharmonic oscillations can thus be fought via the inclusion of a simple resistor,

500 mV Current Sense threshold for Over Power Limit (NCP1239F): the NCP1239 operating in current mode, the circuit Pin 10 monitors the current to modulate its level according to the power demand. Due to the ramp compensation, one must generally note that the Pin 10 voltage is not the exact image of the inductor current. A precise current limitation being essential, the NCP1239 features a separate current sense pin (Pin 9) for an accurate overcurrent detection. The low threshold of this protection (500 mV) avoids excessive losses in the current sense resistor and improves the efficiency. In addition, Pin 9 sources a current that proportional to the high-voltage rail, compensates the current-sense and turn off delays at high line. A resistor inserted between Pin 9 and the sensing resistor offsets the Pin 9 current-sense information to build a precise overload protection, independent of the mains input.

*Large V<sub>CC</sub> operation:* the NCP1239 offers an extended  $V_{CC}$  range up to 36 V, bringing greater flexibility in Flyback or Forward applications.

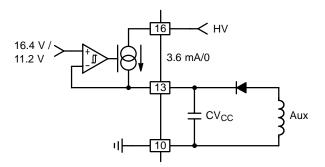

*Internal high–voltage startup switch:* reaching low levels of standby power represents a difficult exercise when the controller requires an external, lossy, resistor connected to the bulk capacitor. Due to an internal logic, the controller disables the high–voltage current source after startup which no longer hampers the consumption in no–load situations.

*Skip-cycle capability:* a continuous flow of pulses is not compatible with no-load standby power requirements. Slicing the switching pattern in bunch of pulses drastically reduces overall losses but can, in certain cases, bring acoustic noise in the transformer. Due to a skip operation taking place at low peak currents only, no mechanical noise appears in the transformer. Furthermore, the skip threshold is made programmable to allow the best trade-off between noise and efficiency.

*Standby Detect/Shutdown of the PFC front-stage:* The NCP1239 incorporates an internal logic that is able to detect a standby situation. Pin1 state changes in accordance to the

detected mode (standby or normal mode). Simply connect a pnp transistor between the NCP1239  $V_{CC}$  and the PFC controller one and drive it using Pin 1, to enable the PFC stage in normal mode and disable it in standby.

*Soft–Start:* the capacitor connected to Pin 6 provides a soft–start sequence that precludes the main power switch from being stressed upon startup. The same voltage is also used to perform frequency jittering and timing for the fault condition detection.

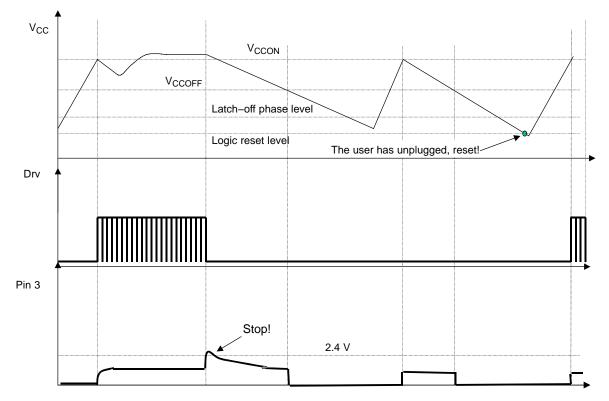

**Major Fault Detection:** the circuit detects when Pin 3 voltage exceeds 2.4 V. When this occurs, the NCP1239 considers that a major fault is present and as a consequence, the circuit gets permanently latched–off. In this mode, the circuit needs the  $V_{CC}$  to go down below 4.0 V to reset, for instance when the user un–plugs the SMPS. This capability is mainly intended to detect an overvoltage condition or/and an over–heating of the application that would be sensed by a thermistor.

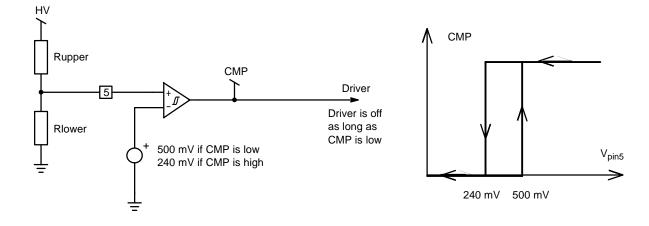

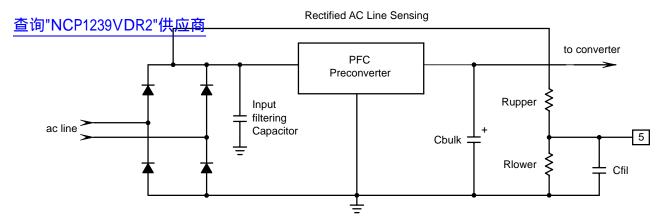

**Brown–out detection:** by monitoring the level on Pin 5 during normal operation, the controller protects the SMPS against low mains conditions. When the Pin 5 voltage falls below 250 mV, the controllers stops pulsing until this level goes back to 500 mV to prevent any instability.

*Short–circuit protection:* short–circuit and especially overload protections are difficult to implement when a strong leakage inductance affects the transformer (the auxiliary winding level does not properly collapse...). Here, every time the feedback pin is at its maximum (higher than 5.0 V practically), an error flag is asserted and the circuit activates a timer that is programmed by the Pin 6 capacitor. If Pin 6 reaches 4.3 V while the error flag is still present, the controller stops the pulses and goes into a latch–off phase, operating in a low–frequency burst–mode. As soon as the fault disappears, the SMPS resumes its operation. The latch–off phase can also be initiated, more classically, when V<sub>CC</sub> drops below UVLO (11.2 V typical).

Adjustable frequency and Internal dithering for improved EMI signature: Pin 4 offers a means to precisely adjust the switching frequency through a simple resistor to ground. Frequency operation is allowed up to 250 kHz. By modulating the internal switching frequency with the Pin 6 saw-tooth (100 Hz with 390 nF), natural energy spread appears and softens the controller's EMI signature.

**5.0 V reference voltage:** a 5.0 V regulator is provided to help biasing any external circuitry in the vicinity of the controller. This reference voltage can typically supply up to 10 mA.

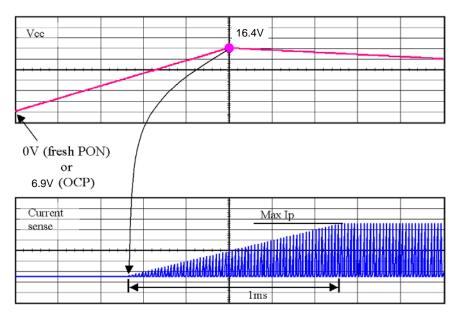

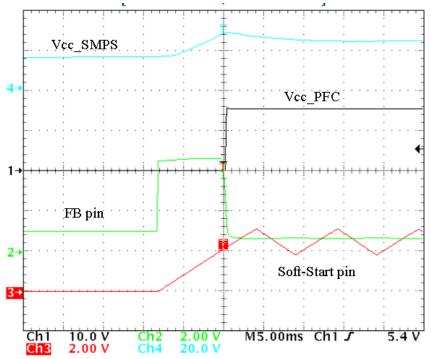

#### Startup, Sequence When the power supply is first connected to the mains

When the power supply is first connected to the mains outlet, the internal current source (typically 3.6 mA) is biased and charges up the  $V_{CC}$  capacitor. When the voltage on this  $V_{CC}$  capacitor reaches the  $V_{CCON}$  level (typically 16.4 V), the current source turns off and no longer wastes any power. At this time, the energy stored by the  $V_{CC}$ capacitor serves to supply the controller and the auxiliary supply is supposed to take over before  $V_{CC}$  collapses below  $V_{CCOFF}$ . Figure 35 shows the internal arrangement of this structure:

The current source brings  $V_{CC}$  above 16.4 V and then turns off Figure 35.

As soon as  $V_{CC}$  reaches 16.4 V, driving pulses are delivered on Pin 12 and the auxiliary winding grows up the  $V_{CC}$  pin. Because the output voltage is below the target (the SMPS is starting up), the feedback pin is at its maximum voltage. A resistor divider outputs the third of the feedback voltage that forms the current setpoint. This setpoint is clamped and the limitation level slowly increases until it reaches 0.9V during the soft start time. In nominal operation, the setpoint clamp keeps equal to 0.9 V (refer to Figure 36).

As soon as the feedback voltage is high enough to activate the 0.9 V setpoint clamp (during the startup period but also anytime an overload occurs), an internal error flag is asserted, testifying that the system is pushed to the maximum power. At that moment, a 100 ms time period (typically, with Cpin6=390 nF that also corresponds to 7.5 ms soft -start) starts while a logic block observes this error flag. If the error flag keeps asserted all along the 100ms period, then the controller assumes that the power supply really undergoes a fault condition and immediately stops all pulses to enter a safe burst operation. The 100 ms timer enables to distinguish a startup phase (shorter than 100 ms) from an overload condition. If the error flag is released before the 100 ms period has elapsed, the controller concludes that no error is present and resets the timer to use it for other purposes (e.g. frequency dithering).

Pin 10 monitors the power switch current and compares it to the current setpoint (one third of the feedback voltage). The current setpoint is limited by the soft-start during the power-on sequence and permanently clamped to 0.9 V In the NCP1239F, a second pin (Pin 9) monitors the current to clamp the power.

#### Figure 36. Current Control

Eigure 37 depicts the Vree explution during a proper startup sequence, showing the state of the error flag:

\*This time is programmed by the Pin 6 capacitor.  $C_{pin6}$  = 390 nF nearly sets the following intervals: - Soft–Start Time (T<sub>ss</sub>):7.5 ms - Jittering Period (T<sub>jittering</sub>): 10 ms - Fault Detection Delay (T<sub>delay</sub>): 100 ms More generally, the times approximately depend on  $C_{pin6}$  as follows: - T<sub>ss</sub> = 7.5 ms \*  $C_{pin6}$  / 390 nF - T<sub>jittering</sub> =10 ms \*  $C_{pin6}$  / 390 nF - T<sub>delay</sub> =100 ms \*  $C_{pin6}$  / 390 nF

Figure 37.

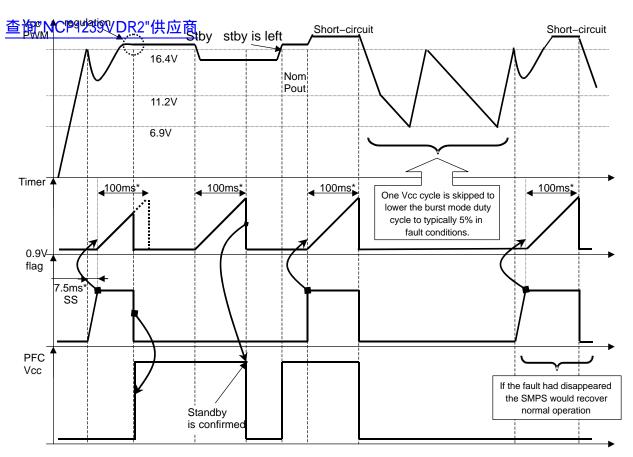

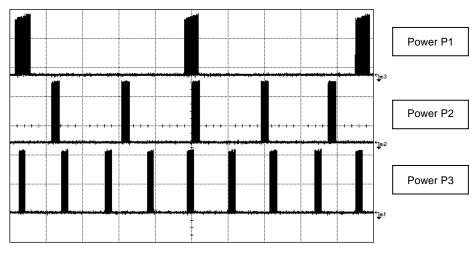

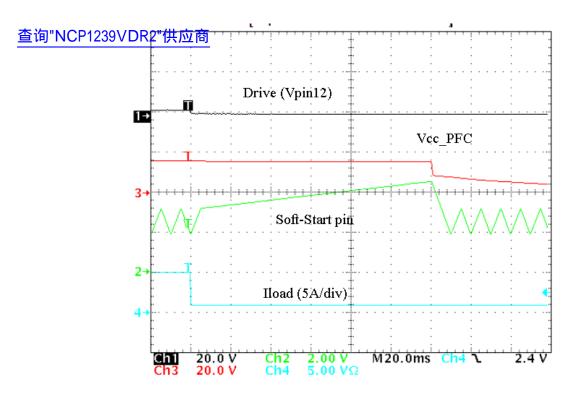

EFC Startup Sequence To ensure an adequate startup sequence of both PWM section and the PFC stage, some logic and timing need to be included as shown on the internal diagram. The key point here is the fact that the PFC always starts after the PWM section. As a result, the SMPS must be designed to cope with transient universal mains operation. Why this? Because of the light-to-heavy load transition where a case exists when the PFC is off, the PWM in standby and the load is suddenly applied. In this scenario, the PWM section must sustain the entire transient period that lasts until the PFC re-starts since it has been deactivated for standby.

The standby detection block generates an internal signal "pfcON" that controls Pin 1 in accordance to the operation mode:

- "pfcON" is high in normal mode and a current source draws 1 mA from Pin 1,

- "pfcON" is low in standby to disable the 1 mA current source. A 10 k $\Omega$  resistor pulls up Pin 1 to V<sub>CC</sub>.

This configuration makes it ideal to drive a pnp transistor that connects or disconnects the NCP1239  $V_{CC}$  to the PFC controller one (refer to Figure 39). The "pfcON" signal is activated following Figure 38 diagram. Let's split this drawing in different time periods to clearly depict signal assertions:

Power on: during this time, V<sub>CC</sub> rises up, the V<sub>CC</sub> capacitor being charged by the 3.6 mA current source. When V<sub>CC</sub> exceeds V<sub>CCON</sub> (16.4 V typ.), driving pulses are delivered to the MOSFET in an attempt to crank the power supply.  $V_{CC}$  collapses (because the  $V_{CC}$  capacitor alone delivers the energy) until sufficient auxiliary voltage is built up in order to take over the startup sequence and thus self-supply the controller. As long as the output voltage has not reached its wished value, the controller pushes for the maximum peak current. During the soft-start (7.5 ms with 390 nF on Pin 6), the maximum permissible current linearly increases till the maximum peak setpoint is reached, the

internal 0.9 V Zener diode actively clamping the current amplitude to (0.9 V/Rsense). During this time, the NCP1239 asserts an error flag. A maximum current condition being observed, the circuit determines if this state results from either a normal response (startup or a transient period) or a fault condition. To make the difference, each time the error flag is asserted, a 100 ms timer starts to count down. If the error flag keeps asserted for the 100 ms period, there is a fault and the PWM controller enters a safe, auto-recovery, burst mode to limit the dissipated heat (see below for more details). During the Power-on sequence, "pfcON" keeps low to pullup Pin 1 to  $V_{CC}$  until the error flag is down. When the error flag is down, the power supply has entered regulation, its auxiliary voltage is stable, then Pin 1 can turn low (1 mA sink current) to safely allow PFC operation.

Entering Standby: when skip-cycle starts to activate, a 100 ms countdown takes place and the logic observes the skip activity. If the skip activity is still there at the end of the 100 ms, then standby is confirmed and the NCP1239 pulls up Pin 1 to V<sub>CC</sub> to shut down the PFC.

Leaving standby: in this case, as soon as the skip-cycle activity disappears, the circuit immediately re-activates the 1 mA sinking current source of Pin 1, to enable the PFC: there is no reaction delay in this situation.

Short-circuit condition: a short circuit is detected on the primary side by measuring the time the error flag is asserted. As explained, if this flag is asserted longer than 100 ms, then the PWM stops oscillating and enters a safe burst mode. In this case, Pin 1 is pulled up to  $V_{CC}$  and the PFC is shut down. During the burst, it is not activated (PFC is off) until the fault goes away and the power supply resumes operation. The PFC being shut off in short-circuit conditions, it naturally reduces the main MOSFET stress.

Latch-off mode: if the controller is permanently latched-off due to a major fault (Pin 3 detection of an OVP or an excessive external temperature), the PFC is kept off (Pin 1 being tied to  $V_{CC}$ ).

\*This time is programmed by the Pin 6 capacitor.  $C_{pin6} = 390 \text{ nF}$  nearly sets the following intervals: - Soft-Start Time (T<sub>ss</sub>):7.5 ms - Jittering Period (T<sub>jittering</sub>): 10 ms - Fault Detection Delay (T<sub>delay</sub>): 100 ms More generally, the times approximately depend on  $C_{pin6}$  as follows: - T<sub>ss</sub> = 7.5 ms \*  $C_{pin6} / 390 \text{ nF}$ - T<sub>delay</sub> =100 ms \*  $C_{pin6} / 390 \text{ nF}$ - T<sub>delay</sub> =100 ms \*  $C_{pin6} / 390 \text{ nF}$

Figure 38.

The PFC controller connection is really straightforward as testilited by Figure 39: simply connect to Pin 1, the base of a pnp transistor that connects the PFC's  $V_{CC}$  to the NCP1239 one (perhaps add a small decoupling capacitor like a 0.1  $\mu$ F on the PFC) and this is all! The PFC startup network goes

away as it is fully supplied by the PWM auxiliary winding and even high quiescent current devices do not hamper the standby power since they are completely disconnected in standby.

The NCP1239 turns off the pnp Q1 during the standby so that the PFC controller is no longer supplied in this mode.

#### Figure 39.

# Short-Circuit or Overload Condition

The NCP1239 differs from other controllers in the sense that a fault condition is detected independently of the auxiliary voltage level. In auxiliary supply–based power supplies, it is necessary that the (isolated) secondary output conditions properly reflects on the (non–isolated) auxiliary winding in order to instruct the controller on what is happening on the other side of the transformer. For the following reasons, it sometimes becomes extremely difficult to build an efficient short–circuit protection circuitry and even more difficult to implement over power detection (e.g. the output load is 25% above the nominal value but Vout is still present).

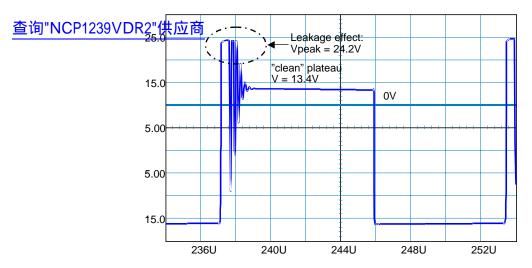

The primary leakage inductance is high: this is probably the main reason why building efficient short-circuit detection is difficult. When the power switch opens, the leakage inductance superimposes a large overvoltage spike on the drain voltage. This spike is seen on the secondary side but also on the auxiliary winding. Unfortunately, since the  $V_{CC}$  capacitor and the auxiliary diode form a peak rectifier, the auxiliary  $V_{CC}$  often depends on this peak value rather than the true plateau which corresponds to the output level.

The leakage effect seen on the auxiliary side pulls-up the final level peak-rectified by the diode

Figure 40.

On Figure 40's example, one can clearly observe the difference between the peak and the real plateau DC level. The delta is around 10 V, which obviously degrades the auxiliary image of the secondary side. When a short–circuit occurs, the leakage can be so strong that the whole plateau has dropped to a few volts, but the leakage contribution becomes so energetic (Ip = Ip max.) that even a few  $\mu$ s duration is enough to prevent V<sub>CC</sub> auxiliary from collapsing and thus stopping the pulses. Needless to say that over power detection is simply impossible.

Low standby power requirement decreases  $V_{CC}$  at no–load: this is particularly true if you try to reach less than 100 mW at high line. Due to skip–cycle, the continuous flow of pulses turns into bunches of pulses (sometimes 1–2 pulses only) that can be spaced by 50ms or more in certain cases. The energy content in each bunch of pulses does not suffer any attenuation. For instance, to lower Figure 40's peak, you could think of inserting a resistor with the auxiliary diode to form a low pass filter with the V<sub>CC</sub> capacitor. Unfortunately, it would drastically reduce the V<sub>CC</sub> capacitor refueling current and V<sub>CC</sub> could not be maintained. To compensate that effect, a solution could be to increase the turn ratio, but then the peak rectification problem comes back again.

As one can see, a short–circuit protection free of the  $V_{CC}$  level would be the best solution. This is exactly what the NCP1239 delivers with the internal 100 ms timer (390 nF being connected to Pin 6). As soon as the internal 0.9 V error flag is asserted high, a 100 ms timer gets started. If the error flag keeps asserted during the 100 ms period, then the controller detects a true fault condition and stops pulsing the output. If this is a simple transient overload, e.g. the error flag goes back to a normal level before the 100 ms period has

elapsed, nothing happens and the controller continues working normally.

When a fault is detected, we have seen that the controller stops delivering pulses. At this time,  $V_{CC}$  starts to drop because the power supply is locked off. When the  $V_{CC}$  drops below  $V_{CCOFF}$  (11.2 V typical), it enters a so-called latch-off phase where the internal consumption is reduced down to about 400  $\mu$ A. The  $V_{CC}$  capacitor continues to deplete, but at a lower rate. When  $V_{CC}$  finally reaches the latch-off level (around 6.9 V), the startup current source turns on and pulls  $V_{CC}$  above  $V_{CCON}$ , exactly as a startup sequence would do. When  $V_{CC}$  exceeds  $V_{CCON}$  (16.4 V), pulses are delivered and can last 100 ms maximum if there is enough voltage or can be prematurely interrupted if  $V_{CC}$  falls below  $V_{CCOFF}$ . Figure 41 shows the difference between these two cases. As already explained, in short–circuit bursts, the PFC section is not validated.

The short–circuit protection features a so–called auto–recovery circuitry. That is to say, during the 100 ms period, the power supply attempts to startup. If the fault has gone, then the controller resumes from the fault and the power supply operates again. If the fault is still present, the pulses are stopped at the end of the 100 ms section (Tpulse) for a given time period Tfault. At the end of Tfault, a new 100 ms attempt is made and so on. To avoid any thermal runaway, a burst duty–cycle defined by Tpulse/(Tfault+Tpulse) below 10% is desirable ((Tfault+Tpulse) is the burst period). If the 100 ms is made by an internal timer in conjunction with the Pin 6 capacitor, the Tfault duration builds on the V<sub>CC</sub> capacitor which is charged/discharged two times. Figure 42 on the following page portrays this behavior.

When  $V_{CC}$  drops faster than the timer, it prematurely interrupts the pulses flow. The 100 ms delay could be shortened or lengthened by changing the Pin 6 capacitor.

The burst period is ensured by the  $V_{CC}$  capacitor charge/discharge cycle The 100 ms delay could be shortened or lengthened by changing the Pin 6 capacitor.

Figure 42.

If hy design we have selected a 47  $\mu$ F V<sub>CC</sub> capacitor, it becomes easy to evaluate the burst period and its duty-cycle. This can be done by properly identifying all time events on Figure 42 and applying the classical formula:  $t = C * \Delta V/i$ . To simplify, let's consider t1 starts while V<sub>CC</sub> = V<sub>CCOFF</sub>. Then:

- t1: I = I<sub>CC</sub>3 = 400  $\mu$ A,  $\Delta$ V= 11.2 6.9 = 3 V  $\rightarrow$  t1 = 505 ms

- t2: I = 3.6 mA,  $\Delta V$ = 16.4 6.9 = 9.5 V  $\rightarrow$  t2 = 124 ms

- t3: I = 400  $\mu$ A,  $\Delta$ V= 16.4 11.2 = 5.2 V  $\rightarrow$  t3 = 611 ms

- t'1 = t1= 505 ms

- t'2 = t2 = 124 ms

The total period duration is thus the sum of all these events which leads to Tfault = 1793 ms. If Tpulse = 100 ms, then our burst duty-cycle equals  $100/(1869 + 100) \approx 5\%$ , which is excellent.

In fact, the calculation assumption, t1 starts while  $V_{CC} = V_{CCOFF}$ , gives the worse case since the duty cycle is calculated in the case where Tpulse exactly equals the active phase duration (switching period when  $V_{CC}$  decreases from  $V_{CCON}$  to  $V_{CCOFF}$ ).

In fact, Tpulse is generally:

– shorter than the switching phase period. In this case, t1 is longer since the latched off phase starts earlier (at a  $V_{CC}$  higher than  $V_{CCOFF}$ ). As a consequence, the final duty cycle is lower than previously estimated,

– longer than the switching phase period. In this case, the circuit detects an overload condition simply because  $V_{CC}$  drops below  $V_{CCOFF}$  (11.2 V) before the fault timer has elapsed. Tpulse is lower than 100 ms and as a result the duty cycle is also lower.

#### (Major) Fault Detection and Latched Off Mode

The NCP1239 features a fast comparator that permanently monitors the "Fault Detect" pin level. If for any reason this level exceeds 2.4 V (typical), the part immediately stops oscillating and stays latched off until the user cycles down the power supply. This enables the SMPS designer to externally shut down the part in particular when a major default occurs, e.g. an Overvoltage Protection (OVP). Figure 43 shows what happens when the part is latched:

When Vpin3 exceeds 2.4 V, NCP1239 permanently latches–off the output pulses...until its  $V_{CC}$  goes below 4 V. The figure can illustrate a case where a thermistor supplied by REF5V is connected to Pin 3 to detect excessive temperatures of the application (refer to application schematic).

Figure 43.

Pin 3 can serve to build an Overvoltage Protection by placing a Zener between the voltage to measure (e.g.,  $V_{CC}$ ) and Pin 3 (refer to application schematic). If a 15 V Zener is applied, the Pin 3 comparator will switch when ( $V_{CC}$  – 15 V) exceeds the 2.4 V internal reference, that is, when  $V_{CC}$  is higher than 17.5 V.

This pin can also monitor the temperature using an external thermistor (refer to application schematic). Thermistors can be of Negative Temperature Coefficient (NTC) type (the resistance decreases versus the temperature) or of Positive Temperature Coefficient (PTC) type (the resistance increases versus the temperature). Let's assume that a NTC thermistor is used (as in the application schematic). Placing it between the 5 V reference voltage (REF5V) and Pin 3, and a classical resistance between Pin 3 and ground, the Pin 3 voltage equals:

$$V_{\text{pin3}} = \frac{R}{R + R_{\text{thermistor}}} \cdot 5 \text{ V}$$

where R and R<sub>thermistor</sub> are respectively the resistor and the thermistor resistance.

$R_{thermistor}$  decreasing versus the temperature, the Pin 3 voltage ( $V_{pin3}$ ) increases when the temperature grows up.

For instance, the thermistor resistance can be in the range of 500 k $\Omega$  at 25°C and as low as 5 k $\Omega$  at 130°C that as an

example, one can take as the temperature limit the application must not exceed. Choosing R equal to 5k, the Pin 3 voltage at  $130^{\circ}$ C that equates:

$$V_{\text{pin3}}(130^{\circ}\text{C}) = \left[\frac{5 \text{ k}}{5 \text{ k} + 5 \text{ k}}\right] \cdot 5 \text{ V} = 2.5 \text{ V}$$

triggers the fault comparator.

This example illustrates that one must just select the bottom resistor so that it exhibits the same resistance as the thermistor at the temperature to be detected.

If the thermistor is a PTC, it must be placed between Pin 3 and ground. One must place a resistor between the 5 V reference voltage and Pin 3. Similarly, the resistor must be selected so that its resistance equals the thermistor one at the temperature to be detected.

#### **Brown–Out and Over Power Limitation**

SMPS are designed for a given input range. When the input voltage is too low (brown–out), the SMPS tends to compensate by sinking an increased current from the line. As a result the power components may suffer from an excessive heating and ultimately the SMPS may be destroyed. To avoid such a risk, the NCP1239 incorporates a brown–out detection that monitors the portion of the input voltage that is applied to Pin 5.

An hysteresis comparator monitors the SMPS input voltage

#### Figure 44.

Also called "Bulk OK" signal (BOK), the Brown–Out (BO) protection prevents the power supply from being adversely destroyed in case the mains drops to a very low value. When it detects such a situation, the NCP1239 no longer pulses but waits until the bulk voltage goes back to its normal level. A certain amount of hysteresis needs to be provided since the bulk capacitor is affected by some ripple, especially at low input levels. For that reason, when the BO comparator toggles, the internal reference voltage changes from 500 mV to 240 mV. This effect is not latched: that is to say, when the bulk capacitor is below the target, the controller does not deliver pulses. As soon as the input voltage grows–up and reaches the level imposed by the resistive divider, pulses are passed to the internal driver and activate the MOSFET.

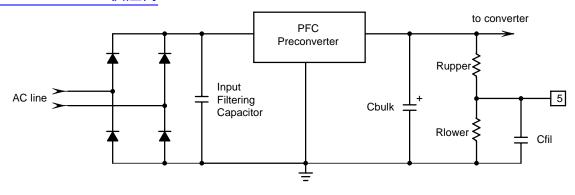

Eigure 45 offers a way to connect the elements around Pin 5 to create a Brown–Out detection:

Example where the voltage of the bulk capacitor is used for the brown-out Protection

#### Figure 45.

The calculation procedure for Rupper and Rlower is easy. The first level transition is always clean: the SMPS is not working during the startup sequence and there exists no ripple superimposed on Cbulk. Supposed we want to start the operation at Vbulk = Vtrip = 120 VDC (i.e., VinAC = 85 V).

- 1. Fix a bridge current Ib compatible with your standby requirements, for instance an Ib of 50  $\mu$ A.

- 2. Then evaluate Rlower by: Rlower =  $0.5/Ib = 10 \text{ k}\Omega$

- 3. Calculate Rupper by:  $(Vtrip 0.5 V)/Ib = (120 0.5)/50 \mu A = 2.39 M\Omega$

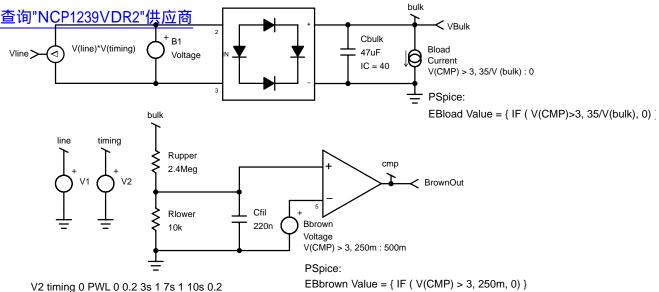

The second threshold, the level at which the power supply stops (VBO), depends on the capacitor Cfil but also on the selected bulk capacitor. Furthermore, when the load varies, the ripple also does and increases as Vin drops. If Cfil allows a too high ripple, chances exist to prematurely stop the converter. By increasing Cfil, you have the ability to select the amount of hysteresis you want to apply. The less ripple appears on a Pin 5, the larger the gap between Vtrip and VBO (the maximum being VBO = Vtrip/2). The best way to assess the right value of Cfil, is to use a simple simulation sketch as the one depicted by Figure 46. A behavioral source loads the rectified DC line and adjusts itself to draw a given

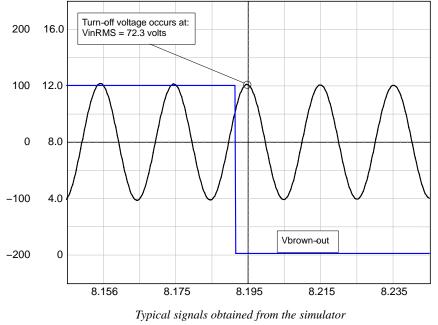

amount of power, actually the power of your converter (35 W in our example). The equation associated to Bload instructs the simulator not to draw current until the Brown–Out converter gives the order, just like what the real converter will do. As a result, Vbulk is free of ripple until the node CMP goes high, giving the green light to switch pulses. The input line is modulated by the "timing" node which ramps up and down to simulate a slow startup/turn–off sequence. Then, by adjusting the Cfil value, it becomes possible to select the right turn–off AC voltage. Figure 47 portrays the typical signal you can expect from the simulator. We measured a turn–on voltage of 85 VAC whereas the turn–off voltage is 72 VAC. Further increasing Cfil lowers this level (for instance, a 1  $\mu$ F capacitor gives VBO = 65 VAC in the example).

As we have seen, the load variations will modify this turn-off level. To remove the dependency between VBO and the load, it is possible to directly sense the rectified input line present at the PFC stage input, as shown in Figure 48. In that case, there still exists the input line ripple, but this ripple is independent of the load. By adjusting Cfil capacitance and the divider section, you can build a brown-out detection independent of the load.

V1 line 0 SIN 0 150 50

A simple simulation configuration helps to tailor the right value for Cfil

Figure 46.

Figure 47.

A second option to directly sense the mains

#### Figure 48.

This second option that directly senses the input voltage (see Figure 48), enables a more direct under-mains detection. Even in a brown-out conditions, the PFC pre-converter may be able to maintain a sufficient bulk voltage, possibly at the price of some excessive stress. Measuring the rectified AC line instead of the bulk voltage, the NCP1239 more surely protects the PFC stage in brown-out conditions.

Using:

- Rlower =  $10 \text{ k}\Omega$ ,

- Rupper = 2. 39 M $\Omega$ ,

- Cfil = 1  $\mu$ F,

One obtains the following voltage thresholds:

- Vtrip = 85 Vrms,

- VBO = 65 Vrms.

#### **Over Power Limit (NCP1239F)**

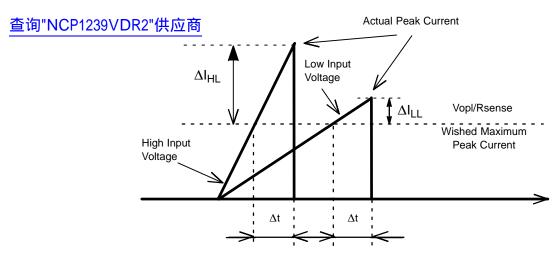

Overload conditions may push the converter to draw an excessive power (which generally increases versus the input voltage). One must avoid such a behavior:

a) not to have to dimension the converter for a power higher than the nominal one,

b) to meet SMPS specifications that often request the power not to exceed a given level.

In addition, it is not recommended to provide the output with more power than normally necessary. To the light of these statements, it becomes interesting to accurately limit the amount of power drawn from the AC line in fault conditions. The easiest way to do so consists of clamping the peak current since in a discontinuous mode flyback converter, the input power (Pin) can be calculated as follows:  $Pin = 1/2 * Lp * Ip_{pk}^{2} * fsw$ , where Lp is the primary inductor,  $Ip_{pk}$  is the inductor peak current and fsw is the switching frequency.

Practically, a sense resistor converts the primary current into a voltage that is compared to a voltage reference. When the voltage representative of the current exceeds the voltage reference, the controller turns off the power switch. The theoretical maximum peak current is then: Imax = Vocp/Rsense, where Vocp is the reference voltage (or overcurrent protection threshold) and Rsense is the sense resistor.

Unfortunately, the controller cannot turn off the power switch immediately when it detects that the current exceeds its maximum permissible level. Internal propagation delays differ the drive turn low. In addition, the power switch needs some time to turn off. Finally, the real current stop can be 250ns or more delayed. During this time, the current continues ramping up so that an overcurrent is obtained.

The propagation delay ( $\Delta t$ ) produces overcurrents ( $\Delta I_{LL}$  at low line,  $\Delta I_{HL}$  at high line in the figure) that are proportional to the input voltage. As a consequence, the actual maximum current and then the power limit gets higher when the AC line increases.

Figure 49.

I max =  $\frac{\text{Vocp}}{\text{Rsense}} + \frac{\text{Vin} \cdot \delta t}{\text{Lp}}$ , where Vin is the converter input voltage and  $\Delta t$  is the total delay in turning off the power switch.

The NCP1239 enables the compensation of the second term in the Imax equation for a precise limitation of the peak current. A current source  $(I_{pin9})$  proportional to the Pin 5 voltage flows out of Pin 9. Since Pin 5 receives a voltage proportional to the input voltage for brown–out detection,  $I_{pin9}$  is proportional to the input voltage too. An external resistor Rcomp can be connected between Pin 9 and the positive terminal of Rsense, so that Pin 9 monitors the following voltage:

$$V_{pin9} = [Rsense \cdot (lp + l_{pin9})] + (Rcomp \cdot l_{pin9})$$

I<sub>pin9</sub> being small compared to the inductor current, the Pin 9 voltage simplifies as follows:

$V_{pin9} = (Rsense \cdot Ip) + (Rcomp \cdot I_{pin9})$

$I_{pin9}$  is proportional to the Pin 5 voltage (80  $\mu$ A/V\*V<sub>pin5</sub> – see parameters specification table) and V<sub>pin5</sub> is a portion of the input voltage (V<sub>pin5</sub> = k<sub>BO</sub>\*Vin). Finally,

$$I_{pin9} = 80 \,\mu A / V \cdot k_{BO} \cdot Vin$$

The voltage  $V_{pin9}$  is compared to the internal reference Vocp. When  $V_{pin9}$  reaches Vocp, the corresponding threshold current (Ipth) is deducted from:

$VopI = (Rsense \cdot Ipth) + (Rcomp \cdot 80 \,\mu A/V \cdot k_{BO} \cdot Vin)$

Then,

$$lpth = \frac{Vopl - (Rcomp \cdot 80 \,\mu A/V \cdot k_{BO} \cdot Vin)}{Rsense}$$

Taking into account the overcurrent resulting from the propagation delays, the maximum current is finally:

$$I \max = \frac{Vocp}{Rsense} - \frac{Rcomp \cdot 80 \,\mu A/V \cdot kBO \cdot Vin}{Rsense} + \frac{Vin \cdot \delta t}{Lp}$$

Choosing Rcomp so that

$$\frac{\text{Rcomp} \cdot \text{SO} \, \mu\text{A}/\text{V} \cdot \text{RgO}}{\text{Rsense}} + \frac{\delta t}{\text{Lp}}$$

the current limit is made constant in the whole input voltage range (Imax = Vocp/Rsense).

As an example, let's assume that:

- the minimum input voltage for operation is 100 V =>  $k_{BO}=0.5/100=0.005$ ,

- Rsense is 0.25  $\Omega$ ,

- Lp=500 μH,

- The total propagation delays are  $\Delta t = 350$  ns,

Then, the Rcomp resistor should be:

$$\mathsf{Rcomp} = \frac{\delta t \cdot \mathsf{Rsense}}{80 \ \mu \cdot \mathsf{k}_{\mathsf{BO}} \cdot \mathsf{Lp}} = \frac{350 \ \mathsf{n} \cdot 0.25}{80 \ \mu \cdot 0.005 \cdot 500 \ \mathsf{m}} \approx 438 \ \Omega$$

An (averaged) portion of the input voltage is applied to the brown-out pin. A current source proportional to this voltage, flows through an external resistor Rcomp to form an offset proportional to the (average) input voltage. Rcomp should be selected so that the offset compensates the overcurrent sensed by the current sensing resistor Rsense.

#### Figure 50. NCP1239F

#### Maximum Duty Cycle Limitation (NCP1239V)

Pin 9 sources a 55  $\mu$ A current. By placing a resistor between this pin and ground, one builds a voltage that forces the maximum on–time. Practically the Pin 9 voltage is compared to the positive ramp of the internal oscillator and the power switch is allowed to be on, only when the ramp is below V<sub>pin9</sub>.

Then the maximum on-time is given by:

$$(ton)max = \frac{Cosc \cdot V_{pin9}}{Iosc}$$

where Cosc and Iosc are respectively the capacitor and the charging current of the oscillator.

$V_{pin9}$  being the product of the Pin 9 current by the Pin 9 resistance ( $R_{pin9}$  – external resistor connected to Pin 9), results in:

$(ton)max = \frac{Cosc \cdot IDmax}{losc} \cdot Rping$ , where  $I_{Dmax}$  is the Pin 9 current source.

One can deduct the maximum duty cycle (Dmax) by dividing by the period T:

$$Dmax = \frac{Cosc \cdot IDmax}{Iosc \cdot T} \cdot Rping = KDmax \cdot Rping$$

where

$$K_{Dmax} = \frac{Cosc \cdot I_{Dmax}}{Iosc \cdot T}$$

.

$K_{Dmax}$  is specified within the parameters' table. Please note that Cosc and Iosc are the internal capacitor and current (respectively), that set the switching period (T). Hence,

$\left[\left(\frac{\text{Cosc}}{\text{losc} \cdot T}\right)\right]$  is a constant and  $K_{\text{Dmax}}$  is independent of the

switching frequency.

In the NCP1239F, the maximum duty-cycle is fixed (80% typically).

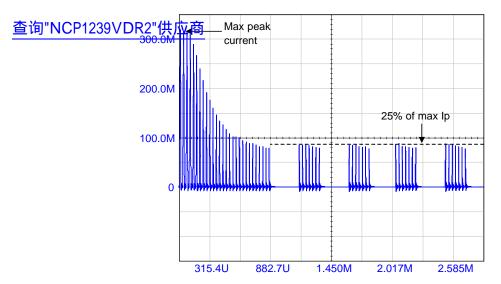

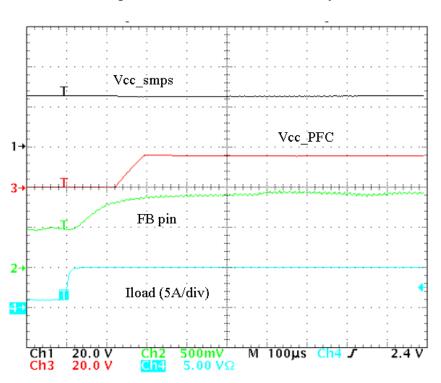

Soft\_Start 公司 NCB1339VDR2"供应商 during the Power On sequence (PON). As soon as V<sub>CC</sub> reaches 16.4 V, the current setpoint is gradually increased from nearly zero up to the maximum clamping level (e.g. 0.9 V/Rsense). This situation lasts a programmable time that is adjusted by the Pin 6 capacitor (7.5 ms typically with  $C_{pin6} = 390$  nF). Further to that time period, the current setpoint is blocked to 0.9 V/Rsense until the supply enters

regulation. The soft-start is also activated at each start of the active phase of fault burst operation. Every restart attempt is followed by a soft-start activation.

Generally speaking, the soft-start will be activated when V<sub>CC</sub> ramps up either from zero (fresh power-on sequence) or 6.9 V, the latch-off threshold after an overload detection (OVL) for instance. Figure 51 shows the soft-start behavior. The time scales are purposely shifted to offer a better zoom portion.

Soft-start is activated during a startup sequence or an OVL condition

## Internal Ramp Compensation

Ramp compensation is a known mean to cure sub-harmonic oscillations. These oscillations take place at half the switching frequency and occur only during Continuous Conduction Mode (CCM) with a duty-cycle greater than 50%. To lower the current loop gain, one usually injects between 50 and 100% of the inductor down-slope. Figure 52 depicts how internally the ramp is generated:

Inserting a resistor in series with the current sense information brings ramp compensation

Figure 52.

Ju the NCP1239, the rame features a swing of 3.2 V. Suppose we select a 65 kHz version. Over a 65 kHz frequency, it corresponds to a 130 mV/ms ramp. In our FLYBACK design, let's assume that our primary inductance Lp is 350 mH, and the SMPS delivers 12 V with a Np:Ns ratio of 1:0.1. The OFF time slope of the primary current is: (Vout + V(t) : NS

$\frac{(\text{Vout} + \text{Vf}) \cdot \frac{\text{Ns}}{\text{Np}}}{\text{Lp}} \text{ that is, 371 mA/ms or 37 mV/ms, once}$ projected over a 0.1  $\Omega$  Rsense for instance. If we select 75% of the down–slope as the required amount of ramp compensation, then we shall inject 27 mV/ms. Our internal compensation being of 208 mV/ms, the divider ratio (divratio) between R<sub>ramp</sub> and the 32 k $\Omega$  is 0.178. A few lines of algebra to determine R<sub>ramp</sub>: Rramp =  $\frac{19 \text{ k} \cdot \text{divratio}}{(1 - \text{divratio})} = 6.92 \text{ k}\Omega.$  The ramp is disabled during standby (i.e., when pfcON is low). This inhibition avoids that the ramp compensation modifies the setpoint above which the NCP1239 enables PFC.

# **Frequency Jittering**

Frequency jittering is a method used to soften the EMI signature by spreading the energy in the vicinity of the main switching component. NCP1239 offers a +3.5% deviation of the nominal switching frequency. The sweep saw-tooth is internally generated and modulates the clock up and down with a period depending on the Pin 6 capacitor (10 ms typically with 390 nF, 10 mS \* Cpin6 / 390 nF in general). Again, if one selects a 65 kHz version, the frequency will equal 65 kHz in the middle of the ripple and will increase as  $V_{pin6}$  rises or decrease as  $V_{pin6}$  ramps down. Figure 53 portrays the behavior we have adopted:

The V<sub>pin6</sub> ramp is used to introduce frequency jittering on the oscillator saw-tooth

Figure 53.

# Skipping Cycle Mode2"供应商 The NCP1239 automatically skips switching cycles when