www.ti.com

# BQ32000

SLUS900D-DECEMBER 2008-REVISED NOVEMBER 2010

WWW.DZSC.COM

# **REAL-TIME CLOCK (RTC)**

Check for Samples: BQ32000

APPLICATIONS

General consumer electronics

## FEATURES

- Automatic Switchover to Backup Supply

- I<sup>2</sup>C Interface Supports Serial Clock up to 400 kHz

- Uses 32.768-kHz Crystal With -63-ppm to +126-ppm Adjustment

- **Integrated Oscillator-Fail Detection**

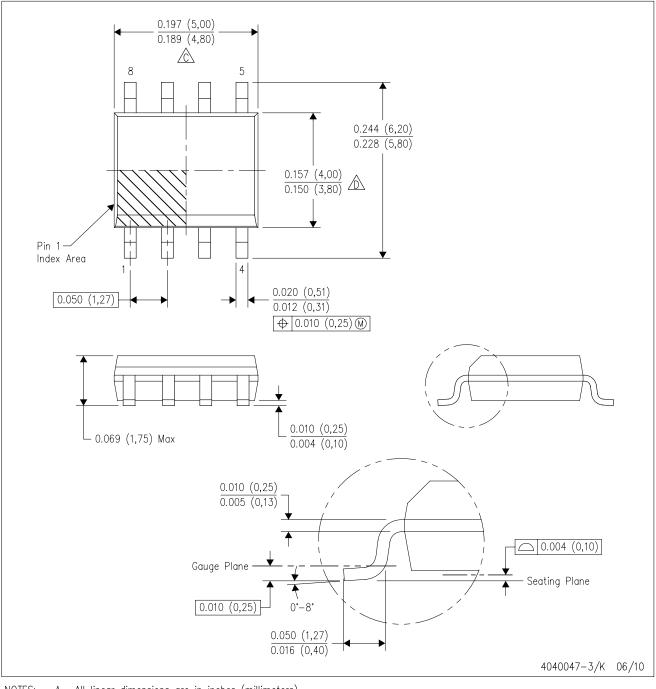

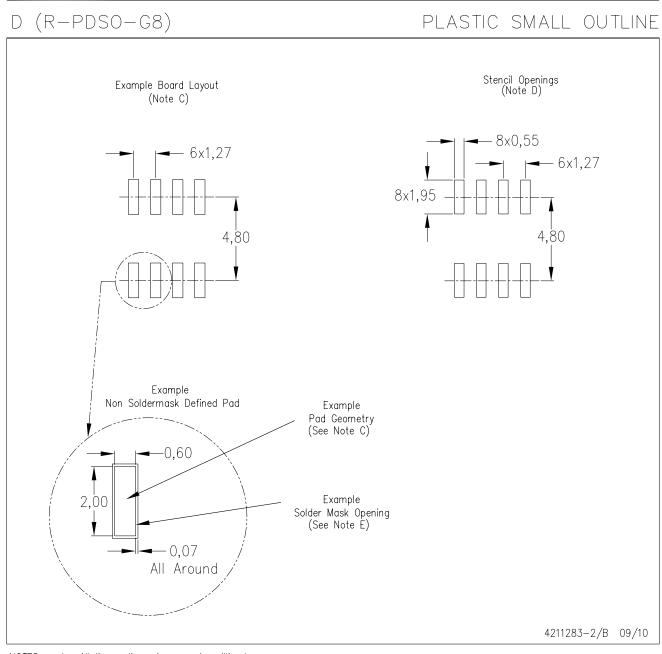

- 8-Pin SOIC Package

- -40°C to 85°C Ambient Operating Temperature

## DESCRIPTION

The bg32000 device is a compatible replacement for industry standard real-time clocks.

The bq32000 features an automatic backup supply with integrated trickle charger. The backup supply can be implemented using a capacitor or non-rechargeable battery. The bq32000 has a programmable calibration adjustment from -63 ppm to +126 ppm. The bq32000 registers include an OF (oscillator fail) flag indicating the status of the RTC oscillator, as well as a STOP bit that allows the host processor to disable the oscillator. The time registers are normally updated once per second, and all the registers are updated at the same time to prevent a timekeeping glitch. The bq32000 includes automatic leap-year compensation.

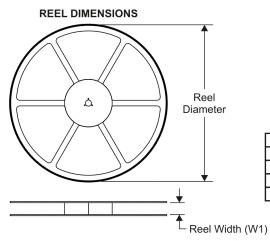

### ORDERING INFORMATION<sup>(1)</sup>

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> |              | ORDERABLE PART NUMBER | TOP-SIDE MARKING                 |  |

|----------------|------------------------|--------------|-----------------------|----------------------------------|--|

| –40°C to 85°C  | SOIC – D               | Reel of 2500 | BQ32000DR             | bq32000 xx y zzzz <sup>(3)</sup> |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI WWW.DZSC.COM web site at www.ti.com.

Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(3) xx = date code, y = assembly site, zzzz = lot code

df.dzsc.com

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SL整體BBCSEMBER 2008-REVISED NOVEMBER 2010

www.ti.com

####

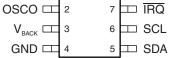

### **TERMINAL FUNCTIONS**

| NAME              | NO. | TYPE | DESCRIPTION                                       |

|-------------------|-----|------|---------------------------------------------------|

| Power and Grou    | nd  |      |                                                   |

| V <sub>CC</sub>   | 8   | -    | Main device power                                 |

| GND               | 4   | -    | Ground                                            |

| V <sub>BACK</sub> | 3   | -    | Backup device power                               |

| Serial Interface  |     |      |                                                   |

| SCL               | 6   | I    | I <sup>2</sup> C serial interface clock           |

| SDA               | 5   | I/O  | I <sup>2</sup> C serial data                      |

| Interrupt         |     |      |                                                   |

| IRQ               | 7   | 0    | Configurable interrupt output. Open-drain output. |

| Oscillator        |     |      |                                                   |

| OSCI              | 1   | -    | Oscillator input                                  |

| OSCO              | 2   | -    | Oscillator output                                 |

# <u>₩豐簡99Q32000"供应商</u>

SLUS900D – DECEMBER 2008 – REVISED NOVEMBER 2010

NOTE: All pullup resistors should be connected to  $V_{CC}$  such that no pullup is applied during backup supply operation.

SL#S9990 PES5MBER 2008: REVISED NOVEMBER 2010

STRUMENTS www.ti.com

EXAS

### **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

over operating free-air temperature range (unless otherwise noted)

|                  |                                        |                        | LIMIT                         | UNIT |

|------------------|----------------------------------------|------------------------|-------------------------------|------|

| V                | Input voltage                          | V <sub>CC</sub> to GND | –0.3 to 4                     | V    |

| V <sub>IN</sub>  | Input voltage                          | All other pins to GND  | –0.3 to V <sub>CC</sub> + 0.3 | V    |

| TJ               | Operating junction temperature         |                        | -40 to 150                    | °C   |

| T <sub>STG</sub> | Storage temperature range after reflow |                        | -60 to 150                    | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING CONDITIONS**

|                |                                        | MIN | TYP    | MAX | UNIT |

|----------------|----------------------------------------|-----|--------|-----|------|

| $V_{CC}$       | Supply voltage, V <sub>CC</sub> to GND | 3   |        | 3.6 | V    |

| T <sub>A</sub> | Operating free-air temperature         | -40 |        | 85  | °C   |

| f <sub>o</sub> | Crystal resonant frequency             | ••• | 32.768 |     | kHz  |

| $R_S$          | Crystal series resistance              |     |        | 40  | kΩ   |

| CL             | Crystal load capacitance               |     | 12     |     | pF   |

## **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                      | TEST CONDITION                                                       | MIN                 | TYP                | MAX                 | UNIT |

|-----------------|--------------------------------|----------------------------------------------------------------------|---------------------|--------------------|---------------------|------|

| Power           | Supply                         |                                                                      |                     |                    |                     |      |

| I <sub>CC</sub> | V <sub>CC</sub> supply current |                                                                      |                     | 100                |                     | μA   |

| V               | De elume europhicuelte en      | Operating                                                            | 1.4                 |                    | V <sub>CC</sub>     | V    |

| VBACK           | Backup supply voltage          | Switchover                                                           | 2.0                 |                    | V <sub>CC</sub>     | V    |

| IBACK           | Backup supply current          | $V_{CC} = 0 V$ , $V_{BAT} = 3V$ , Oscillator on, $T_A = 25^{\circ}C$ |                     | 1.2                | 1.5                 | μA   |

| Logic           | Level Inputs                   |                                                                      | <u>.</u>            |                    |                     |      |

| V <sub>IL</sub> | Input low voltage              |                                                                      |                     |                    | 0.3 V <sub>CC</sub> | V    |

| V <sub>IH</sub> | Input high voltage             |                                                                      | 0.7 V <sub>CC</sub> |                    |                     | V    |

| I <sub>IN</sub> | Input current                  | $0 V \le V_{IN} \le V_{CC}$                                          | -1                  |                    | 1                   | μA   |

| Logic           | Level Outputs                  |                                                                      | <u>.</u>            |                    |                     |      |

| V <sub>OL</sub> | Output low voltage             | I <sub>OL</sub> = 3 mA                                               |                     |                    | 0.4                 | V    |

| IL.             | Leakage current                |                                                                      | -1                  |                    | 1                   | μA   |

| Real-T          | ime Clock Characteristics      |                                                                      |                     |                    |                     |      |

|                 | Pre-calibration accuracy       | $V_{CC}$ = 3.3 V, $V_{BAT}$ = 3 V, Oscillator on, $T_A$ = 25°C       |                     | ±35 <sup>(1)</sup> |                     | ppm  |

(1) Typical accuracy is measured using reference board design and KDS DMX-26S surface-mount 32.768-kHz crystal. Variation in board design and crystal section results in different typical accuracy.

\*警衔曾Q32000"供应商

SLUS900D - DECEMBER 2008 - REVISED NOVEMBER 2010

### **DEVICE INFORMATION**

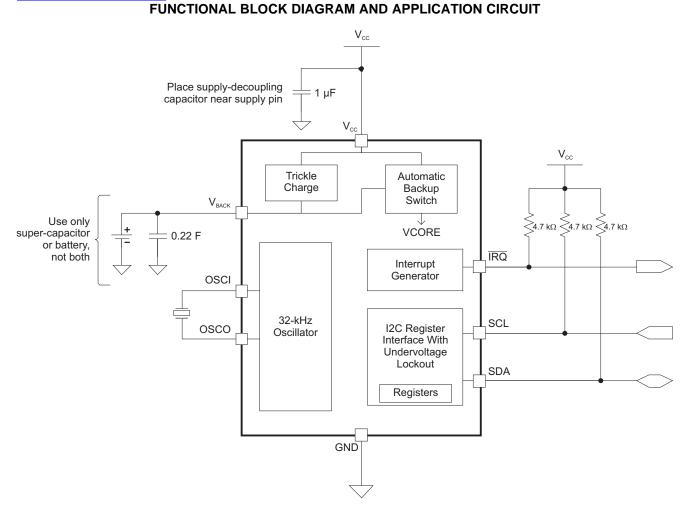

## **IRQ** Function

The IRQ pin of the bq32000 functions as a general-purpose output or a frequency test output. The function of IRQ is configurable in the device register space by setting the FT, FTF, and OUT bits. On initial power cycles, the OUT bit is set to one, and the FTF and FT bits are set to zero. On subsequent power-ups, with backup supply present, the OUT bit remains unchanged, and the FTF and FT bits are set to zero. When operating on backup supply, the IRQ pin function is unused. IRQ pullup resistor should be tied to  $V_{CC}$  to prevent IRQ operation when operating on backup supply. The effect of the calibration logic is not normally observable when IRQ is configured to output 1 Hz. The calibration logic functions by periodically adjusting the width of the 1-Hz clock. The calibration effect is observable only every eight or sixteen minutes, depending on the sign of the calibration.

| Figure 1. IRQ Pin Functional Diagra | am |

|-------------------------------------|----|

|-------------------------------------|----|

### Table 1. IRQ Function

| FT | OUT | FTF | <b>IRQ</b> STATE |

|----|-----|-----|------------------|

| 1  | Х   | 1   | 1 Hz             |

| 1  | Х   | 0   | 512 Hz           |

| 0  | 1   | Х   | 1                |

| 0  | 0   | Х   | 0                |

# SL经销码 DESEMBER 2008-REVISED NOVEMBER 2010

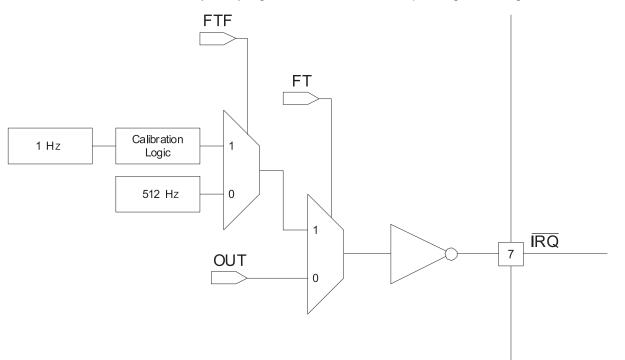

### V<sub>BACK</sub> Switchover

The bq32000 has an internal switchover circuit that causes the device to switch from main power supply to backup power supply when the voltage of the main supply pin V<sub>CC</sub> drops below a minimum threshold. The V<sub>BACK</sub> switchover circuit uses an internal reference voltage V<sub>REF</sub> derived from the on-chip bandgap reference; V<sub>REF</sub> is approximately 2.8 V. The device switches to the V<sub>BACK</sub> supply when V<sub>CC</sub> is less than the lesser of V<sub>BACK</sub> or V<sub>REF</sub>. Similarly, the device switches to the V<sub>CC</sub> supply when V<sub>CC</sub> is greater than either V<sub>BACK</sub> or V<sub>REF</sub>.

Some registers are reset to default values when the RTC switches from main power supply to backup power supply. Please see the register definitions to determine what register bits are effected by a backup switchover (effected bits have thier reset value (1/0) shown for 'Cycle', bits that are unchanged by backup are maked 'UC').

The time keeping registers can take up to 1 second to update after the RTC switches from backup power supply to main power supply.

#### SLUS900D – DECEMBER 2008 – REVISED NOVEMBER 2010

## \*查椅曾Q32000"供应商

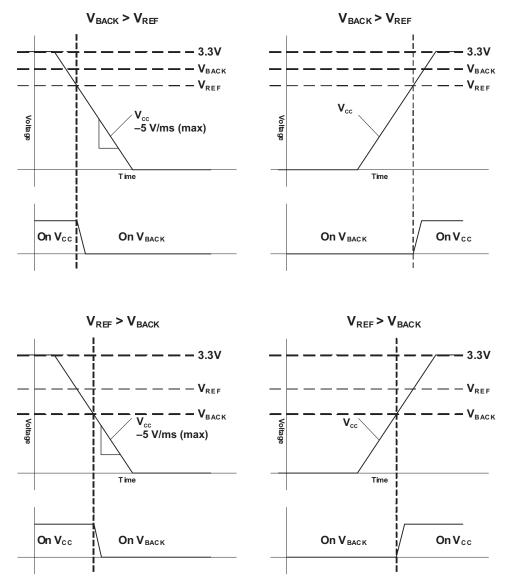

### Trickle Charge

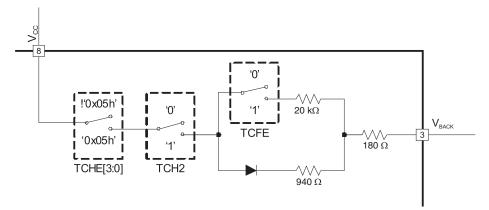

The bq32000 includes a trickle charge circuit to maintain the charge of the backup supply when a super capacitor is used. The trickle charge circuit is implemented as a series of three switches that are independently controlled by setting the TCHE[3:0], TCH2, and TCFE bits in the register space.

TCHE[3:0] must be written as 0x5h and TCH2 as 1 to close the trickle charge switches and enable charging of the backup supply from  $V_{CC}$ . Additionally, TCFE can be set to 1 to bypass the internal diode and boost the charge voltage of the backup supply. All trickle charge switches are opened when the device is initially powered on and each time the device switches from the main supply to the backup supply. The trickle charge circuit is intended for use with super capacitors; however, it can be used with a rechargeable battery under certain conditions. Care must be taken not to overcharge a rechargeable battery when enabling trickle charge. Follow all charging guidelines specific to the rechargeable battery or super capacitor when enabling trickle charge.

Figure 3. Trickle Charge Switch Functional Diagram

### I<sup>2</sup>C Serial Interface

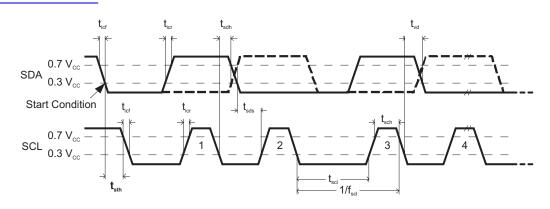

The I<sup>2</sup>C interface allows control and monitoring of the RTC by a microcontroller. I<sup>2</sup>C is a two-wire serial interface developed by Philips Semiconductor (see I<sup>2</sup>C-Bus Specification, Version 2.1, January 2000).

The bus consists of a data line (SDA) and a clock line (SCL) with off-chip pullup resistors. When the bus is idle, both SDA and SCL lines are pulled high.

A master device, usually a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer.

A slave device receives and/or transmits data on the bus under control of the master device. This device operates only as a slave device.

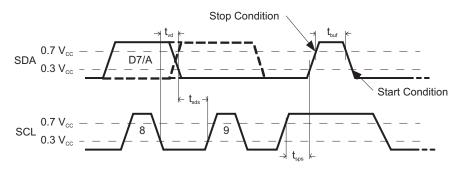

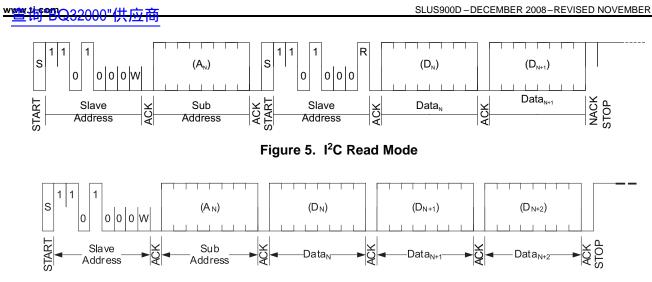

$I^2C$  communication is initiated by a master sending a start condition, a high-to-low transition on the SDA I/O while SCL is held high. After the start condition, the device address byte is sent, most-significant bit (MSB) first, including the data direction bit (R/W). After receiving a valid address byte, this device responds with an acknowledge, a low on the SDA I/O during the high of the acknowledge-related clock pulse. This device responds to the I<sup>2</sup>C slave address 11010000b for write commands and slave address 11010001b for read commands.

This device does not respond to the general call address.

A data byte follows the address acknowledge. If the R/W bit is low, the data is written from the master. If the R/W bit is high, the data from this device are the values read from the register previously selected by a write to the subaddress register. The data byte is followed by an acknowledge sent from this device. Data is output only if complete bytes are received and acknowledged.

A stop condition, which is a low-to-high transition on the SDA I/O while the SCL input is high, is sent by the master to terminate the transfer. A master device must wait at least 60  $\mu$ s after the RTC exits backup mode to generate a START condition.

Copyright © 2008–2010, Texas Instruments Incorporated

TEXAS INSTRUMENTS

## SL经销DBESSTOFF 2008-REVISED NOVEMBER 2010

Figure 4. I<sup>2</sup>C Timing Diagram

| Table 2 | 2. I <sup>2</sup> C | Timing |

|---------|---------------------|--------|

|---------|---------------------|--------|

|                        | DADAMETED                                                      | STAN | DARD M | ODE  | FAST M                                |     |     |      |

|------------------------|----------------------------------------------------------------|------|--------|------|---------------------------------------|-----|-----|------|

|                        | PARAMETER                                                      | MIN  | TYP    | MAX  | MIN                                   | TYP | MAX | UNIT |

| f <sub>scl</sub>       | I <sup>2</sup> C clock frequency                               | 0    |        | 100  | 0                                     |     | 400 | kHz  |

| t <sub>sch</sub>       | I <sup>2</sup> C clock high time                               | 4    |        |      | 0.6                                   |     |     | μS   |

| t <sub>scl</sub>       | I <sup>2</sup> C clock low time                                | 4.7  |        |      | 1.3                                   |     |     | μS   |

| t <sub>sp</sub>        | I <sup>2</sup> C spike time                                    | 0    |        | 50   | 0                                     |     | 50  | ns   |

| t <sub>sds</sub>       | I <sup>2</sup> C serial data setup time                        | 250  |        |      | 100                                   |     |     | ns   |

| t <sub>sdh</sub>       | I <sup>2</sup> C serial data hold time                         | 0    |        |      | 0                                     |     |     | ns   |

| t <sub>icr</sub>       | I <sup>2</sup> C input rise time                               |      |        | 1000 | 20 + 0.1C <sub>b</sub> <sup>(1)</sup> |     | 300 | ns   |

| t <sub>icf</sub>       | I <sup>2</sup> C input fall time                               |      |        | 300  | 20 + 0.1C <sub>b</sub> <sup>(1)</sup> |     | 300 | ns   |

| t <sub>ocf</sub>       | I <sup>2</sup> C output fall time                              |      |        | 300  | 20 + 0.1C <sub>b</sub> <sup>(1)</sup> |     | 300 | μS   |

| t <sub>buf</sub>       | I <sup>2</sup> C bus free time                                 | 4.7  |        |      | 1.3                                   |     |     | μS   |

| t <sub>sts</sub>       | I <sup>2</sup> C Start setup time                              | 4.7  |        |      | 0.6                                   |     |     | μs   |

| t <sub>sth</sub>       | I <sup>2</sup> C Start hold time                               | 4    |        |      | 0.6                                   |     |     | μS   |

| t <sub>sps</sub>       | I <sup>2</sup> C Stop setup time                               | 4    |        |      | 0.6                                   |     |     | μS   |

| t <sub>vd (data)</sub> | Valid data time (SCL low to SDA valid)                         |      |        | 1    |                                       |     | 1   | μS   |

| t <sub>vd (ack)</sub>  | Valid data time of ACK<br>(ACK signal from SCL low to SDA low) |      |        | 1    |                                       |     | 1   | μS   |

(1)  $C_b = total capacitance of one bus line in pF$

### SLUS900D - DECEMBER 2008 - REVISED NOVEMBER 2010

Figure 6. I<sup>2</sup>C Write Mode

## **Register Maps**

### **Table 3. Normal Registers**

| REGISTER | ADDRESS<br>(HEX) | REGISTER NAME | DESCRIPTION                           |

|----------|------------------|---------------|---------------------------------------|

| 0        | 0x00             | SECONDS       | Clock seconds and STOP bit            |

| 1        | 0x01             | MINUTES       | Clock minutes                         |

| 2        | 0x02             | CENT_HOURS    | Clock hours, century, and CENT_EN bit |

| 3        | 0x03             | DAY           | Clock day                             |

| 4        | 0x04             | DATE          | Clock date                            |

| 5        | 0x05             | MONTH         | Clock month                           |

| 6        | 0x06             | YEARS         | Clock years                           |

| 7        | 0x07             | CAL_CFG1      | Calibration and configuration         |

| 8        | 0x08             | TCH2          | Trickle charge enable                 |

| 9        | 0x09             | CFG2          | Configuration 2                       |

### **Table 4. Special Function Registers**

| REGISTER | ADDRESS<br>(HEX) | REGISTER NAME | DESCRIPTION               |

|----------|------------------|---------------|---------------------------|

| 32       | 0x20             | SF KEY 1      | Special function key 1    |

| 33       | 0x21             | SF KEY 2      | Special function key 2    |

| 34       | 0x22             | SFR           | Special function register |

## SL#S9990 PES5MBER 2008: REVISED NOVEMBER 2010

## **Normal Register Descriptions**

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    | l able 5.            | SECONDS   | Register |      |    |            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-----------|----------|------|----|------------|

| Address       | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |                      |           |          |      |    |            |

| Name          | SECON                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS                 |                      |           |          |      |    |            |

| Initial Value | 0XXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                | KXb                |                      |           |          |      |    |            |

| Description   | Clock se                                                                                                                                                                                                                                                                                                                                                                                                                                             | econds and ST      | OP bit               |           |          |      |    |            |

| D7            | D6                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D5                 | D4                   | D3        | D2       | D1   | D0 | BIT(S)     |

| STOP          |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10_SECOND 1_SECOND |                      |           |          |      |    |            |

| r/w           |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | r/w                |                      |           | r,       | /w   |    | Read/Write |

| 0             | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Х                  | Х                    | Х         | Х        | Х    | Х  | Initial    |

| UC            | UC                                                                                                                                                                                                                                                                                                                                                                                                                                                   | UC                 | UC                   | UC        | UC       | UC   | UC | Cycle      |

| STOP          | Oscillator stop. The STOP bit is used to force the oscillator to stop oscillating. STOP is set to 0 on initial application of power, on all subsequent power cycles STOP remains unchanged. On initial power application STOP can be written to 1 and then written to 0 to force start the oscillator.<br>0 Normal<br>1 Stop                                                                                                                         |                    |                      |           |          |      |    |            |

| 10_SECOND     | BCD of tens of seconds. The 10_SECOND bits are the BCD representation of the number of tens of seconds on the clock. Valid values are 0 to 5. If invalid data is written to 10_SECOND, the clock will update with invalid data in 10_SECOND until the counter rolls over; thereafter, the data in 10_SECOND is valid. Time keeping registers can take up to 1 second to update after the RTC switches from backup power supply to main power supply. |                    |                      |           |          |      |    |            |

| 1_SECOND      | BCD of seconds. The 1_SECOND bits are the BCD representation of the number of seconds on the clock. Valid values are 0 to 9. If invalid data is written to 1_SECOND, the clock will update with invalid data in 1_SECOND until the counter rolls over; thereafter, the data in 1_SECOND is valid. Time keeping registers can take up to 1 second to update after the RTC switches from backup power supply to main power supply.                     |                    |                      |           |          |      |    |            |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    | Table 6              | . MINUTES | Register |      |    |            |

| Address       | 0x01                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |                      |           |          |      |    |            |

| Name          | MINUTE                                                                                                                                                                                                                                                                                                                                                                                                                                               | ES                 |                      |           |          |      |    |            |

| Initial Value | 1XXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                               | КХb                |                      |           |          |      |    |            |

| Description   | Clock m                                                                                                                                                                                                                                                                                                                                                                                                                                              | inutes             |                      |           |          |      |    |            |

| D7            | D6                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D5                 | D4                   | D3        | D2       | D1   | D0 | BIT(S)     |

| OF            |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10_MINUTE          |                      |           | 1_MI     | NUTE |    | Name       |

| r/w           |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | r/w                |                      |           | r,       | /w   |    | Read/Write |

| 1             | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Х                  | Х                    | Х         | Х        | Х    | Х  | Initial    |

| 0             | UC                                                                                                                                                                                                                                                                                                                                                                                                                                                   | UC                 | UC                   | UC        | UC       | UC   | UC | Cycle      |

| OF            |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    | bit is a latched fla |           |          |      |    |            |

### Table 5. SECONDS Register

Oscillator fail flag. The OF bit is a latched flag indicating when the 32.768-kHz oscillator has dropped at least four consecutive pulses. The OF flag is always set on initial power-up, and it can be cleared through the serial interface. When OF is 0, no oscillator failure has been detected. When OF is 1, the oscillator fail detect circuit has detected at least four consecutive dropped pulses.

0 No failure detected

1 Failure detected

10\_MINUTE BCD of tens of minutes. The 10\_MINUTE bits are the BCD representation of the number of tens of minutes on the clock. Valid values are 0 to 5. If invalid data is written to 10\_MINUTE, the clock will update with invalid data in 10\_MINUTE until the counter rolls over; thereafter, the data in 10\_MINUTE is valid. Time keeping registers can take up to 1 second to update after the RTC switches from backup power supply to main power supply.

1\_MINUTE BCD of minutes. The 1\_MINUTE bits are the BCD representation of the number of minutes on the clock. Valid values are 0 to 9. If invalid data is written to 1\_MINUTE, the clock will update with invalid data in 1\_MINUTE until the counter rolls over; thereafter, the data in 1\_MINUTE is valid. Time keeping registers can take up to 1 second to update after the RTC switches from backup power supply to main power supply.

www.ti.com

#### SLUS900D - DECEMBER 2008 - REVISED NOVEMBER 2010

## "豐樹"的Q32000"供应商

### Table 7. CENT\_HOURS Register

| Address                    | 0x02                                                                           |                                                                                                          |                                                      |                                                                                                                  |                                                                             |                                                                         |                                                       |              |

|----------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------|--------------|

| Name                       | CENT_H                                                                         | IOURS                                                                                                    |                                                      |                                                                                                                  |                                                                             |                                                                         |                                                       |              |

| Initial Value              | XXXXXX                                                                         | XXb                                                                                                      |                                                      |                                                                                                                  |                                                                             |                                                                         |                                                       |              |

| Description                | Clock ho                                                                       | ours, century, a                                                                                         | nd CENT_EN b                                         | it                                                                                                               |                                                                             |                                                                         |                                                       |              |

| D7                         | D6                                                                             | D5                                                                                                       | D4                                                   | D3                                                                                                               | D2                                                                          | D1                                                                      | D0                                                    | BIT(S)       |

| CENT_EN                    | CENT                                                                           | 10_H                                                                                                     | IOUR                                                 |                                                                                                                  | 1_H                                                                         | OUR                                                                     |                                                       | Name         |

| r/w                        | r/w                                                                            | r                                                                                                        | /w                                                   |                                                                                                                  | r/                                                                          | /w                                                                      |                                                       | Read/Write   |

| Х                          | Х                                                                              | Х                                                                                                        | Х                                                    | Х                                                                                                                | Х                                                                           | Х                                                                       | Х                                                     | Initial      |

| UC                         | UC                                                                             | UC                                                                                                       | UC                                                   | UC                                                                                                               | UC                                                                          | UC                                                                      | UC                                                    | Cycle        |

| CENT_EN<br>CENT<br>10_HOUR | tracks the ce<br>0 Cen<br>1 Cen<br>Century. The<br>the year cou<br>CENT (1 for | ntury using the<br>tury disabled<br>tury enabled<br>CENT bit trac<br>nt rolls from 99<br>current century | ks the century v<br>to 00. Because<br>and 0 for next | the century tim<br>ENT_EN is set to<br>when century tim<br>the clock comp<br>century, or 0 for<br>a 10 HOUR bits | o 0, the clock igr<br>ekeeping is ena<br>liments the CEN<br>current century | bled. The CENT<br>bled. The clock<br>IT bit, the user<br>and 1 for next | bit.<br>toggles the Cl<br>can define the<br>century). | ENT bit when |

| 10_HOOK                    | the clock, in invalid data i                                                   | 24-hour format<br>n 10_HOUR ui                                                                           | . Valid values a<br>ntil the counter r               | re 0 to 2. If inval                                                                                              | id data is writter<br>fter, the data in                                     | n to 10_HOUR,<br>10_HOUR is va                                          | the clock will u<br>alid. Time keep                   |              |

| 1_HOUR                     | hour format.<br>1_HOUR unt                                                     | Valid values a<br>il the counter r                                                                       | re 0 to 9. If inval<br>olls over; therea             | JR bits are the E<br>lid data is writter<br>after, the data in<br>om backup pow                                  | n to 1_HOUR, th<br>1_HOUR is vali                                           | e clock will upd<br>d. Time keeping                                     | late with invalic<br>g registers can                  |              |

### Table 8. DAY Register

| Address       | 0x03     |           |    |    |    |    |    |        |  |  |  |

|---------------|----------|-----------|----|----|----|----|----|--------|--|--|--|

| Name          | DAY      |           |    |    |    |    |    |        |  |  |  |

| Initial Value | 00000X   | XXb       |    |    |    |    |    |        |  |  |  |

| Description   | Clock da | Clock day |    |    |    |    |    |        |  |  |  |

| D7            | De       | D5        | D4 | 50 | D2 | D1 | DO | BIT(S) |  |  |  |

| D7 | D6  | D5   | D4 | D3 | D2   | D1  | D0 | BIT(S)  |

|----|-----|------|----|----|------|-----|----|---------|

|    |     | RSVD |    |    | Name |     |    |         |

|    | r/w |      |    |    |      | r/w |    |         |

| 0  | 0   | 0    | 0  | 0  | Х    | Х   | Х  | Initial |

| 0  | 0   | 0    | 0  | 0  | UC   | UC  | UC | Cycle   |

RSVD DAY Reserved. The RSVD bits should always be written as 0.

BCD of the day of the week. The DAY bits are the BCD representation of the day of the week. Valid values are 1 to 7 and represent the days from Sunday to Saturday. DAY updates if set to 0 until the counter rolls over; thereafter, the data in DAY is valid. Time keeping registers can take up to 1 second to update after the RTC switches from backup power supply to main power supply.

- 1 Sunday

- 2 Monday

- 3 Tuesday

- 4 Wednesday

- 5 Thursday

- 6 Friday

- 7 Saturday

# SI 些 網 DE CESEMBER 2010

www.ti.com

### Table 9. DATE Register

| Address<br>Name<br>Initial Value<br>Description | 0x04<br>DATE<br>00XXXX<br>Clock da                             |                                                         |                                       |                                                              |                    |                  |                   |                |

|-------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------|---------------------------------------|--------------------------------------------------------------|--------------------|------------------|-------------------|----------------|

| D7                                              | D6                                                             | D5                                                      | D4                                    | D3                                                           | D2                 | D1               | D0                | BIT(S)         |

| RS                                              | VD                                                             | 10_[                                                    | DATE                                  |                                                              | 1_D                | ATE              |                   | Name           |

| r/                                              | Ŵ                                                              | r.                                                      |                                       |                                                              |                    |                  | Read/Write        |                |

| 0                                               | 0                                                              | Х                                                       | Х                                     | Х                                                            | Х                  | Х                | Х                 | Initial        |

| 0                                               | 0                                                              | UC                                                      | UC                                    | UC                                                           | UC                 | UC               | UC                | Cycle          |

| RSVD<br>10_DATE                                 | BCD of tens<br>3 <sup>(1)</sup> . If invalie<br>thereafter, th | of date. The 10<br>d data is writter<br>ne data in 10_D | to 10_DATE, th                        | the BCD repres<br>the clock will update<br>the keeping regis | ate with invalid o | data in 10_DATE  | E until the cou   |                |

| 1_DATE                                          | data is writte<br>data in 1_D/                                 | en to 1_DATE, f                                         | he clock will upo<br>ne keeping regis | ) representation<br>date with invalid<br>sters can take up   | data in 1_DATE     | until the counte | er rolls over; th | nereafter, the |

<sup>10</sup>\_DATE and 1\_DATE must form a valid date, 01 to 31, dependent on month and year. (1)

|               |                                          |                                  | Table 1                          | 0. MONTH F                       | legister                            |                                        |                               |                              |  |  |  |

|---------------|------------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------------------|----------------------------------------|-------------------------------|------------------------------|--|--|--|

| Address       | 0x05                                     |                                  |                                  |                                  |                                     |                                        |                               |                              |  |  |  |

| Name          | MONTH                                    | MONTH                            |                                  |                                  |                                     |                                        |                               |                              |  |  |  |

| Initial Value | 000XXX                                   | 000XXXXb                         |                                  |                                  |                                     |                                        |                               |                              |  |  |  |

| Description   | Clock m                                  | onth                             |                                  |                                  |                                     |                                        |                               |                              |  |  |  |

| D7            | D6                                       | D5                               | D4                               | D3                               | D2                                  | D1                                     | D0                            | BIT(S)                       |  |  |  |

|               | RSVD                                     |                                  | 10_MONTH                         |                                  | 1_M0                                | ЭNTH                                   |                               | Name                         |  |  |  |

|               | r/w                                      |                                  | r/w                              |                                  | r/                                  | /w                                     |                               | Read/Write                   |  |  |  |

| 0             | 0                                        | 0                                | Х                                | Х                                | Х                                   | Х                                      | х                             | Initial                      |  |  |  |

| 0             | 0                                        | 0                                | UC                               | UC                               | UC                                  | UC                                     | UC                            | Cycle                        |  |  |  |

| RSVD          | Reserved. T                              | he RSVD bits s                   | should always be                 | written as 0.                    |                                     |                                        |                               |                              |  |  |  |

| 10_MONTH      | BCD of tens<br>are 0 to 1 <sup>(1)</sup> | of month. The<br>If invalid data | 10_MONTH bits is written to 10_I | are the BCD re<br>MONTH, the clo | presentation of<br>ck will update w | the tens of mon<br>vith invalid data i | th on the clocl<br>n 10_MONTH | <. Valid values<br>until the |  |  |  |

counter rolls over; thereafter, the data in  $10\_MONTH$  is valid. BCD of month. The 1\_MONTH bits are the BCD representation of the month on the clock. Valid values are 0 to 9<sup>(1)</sup>. If 1\_MONTH

invalid data is written to 1\_MONTH, the clock will update with invalid data in 1\_MONTH until the counter rolls over; thereafter, the data in 1\_MONTH is valid.

(1) 10\_MONTH and 1\_MONTH must form a valid date, 01 to 12.

SLUS900D-DECEMBER 2008-REVISED NOVEMBER 2010

##

|               |                                   |                   | Table 1                              | 1. YEARS R                                                                   | egister          |                   |                    |                  |  |

|---------------|-----------------------------------|-------------------|--------------------------------------|------------------------------------------------------------------------------|------------------|-------------------|--------------------|------------------|--|

| Address       | 0x06                              |                   |                                      |                                                                              |                  |                   |                    |                  |  |

| Name          | YEARS                             |                   |                                      |                                                                              |                  |                   |                    |                  |  |

| Initial Value | XXXXXX                            | XXXXXXXb          |                                      |                                                                              |                  |                   |                    |                  |  |

| Description   | Clock ye                          | ear               |                                      |                                                                              |                  |                   |                    |                  |  |

| D7            | D6                                | D5                | D4                                   | D3                                                                           | D2               | D1                | D0                 | BIT(S)           |  |

|               | 10_Y                              | 'EAR              |                                      |                                                                              | 1_YE             | EAR               |                    | Name             |  |

|               | r/                                | w                 |                                      |                                                                              | r⁄v              | N                 |                    | Read/Write       |  |

| Х             | Х                                 | Х                 | Х                                    | Х                                                                            | Х                | Х                 | Х                  | Initial          |  |

| UC            | UC                                | UC                | UC                                   | UC                                                                           | UC               | UC                | UC                 | Cycle            |  |

| 10_YEAR       | to 9. If invali<br>thereafter, th | d data is written | to 10_YEAR, tl<br>EAR is valid. Tir  | re the BCD repre<br>he clock will upd<br>me keeping regis<br>n power supply. | ate with invalid | data in 10_YEA    | R until the cour   | nter rolls over; |  |

| 1_YEAR        | data is writte<br>data in 1_YE    | en to 1_YEAR, t   | he clock will up<br>ne keeping regis | D representation<br>date with invalid<br>sters can take up                   | data in 1_YEAR   | t until the count | er rolls over; the | ereafter, the    |  |

### Table 12. CAL\_CFG1 Register

|               |                                    |                        |                                        |                   | •              |                    |                 |                 |

|---------------|------------------------------------|------------------------|----------------------------------------|-------------------|----------------|--------------------|-----------------|-----------------|

| Address       | 0x07                               |                        |                                        |                   |                |                    |                 |                 |

| Name          | CAL_CF                             | G1                     |                                        |                   |                |                    |                 |                 |

| Initial Value | 100000                             | 00b                    |                                        |                   |                |                    |                 |                 |

| Description   | Calibrat                           | ion and control        |                                        |                   |                |                    |                 |                 |

| D7            | D6                                 | D5                     | D4                                     | D3                | D2             | D1                 | D0              | BIT(S)          |

| OUT           | FT                                 | S                      |                                        |                   | CAL            |                    |                 | Name            |

| r/w           | r/w                                | r/w                    |                                        |                   | r/w            |                    |                 | Read/Write      |

| 1             | 0                                  | 0                      | 0                                      | 0                 | 0              | 0                  | 0               | Initial         |

| UC            | UC                                 | UC                     | UC                                     | UC                | UC             | UC                 | UC              | Cycle           |

| FT            | 1 IRQ                              | the IRQ pin. T<br>able | is used to enable<br>he FTF bit in the |                   |                |                    |                 | quare wave is   |

| S             | slows the R <sup>-</sup><br>0 Slov |                        | determines the p<br>en the calibratior |                   |                | to the oscillator. | If S is 0, ther | the calibration |

| CAL           | Calibration.                       | The CAL bits a         | long with S deter                      | rmine the calibra | tion amount as | shown in Table     | 13.             |                 |

### Table 13. Calibration

| CAL (DEC) | S = 0                    | S = 1                    |

|-----------|--------------------------|--------------------------|

| 0         | +0 ppm                   | –0 ppm                   |

| 1         | +2 ppm                   | –4 ppm                   |

| N         | +N / 491520 (per minute) | –N / 245760 (per minute) |

| 30        | +61 ppm                  | –122 ppm                 |

| 31        | +63 ppm                  | –126 ppm                 |

Copyright © 2008–2010, Texas Instruments Incorporated

# SLUS THE DESTINGT AND THE ADDRESS AND AND A STATE AND

www.ti.com

### Table 14. TCH2 Register

| A                                                                                |                                                                                                         |                                                                                                     |                                                             |                                          |                          |                    |         |                                        |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------|--------------------------|--------------------|---------|----------------------------------------|

| Address                                                                          | 0x08                                                                                                    |                                                                                                     |                                                             |                                          |                          |                    |         |                                        |

| Name                                                                             | TCH2                                                                                                    |                                                                                                     |                                                             |                                          |                          |                    |         |                                        |

| Initial Value                                                                    | 1001000                                                                                                 | )0b                                                                                                 |                                                             |                                          |                          |                    |         |                                        |

| Description                                                                      | Trickle c                                                                                               | harge TCH2 co                                                                                       | ontrol                                                      |                                          |                          |                    |         |                                        |

| D7                                                                               | D6                                                                                                      | D5                                                                                                  | D4                                                          | D3                                       | D2                       | D1                 | D0      | BIT(S)                                 |

| RS                                                                               | VD                                                                                                      | TCH2                                                                                                |                                                             |                                          | RSVD                     |                    |         | Name                                   |

| r/                                                                               | w                                                                                                       | r/w                                                                                                 |                                                             |                                          | r/w                      |                    |         | Read/Write                             |

| 1                                                                                | 0                                                                                                       | 0                                                                                                   | 1                                                           | 0                                        | 0                        | 0                  | 0       | Initial                                |

| UC                                                                               | 0                                                                                                       | 0                                                                                                   | 1                                                           | UC                                       | UC                       | UC                 | UC      | Cycle                                  |

| RSVD                                                                             | Reserved. T                                                                                             | he RSVD bits s                                                                                      | hould always be                                             | e written as 0.                          |                          |                    |         |                                        |

| TCH2                                                                             | charge switc<br>TCH2 is 1, th                                                                           | hes must be clo<br>nen the TCH2 s                                                                   |                                                             | termines if the in<br>r trickle charging |                          |                    |         |                                        |

|                                                                                  | 0 Ope<br>1 Clos                                                                                         |                                                                                                     |                                                             |                                          |                          |                    |         |                                        |

|                                                                                  | 1 0100                                                                                                  |                                                                                                     |                                                             |                                          |                          |                    |         |                                        |

|                                                                                  |                                                                                                         |                                                                                                     |                                                             |                                          |                          |                    |         |                                        |

|                                                                                  |                                                                                                         |                                                                                                     | Table                                                       | 15. CFG2 Re                              | egister                  |                    |         |                                        |

| Address                                                                          | 0x09                                                                                                    |                                                                                                     | Table                                                       | 15. CFG2 Re                              | egister                  |                    |         |                                        |

|                                                                                  | CFG2                                                                                                    |                                                                                                     | Table                                                       | 15. CFG2 Re                              | egister                  |                    |         |                                        |

| Name                                                                             |                                                                                                         | 10b                                                                                                 | Table                                                       | 15. CFG2 Re                              | egister                  |                    |         |                                        |

| Name<br>Initial Value                                                            | CFG2                                                                                                    |                                                                                                     | Table                                                       | 15. CFG2 Re                              | egister                  |                    |         |                                        |

| Name<br>Initial Value                                                            | CFG2<br>1010101                                                                                         |                                                                                                     | Table                                                       | 15. CFG2 Re                              | egister<br>D2            | D1                 | D0      | BIT(S)                                 |

| Name<br>Initial Value<br>Description                                             | CFG2<br>1010101<br>Configur                                                                             | ration 2<br>D5                                                                                      |                                                             |                                          |                          |                    | D0      | BIT(S)<br>Name                         |

| Name<br>Initial Value<br>Description<br>D7                                       | CFG2<br>1010101<br>Configur<br>D6                                                                       | D5                                                                                                  | D4                                                          |                                          | D2<br>TC                 |                    | D0      |                                        |

| Name<br>Initial Value<br>Description<br>D7<br>RSVD                               | CFG2<br>1010101<br>Configur<br>D6<br>TCFE                                                               | D5                                                                                                  | D4<br>SVD                                                   |                                          | D2<br>TC                 | HE                 | D0<br>0 | Name                                   |

| Description<br>D7<br>RSVD<br>r/w                                                 | CFG2<br>1010101<br>Configur<br>D6<br>TCFE<br>r/w                                                        | ration 2<br>D5<br>RS<br>r/                                                                          | D4<br>SVD<br>W                                              | D3                                       | D2<br>TC<br>r/           | HE<br>W            |         | Name<br>Read/Write                     |

| Name<br>Initial Value<br>Description<br>D7<br>RSVD<br>r/w<br>1<br>1              | CFG2<br>1010101<br>Configur<br>D6<br>TCFE<br>r/w<br>0<br>0                                              | ration 2<br>D5<br>RS<br>r/<br>1<br>UC                                                               | D4<br>SVD<br>/w<br>0                                        | D3<br>1<br>1                             | D2<br>TC<br>r/<br>0      | HE<br>w<br>1       | 0       | Name<br>Read/Write<br>Initial          |

| Name<br>Initial Value<br>Description<br>D7<br>RSVD<br>r/w<br>1<br>1<br>RSVD      | CFG2<br>1010101<br>Configur<br>D6<br>TCFE<br>r/w<br>0<br>0<br>0<br>Reserved. T<br>Trickle charg         | ration 2<br>D5<br>RS<br>r/<br>1<br>UC<br>he RSVD bits s                                             | D4<br>SVD<br>/w<br>UC<br>hould always be<br>The TCFE bit is | D3<br>1<br>1                             | D2<br>TC<br>r/<br>0<br>0 | HE<br>/w<br>1<br>1 | 0       | Name<br>Read/Write<br>Initial<br>Cycle |

| Name<br>Initial Value<br>Description<br>D7<br>RSVD<br>r/w<br>1<br>1<br>1<br>RSVD | CFG2<br>1010101<br>Configur<br>D6<br>TCFE<br>r/w<br>0<br>0<br>0<br>Reserved. T<br>Trickle charg         | ration 2<br>D5<br>RS<br>r/<br>1<br>UC<br>he RSVD bits s<br>ge FET bypass.<br>is 1, the FET is       | D4<br>SVD<br>/w<br>UC<br>hould always be<br>The TCFE bit is | D3<br>1<br>1<br>written as 0.            | D2<br>TC<br>r/<br>0<br>0 | HE<br>/w<br>1<br>1 | 0       | Name<br>Read/Write<br>Initial<br>Cycle |

| Name<br>Initial Value<br>Description<br>D7<br>RSVD<br>r/w<br>1                   | CFG2<br>1010101<br>Configur<br>D6<br>TCFE<br>r/w<br>0<br>0<br>Reserved. T<br>Trickle charg<br>When TCFE | ration 2<br>D5<br>RS<br>r/<br>1<br>UC<br>he RSVD bits s<br>ge FET bypass.<br>is 1, the FET is<br>en | D4<br>SVD<br>/w<br>UC<br>hould always be<br>The TCFE bit is | D3<br>1<br>1<br>written as 0.            | D2<br>TC<br>r/<br>0<br>0 | HE<br>/w<br>1<br>1 | 0       | Name<br>Read/Write<br>Initial<br>Cycle |

SLUS900D-DECEMBER 2008-REVISED NOVEMBER 2010

#### ₩警**拾92000**"供应商

### **Special Function Registers**

### Table 16. SF KEY 1 Register

| Address       | 0x20                   |

|---------------|------------------------|

| Name          | SF KEY 1               |

| Initial Value | 0000000b               |

| Description   | Special function key 1 |

| D7 | D6        | D5 | D4 | D3 | D2 | D1 | D0 | BIT(S)     |  |  |

|----|-----------|----|----|----|----|----|----|------------|--|--|

|    | SF KEY B1 |    |    |    |    |    |    |            |  |  |

|    |           |    | r, | /w |    |    |    | Read/Write |  |  |

| 0  | 0         | 0  | 0  | 0  | 0  | 0  | 0  | Initial    |  |  |

| 0  | 0         | 0  | 0  | 0  | 0  | 0  | 0  | Cycle      |  |  |

SF KEY B1

Special function access key byte 1. Reads as 0x00, and key is 0x5E.

The SF KEY 1 and SF KEY 2 registers are used to enable access to the main special function register (SFR). Access to SFR is granted only after the special function keys are written sequentially to SF KEY 1 and SF KEY 2. Each write to the SFR must be preceded by writing the SF keys to the SF key registers, in order, SF KEY 1 then SF KEY 2.

### Table 17. SF KEY 2 Register

| Address       | 0x21    | 0x21           |      |       |    |    |    |            |  |  |  |

|---------------|---------|----------------|------|-------|----|----|----|------------|--|--|--|

| Name          | SF KEY  | SF KEY 2       |      |       |    |    |    |            |  |  |  |

| Initial Value | 000000  | 0000000b       |      |       |    |    |    |            |  |  |  |

| Description   | Special | function key 2 |      |       |    |    |    |            |  |  |  |

| D7            | D6      | D5             | D4   | D3    | D2 | D1 | D0 | BIT(S)     |  |  |  |

|               |         |                | SF K | CEY 2 |    |    |    | Name       |  |  |  |

|               |         |                | r/   | /w    |    |    |    | Read/Write |  |  |  |

| 0             | 0       | 0              | 0    | 0     | 0  | 0  | 0  | Initial    |  |  |  |

| 0             | 0       | 0              | 0    | 0     | 0  | 0  | 0  | Cycle      |  |  |  |

SF KEY 2

Special function access key byte 2. Reads as 0x00, and key is 0xC7.

The SF KEY 1 and SF KEY 2 registers are used to enable access to the main special function register (SFR). Access to SFR is granted only after the special function keys are written sequentially to SF KEY 1 and SF KEY 2. Each write to the SFR must be preceded by writing the SF keys to the SF key registers, in order, SF KEY 1 then SF KEY 2.

#### Table 18. SFR Register

|               |         |                             |    |    | 0  |    |    |         |  |  |  |

|---------------|---------|-----------------------------|----|----|----|----|----|---------|--|--|--|

| Address       | 0x22    |                             |    |    |    |    |    |         |  |  |  |