# Ultra-Small, Low-Power, 16-Bit Analog-to-Digital Converter with Internal Reference

Check for Samples: ADS1113 ADS1114 ADS1115

### **FEATURES**

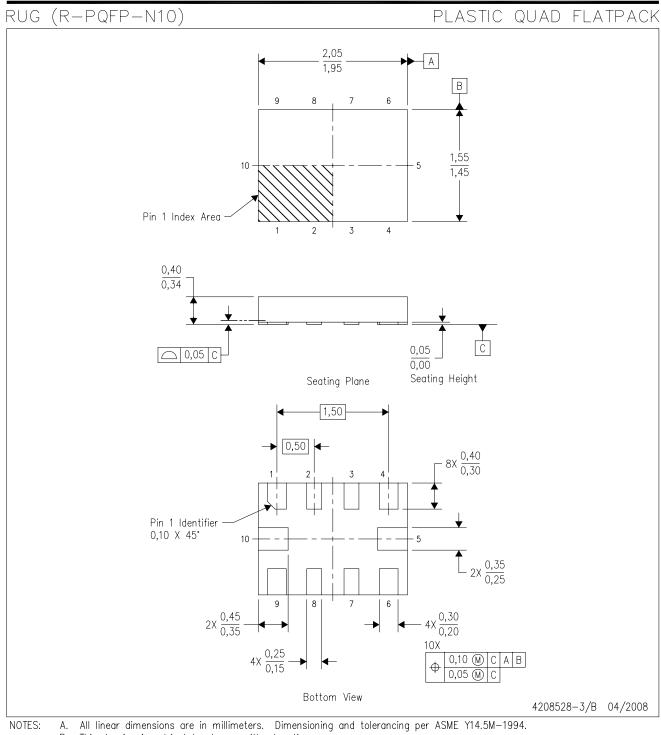

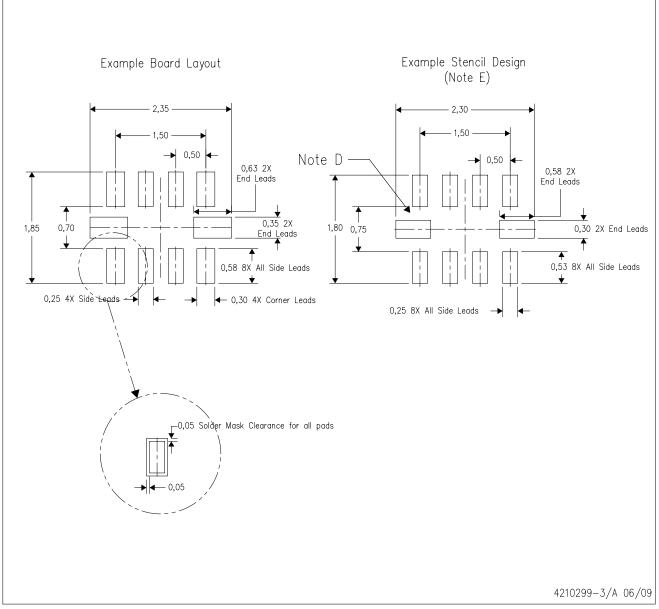

- ULTRA-SMALL QFN PACKAGE: 2mm × 1,5mm × 0,4mm

- WIDE SUPPLY RANGE: 2.0V to 5.5V

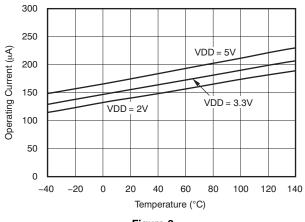

- LOW CURRENT CONSUMPTION: Continuous Mode: Only 150µA Single-Shot Mode: Auto Shut-Down

- PROGRAMMABLE DATA RATE:

8SPS to 860SPS

- INTERNAL LOW-DRIFT VOLTAGE REFERENCE

- INTERNAL OSCILLATOR

- INTERNAL PGA

- I<sup>2</sup>C <sup>™</sup> INTERFACE: Pin-Selectable Addresses

- FOUR SINGLE-ENDED OR TWO DIFFERENTIAL INPUTS (ADS1115)

- PROGRAMMABLE COMPARATOR (ADS1114 and ADS1115)

- OPERATING TEMPERATURE: –40°C to +140°C

### **APPLICATIONS**

- PORTABLE INSTRUMENTATION

- CONSUMER GOODS

- BATTERY MONITORING

- TEMPERATURE MEASUREMENT

- FACTORY AUTOMATION AND PROCESS CONTROLS

### DESCRIPTION

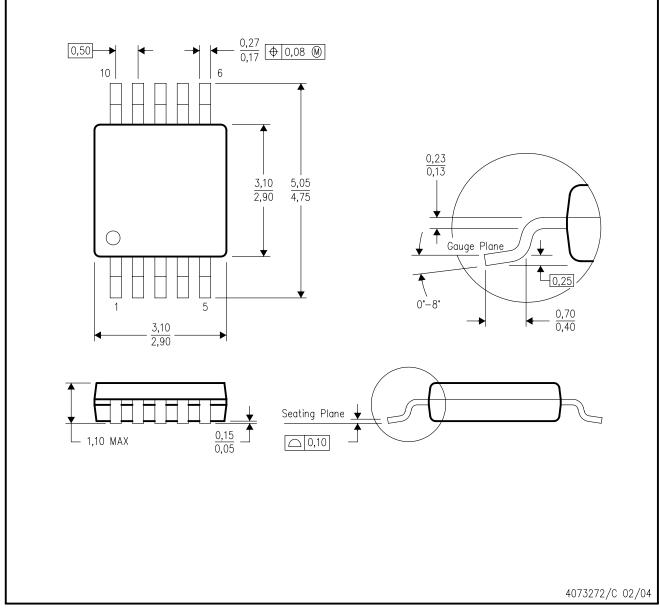

The ADS1113, ADS1114, and ADS1115 are precision analog-to-digital converters (ADCs) with 16 bits of resolution offered in an ultra-small, leadless QFN-10 package or an MSOP-10 package. The ADS1113/4/5 are designed with precision, power, and ease of implementation in mind. The ADS1113/4/5 feature an onboard reference and oscillator. Data are transferred via an I<sup>2</sup>C-compatible serial interface; four I<sup>2</sup>C slave addresses can be selected. The ADS1113/4/5 operate from a single power supply ranging from 2.0V to 5.5V.

The ADS1113/4/5 can perform conversions at rates up to 860 samples per second (SPS). An onboard PGA is available on the ADS1114 and ADS1115 that offers input ranges from the supply to as low as  $\pm 256$  mV, allowing both large and small signals to be measured with high resolution. The ADS1115 also features an input multiplexer (MUX) that provides two differential or four single-ended inputs.

The ADS1113/4/5 operate either in continuous conversion mode or a single-shot mode that automatically powers down after a conversion and greatly reduces current consumption during idle periods. The ADS1113/4/5 are specified from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. I2C is a trademark of NXP Semiconductors.

All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Inscruments standard warranty. Production processing does not recessarily include testing of all parameters.

df.dzsc.com

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **ORDERING INFORMATION**

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### ABSOLUTE MAXIMUM RATINGS (1)

|                                          | ADS1113, ADS1114, ADS1115 | UNIT |

|------------------------------------------|---------------------------|------|

| VDD to GND                               | -0.3 to +5.5              | V    |

| Analog input current                     | 100, momentary            | mA   |

| Analog input current                     | 10, continuous            | mA   |

| Analog input voltage to GND              | -0.3 to VDD + 0.3         | V    |

| SDA, SCL, ADDR, ALERT/RDY voltage to GND | -0.5 to +5.5              | V    |

| Maximum junction temperature             | +150                      | °C   |

| Operating temperature range              | -40 to +140               | °C   |

| Storage temperature range                | -60 to +150               | °C   |

(1) Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### **PRODUCT FAMILY**

| DEVICE  | PACKAGE<br>DESIGNATOR<br>MSOP/QFN | RESOLUTION<br>(Bits) | MAXIMUM SAMPLE<br>RATE (SPS) | COMPARATOR | PGA | INPUT CHANNELS<br>(Differential/<br>Single-Ended) |

|---------|-----------------------------------|----------------------|------------------------------|------------|-----|---------------------------------------------------|

| ADS1113 | BROI/N6J                          | 16                   | 860                          | No         | No  | 1/1                                               |

| ADS1114 | BRNI/N5J                          | 16                   | 860                          | Yes        | Yes | 1/1                                               |

| ADS1115 | BOGI/N4J                          | 16                   | 860                          | Yes        | Yes | 2/4                                               |

| ADS1013 | BRMI/N9J                          | 12                   | 3300                         | No         | No  | 1/1                                               |

| ADS1014 | BRQI/N8J                          | 12                   | 3300                         | Yes        | Yes | 1/1                                               |

| ADS1015 | BRPI/N7J                          | 12                   | 3300                         | Yes        | Yes | 2/4                                               |

# <u>₩豐铈乳D\$1113IRUCT"供应商</u>

#### **ELECTRICAL CHARACTERISTICS**

All specifications at  $-40^{\circ}$ C to  $+125^{\circ}$ C, VDD = 3.3V, and Full-Scale (FS) =  $\pm 2.048$ V, unless otherwise noted. Typical values are at  $+25^{\circ}$ C.

|                                         |                                                        | ADS1113, ADS1114, ADS1115 |                                            |         |        |

|-----------------------------------------|--------------------------------------------------------|---------------------------|--------------------------------------------|---------|--------|

| PARAMETER                               | TEST CONDITIONS                                        | MIN                       | ТҮР                                        | MAX     | UNIT   |

| ANALOG INPUT                            |                                                        |                           |                                            |         |        |

| Full-scale input voltage <sup>(1)</sup> | $V_{IN} = (AIN_P) - (AIN_N)$                           |                           | ±4.096/PGA                                 |         | V      |

| Analog input voltage                    | AIN <sub>P</sub> or AIN <sub>N</sub> to GND            | GND                       |                                            | VDD     | V      |

| Differential input impedance            |                                                        |                           | See Table 2                                |         |        |

|                                         | $FS = \pm 6.144V^{(1)}$                                |                           | 10                                         |         | MΩ     |

| Common mode input impedance             | $FS = \pm 4.096V^{(1)}$ , $\pm 2.048V$                 |                           | 6                                          |         | MΩ     |

| Common-mode input impedance             | $FS = \pm 1.024V$                                      |                           | 3                                          |         | MΩ     |

|                                         | FS = ±0.512V, ±0.256V                                  |                           | 100                                        |         | MΩ     |

| SYSTEM PERFORMANCE                      |                                                        | ·                         |                                            |         |        |

| Resolution                              | No missing codes                                       | 16                        |                                            |         | Bits   |

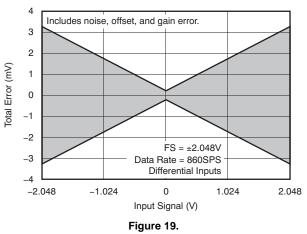

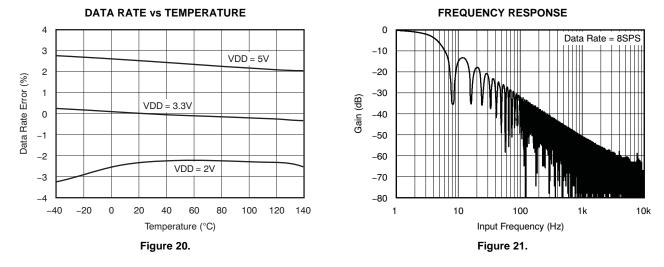

| Data rate (DR)                          |                                                        |                           | 8, 16, 32,<br>64, 128,<br>250, 475,<br>860 |         | SPS    |

| Data rate variation                     | All data rates                                         | -10                       |                                            | 10      | %      |

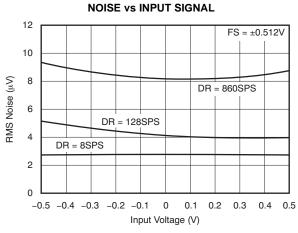

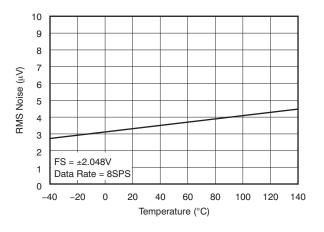

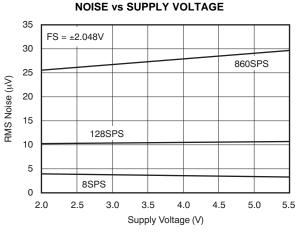

| Output noise                            |                                                        | See T                     | ypical Characte                            | ristics |        |

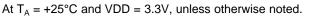

| Integral nonlinearity                   | DR = 8SPS, FS = $\pm 2.048V$ , best fit <sup>(2)</sup> |                           |                                            | 1       | LSB    |

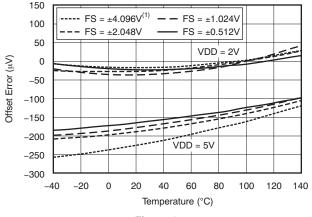

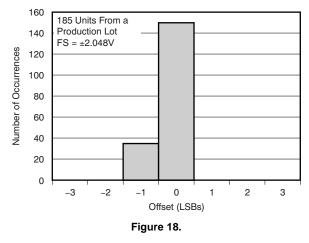

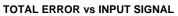

|                                         | FS = ±2.048V, differential inputs                      |                           | ±1                                         | ±3      | LSB    |

| Offset error                            | FS = ±2.048V, single-ended inputs                      |                           | ±3                                         |         | LSB    |

| Offset drift                            | FS = ±2.048V                                           |                           | 0.005                                      |         | LSB/°C |

| Offset power-supply rejection           | FS = ±2.048V                                           |                           | 1                                          |         | LSB/V  |

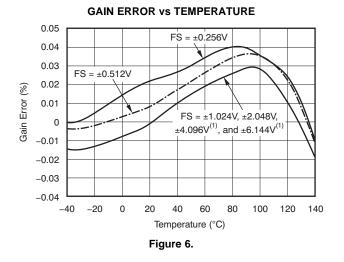

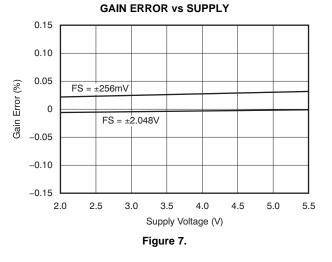

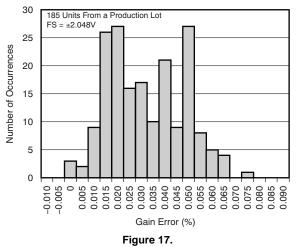

| Gain error <sup>(3)</sup>               | FS = ±2.048V at 25°C                                   |                           | 0.01                                       | 0.15    | %      |

|                                         | FS = ±0.256V                                           |                           | 7                                          |         | ppm/°C |

| Gain drift <sup>(3)</sup>               | FS = ±2.048V                                           |                           | 5                                          | 40      | ppm/°C |

|                                         | $FS = \pm 6.144V^{(1)}$                                |                           | 5                                          |         | ppm/°C |

| Gain power-supply rejection             |                                                        |                           | 80                                         |         | ppm/V  |

| PGA gain match <sup>(3)</sup>           | Match between any two PGA gains                        |                           | 0.02                                       | 0.1     | %      |

| Gain match                              | Match between any two inputs                           |                           | 0.05                                       | 0.1     | %      |

| Offset match                            | Match between any two inputs                           |                           | 3                                          |         | LSB    |

|                                         | At dc and FS = $\pm 0.256V$                            |                           | 105                                        |         | dB     |

|                                         | At dc and FS = $\pm 2.048V$                            |                           | 100                                        |         | dB     |

| Common-mode rejection                   | At dc and FS = $\pm 6.144V^{(1)}$                      |                           | 90                                         |         | dB     |

|                                         | $f_{CM} = 60Hz, DR = 8SPS$                             |                           | 105                                        |         | dB     |

|                                         | $f_{CM} = 50Hz, DR = 8SPS$                             |                           | 105                                        |         | dB     |

| DIGITAL INPUT/OUTPUT                    |                                                        |                           |                                            |         |        |

| Logic level                             |                                                        |                           |                                            |         |        |

| V <sub>IH</sub>                         |                                                        | 0.7VDD                    |                                            | 5.5     | V      |

| VIL                                     |                                                        | GND – 0.5                 |                                            | 0.3VDD  | V      |

| V <sub>OL</sub>                         | I <sub>OL</sub> = 3mA                                  | GND                       | 0.15                                       | 0.4     | V      |

| Input leakage                           |                                                        |                           |                                            |         |        |

| I <sub>H</sub>                          | V <sub>IH</sub> = 5.5V                                 |                           |                                            | 10      | μA     |

| ۱                                       | V <sub>IL</sub> = GND                                  | 10                        |                                            |         | μA     |

(1) This parameter expresses the full-scale range of the ADC scaling. In no event should more than VDD + 0.3V be applied to this device.

(2) 99% of full-scale.

(3) Includes all errors from onboard PGA and reference.

www.ti.com

### **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $-40^{\circ}$ C to  $+125^{\circ}$ C, VDD = 3.3V, and Full-Scale (FS) =  $\pm 2.048$ V, unless otherwise noted. Typical values are at  $+25^{\circ}$ C.

|                           |                                | ADS111 | ADS1113, ADS1114, ADS1115 |      |      |

|---------------------------|--------------------------------|--------|---------------------------|------|------|

| PARAMETER                 | TEST CONDITIONS                | MIN    | TYP                       | MAX  | UNIT |

| POWER-SUPPLY REQUIREMENTS | S                              |        |                           |      | r    |

| Power-supply voltage      |                                | 2      |                           | 5.5  | V    |

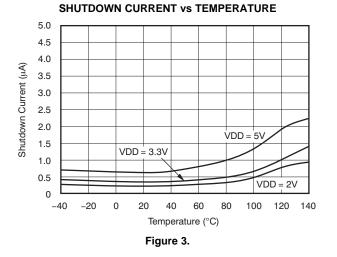

|                           | Power-down current at 25°C     |        | 0.5                       | 2    | μA   |

|                           | Power-down current up to 125°C |        |                           | 5    | μA   |

| Supply current            | Operating current at 25°C      |        | 150                       | 200  | μA   |

|                           | Operating current up to 125°C  |        |                           | 300  | μA   |

|                           | VDD = 5.0V                     |        | 0.9                       |      | mW   |

| Power dissipation         | VDD = 3.3V                     |        | 0.5                       |      | mW   |

|                           | VDD = 2.0V                     |        | 0.3                       |      | mW   |

| TEMPERATURE               |                                |        |                           |      | r    |

| Storage temperature       |                                | -60    |                           | +150 | °C   |

| Operating temperature     |                                | -40    |                           | +140 | °C   |

| Specified temperature     |                                | -40    |                           | +125 | °C   |

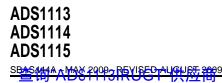

### **PIN CONFIGURATIONS**

#### **PIN DESCRIPTIONS**

|       | DEVICE ANALOG/<br>DIGITAL<br>INPUT/<br>ADS1113 ADS1114 ADS1115 OUTPUT |           |           |                |                                                                                           |

|-------|-----------------------------------------------------------------------|-----------|-----------|----------------|-------------------------------------------------------------------------------------------|

| PIN # |                                                                       |           | INPUT/    | DESCRIPTION    |                                                                                           |

| 1     | ADDR                                                                  | ADDR      | ADDR      | Digital Input  | I <sup>2</sup> C slave address select                                                     |

| 2     | NC <sup>(1)</sup>                                                     | ALERT/RDY | ALERT/RDY | Digital Output | Digital comparator output or conversion ready (NC for ADS1113)                            |

| 3     | GND                                                                   | GND       | GND       | Analog         | Ground                                                                                    |

| 4     | AIN0                                                                  | AIN0      | AIN0      | Analog Input   | Differential channel 1: Positive input or single-ended channel 1 input                    |

| 5     | AIN1                                                                  | AIN1      | AIN1      | Analog Input   | Differential channel 1: Negative input or single-ended channel 2 input                    |

| 6     | NC                                                                    | NC        | AIN2      | Analog Input   | Differential channel 2: Positive input or single-ended channel 3 input (NC for ADS1113/4) |

| 7     | NC                                                                    | NC        | AIN3      | Analog Input   | Differential channel 2: Negative input or single-ended channel 4 input (NC for ADS1113/4) |

| 8     | VDD                                                                   | VDD       | VDD       | Analog         | Power supply: 2.0V to 5.5V                                                                |

| 9     | SDA                                                                   | SDA       | SDA       | Digital I/O    | Serial data: Transmits and receives data                                                  |

| 10    | SCL                                                                   | SCL       | SCL       | Digital Input  | Serial clock input: Clocks data on SDA                                                    |

(1) NC pins may be left floating or tied to ground.

Copyright © 2009, Texas Instruments Incorporated

# <u>₩營物究D\$1113IRUGT"供应商</u>

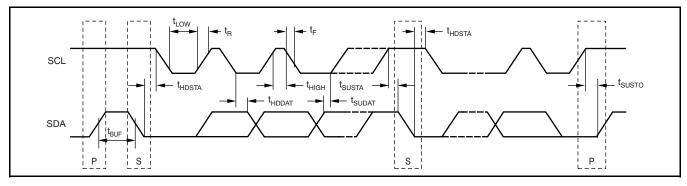

### TIMING REQUIREMENTS

Figure 1. I<sup>2</sup>C Timing Diagram

| Table 1. I <sup>2</sup> C Timing Definit | itions |

|------------------------------------------|--------|

|------------------------------------------|--------|

|                                                                                               |                    | FAST    | MODE | HIGH-SPE | ED MODE |      |

|-----------------------------------------------------------------------------------------------|--------------------|---------|------|----------|---------|------|

| PARAMETER                                                                                     |                    | MIN MAX |      | MIN      | MAX     | UNIT |

| SCL operating frequency                                                                       | f <sub>SCL</sub>   | 0.01    | 0.4  | 0.01     | 3.4     | MHz  |

| Bus free time between START and STOP condition                                                | t <sub>BUF</sub>   | 600     |      | 160      |         | ns   |

| Hold time after repeated START condition.<br>After this period, the first clock is generated. | t <sub>HDSTA</sub> | 600     |      | 160      |         | ns   |

| Repeated START condition setup time                                                           | t <sub>SUSTA</sub> | 600     |      | 160      |         | ns   |

| Stop condition setup time                                                                     | t <sub>SUSTO</sub> | 600     |      | 160      |         | ns   |

| Data hold time                                                                                | t <sub>hddat</sub> | 0       |      | 0        |         | ns   |

| Data setup time                                                                               | t <sub>SUDAT</sub> | 100     |      | 10       |         | ns   |

| SCL clock low period                                                                          | t <sub>LOW</sub>   | 1300    |      | 160      |         | ns   |

| SCL clock high period                                                                         | t <sub>HIGH</sub>  | 600     |      | 60       |         | ns   |

| Clock/data fall time                                                                          | t <sub>F</sub>     |         | 300  |          | 160     | ns   |

| Clock/data rise time                                                                          | t <sub>R</sub>     |         | 300  |          | 160     | ns   |

www.ti.com

### **TYPICAL CHARACTERISTICS**

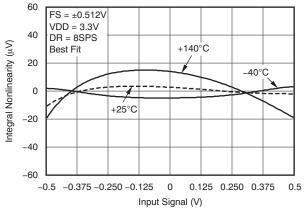

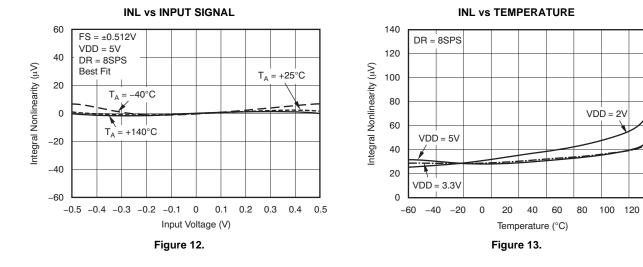

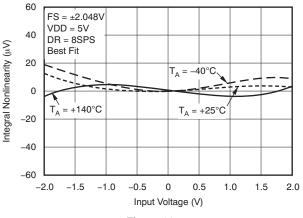

At  $T_A = +25^{\circ}C$  and VDD = 3.3V, unless otherwise noted.

#### **OPERATING CURRENT vs TEMPERATURE**

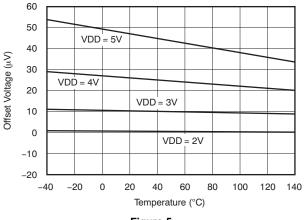

#### SINGLE-ENDED OFFSET ERROR vs TEMPERATURE<sup>(1)</sup>

Figure 4.

(1) This parameter expresses the full-scale range of the ADC scaling. In no event should more than VDD + 0.3V be applied to this device.

+140<sup>°</sup>C

, +25°C

1.0

1.5

2.0

0.5

-40°C

# <u>₩豐铈究D\$1113IRUGT"供应商</u>

**TYPICAL CHARACTERISTICS (continued)**

60

40

20

0

-20

-40

-60

-2.0

-1.5

-1.0

Integral Nonlinearity (µV)

FS = ±2.048V VDD = 3.3V

DR = 8SPS

Best Fit

#### Figure 8.

#### Figure 10.

#### INL vs INPUT SIGNAL

Figure 9.

-0.5

0

Input Signal (V)

**INL vs INPUT SIGNAL**

(2) This parameter expresses the full-scale range of the ADC scaling. In no event should more than VDD + 0.3V be applied to this device.

140

## ADS1113 ADS1114 ADS1115 S时候前本小的长行9973限以後已对49月的新報報

www.ti.com

TYPICAL CHARACTERISTICS (continued)

#### Figure 14.

#### NOISE vs TEMPERATURE

#### Figure 15.

#### GAIN ERROR HISTOGRAM

8

#

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$  and VDD = 3.3V, unless otherwise noted.

www.ti.com

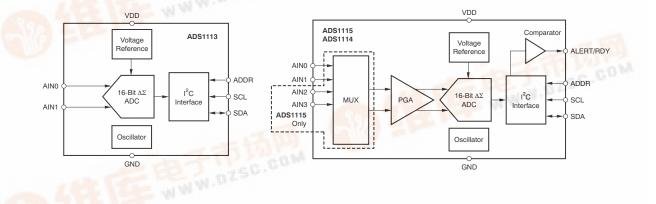

### OVERVIEW

The ADS1113/4/5 are very small, low-power, 16-bit, delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converters (ADCs). The ADS1113/4/5 are extremely easy to configure and design into a wide variety of applications, and allow precise measurements to be obtained with very little effort. Both experienced and novice users of data converters find designing with the ADS1113/4/5 family to be intuitive and problem-free.

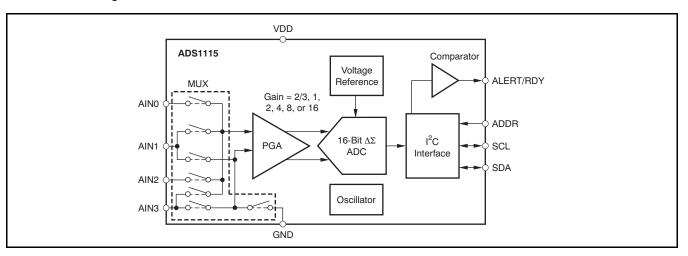

The ADS1113/4/5 consist of a  $\Delta\Sigma$  analog-to-digital (A/D) core with adjustable gain (excludes the ADS1113), an internal voltage reference, a clock oscillator, and an I<sup>2</sup>C interface. An additional feature available on the ADS1114/5 is a programmable digital comparator that provides an alert on a dedicated pin. All of these features are intended to reduce required external circuitry and improve performance. Figure 22 shows the ADS1115 functional block diagram.

The ADS1113/4/5 A/D core measures a differential signal,  $V_{IN}$ , that is the difference of AIN<sub>P</sub> and AIN<sub>N</sub>. A MUX is available on the ADS1115. This architecture results in a very strong attenuation in any common-mode signals. The converter core consists

of a differential, switched-capacitor  $\Delta\Sigma$  modulator followed by a digital filter. Input signals are compared to the internal voltage reference. The digital filter receives a high-speed bitstream from the modulator and outputs a code proportional to the input voltage.

The ADS1113/4/5 have two available conversion modes: single-shot mode and continuous conversion mode. In single-shot mode, the ADC performs one conversion of the input signal upon request and stores the value to an internal result register. The device then enters a low-power shutdown mode. This mode is intended to provide significant power savings in systems that only require periodic conversions or when there are long idle periods between conversions. In continuous conversion mode, the ADC automatically begins a conversion of the input signal as soon as the previous conversion is completed. The rate of continuous conversion is equal to the programmed data rate. Data can be read at any time and always reflect the most recent completed conversion.

Figure 22. ADS1115 Functional Block Diagram

###

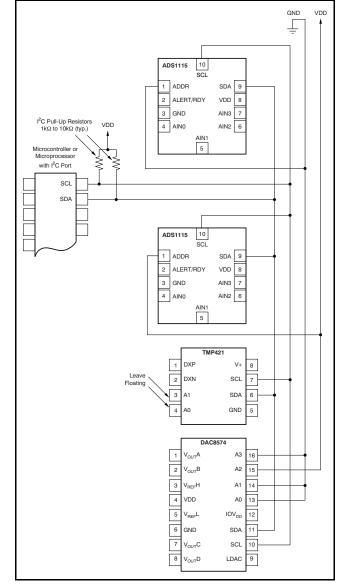

#### QUICKSTART GUIDE

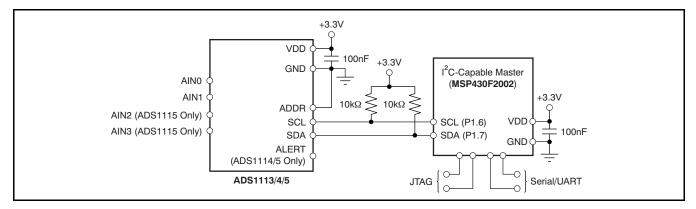

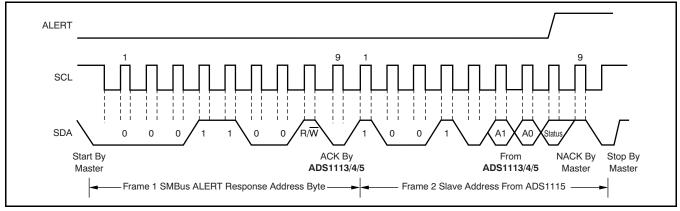

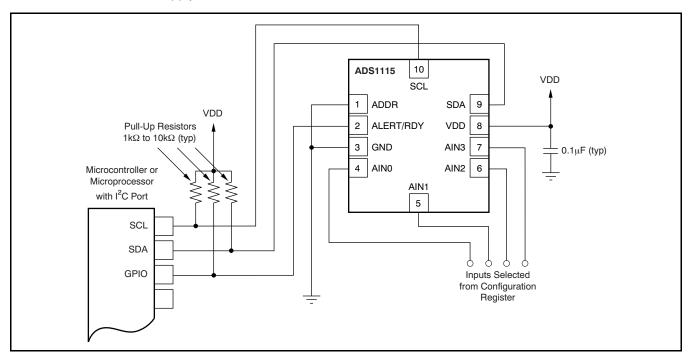

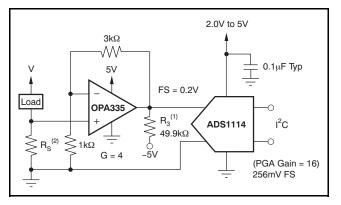

This section provides a brief example of ADS1113/4/5 communications. Refer to subsequent sections of this data sheet for more detailed explanations. Hardware for this design includes: one ADS1113/4/5 configured with an  $l^2C$  address of 1001000; a microcontroller with an  $l^2C$  interface (TI recommends the MSP430F2002); discrete components such as resistors, capacitors, and serial connectors; and a 2V to 5V power supply. Figure 23 shows the basic hardware configuration.

The ADS1113/4/5 communicate with the master (microcontroller) through an  $I^2C$  interface. The master provides a clock signal on the SCL pin and data are transferred via the SDA pin. The ADS1113/4/5 never drive the SCL pin. For information on programming and debugging the microcontroller being used, refer to the device-specific product data sheet.

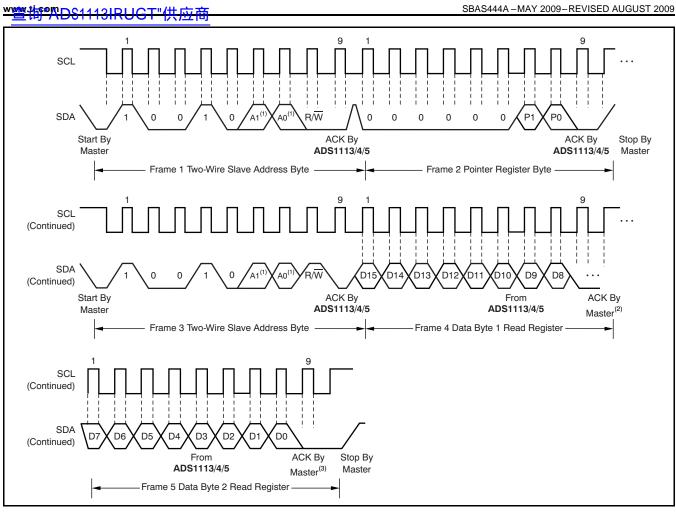

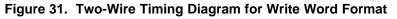

The first byte sent by the master should be the ADS1113/4/5 address followed by a bit that instructs the ADS1113/4/5 to listen for a subsequent byte. The second byte is the register pointer. Refer to Table 9 for a register map. The third and fourth bytes sent from the master are written to the register indicated in the second byte. Refer to Figure 30 and Figure 31 for read and write operation timing diagrams, respectively. All read and write transactions with the ADS1113/4/5 must be preceded by a start condition and followed by a stop condition.

For example, to write to the configuration register to set the ADS1113/4/5 to continuous conversion mode and then read the conversion result, send the following bytes in this order:

#### Write to Config register:

First byte: 0b10010000 (first 7-bit I<sup>2</sup>C address followed by a low read/write bit)

Second byte: 0b0000001 (points to Config register)

Third byte: 0b10000100 (MSB of the Config register to be written)

Fourth byte: 0b10000011 (LSB of the Config register to be written)

#### Write to Pointer register:

First byte: 0b10010000 (first 7-bit  $I^2C$  address followed by a low read/write bit)

Second byte: 0b0000000 (points to Conversion register)

#### Read Conversion register:

First byte: 0b10010001 (first 7-bit  $I^2C$  address followed by a high read/write bit)

Second byte: the ADS1113/4/5 response with the MSB of the Conversion register

Third byte: the ADS1113/4/5 response with the LSB of the Conversion register

Figure 23. Basic Hardware Configuration

### SBAS在14A A MAX 20093 REVISED A UGU 医 2009

www.ti.com

### MULTIPLEXER

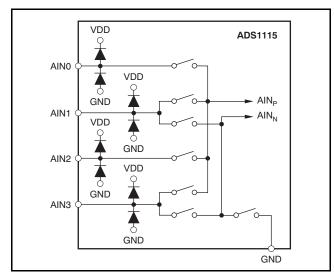

The ADS1115 contains an input multiplexer, as shown in Figure 24. Either four single-ended or two differential signals can be measured. Additionally, AIN0 and AIN1 may be measured differentially to AIN3. The multiplexer is configured by three bits in the Config register. When single-ended signals are measured, the negative input of the ADC is internally connected to GND by a switch within the multiplexer.

Figure 24. ADS1115 MUX

The ADS1113 and ADS1114 do not have a multiplexer. Either one differential or one single-ended signal may be measured with these devices. For single-ended measurements, connect the AIN1 pin to GND. Note that in subsequent sections of this data sheet,  $AIN_P$  refers to AIN0 and  $AIN_N$  refers to AIN1 for the ADS1113 and ADS1114.

When measuring single-ended inputs it is important to note that the negative range of the output codes are not used. These codes are for measuring negative differential signals such as  $(\text{AIN}_{\text{P}} - \text{AIN}_{\text{N}}) < 0.$  ESD diodes to VDD and GND protect the inputs on all three devices (ADS1113, ADS1114, and ADS1115). To prevent the ESD diodes from turning on, the absolute voltage on any input must stay within the following range:

GND - 0.3V < AINx < VDD + 0.3V

If it is possible that the voltages on the input pins may violate these conditions, external Schottky clamp diodes and/or series resistors may be required to limit the input current to safe values (see the Absolute Maximum Ratings table).

Also, overdriving one unused input on the ADS1115 may affect conversions taking place on other input pins. If overdrive on unused inputs is possible, again it is recommended to clamp the signal with external Schottky diodes.

### ANALOG INPUTS

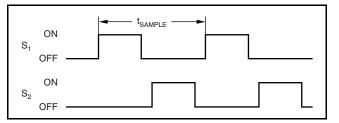

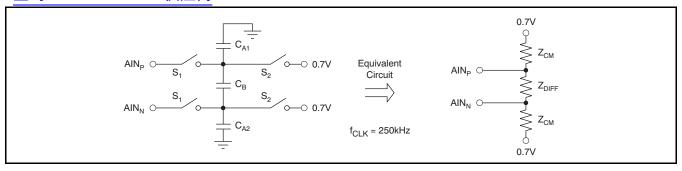

The ADS1113/4/5 use a switched-capacitor input stage where capacitors are continuously charged and then discharged to measure the voltage between AIN<sub>P</sub> and AIN<sub>N</sub>. The capacitors used are small, and to external circuitry the average loading appears resistive. This structure is shown in Figure 26 . The resistance is set by the capacitor values and the rate at which they are switched. Figure 25 shows the on/off setting of the switches illustrated in Figure 26. During the sampling phase,  $S_1$  switches are closed. This event charges  $C_{A1}$  to AIN<sub>P</sub>,  $C_{A2}$  to AIN<sub>N</sub>, and  $C_B$ to  $(AIN_P - AIN_N)$ . During the discharge phase, S<sub>1</sub> is first opened and then  $S_2$  is closed. Both  $C_{A1}$  and  $C_{A2}$ then discharge to approximately 0.7V and  $C_{B}$ discharges to 0V. This charging draws a very small transient current from the source driving the ADS1113/4/5 analog inputs. The average value of this current can be used to calculate the effective impedance ( $R_{eff}$ ) where  $R_{eff} = V_{IN}/I_{AVERAGE}$ .

Figure 25. S<sub>1</sub> and S<sub>2</sub> Switch Timing for Figure 26

### <u>₩豐椅\$\$\$\$0\$1113IRUGT"供应商</u>

Figure 26. Simplified Analog Input Circuit

The common-mode input impedance is measured by applying a common-mode signal to shorted  $AIN_P$  and  $AIN_N$  inputs and measuring the average current consumed by each pin. The common-mode input impedance changes depending on the PGA gain setting, but is approximately  $6M\Omega$  for the default PGA gain setting. In Figure 26 , the common-mode input impedance is  $Z_{CM}$ .

The differential input impedance is measured by applying a differential signal to  $AIN_P$  and  $AIN_N$  inputs where one input is held at 0.7V. The current that flows through the pin connected to 0.7V is the differential current and scales with the PGA gain setting. In Figure 26 , the differential input impedance is  $Z_{\text{DIFF}}$ . Table 2 describes the typical differential input impedance.

| Table 2. | Differential | Input Im | pedance |

|----------|--------------|----------|---------|

|----------|--------------|----------|---------|

| FS (V)                 | DIFFERENTIAL INPUT IMPEDANCE |

|------------------------|------------------------------|

| ±6.144V <sup>(1)</sup> | 22ΜΩ                         |

| ±4.096V <sup>(1)</sup> | 15ΜΩ                         |

| ±2.048V                | 4.9ΜΩ                        |

| ±1.024V                | 2.4ΜΩ                        |

| ±0.512V                | 710kΩ                        |

| ±0.256V                | 710kΩ                        |

This parameter expresses the full-scale range of the ADC scaling. In no event should more than VDD + 0.3V be applied to this device. The typical value of the input impedance cannot be neglected. Unless the input source has a low impedance, the ADS1113/4/5 input impedance may affect the measurement accuracy. For sources with high output impedance, buffering may be necessary. Active buffers introduce noise, and also introduce offset and gain errors. All of these factors should be considered in high-accuracy applications.

Because the clock oscillator frequency drifts slightly with temperature, the input impedances also drift. For many applications, this input impedance drift can be ignored, and the values given in Table 2 for typical input impedance are valid.

### FULL-SCALE INPUT

A programmable gain amplifier (PGA) is implemented before the  $\Delta\Sigma$  core of the ADS1114/5. The PGA can be set to gains of 2/3, 1, 2, 4, 8, and 16. Table 3 shows the corresponding full-scale (FS) ranges. The PGA is configured by three bits in the Config register. The ADS1113 has a fixed full-scale input range of ±2.048V. The PGA = 2/3 setting allows input measurement to extend up to the supply voltage when VDD is larger than 4V. Note though that in this case (as well as for PGA = 1 and VDD < 4V), it is not possible to reach a full-scale output code on the ADC. Analog input voltage limits given in the Electrical Characteristics table.

| PGA SETTING | FS (V)                 |

|-------------|------------------------|

| 2/3         | ±6.144V <sup>(1)</sup> |

| 1           | ±4.096V <sup>(1)</sup> |

| 2           | ±2.048V                |

| 4           | ±1.024V                |

| 8           | ±0.512V                |

| 16          | ±0.256V                |

This parameter expresses the full-scale range of the ADC scaling. In no event should more than VDD + 0.3V be applied to this device.

SB金结结本大性发 20093 REVISED PHUGU 经 2009

#### DATA FORMAT

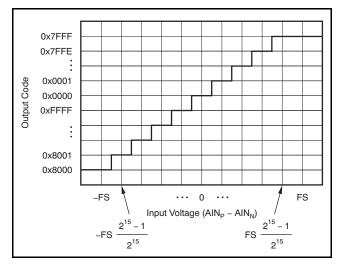

The ADS1113/4/5 provide 16 bits of data in binary twos complement format. The positive full-scale input produces an output code of 7FFFh and the negative full-scale input produces an output code of 8000h. The output clips at these codes for signals that exceed full-scale. Table 4 summarizes the ideal output codes for different input signals. Figure 27 shows code transitions versus input voltage.

| Table 4. In | put Signal v | versus Ideal | Output Code |

|-------------|--------------|--------------|-------------|

|-------------|--------------|--------------|-------------|

| $\begin{array}{l} \text{INPUT SIGNAL, V}_{\text{IN}} \\ (\text{AIN}_{\text{P}} - \text{AIN}_{\text{N}}) \end{array}$ | IDEAL OUTPUT CODE <sup>(1)</sup> |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------|

| ≥ FS (2 <sup>15</sup> – 1)/2 <sup>15</sup>                                                                           | 7FFFh                            |

| +FS/2 <sup>15</sup>                                                                                                  | 0001h                            |

| 0                                                                                                                    | 0                                |

| -FS/2 <sup>15</sup>                                                                                                  | FFFFh                            |

| ≤ –FS                                                                                                                | 8000h                            |

1. Excludes the effects of noise, INL, offset, and gain errors.

### ALIASING

As with any data converter, if the input signal contains frequencies greater than half the data rate, aliasing occurs. To prevent aliasing, the input signal must be bandlimited. Some signals are inherently bandlimited. For example, the output of a thermocouple, which has a limited rate of change. Nevertheless, they can contain noise and interference components. These components can fold back into the sampling band in the same way as with any other signal.

Texas

INSTRUMENTS

When designing an input filter circuit, be sure to take into account the interaction between the filter network and the input impedance of the ADS1113/4/5.

instances, a simple RC filter is adequate.

### **OPERATING MODES**

The ADS1113/4/5 operate in one of two modes: continuous conversion or single-shot. In continuous conversion mode, the ADS1113/4/5 continuously perform conversions. Once a conversion has been completed, the ADS1113/4/5 place the result in the Conversion register and immediately begins another conversion. In single-shot mode, the ADS1113/4/5 wait until the OS bit is set high. Once asserted, the bit is set to '0', indicating that a conversion is currently in progress. Once conversion data are ready, the OS bit reasserts and the device powers down. Writing a '1' to the OS bit during a conversion has no effect.

#### **RESET AND POWER-UP**

When the ADS1113/4/5 powers up, a reset is performed. As part of the reset process, the ADS1113/4/5 set all of the bits in the Config register to the respective default settings.

The ADS1113/4/5 respond to the I<sup>2</sup>C general call reset command. When the ADS1113/4/5 receive a general call reset, an internal reset is performed as if the device had been powered on.

### **DUTY CYCLING FOR LOW POWER**

For many applications, the improved performance at low data rates may not be required. For these applications, the ADS1113/4/5 support duty cycling that can yield significant power savings by periodically requesting high data rate readings at an effectively lower data rate. For example, an ADS1113/4/5 in power-down mode with a data rate set to 860SPS could be operated by a microcontroller that instructs a single-shot conversion every 125ms (8SPS). Because a conversion at 860SPS only requires about 1.2ms, the ADS1113/4/5 enter power-down mode for the remaining 123.8ms. In this configuration, the ADS1113/4/5 consume about 1/100th the power of the ADS1113/4/5 operated in continuous conversion mode. The rate of duty cycling is completely arbitrary and is defined by the master controller. The ADS1113/4/5 offer lower data rates that do not implement duty cycling and offer improved noise performance if it is needed.

### <u>₩豐椅\$\$\$\$0\$11131RUGT"供应商</u>

#### COMPARATOR (ADS1114/15 ONLY)

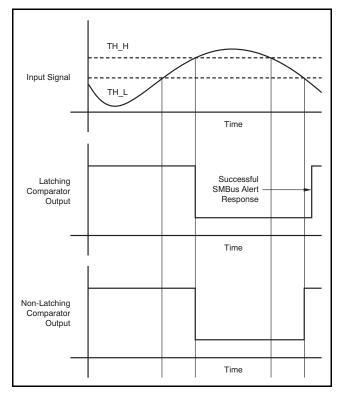

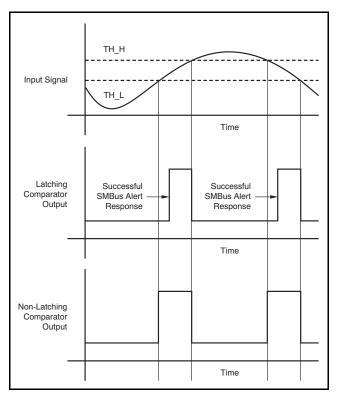

ADS1114/5 are each equipped with a The customizable comparator that can issue an alert on the ALERT/RDY pin. This feature can significantly reduce external circuitry for many applications. The comparator can be implemented as either a traditional comparator or a window comparator via the COMP\_MODE bit in the Config register. When implemented as a traditional comparator, the ALERT/RDY pin asserts (active low by default) when conversion data exceed the limit set in the high threshold register. The comparator then deasserts when the input signal falls below the low threshold register value. In window comparator mode, the ALERT/RDY pin asserts if conversion data exceed the high threshold register or fall below the low threshold register.

In either window or traditional comparator mode, the comparator can be configured to latch once asserted by the COMP\_LAT bit in the Config register. This setting causes the assertion to remain even if the input signal is not beyond the bounds of the threshold registers. This latched assertion can be cleared by issuing an SMBus alert response or by reading the Conversion register. The COMP\_POL bit in the Config register configures the ALERT/RDY pin as active high or active low. Operational diagrams for the comparator modes are shown in Figure 28 and Figure 29.

The comparator can be configured to activate the ALERT/RDY pin after a set number of successive readings exceed the threshold. The comparator can be configured to wait for one, two, or four readings beyond the threshold before activating the ALERT/RDY pin by changing the COMP\_QUE bits in the Config register. The COMP\_QUE bits can also disable the comparator function.

### CONVERSION READY PIN (ADS1114/5 ONLY)

The ALERT/RDY pin can also be configured as a conversion ready pin. This mode of operation can be realized if the MSB of the high threshold register is set to '1' and the MSB of the low threshold register is set to '0'. The COMP\_POL bit continues to function and the COMP\_QUE bits can disable the pin; however, the COMP\_MODE and COMP\_LAT bits no longer control any function. When configured as a conversion ready pin, ALERT/RDY continues to require a pull-up resistor. When in continuous conversion mode, the ALERT/RDY pin at the end of each conversion. When in single-shot shutdown mode, the ALERT/RDY pin asserts low at the end of a conversion if the COMP\_POL bit is set to '0'.

Figure 28. Alert Pin Timing Diagram When Configured as a Traditional Comparator

Figure 29. Alert Pin Timing Diagram When Configured as a Window Comparator

SB查给持A大MAY 2009-7月415EDTAUGU获留9

#### SMBus ALERT RESPONSE

When configured in latching mode (COMP LAT = '1' in the Config register), the ALERT/RDY pin can be implemented with an SMBus alert. The pin asserts if the comparator detects a conversion that exceeds an upper or lower threshold. This interrupt is latched and can be cleared only by reading conversion data, or by issuing a successful SMBus alert response and reading the asserting device I<sup>2</sup>C address. If conversion data exceed the upper or lower thresholds after being cleared, the pin reasserts. This assertion does not affect conversions that are already in progress. The ALERT/RDY pin, as with the SDA pin, is an open-drain pin. This architecture allows several devices to share the same interface bus. When disabled, the pin holds a high state so that it does not interfere with other devices on the same bus line.

When the master senses that the ALERT/RDY pin has latched, it issues an SMBus alert command (00011001) to the I<sup>2</sup>C bus. Any ADS1114/5 data converters on the I<sup>2</sup>C bus with the ALERT/RDY pins asserted respond to the command with the slave address. In the event that two or more ADS1114/5 data converters present on the bus assert the latched ALERT/RDY pin, arbitration during the address response portion of the SMBus alert decides which device clears its assertion. The device with the lowest I<sup>2</sup>C address always wins arbitration. If a device loses arbitration, it does not clear the comparator output pin assertion. The master then repeats the SMBus alert response until all devices have had the respective assertions cleared. In window comparator mode, the SMBus alert status bit indicates a '1' if signals exceed the high threshold and a '0' if signals exceed the low threshold.

### I<sup>2</sup>C INTERFACE

The ADS1113/4/5 communicate through an  $I^2C$  interface.  $I^2C$  is a two-wire open-drain interface that supports multiple devices and masters on a single bus. Devices on the  $I^2C$  bus only drive the bus lines low by connecting them to ground; they never drive the bus lines high. Instead, the bus wires are pulled high by pull-up resistors, so the bus wires are high when no device is driving them low. This way, two devices cannot conflict; if two devices drive the bus simultaneously, there is no driver contention.

Communication on the I<sup>2</sup>C bus always takes place between two devices, one acting as the master and the other as the slave. Both masters and slaves can read and write, but slaves can only do so under the direction of the master. Some I<sup>2</sup>C devices can act as masters or slaves, but the ADS1113/4/5 can only act as slave devices.

An  $l^2C$  bus consists of two lines, SDA and SCL. SDA carries data; SCL provides the clock. All data are transmitted across the  $l^2C$  bus in groups of eight bits. To send a bit on the  $l^2C$  bus, the SDA line is driven to the appropriate level while SCL is low (a low on SDA indicates the bit is zero; a high indicates the bit is one). Once the SDA line settles, the SCL line is brought high, then low. This pulse on SCL clocks the SDA bit into the receiver shift register. If the  $l^2C$  bus is held idle for more than 25ms, the bus times out.

The I<sup>2</sup>C bus is bidirectional: the SDA line is used for both transmitting and receiving data. When the master reads from a slave, the slave drives the data line; when the master sends to a slave, the master drives the data line. The master always drives the clock line. The ADS1113/4/5 never drive SCL, because they cannot act as a master. On the ADS1113/4/5, SCL is an input only.

Most of the time the bus is idle; no communication occurs, and both lines are high. When communication is taking place, the bus is active. Only master devices can start a communication and initiate a START condition on the bus. Normally, the data line is only allowed to change state while the clock line is low. If the data line changes state while the clock line is high, it is either a START condition or a STOP condition. A START condition occurs when the clock line is high and the data line goes from high to low. A STOP condition occurs when the clock line is high and the data line goes from low to high.

After the master issues a START condition, it sends a byte that indicates which slave device it wants to communicate with. This byte is called the *address* byte. Each device on an  $I^2C$  bus has a unique 7-bit address to which it responds. The master sends an address in the address byte, together with a bit that indicates whether it wishes to read from or write to the slave device.

Every byte transmitted on the I<sup>2</sup>C bus, whether it is address or data, is acknowledged with an *acknowledge* bit. When the master has finished sending a byte (eight data bits) to a slave, it stops driving SDA and waits for the slave to acknowledge the byte. The slave acknowledges the byte by pulling SDA low. The master then sends a clock pulse to clock the acknowledge bit. Similarly, when the master has finished reading a byte, it pulls SDA low to acknowledge this to the slave. It then sends a clock pulse to clock the bit. (The master always drives the clock line.)

A *not-acknowledge* is performed by simply leaving SDA high during an acknowledge cycle. If a device is not present on the bus, and the master attempts to address it, it receives a not-acknowledge because no device is present at that address to pull the line low.

### \* 2 1 13 RUGT 供应商

When the master has finished communicating with a slave, it may issue a STOP condition. When a STOP condition is issued, the bus becomes idle again. The master may also issue another START condition. When a START condition is issued while the bus is active, it is called a repeated START condition.

See the *Timing Requirements* section for a timing diagram showing the ADS1113/4/5 l<sup>2</sup>C transaction.

### I<sup>2</sup>C ADDRESS SELECTION

The ADS1113/4/5 have one address pin, ADDR, that sets the  $l^2C$  address. This pin can be connected to ground, VDD, SDA, or SCL, allowing four addresses to be selected with one pin as shown in Table 5. The state of the address pin ADDR is sampled continuously.

#### Table 5. ADDR Pin Connection and Corresponding Slave Address

| ADDR PIN | SLAVE ADDRESS |

|----------|---------------|

| Ground   | 1001000       |

| VDD      | 1001001       |

| SDA      | 1001010       |

| SCL      | 1001011       |

### I<sup>2</sup>C GENERAL CALL

The ADS1113/4/5 respond to the  $I^2C$  general call address (0000000) if the eighth bit is '0'. The devices acknowledge the general call address and respond to commands in the second byte. If the second byte is 00000110 (06h), the ADS1113/4/5 reset the internal registers and enter power-down mode.

### I<sup>2</sup>C SPEED MODES

The  $I^2C$  bus operates at one of three speeds. Standard mode allows a clock frequency of up to 100kHz; fast mode permits a clock frequency of up to 400kHz; and high-speed mode (also called Hs mode) allows a clock frequency of up to 3.4MHz. The ADS1113/4/5 are fully compatible with all three modes.

No special action is required to use the ADS1113/4/5 in standard or fast mode, but high-speed mode must be activated. To activate high-speed mode, send a special address byte of *00001xxx* following the START condition, where *xxx* are bits unique to the Hs-capable master. This byte is called the Hs master code. (Note that this is different from normal address bytes; the eighth bit does not indicate read/write status.) The ADS1113/4/5 do not acknowledge this

byte; the I<sup>2</sup>C specification prohibits acknowledgment of the Hs master code. Upon receiving a master code, the ADS1113/4/5 switch on Hs mode filters, and communicate at up to 3.4MHz. The ADS1113/4/5 switch out of Hs mode with the next STOP condition.

For more information on high-speed mode, consult the  $l^2C$  specification.

### **SLAVE MODE OPERATIONS**

The ADS1113/4/5 can act as either slave receivers or slave transmitters. As a slave device, the ADS1113/4/5 cannot drive the SCL line.

#### **Receive Mode:**

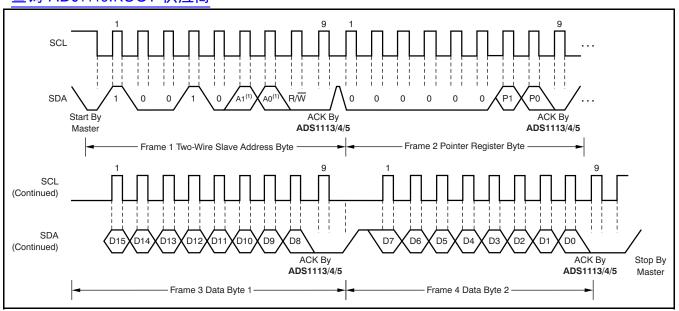

In slave receive mode the first byte transmitted from the master to the slave is the address with the R/W bit low. This byte allows the slave to be written to. The next byte transmitted by the master is the register pointer byte. The ADS1113/4/5 then acknowledge receipt of the register pointer byte. The next two bytes are written to the address given by the register pointer. The ADS1113/4/5 acknowledge each byte sent. Register bytes are sent with the most significant byte first, followed by the least significant byte.

#### Transmit Mode:

In slave transmit mode, the first byte transmitted by the master is the 7-bit slave address followed by the high R/W bit. This byte places the slave into transmit mode and indicates that the ADS1113/4/5 are being read from. The next byte transmitted by the slave is the most significant byte of the register that is indicated by the register pointer. This byte is followed by an acknowledgment from the master. The remaining least significant byte is then sent by the slave and is followed by an acknowledgment from the master. The master may terminate transmission after any byte by not acknowledging or issuing a START or STOP condition.

#### WRITING/READING THE REGISTERS

To access a specific register from the ADS1113/4/5, the master must first write an appropriate value to the Pointer register. The Pointer register is written directly after the slave address byte, low R/W bit, and a successful slave acknowledgment. After the Pointer register is written, the slave acknowledges and the master issues a STOP or a repeated START condition.

Copyright © 2009, Texas Instruments Incorporated

www.ti.com

# SB查给持A大MAY 2009-7月415EDTAUGU获留9

When reading from the ADS1113/4/5, the previous value written to the Pointer register determines the register that is read from. To change which register is read, a new value must be written to the Pointer register. To write a new value to the Pointer register, the master issues a slave address byte with the  $R/\overline{W}$ bit low, followed by the Pointer register byte. No additional data need to be transmitted, and a STOP condition can be issued by the master. The master may now issue a START condition and send the slave address byte with the R/W bit high to begin the read. Table 10 details this sequence. If repeated reads from the same register are desired, there is no need to continually send Pointer register bytes, because the ADS1113/4/5 store the value of the Pointer register until it is modified by a write operation. However, every write operation requires the Pointer register to be written.

#### REGISTERS

The ADS1113/4/5 have four registers that are accessible via the I<sup>2</sup>C port. The Conversion register contains the result of the last conversion. The Config register allows the user to change the ADS1113/4/5 operating modes and query the status of the devices. Two registers, Lo\_thresh and Hi\_thresh, set the threshold values used for the comparator function.

### POINTER REGISTER

The four registers are accessed by writing to the Pointer register byte; see Figure 30 . Table 6 and Table 7 indicate the Pointer register byte map.

| Table 6. Register Address | Table | 6. | Register | Address |

|---------------------------|-------|----|----------|---------|

|---------------------------|-------|----|----------|---------|

|       | •     |                     |

|-------|-------|---------------------|

| BIT 1 | BIT 0 | REGISTER            |

| 0     | 0     | Conversion register |

| 0     | 1     | Config register     |

| 1     | 0     | Lo_thresh register  |

| 1     | 1     | Hi_thresh register  |

#### **CONVERSION REGISTER**

The 16-bit register contains the result of the last conversion in binary twos complement format. Following reset or power-up, the Conversion register is cleared to '0', and remains '0' until the first conversion is completed.

The register format is shown in Table 8 .

#### **CONFIG REGISTER**

The 16-bit register can be used to control the ADS1113/4/5 operating mode, input selection, data rate, PGA settings, and comparator modes. The register format is shown in Table 9.

#### Table 7. Pointer Register Byte (Write-Only)

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1            | BIT 0 |

|-------|-------|-------|-------|-------|-------|------------------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | Register address |       |

#### Table 8. Conversion Register (Read-Only)

| BIT  | 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| NAME | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

#### Table 9. Config Register (Read/Write)

| -    |     |      |      |           |          |          |           |           |

|------|-----|------|------|-----------|----------|----------|-----------|-----------|

| BIT  | 15  | 14   | 13   | 12        | 11       | 10       | 9         | 8         |

| NAME | OS  | MUX2 | MUX1 | MUX0      | PGA2     | PGA1     | PGA0      | MODE      |

|      |     |      |      |           |          |          |           |           |

| BIT  | 7   | 6    | 5    | 4         | 3        | 2        | 1         | 0         |

| NAME | DR2 | DR1  | DR0  | COMP_MODE | COMP_POL | COMP_LAT | COMP_QUE1 | COMP_QUE0 |

Default = 8583h.

Bit [15]

#### OS: Operational status/single-shot conversion start

This bit determines the operational status of the device. This bit can only be written when in power-down mode.

For a write status:

0 : No effect

1 : Begin a single conversion (when in power-down mode)

For a read status:

0 : Device is currently performing a conversion

1 : Device is not currently performing a conversion

ADS1113 ADS1114 ADS1115 SBAS444A – MAY 2009 – REVISED AUGUST 2009

| MUX[2:0]: Input multiplexer configuration (ADS                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                      | i1115 only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| These bits configure the input multiplexer. They se                                                                                                                  | erve no function on the ADS1113/4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $000:AIN_P$ = AIN0 and $AIN_N$ = AIN1 (default) 001: $AIN_P$ = AIN0 and $AIN_N$ = AIN3 010: $AIN_P$ = AIN1 and $AIN_N$ = AIN3 011: $AIN_P$ = AIN2 and $AIN_N$ = AIN3 | $100$ : $AIN_P$ = $AIN0$ and $AIN_N$ = $GND$ $101$ : $AIN_P$ = $AIN1$ and $AIN_N$ = $GND$ $110$ : $AIN_P$ = $AIN2$ and $AIN_N$ = $GND$ $111$ : $AIN_P$ = $AIN3$ and $AIN_N$ = $GND$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PGA[2:0]: Programmable gain amplifier configu                                                                                                                        | ration (ADS1114 and ADS1115 only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| These bits configure the programmable gain ampli                                                                                                                     | fier. They serve no function on the ADS1113.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 000 : FS = $\pm 6.144V$ <sup>(1)</sup><br>001 : FS = $\pm 4.096V$ <sup>(1)</sup><br>010 : FS = $\pm 2.048V$ (default)<br>011 : FS = $\pm 1.024V$                     | 100 : FS = ±0.512V<br>101 : FS = ±0.256V<br>110 : FS = ±0.256V<br>111 : FS = ±0.256V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MODE: Device operating mode                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |