|                                              |        |       |      |       |             |        |         | F   | REVISIO     | ONS |          |               |                       |        |                   |       |                                       |         |      |    |

|----------------------------------------------|--------|-------|------|-------|-------------|--------|---------|-----|-------------|-----|----------|---------------|-----------------------|--------|-------------------|-------|---------------------------------------|---------|------|----|

| ∟т査询"                                        | 962-9  | 97550 | 01Q) | KA"供  | <del></del> | ESCR   | IPTION  | l   |             |     |          |               | DA                    | TE (YF | R-MO-D            | )A)   |                                       | APPR    | OVED |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     | '           |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      | i  |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

| REV                                          |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   | Γ     |                                       |         |      |    |

| SHEET                                        |        |       |      |       |             |        |         |     |             | -,  |          |               |                       |        |                   |       |                                       |         |      |    |

| REV                                          |        |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         | -    |    |

| SHEET                                        | 15     | 16    | 17   | 18    | 19          | 20     | 21      | 22  | 23          | 24  | 25       | 26            |                       |        |                   |       | ļ                                     |         |      |    |

| REV STATUS                                   |        |       |      | RE\   | /           |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      | Ĭ  |

| OF SHEETS                                    |        |       |      | SHE   | ET          |        | 1       | 2   | 3           | 4   | 5        | 6             | 7                     | 8      | 9                 | 10    | 11                                    | 12      | 13   | 14 |

| PMIC N/A                                     |        |       |      | PR    | EPARE       | D BY   |         |     |             |     |          |               |                       |        |                   | •     | · · · · · · · · · · · · · · · · · · · | ·       |      |    |

|                                              |        |       |      |       |             |        | Vonnell |     |             | :   | D        | EFEN          | SE S                  | UPPL   | Y CE              | NTEF  | R COL                                 | .UMB    | US   |    |

|                                              | VDAR   |       |      | CHE   | CKED        | BY     |         |     |             |     |          |               | COL                   | UMBU   | JS, O             | HIO - | 43216                                 | 5       |      |    |

| MICROCIRC                                    | UIT D  | PRAW  | ING  |       |             | laymon | d Monr  | nin |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

| THIS DRAWING IS AVAILABLE                    |        |       | APF  | PROVE | D BY        |        |         |     | NAIC        |     |          | \ 11 <b>T</b> | DIC                   | IT A I | 1 181             |       |                                       | A 1     |      |    |

| FOR USE BY ALL DEPARTMENTS                   |        |       |      |       | laymon      | d Monr | nin     |     | AS          | YNC | HRC      | NOIT,         | DIG<br>IS C           |        | L.IIN<br>// I.N.I | EAR   | , DUA<br>IONS                         | 4L<br>2 |      |    |

|                                              |        |       |      |       |             |        |         |     |             |     |          | VITH          |                       |        | /1014I            |       | IOINC                                 | ,       |      |    |

| AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE |        |       | DRA  | WING  | APPRO       | DVAL [ | DATE    | *** |             |     |          | C SI          |                       |        |                   |       |                                       |         |      |    |

| DELIVERING OF DEFEROE                        |        |       |      |       |             | 8-13   |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

| AMS                                          | SC N/A |       |      | REV   | ISION       | LEVEL  |         |     | <del></del> | s   | IZE      |               |                       |        | T                 |       |                                       |         |      |    |

|                                              |        |       |      |       |             |        |         |     |             | L   | A        | L CA          | GE CC<br><b>67268</b> |        |                   |       | 5962                                  | -9755   | 50   |    |

|                                              |        |       |      |       |             |        |         |     |             | SHE | ET<br>—— |               |                       | OF     | 26                |       |                                       |         |      |    |

| OSCC FORM 2233                               | 3      |       |      |       |             |        |         |     |             |     |          |               |                       |        |                   |       |                                       |         |      |    |

<u>DISTRIBUTION STATEMENT A.</u> Approved for public release; distribution is unlimited.

5962-E267-97

**9004708 0030153 421**

#### 1. SCOPE

#### 查询"5962-9755001QXA"供应商

- 1.1 Scope. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

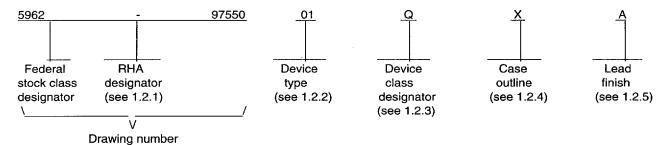

- 1.2 PIN. The PIN is as shown in the following example:

- 1.2.1 RHA designator. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 Device type(s). The device type(s) identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>                               |  |  |

|-------------|----------------|-------------------------------------------------------|--|--|

| 01          | TL16C552AM     | Dual Asynchronous Communications<br>Element With FIFO |  |  |

1.2.3 Device class designator. The device class designator is a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

М

Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535,

appendix A

Q or V

Certification and qualification to MIL-PRF-38535

1.2.4 Case outline(s). The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style          |

|----------------|------------------------|------------------|------------------------|

| ×              | See Figure 1           | 68               | Ceramic quad flat pack |

1.2.5 Lead finish. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 2    |

DSCC FORM 2234 **APR 97**

9004708 0030154 368

#### 1. 3 Absolute maximum ratings. 1/ 2/

| É | 頁 5962-9755001QXA"供应商<br>Supply voltage range (Ⅷ)       |                    |

|---|---------------------------------------------------------|--------------------|

|   |                                                         |                    |

|   | Input voltage (V <sub>N</sub> )                         |                    |

|   | Continuous total power dissipation at 25°C              | 1689 mW <u>3</u> / |

|   | Operating free air temperature range (T <sub>A</sub> )  |                    |

|   | Storage temperature range (T <sub>STG</sub> )           | -65°C to +150°C    |

|   | Thermal resistance, junction-to-case (Peuc)             | 3°C/W              |

|   | Thermal resistance, junction-to-air (P <sub>BJA</sub> ) |                    |

|   | Junction temperature (T <sub>J</sub> )                  | +175 °C            |

|   |                                                         |                    |

#### 1.4 Recommended operating conditions. 2

| Supply voltage range (Vbb)                             | 4.75 V dc to 5.25 V dc      |

|--------------------------------------------------------|-----------------------------|

| High-level input voltage range (V <sub>H</sub> )       | +2.0 V dc to V <sub>D</sub> |

| Low-level input voltage (VL)                           | +0.0 V dc to +0.8 V         |

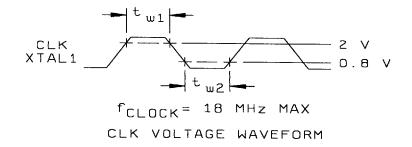

| Clock frequency, (fclock)                              | 16MHz max                   |

| Operating free-air temperature range (T <sub>A</sub> ) | -55 °C to +125 °C           |

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solicitation.

#### **SPECIFICATION**

**MILITARY**

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

#### **STANDARDS**

#### **MILITARY**

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-973 - Configuration Management.

MIL-STD-1835 - Microcircuit Case Outlines.

#### **HANDBOOKS**

#### **MILITARY**

MIL-HDBK-103 - List of Standard Microcircuit Drawings (SMD's).

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

- 1/ Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

- Unless otherwise noted, all voltages are referenced to GND.

- 3/ Above 25°C, derate at a factor of 13.5mW/°C.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 3    |

DSCC FORM 2234 APR 97

9004708 0030155 2T4 **33**

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein, the text of this drawing and the references cited herein the text of this drawing and the references cited herein the text of this drawing and the references cited herein the text of this drawing and the references cited herein the text of this drawing and the references cited herein the text of this drawing and the references cited herein the text of the tex

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

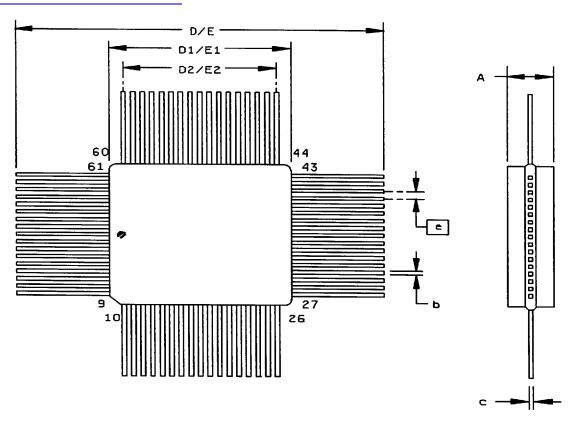

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 Terminal connection(s). The terminal connection(s) shall be as specified on figure 2.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full ambient operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-HDBK-103. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

- 3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

- 3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M</u>. For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-973.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 10 (see MIL-PRF-38535, appendix A).

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>4 |

DSCC FORM 2234 APR 97

**9**004708 0030156 130 **11**

| Test                          | Symbol          | Conditions<br>-55°C ≤ T <sub>A</sub> ≤+125°C<br>unless otherwise specified                                                                                                                                              | Group A subgroups | Device<br>Types | Limits |     | Unit |

|-------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|--------|-----|------|

|                               |                 |                                                                                                                                                                                                                         |                   |                 | Min    | Max |      |

| High level output voltage     | Vон             | $V_{DD} = 5.25 \text{ V}, V_{IH} = 2 \text{ V},$ $V_{IL} = 0.8 \text{ V},$ $I_{OH} = -12 \text{ mA for PD0-PD7},$ $I_{OH} = -4 \text{ mA for all other}$ outputs $1/$                                                   | 1, 2, 3           | All             | 2.4    |     | V    |

| Low-level output voltage      | Vol             | $V_{DD} = 5.25 \text{ V}, V_{IH} = 2 \text{ V},$ $V_{IL} = 0.8 \text{ V},$ $l_{OL} = 12 \text{ mA for PD0-PD7},$ $l_{OL} = 12 \text{ mA for INIT},$ $AFD, STB, and SLIN,$ $l_{OL} = 4 \text{ mA for all other}$ outputs | 1, 2, 3           | All             |        | 0.4 | V    |

| Input current                 | •               | V <sub>DD</sub> = 5.25 V, all other terminals floating 2/                                                                                                                                                               | 1, 2, 3           | All             |        | ±10 | μА   |

| High impedance output current | loz             | $V_{DD}$ = 5.25 V, $V_{O}$ = 0 V with chip de-selected or $V_{O}$ = 5.25 V with chip and write-mode selected 1/                                                                                                         | 1, 2, 3           | All             |        | ±20 | μА   |

| Dynamic supply current        | Ьо              | $V_{DD}$ = 5.25 V, inputs at 0.8 V or 2.0 V, no loads on outputs, $f_{CLK}$ = 8 MHz                                                                                                                                     | 1, 2, 3           | All             |        | 50  | mA   |

|                               |                 | Clock Timing Requireme                                                                                                                                                                                                  | ents <u>3</u> /   | <u>-l</u>       | l      | .1  | L    |

| Pulse duration, CLK↑          | t <sub>w1</sub> | see figure 3                                                                                                                                                                                                            | 9, 10, 11         |                 | 31     |     | ns   |

| Pulse duration, CLK↓          | t <sub>w2</sub> | see figure 3                                                                                                                                                                                                            | 9, 10, 11         |                 | 31     | T   | ns   |

| Pulse duration, RESET         | t <sub>w3</sub> | see figure 3                                                                                                                                                                                                            | 9, 10, 11         |                 | 1000   | 1   | ns   |

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 5    |

**■ 9004708 0030157 077 ■**

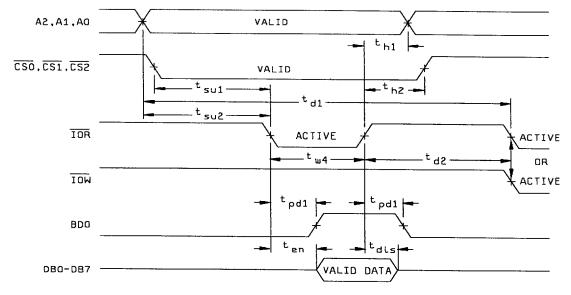

TABLE I. Electrical performance characteristics - Continued. 查询"5962-9755001QXA"供应商 Read Cycle Timing Requirements 3/

| Test                                                             | Symbol Conditions -55°C ≤ T <sub>A</sub> ≤+125°C unless otherwise specified |                            | Group A<br>subgroups | Device<br>Types |     |     | Unit |

|------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------|----------------------|-----------------|-----|-----|------|

|                                                                  |                                                                             | uniess otherwise specified |                      |                 | Min | Max |      |

| Pulse duration, IOR↓                                             | t <sub>w4</sub>                                                             | see figure 3               | 9, 10, 11            |                 | 80  |     | ns   |

| Setup time, CSx valid before IOR ↓ 4/                            | t <sub>su1</sub>                                                            | see figure 3               | 9, 10, 11            |                 | 15  |     | ns   |

| Setup time, A2-A0 valid before IOR ↓ 4/                          | t <sub>su2</sub>                                                            | see figure 3               | 9, 10, 11            |                 | 15  |     | ns   |

| Hold time, A2-A0 valid after IOR ↑ 4/                            | t <sub>h1</sub>                                                             | see figure 3               | 9, 10, 11            |                 | 20  |     | ns   |

| Hold time, CSx valid after IOR↑ 4/                               | t <sub>h2</sub>                                                             | see figure 3               | 9, 10, 11            |                 | 20  |     | ns   |

| Delay time, $t_{su2} + t_{w4} + t_{d2} = 5/$                     | taı                                                                         | see figure 3               | 9, 10, 11            |                 | 175 |     | ns   |

| Delay time, IOR↑ to IOR or IOW↓                                  | t <sub>d2</sub>                                                             | see figure 3               | 9, 10, 11            |                 | 80  |     | ns   |

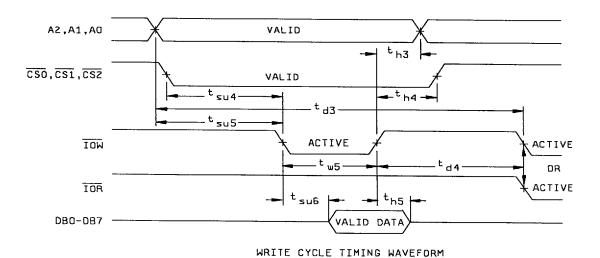

|                                                                  |                                                                             | Write Cycle Timing Require | ments <u>3</u> /     |                 |     |     |      |

| Pulse duration, IOW ↓                                            | t <sub>w5</sub>                                                             | see figure 3               | 9, 10, 11            |                 | 80  |     | ns   |

| Setup time, CSx valid before IOW ↓ 4/                            | t <sub>su4</sub>                                                            | see figure 3               | 9, 10, <b>11</b>     |                 | 15  |     | ns   |

| Setup time, A2-A0 valid before IOW \( \preceq \frac{4}{} \)      | t <sub>su5</sub>                                                            | see figure 3               | 9, 10, 11            |                 | 15  |     | ns   |

| Setup time, DB0-DB7 valid before IOW ↑                           | t <sub>su6</sub>                                                            | see figure 3               | 9, 10, 11            |                 | 15  |     | ns   |

| Hold time, A2-A0 valid after IOW ↑ 4/                            | t <sub>h3</sub>                                                             | see figure 3               | 9, 10, 11            |                 | 20  |     | ns   |

| Hold time, CSx valid after IOW ↑ 4/                              | t <sub>h4</sub>                                                             | see figure 3               | 9, 10, 11            |                 | 20  |     | ns   |

| Hold time, DB0-DB7 valid after IOW ↑                             | t <sub>h5</sub>                                                             | see figure 3               | 9, 10, 11            |                 | 15  |     | ns   |

| Delay time, t <sub>su5</sub> + t <sub>w5</sub> + t <sub>d4</sub> | t <sub>d3</sub>                                                             | see figure 3               | 9, 10, 11            |                 | 175 |     | ns   |

| Delay time, IOW ↑ to IOW or IOR↓                                 | t <sub>d4</sub>                                                             | see figure 3               | 9, 10, 11            |                 | 80  |     | ns   |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>6 |

DSCC FORM 2234 APR 97

9004708 0030158 TO3 **EE**

## TABLE I. <u>Electrical performance characteristics</u> - Continued. 查询"5962-9755001QXA"供应**P**ead Cycle Switching Characteristics <u>3</u>/ <u>6</u>/

| Test                                                           | Symbol           | Symbol Conditions -55°C ≤ T <sub>A</sub> ≤+125°C unless otherwise specified |              | Device<br>Types | Limits |     | Unit           |

|----------------------------------------------------------------|------------------|-----------------------------------------------------------------------------|--------------|-----------------|--------|-----|----------------|

|                                                                | - 10 11          |                                                                             |              |                 | Min    | Max |                |

| Propagation delay time,<br>IOR↓ to BDO↑ or IOR↑ to<br>BDO↓     | t <sub>pd1</sub> | C <sub>L</sub> = 100pF<br>see figure 3                                      | 9, 10, 11    |                 |        | 60  | ns             |

| Enable time, IOR ↓ to DB0-DB7 valid                            | t <sub>en</sub>  | C <sub>L</sub> = 100pF<br>see figure 3                                      | 9, 10, 11    |                 | ***    | 60  | ns             |

| Disable time, IOR↑ to DB0-DB7 released                         | t <sub>dis</sub> | C <sub>L</sub> = 100pF<br>see figure 3                                      | 9, 10, 11    |                 |        | 60  | ns             |

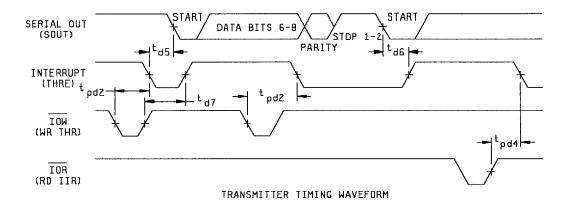

|                                                                |                  | Transmitter Switching Charac                                                | teristics 3/ |                 |        |     |                |

| Delay time, interrupt THRE↓ to SOUT↓ <u>7</u> /                | t <sub>d5</sub>  | see figure 3                                                                | 9, 10, 11    |                 | 8      | 24  | RCLK<br>cycles |

| Delay time, SOUT↓ at start to interrupt THRE↑ 8/               | t <sub>d6</sub>  | see figure 3                                                                | 9, 10, 11    |                 | 8      | 9   | RCLK cycles    |

| Delay time, IOW (WR THR)↑ to interrupt THRE↑ 8/                | t <sub>d7</sub>  | see figure 3                                                                | 9, 10, 11    |                 | 16     | 32  | RCLK cycles    |

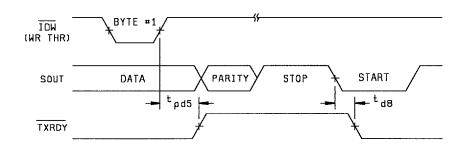

| Delay time, SOUT↓ at start to TXRDY ↓                          | t <sub>d8</sub>  | C <sub>L</sub> = 100pF<br>see figure 3                                      | 9, 10, 11    |                 |        | 8   | RCLK cycles    |

| Propagation delay time,<br>IOW (WR THR)↓ to interrupt<br>THRE↓ | t <sub>pd2</sub> | C <sub>L</sub> = 100pF<br>see figure 3                                      | 9, 10, 11    |                 |        | 140 | ns             |

| Propagation delay time, IOR (RD IIR)↑ to interrupt THRE↓       | t <sub>pd4</sub> | C <sub>L</sub> = 100pF<br>see figure 3                                      | 9, 10, 11    |                 |        | 140 | ns             |

| Propagation delay time, IOW (WR THR)↑ to TXRDY ↑               | t <sub>pd5</sub> | C <sub>L</sub> = 100pF<br>see figure 3                                      | 9, 10, 11    |                 |        | 195 | ns             |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 7    |

DSCC FORM 2234 APR 97

9004708 0030159 94T **=**

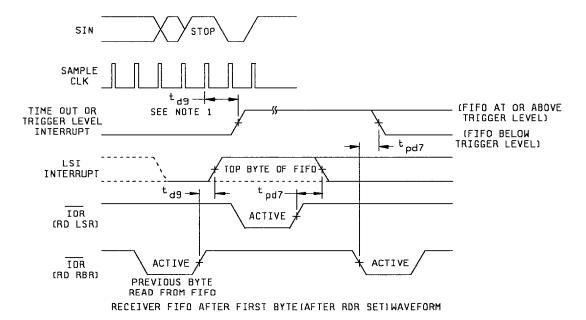

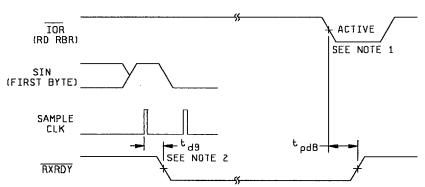

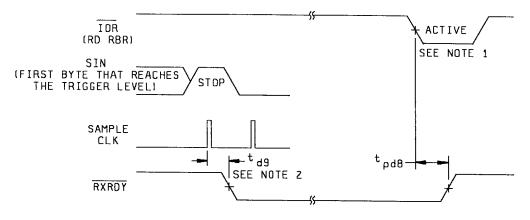

# TABLE I. <u>Electrical Performance Characteristics</u> - Continued 查询"5962-9755001QXA"供应商 Receiver Switching Characteristics <u>3</u>/

| Test                                                                     | Symbol            | Conditions -55°C ≤ T <sub>A</sub> ≤+125°C unless otherwise specified | Group A<br>subgroups   | Device<br>Types | Lin | nits | Unit           |

|--------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------|------------------------|-----------------|-----|------|----------------|

|                                                                          |                   | '                                                                    |                        |                 | Min | Max  |                |

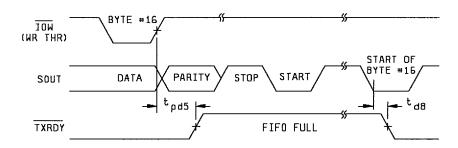

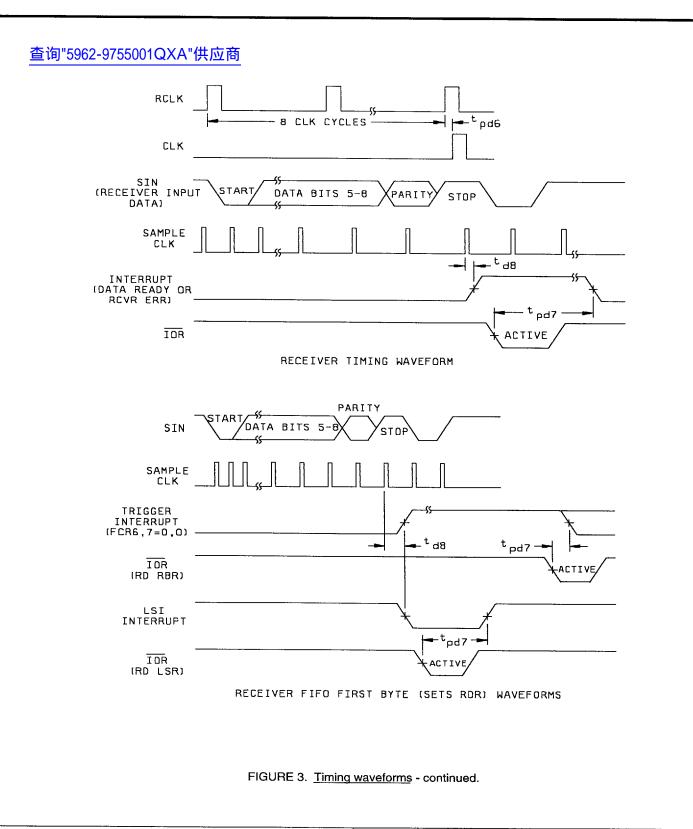

| Delay time, from stop to INT  9/                                         | t <sub>d9</sub>   | see figure 3                                                         | 9, 10, 11              |                 |     | 1    | RCLK<br>cycles |

| Propagation delay time, RCLK↑ to sample CLK↑                             | t <sub>pd6</sub>  | see figure 3                                                         | 9, 10, 11              |                 |     | 100  | ns             |

| Propagation delay time,<br>IOR (RD RBR / RD LSR)↓ to<br>reset interrupt↓ | t <sub>pd7</sub>  | C <sub>L</sub> = 100pF<br>see figure 3                               | 9, 10, 11              |                 |     | 150  | ns             |

| Propagation delay time,<br>IOR (RD RBR)↓ to RXRDY ↑                      | t <sub>pd8</sub>  | see figure 3                                                         | 9, 10, 11              |                 |     | 150  | ns             |

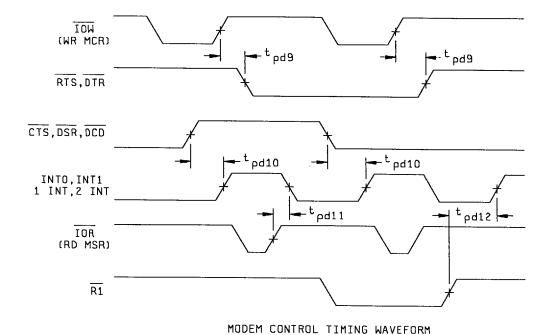

|                                                                          | M                 | lodem Control Switching Char                                         | acteristics <u>3</u> / |                 |     |      |                |

| Propagation delay time, IOW (WR MCR)↑ to RTS or DTR ↓↑                   | t <sub>pd9</sub>  | C <sub>L</sub> = 100pF<br>see figure 3                               | 9, 10, 11              |                 |     | 100  | ns             |

| Propagation delay time,<br>modem input (CTS, DSR)↓↑<br>to interrupt↑     | t <sub>pd10</sub> | C <sub>L</sub> = 100pF<br>see figure 3                               | 9, 10, 11              |                 |     | 170  | ns             |

| Propagation delay time,<br>IOR (RD MSR)↑ to interrupt↓                   | t <sub>pd11</sub> | C <sub>L</sub> = 100pF<br>see figure 3                               | 9, 10, 11              |                 |     | 140  | ns             |

| Propagation delay time, RIT to interrupt                                 | t <sub>pd12</sub> | C <sub>L</sub> = 100pF<br>see figure 3                               | 9, 10, 11              |                 |     | 170  | ns             |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>8 |

DSCC FORM 2234 APR 97

**9**004708 0030160 661

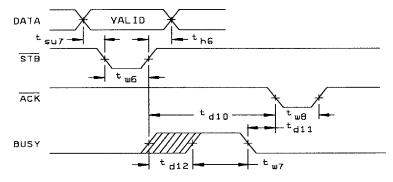

# TABLE I. <u>Electrical Performance Characteristics</u> - Continued 查询"5962-9755001QXA"供应商 Parallel Port Timing Requirements <u>3</u>/

| Test                                                     | Symbol           | Conditions -55°C ≤ T <sub>A</sub> ≤+125°C unless otherwise specified | Group A<br>subgroups | Device<br>Types |     |     | Unit |

|----------------------------------------------------------|------------------|----------------------------------------------------------------------|----------------------|-----------------|-----|-----|------|

|                                                          |                  |                                                                      |                      |                 | Min | Max |      |

| Setup time, data valid before<br>STB ↓                   | t <sub>su7</sub> | see figure 3                                                         | 9, 10, 11            |                 | 1   |     | μs   |

| Hold time, data valid after STB ↑                        | t <sub>h6</sub>  | see figure 3                                                         | 9, 10, 11            |                 | 1   |     | μs   |

| Pulse duration, STB ↓                                    | t <sub>w6</sub>  | see figure 3                                                         | 9, 10, 11            |                 | 1   |     | μS   |

| Delay time, BUSY↑ to ACK ↓ 10/                           | t <sub>d10</sub> | see figure 3                                                         | 9, 10, 11            |                 |     |     | •    |

| Delay time, BUSY↓ to ACK ↓ 10/                           | t <sub>d11</sub> | see figure 3                                                         | 9, 10, 11            |                 |     |     |      |

| Pulse duration, BUSY <sup>↑</sup> 10/                    | t <sub>w7</sub>  | see figure 3                                                         | 9, 10, 11            |                 |     |     |      |

| Pulse duration, ACK ↓ <u>10</u> /                        | t <sub>w8</sub>  | see figure 3                                                         | 9, 10, 11            |                 |     |     |      |

| Delay time, BUSY <sup>↑</sup> after STB <sup>↑</sup> 10/ | t <sub>d12</sub> | see figure 3                                                         | 9, 10, 11            |                 |     |     |      |

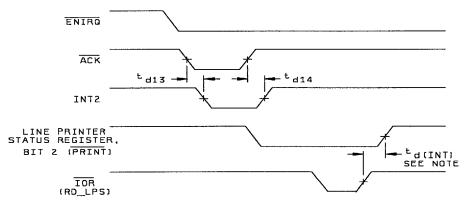

| Delay time, INT2↓ after ACK ↓                            | t <sub>d13</sub> | C <sub>L</sub> = 15pF<br>see figure 3                                | 9, 10, 11            |                 |     | 22  | ns   |

| Delay time, INT2↑ after ACK ↑                            | t <sub>d14</sub> | C <sub>L</sub> = 15pF<br>see figure 3                                | 9, 10, 11            |                 |     | 20  | ns   |

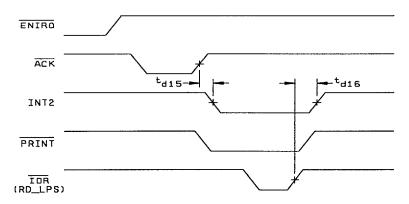

| Delay time, INT2↑ after ACK ↑                            | t <sub>d15</sub> | C <sub>L</sub> = 15pF<br>see figure 3                                | 9, 10, 11            |                 |     | 24  | ns   |

| Delay time, INT2↓ after IOR↑                             | t <sub>d16</sub> | C <sub>L</sub> = 15pF<br>see figure 3                                | 9, 10, 11            |                 | . 1 | 25  | ns   |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                         | SIZE<br><b>A</b> |                | 5962-97550 |

|----------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 9    |

DSCC FORM 2234 APR 97

9004708 0030161 5T8 **33**

#### TABLE I. <u>Electrical Performance Characteristics</u> - Continued 查询"5962-9755001QXA"供应商

- $\underline{1}$ / Excluding STB , INIT , AFD , and SLIN pins because these terminals are open-drain pins with an internal pull-up resistor to  $V_{DD}$  of approximately  $10 \text{K}\Omega$ .

- 2/ Excluding the TRI pin because this input terminal contains an internal pull-down resistor that is approximately 5to.

- 3/ These parameters are guaranteed by design but not tested except for \$\dagger{a}\_1\$, which is tested at 25°C, 125°C, and -55°C.

- 4/ The internal address strobe is always active during this test.

- 5/ In the FIFO mode,  $t_{11} = 425$ nS (min) between reads of the receiver FIFO and the status registers (interrupt identification register and line status register).

- 6/ Vol., Voh, and the external loading determine the charge and discharge time.

- 7/ The acronym THRE stands for transmitter holding register empty.

- 8/ When the transmitter interrupt delay is active, this delay is lengthened by one character time minus the last stop bit time.

- 9/ The receiver data available indicator, the overrun error indicator, the trigger level interrupts, and the active RXRDY indicator are delayed 3 RCLK cycles in the FIFO mode (FCR0 = 1). After the first byte has been received, status indicators (PE, FE, BI) are delayed 3 RCLK cycles. These indicators are updated immediately for any further bytes received after RDRBR goes active. There are 8 RCLK cycle delays for trigger change level interrupts.

- 10/ Limits for these parameters are defined by the printer being used and are not part of this specification.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>10 |

DSCC FORM 2234 APR 97

**-** 9004708 0030162 434 **-**

|          | Dimensions |           |        |        |  |

|----------|------------|-----------|--------|--------|--|

|          | Inches     |           | Millin | neters |  |

| Symbol   | Min        | Max       | Min    | Max    |  |

| A        | 0.134      | 0.154     | 3.404  | 3.912  |  |

| b        | 0.008      | 0.013     | 0.203  | 0.330  |  |

| С        | 0.005      | 0.007     | 0.127  | 0.178  |  |

| D/E      | 1.300      | 1.500     | 33.02  | 38.10  |  |

| D1/E1    | 0.485      | 0.500     | 12.32  | 12.70  |  |

| D2/E2    | 0.400      | 0.400 TYP |        | TYP    |  |

| <u>e</u> | 0.025      | 0.025 BSC |        | BSC    |  |

FIGURE 1. Case outline.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>11 |

DSCC FORM 2234 APR 97

9004708 0030163 370

| <del>*</del> \/==================================== |                 |                 |                 |                 |  |  |  |  |

|-----------------------------------------------------|-----------------|-----------------|-----------------|-----------------|--|--|--|--|

| 查询"5962-97 <mark>55001QXA"供应商</mark> Device Type 01 |                 |                 |                 |                 |  |  |  |  |

|                                                     |                 | Case O          |                 |                 |  |  |  |  |

|                                                     | Terminal Number | Terminal Symbol | Terminal Number | Terminal Symbol |  |  |  |  |

|                                                     | 1               | PMED            | 35              | A0              |  |  |  |  |

|                                                     | 2               | TRI             | 36              | IOW             |  |  |  |  |

|                                                     | 3               | CS1             | 37              | IOR             |  |  |  |  |

| Case Outline X  |                 |                 |                 |  |  |  |  |

|-----------------|-----------------|-----------------|-----------------|--|--|--|--|

| Terminal Number | Terminal Symbol | Terminal Number | Terminal Symbol |  |  |  |  |

| 1               | PMED            | 35              | A0              |  |  |  |  |

| 2               | TRI             | 36              | IOW             |  |  |  |  |

| 3               | CS1             | 37              | IOR             |  |  |  |  |

| 4               | CLK             | 38              | CS2             |  |  |  |  |

| 5               | DSR1            | 39              | RESET           |  |  |  |  |

| 6               | RI1             | 40              | $V_{DD}$        |  |  |  |  |

| 7               | GND             | 41              | SIN0            |  |  |  |  |

| 8               | DCD1            | 42              | TXRDY1          |  |  |  |  |

| 9               | RXRDY0          | 43              | ENIRQ           |  |  |  |  |

| 10              | SOUT1           | 44              | BD0             |  |  |  |  |

| 11              | DTR1            | 45              | INTO            |  |  |  |  |

| 12              | RTS1            | 46              | PD7             |  |  |  |  |

| 13              | CTS1            | 47              | PD6             |  |  |  |  |

| 14              | DB0             | 48              | PD5             |  |  |  |  |

| 15              | DB1             | 49              | PD4             |  |  |  |  |

| 16              | DB2             | 50              | PD3             |  |  |  |  |

| 17              | DB3             | 51              | PD2             |  |  |  |  |

| 18              | DB4             | 52              | PD1             |  |  |  |  |

| 19              | DB5             | 53              | PD0             |  |  |  |  |

| 20              | DB6             | 54              | GND             |  |  |  |  |

| 21              | DB7             | 55              | STB             |  |  |  |  |

| 22              | TXRDY0          | 56              | AFD             |  |  |  |  |

| 23              | V <sub>DD</sub> | 57              | INIT            |  |  |  |  |

| 24              | RTS0            | 58              | SLIN            |  |  |  |  |

| 25              | DTR0            | 59              | INT2            |  |  |  |  |

| 26              | SOUT0           | 60              | INT1            |  |  |  |  |

| 27              | GND             | 61              | RXRDY1          |  |  |  |  |

| 27              | CTS0            | 62              | SIN1            |  |  |  |  |

| 29              | DCD0            | 63              | ERR             |  |  |  |  |

| 30              | RIO             | 64              | V <sub>DD</sub> |  |  |  |  |

| 31              | DSR0            | 65              | SLCT            |  |  |  |  |

| 32              | CS0             | 66              | BUSY            |  |  |  |  |

| 33              | A2              | 67              | PE              |  |  |  |  |

| 34              | A1              | 68              | ACK             |  |  |  |  |

FIGURE 2. <u>Terminal connections</u>.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550  |

|-------------------------------------------------------------|------------------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET<br>12 |

■ 9004708 0030164 207 **■**

| 查询"596½ng/<br>Name | No.      | <u> </u> | Description                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK                | 68       | 1        | Line printer acknowledge. ACK goes low to indicate a successful data transfer has                                                                                                                                                                                                                                                                                  |

| AED                |          |          | taken place. ACK generates a printer port interrupt during its positive transition.                                                                                                                                                                                                                                                                                |

| AFD                | 56       | I/O      | Line printer autofeed. AFD is an open-drain line that provides the printer with an                                                                                                                                                                                                                                                                                 |

|                    |          |          | active-low signal when continuous form paper is to be autofed to the printer. AFD has an internal pull-up resistor to $V_{DD}$ of approximately 10 k $\Omega$ .                                                                                                                                                                                                    |

| An (n = 0 to 3)    | 35,34,33 | i        | Address. The address lines A0-A2 select the internal registers during CPU bus operations.                                                                                                                                                                                                                                                                          |

| BDO                | 44       | 0        | Bus buffer. BDO is an active-high output and is asserted when either serial channe or the parallel port is read. BDO controls the system bus driver.                                                                                                                                                                                                               |

| BUSY               | 66       | 1        | Line printer busy. BUSY is an input line from the printer that goes high when the printer is not ready to accept data.                                                                                                                                                                                                                                             |

| CLK                | 4        | ı        | Clock. CLK is the external clock input to the baud rate divisor of each ACE.                                                                                                                                                                                                                                                                                       |

| CSn (n = 0 to 2)   | 32,3,38  | 1        | Chip select. Each CSn input acts as an enable for the write and read signals for                                                                                                                                                                                                                                                                                   |

| •                  |          |          | serial channels 1 (CS0) and 2 (CS1). CS2 enable the signals to the printer port.                                                                                                                                                                                                                                                                                   |

| CTSn (n = 0 and    | 1) 28,13 | l I      | Clear to send. The logical state of each CTSn terminal is reflected in the CTS bit of                                                                                                                                                                                                                                                                              |

|                    |          |          | the modern status register (CTS is bit 4 of the modern status register, written as                                                                                                                                                                                                                                                                                 |

|                    |          |          | MSR4) of each ACE. A change of state in eitherCTS terminal since the previous                                                                                                                                                                                                                                                                                      |

|                    |          |          | reading of the associated MSR causes the setting of ∆ CTS (MSR0) of each modern                                                                                                                                                                                                                                                                                    |

|                    |          |          | status register.                                                                                                                                                                                                                                                                                                                                                   |

| DBn (n = 0 to 7)   | 14-21    | I/O      | Data bits DB0 - DB7. The data bus provides eight I/O lines with 3-state outputs for the transfer of data, control, and status information between the TL16C552A and the CPU. These lines are normally in the high-impedance state except during read operations. DB0 is the least significant bit (LSB) and is the first serial bit to be received or transmitted. |

| DCDn (n = 0 and 1  | ) 29,8   | 1        | Data carrier detect. DCD is a modem input. Its condition can be tested by the CPL                                                                                                                                                                                                                                                                                  |

|                    |          |          | by reading MSR7 (DCD) of the modern status registers. MSR3 (ADCD) of the                                                                                                                                                                                                                                                                                           |

|                    |          |          | modem status register indicates whether DCD has changed states since the                                                                                                                                                                                                                                                                                           |

|                    |          |          | previous reading of the MSR. DCD has no effect on the receiver.                                                                                                                                                                                                                                                                                                    |

| DSRn (n = 0 and 1  | ) 31,5   | 1        | Data set ready. The logical state of the DSRn terminals is reflected in the MSR5 of                                                                                                                                                                                                                                                                                |

|                    |          |          | its associated modern status register. ΔDSR (MSR1) indicates whether the                                                                                                                                                                                                                                                                                           |

|                    |          |          | associated DSRn terminal has changed states since the previous reading of the MSR.                                                                                                                                                                                                                                                                                 |

| DTRn (n = 0 and    | 1) 25,11 | 0        | Data terminal ready. Each DTRn can be set low by setting MCR0, modem control                                                                                                                                                                                                                                                                                       |

|                    |          |          | register bit 0 of its associated ACE. DTRn is cleared (high) by clearing the DTR bi                                                                                                                                                                                                                                                                                |

|                    |          |          | (MCR0) or whenever a reset occurs. When active (low), DTRn indicates that its                                                                                                                                                                                                                                                                                      |

|                    |          |          | ACE is ready to receive data.                                                                                                                                                                                                                                                                                                                                      |

FIGURE 2a. Terminal description.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                | 5962-97550 |

|-------------------------------------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL | SHEET 13   |

9004708 0030165 143

| 查询readinal         | (55001Q) | (A"供应I |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NO.      | 1/0    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ENIRQ              | 43       | ı      | Parallel port interrupt source mode selection. When ENIRQ is low, the AT mode of interrupts is enabled. In AT mode, INT2 is intentionally connected to ACK. When ENIRQ is tied high, the PS-2 mode of interrupt is enabled and INT2 is internally tied to the inverse of the PRINT bit in the line printer status register. INT2 is latched high on the rising edge of ACK. INT2 is held until the status register is read, which then clears the PRINT status bit and INT2.                          |

| ERR                | 63       | 1      | Line printer error. ERR is an input line from the printer. The printer reports an error by holding ERR low during the error condition.                                                                                                                                                                                                                                                                                                                                                                |

| GND                | 1,27,54  |        | Ground (0 V). All terminals must be tied to GND for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| INIT               | 57       | I/O    | Line printer initialize. INIT is an open-drain that provides the printer with an active-low signal that allows the printer initialization routine to be started. INIT has an internal pull-up resistor to V <sub>DD</sub> of approximately 10 kΩ.                                                                                                                                                                                                                                                     |

| INTn (n = 0 and 1) | 45,60    | 0      | External serial channel interrupt. Each serial channel interrupt 3-state output (enabled by bit 3 of the MCR) goes active (high) when one of the following interrupts has an active (high) condition and is enabled by the interrupt enable register of its associated channel: receiver error flag, received data available, transmitter holding register empty, and modem status. The interrupt is cleared on appropriate service. Upon reset, the interrupt output is in the high-impedance state. |

| INT2               | 59       | 0      | Printer port interrupt. INT2 is an active-high, 3-state output generated by the positive transition of ACK. INT2 is enabled by bit 4 of the write control register.  Upon reset, INT2 is in the high-impedance state. Its mode is also controlled by ENIRQ.                                                                                                                                                                                                                                           |

| IOR                | 37       | I      | Input/output read strobe. IOR is an active-low input that enables the selected channel to output data to the data bus (DB0-DB7). The data output depends on the register selected by the address inputs A0, A1, A2, and chip select. Chip select 0 (CS0) selects ACE #1, chip select 1 (CS1) selects ACE #2, and chip select 2 (CS2) selects the printer port.                                                                                                                                        |

| IOW                | 36       | l      | Input/output write strobe. IOW is an active-low input causing data from the data bus to be input to either ACE or to the parallel port. The destination depends on the register selected by the address inputs A0, A1, A2, and chip selects CS0, CS1, and CS2.                                                                                                                                                                                                                                        |

| PDn (n = 0 to 7)   | 53-46    | 1/0    | Parallel data bits (0-7). PD0-PD7 provide a byte wide input or output port to the system.                                                                                                                                                                                                                                                                                                                                                                                                             |

| PE                 | 67       | -      | Line printer paper empty. PE is an input line from the printer that goes high when the printer runs out of paper.                                                                                                                                                                                                                                                                                                                                                                                     |

| PEMD               | 1        | l      | Printer enhancement mode. When low, PEMD enables the write data register to the PD0 - PD7 lines. A high on PEMD allows direction control of the PD0 - PD7 port by the DIR bit in the control register. PEMD is usually tied low for the printer operation.                                                                                                                                                                                                                                            |

FIGURE 2a. <u>Terminal description</u> - continued.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                | 5962-97550  |

|-------------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |           | REVISION LEVEL | SHEET<br>14 |

■ 9004708 0030166 08T ■

| 查询"6862NAZ55001Q>                 | (A"供应i |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO.                          | I/O    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RESET 39                          | ŀ      | RESET . When low, RESET forces the TL16C552A into an idle mode in which all                                                                                                                                                                                                                                                                                                                                                                                        |

|                                   |        | serial data activities are suspended. The modem control register along with its                                                                                                                                                                                                                                                                                                                                                                                    |

| ŀ                                 |        | associated outputs are cleared. The line status register is cleared except for the                                                                                                                                                                                                                                                                                                                                                                                 |

|                                   |        | THRE and TEMT bits, which are set. All functions of the device remain in the idle                                                                                                                                                                                                                                                                                                                                                                                  |

|                                   |        | state until programmed to resume serial data activities. RESET has a hysteresis                                                                                                                                                                                                                                                                                                                                                                                    |

|                                   |        | level of typically 400 mV.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RTSn (n = 0 and 1) 24,12          | 0      | Request to send. The RTS outputs are set low by setting MCR1 of its UARTs                                                                                                                                                                                                                                                                                                                                                                                          |

|                                   |        | modem control register. Both RTS terminals are reset high by RESET . A low on                                                                                                                                                                                                                                                                                                                                                                                      |

|                                   |        | RTS indicates that its ACE has data ready to transmit. In half-duplex operations,                                                                                                                                                                                                                                                                                                                                                                                  |