# LM5115A Secondary Side Post Regulator/DC-DC Converter with Power-up/Power-down Tracking

#### **General Description**

The LM5115A controller contains all of the features necessary to produce multiple tracking outputs using the Secondary Side Post Regulation (SSPR) technique. The SSPR technique develops a highly efficient and well regulated auxiliary output from the secondary side switching waveform of an isolated power converter. LM5115A can be also used as a standalone DC/DC synchronous buck controller (Refer to Synchronous Buck section). Regulation of the auxiliary output voltage is achieved by leading edge pulse width modulation (PWM) of the main channel duty cycle. Leading edge modulation is compatible with either current mode or voltage mode control of the main output. The LM5115A drives external high-side and low-side NMOS power switches configured as a synchronous buck regulator. A current sense amplifier provides overload protection and operates over a wide common mode input range. Additional features include a low dropout (LDO) bias regulator, error amplifier, precision reference, adaptive dead time control of the gate signals and thermal shutdown.

#### **Features**

- Power-up/Power-down Tracking

- Self-synchronization to main channel output

- Leading edge pulse width modulation

- Valley current Mode control

- Standalone DC/DC synchronous buck mode

- Operates from AC or DC input up to 75V

- Wide 4.5V to 30V bias supply range

- Wide 0.75V to 13.5V output range.

- Top and bottom gate drivers sink 2.5A peak

- Adaptive gate driver dead-time control

- Wide bandwidth error amplifier (4MHz)

- Programmable soft-start

- Thermal shutdown protection

- TSSOP-16 package

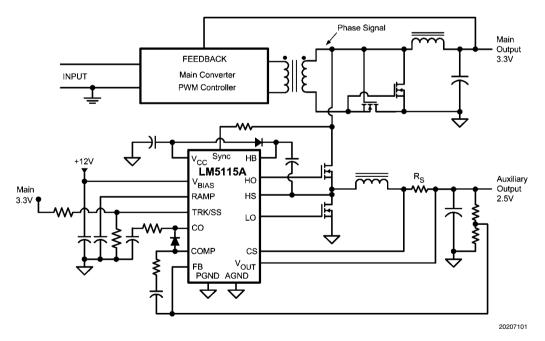

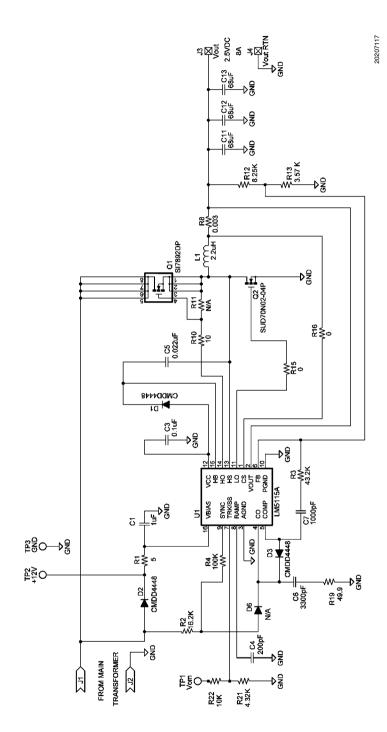

#### **Typical Application Circuit**

FIGURE 1. Simplified Multiple Output Power Converter Utilizing SSPR Technique

#### Connection Diagram 查询"LM5115AMT"供应商

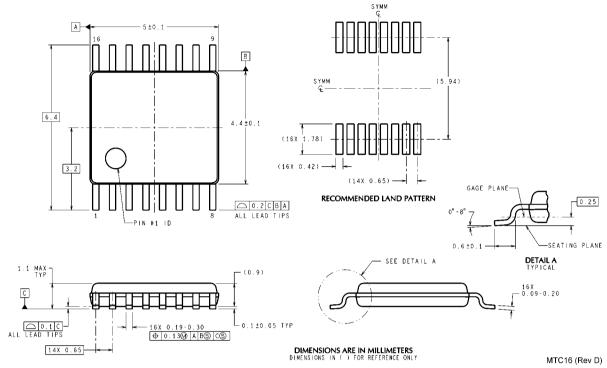

16-Lead TSSOP See NS Package Numbers MTC16

### **Ordering Information**

| Ordering Number | Ordering Number Package Type Ns |       | Supplied As                       |  |  |

|-----------------|---------------------------------|-------|-----------------------------------|--|--|

| LM5115AMT       | TSSOP-16                        | MTC16 | 92 Units Per Anti-Static Tube     |  |  |

| LM5115AMTX      | TSSOP-16                        | MTC16 | 2500 units shipped as Tape & Reel |  |  |

### **Pin Descriptions**

| Pin | Name   | Description                                                                                                                                             | Application Information                                                                                                                                                                                                                                                                                                                          |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CS     | Current Sense amplifier positive input                                                                                                                  | A low inductance current sense resistor is connected between CS and VOUT. Current limiting occurs when the differential voltage between CS and VOUT exceeds 45mV (typical).                                                                                                                                                                      |

| 2   | VOUT   | Current sense amplifier negative input  Connected directly to the output voltage. The curr amplifier operates over a voltage range from 0V to VOUT pin. |                                                                                                                                                                                                                                                                                                                                                  |

| 3   | AGND   | Analog ground                                                                                                                                           | Connect directly to the power ground pin (PGND).                                                                                                                                                                                                                                                                                                 |

| 4   | со     | Current limit output                                                                                                                                    | For normal current limit operation, connect the CO pin to the COMP pin through a diode. CO pin is connected to ground through a resistor in series with a capacitor to provide adequate control loop compensation for the current limit gm amplifier. Leave this pin open to disable the current limit function.                                 |

| 5   | COMP   | Compensation. Error amplifier output                                                                                                                    | COMP pin pull-up is provided by an internal 300uA current source.                                                                                                                                                                                                                                                                                |

| 6   | FB     | Feedback. Error amplifier inverting input                                                                                                               | Connected to the regulated output through the feedback resistor divider and compensation components. The non-inverting input of the error amplifier is internally connected to the SS pin.                                                                                                                                                       |

| 7   | TRK/SS | Tracking/Soft-start control                                                                                                                             | Non-inverting input to error amp with 15 $\mu$ A pull-up current source. Can be used with capacitor for soft-start or tied to external divider of a master output for tracking. TRK/SS is the reference input to the amplifier when the voltage applied to the pin is < 0.75V. For higher inputs, the internal reference controls the amplifier. |

| 8   | RAMP   | PWM Ramp signal                                                                                                                                         | An external capacitor connected to this pin sets the ramp slope for the voltage mode PWM. The RAMP capacitor is charged with a current that is proportional to current into the SYNC pin. The capacitor is discharged at the end of every cycle by an internal MOSFET.                                                                           |

| Pin | Name    | Description                          | Application Information                                                                                                                                                                                                                   |

|-----|---------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | 查询从此151 | \$5/AeA/bhizattobuināut              | A low impedance current input pin. The current into this pin sets the RAMP capacitor charge current and the frequency of an internal oscillator that provides a clock for the free-run (DC input) mode.                                   |

| 10  | PGND    | Power Ground                         | Connect directly to the analog ground pin (AGND).                                                                                                                                                                                         |

| 11  | LO      | Low-side gate driver output          | Connect to the gate of the low-side synchronous MOSFET through a short low inductance path.                                                                                                                                               |

| 12  | VCC     | Output of bias regulator             | Nominal 7V output from the internal LDO bias regulator. Locally decouple to PGND using a low ESR/ESL capacitor located as close to controller as possible.                                                                                |

| 13  | HS      | High-side MOSFET source connection   | Connect to negative terminal of the bootstrap capacitor and the source terminal of the high-side MOSFET.                                                                                                                                  |

| 14  | НО      | High-side gate driver output         | Connect to the gate of high-side MOSFET through a short low inductance path.                                                                                                                                                              |

| 15  | НВ      | High-side gate driver bootstrap rail | Connect to the cathode of the bootstrap diode and the positive terminal of the bootstrap capacitor. The bootstrap capacitor supplies current to charge the high-side MOSFET gate and should be placed as close to controller as possible. |

| 16  | VBIAS   | Supply Bias Input                    | Input to the LDO bias regulator and current sense amplifier that powers internal blocks. Input range of VBIAS is 4.5V to 30V.                                                                                                             |

VBIAS to GND -0.3V to 32V VCC to GND -0.3V to 9V HS to GND -1V to 76V VOUT, CS to GND - 0.3V to 15V All other inputs to GND -0.3V to 7.0V Storage Temperature Range -55°C to +150°C Junction Temperature +150°C ESD Rating HBM (Note 2) 2 kV

#### **Operating Ratings**

VBIAS supply voltage 5V to 30V VCC supply voltage 5V to 7.5V HS voltage 0V to 75V VCC + HS HB voltage Operating Junction Temperature -40°C to +125°C

#### **Typical Operating Conditions**

| Parameter                                       | Min   | Тур | Max  | Units |

|-------------------------------------------------|-------|-----|------|-------|

| Supply Voltage, VBIAS                           | 4.5   |     | 30   | V     |

| Supply Voltage, VCC                             | 4.5   |     | 7    | V     |

| Supply voltage bypass, CVBIAS                   | 0.1   | 1   |      | μF    |

| Reference bypass capacitor, CVCC                | 0.1   | 1   | 10   | μF    |

| HB-HS bootstrap capacitor                       | 0.047 |     |      | μF    |

| SYNC Current Range (VCC = 4.5V)                 | 50    |     | 150  | μΑ    |

| RAMP Saw Tooth Amplitude                        | 1     |     | 1.75 | V     |

| VOUT regulation voltage (VBIAS min = 3V + VOUT) | 0.75  |     | 13.5 | V     |

#### $\textbf{Electrical Characteristics} \quad \text{(Note 3)} \quad \text{Unless otherwise specified, } \\ T_J = -40^{\circ}\text{C to } + 125^{\circ}\text{C}, \\ \text{VBIAS} = 12\text{V}, \\ \text{No Load} \\ \text{Note 3} \\ \text{No Load} \\ \text{Note 3} \\ \text{Note$ on LO or HO.

| Symbol     | Parameter                         | Conditions                                                                       | Min  | Тур  | Max  | Units |

|------------|-----------------------------------|----------------------------------------------------------------------------------|------|------|------|-------|

| VBIAS SUP  | PLY                               |                                                                                  |      |      | , ,  |       |

| Ibias      | VBIAS Supply Current              | F <sub>SYNC</sub> = 200kHz                                                       |      |      | 4    | mA    |

| VCC LOW D  | PROPOUT BIAS REGULATOR            |                                                                                  |      | •    |      |       |

| VccReg     | VCC Regulation                    | VCC open circuit. Outputs not switching                                          | 6.65 | 7    | 7.15 | V     |

|            | VCC Current Limit                 | (Note 4)                                                                         |      | 40   |      | mA    |

|            | VCC Under-voltage Lockout Voltage | Positive going VCC                                                               | 4    |      | 4.5  | V     |

|            | VCC Under-voltage Hysteresis      |                                                                                  | 0.2  | 0.25 | 0.3  | V     |

| TRACK / SC | OFT-START                         |                                                                                  |      |      |      |       |

|            | SS Pull-up Source                 |                                                                                  | 10   | 15   | 20   | μΑ    |

|            | SS Discharge Impedance            |                                                                                  |      | 140  |      | Ω     |

| ERROR AM   | PLIFIER and FEEDBACK REFERENC     | E                                                                                |      |      |      |       |

| VREF       | FB Reference Voltage              | Measured at FB pin                                                               | .737 | .750 | .763 | V     |

|            | FB Input Bias Current             | FB = 2V                                                                          |      | 0.2  | 0.5  | μΑ    |

|            | COMP Source Current               |                                                                                  |      | 300  |      | μΑ    |

|            | Open Loop Voltage Gain            |                                                                                  |      | 60   |      | dB    |

| GBW        | Gain Bandwidth Product            |                                                                                  |      | 4    |      | MHz   |

| Vio        | Input Offset Voltage              |                                                                                  |      | 22   |      | mV    |

|            | COMP Offset                       | Threshold for V <sub>HO</sub> = high RAMP = CS = VOUT = 0V                       |      | 2    |      | V     |

|            | RAMP Offset                       | Threshold for $V_{HO}$ = high COMP = 1.5V,<br>CS = VOUT = 0V                     |      | 1.0  |      | V     |

| CURRENT S  | SENSE AMPLIFIER                   |                                                                                  |      | •    | ,    |       |

|            | Current Sense Amplifier Headroom  | Headroom = V <sub>bias</sub> – Vout<br>V <sub>bias</sub> = 4.5 V and Vout= 1.5 V | 3    |      |      | V     |

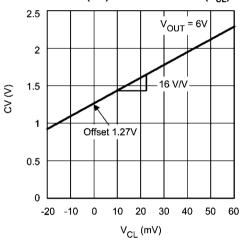

|            | Current Sense Amplifier Gain      |                                                                                  |      | 16   |      | V/V   |

|            | Output DC Offset                  |                                                                                  |      | 1.27 |      | V     |

|            | Amplifier Bandwidth               |                                                                                  |      | 500  |      | kHz   |

| Symbol             | Parameter                        | Conditions                                                       | Min | Тур  | Max  | Units  |

|--------------------|----------------------------------|------------------------------------------------------------------|-----|------|------|--------|

| URREN              | <b>渝IIL</b> M5115AMT"供应商         |                                                                  |     |      |      |        |

|                    | Slow ILIMIT Amp Transconductance |                                                                  |     | 5    |      | mA / V |

|                    | Overall Transconductance         |                                                                  |     | 90   |      | mA / V |

|                    | Slow ILimit Threshold            | $V_{CL} = V_{CS} - V_{VOUT}$<br>VOUT = 6V and CO/COMP = 1.5V     | 39  | 45   | 51   | mV     |

|                    | Slow ILimit Foldback             | $V_{CL} = V_{CS} - V_{VOUT}$<br>VOUT = 0V and CO/COMP = 1.5V     | 34  | 39   | 46   | mV     |

|                    | Fast ILimit Pull-Down Current    | Vds = 2V                                                         |     | 45   |      | mA     |

|                    | Fast ILimit Threshold            |                                                                  |     | 60   |      | mV     |

| V <sub>CLNEG</sub> | Negative Current Limit           | VOUT = 6V<br>$V_{CL} = V_{CS} - V_{VOUT}$ to cause LO to shutoff |     | -17  |      | mV     |

|                    | CO Clamp Voltage                 |                                                                  | 5.5 | 6    | 6.5  | V      |

|                    | ICO Pull-Up Current              |                                                                  |     | 15   |      | μΑ     |

| AMP GEN            | ERATOR                           |                                                                  |     |      |      |        |

|                    | SYNC Input Impedance             |                                                                  |     | 2.5  |      | kΩ     |

|                    | SYNC Threshold                   | End of cycle detection threshold                                 |     | 20   |      | μΑ     |

|                    | Free Run Mode Peak Threshold     | RAMP peak voltage with dc current applied to SYNC.               |     |      | 2.35 | V      |

|                    | Current Mirror Gain              | Ratio of RAMP charge current to SYNC input current.              | 2.7 |      | 3.3  | A/A    |

|                    | Discharge Impedance              |                                                                  |     | 100  |      | Ω      |

| OW-SIDE            | GATE DRIVER                      |                                                                  |     | ,    | ,    |        |

| V <sub>OLL</sub>   | LO Low-state Output Voltage      | I <sub>LO</sub> = 100mA                                          |     | 0.15 | 0.5  | V      |

| V <sub>OHL</sub>   | LO High-state Output Voltage     | $I_{LO}$ = -100mA, $V_{OHL}$ = $V_{CC}$ - $V_{LO}$               |     | 0.35 | 0.8  | V      |

|                    | LO Rise Time                     | C <sub>LOAD</sub> = 1000pF                                       |     | 15   |      | ns     |

|                    | LO Fall Time                     | C <sub>LOAD</sub> = 1000pF                                       |     | 12   |      | ns     |

| I <sub>OHL</sub>   | Peak LO Source Current           | V <sub>LO</sub> = 0V                                             |     | 2    |      | Α      |

| I <sub>OLL</sub>   | Peak LO Sink Current             | V <sub>LO</sub> = 12V                                            |     | 2.5  |      | Α      |

|                    | GATE DRIVER                      | 1                                                                |     |      |      |        |

| V <sub>OLH</sub>   | HO Low-state Output Voltage      | I <sub>HO</sub> = 100mA                                          |     | 0.15 | 0.5  | V      |

| V <sub>OHH</sub>   | HO High-state Output Voltage     | $I_{HO}$ = -100mA, $V_{OHH}$ = $V_{HB}$ $-V_{HO}$                |     | 0.35 | 0.8  | V      |

| OTHT               | HO Rise Time                     | C <sub>LOAD</sub> = 1000pF                                       |     | 15   |      | ns     |

|                    | HO High-side Fall Time           | C <sub>LOAD</sub> = 1000pF                                       |     | 12   |      | ns     |

| I <sub>OHH</sub>   | Peak HO Source Current           | $V_{HO} = 0V$                                                    |     | 2    |      | A      |

| I <sub>OLH</sub>   | Peak HO Sink Current             | V <sub>HO</sub> = 12V                                            |     | 2.5  |      | A      |

|                    | G CHARACTERISITCS                | по :                                                             |     | 10   | 1    |        |

|                    | LO Fall to HO Rise Delay         | C <sub>LOAD</sub> = 0                                            |     | 40   |      | ns     |

|                    | HO Fall to LO Rise Delay         | $C_{LOAD} = 0$                                                   |     | 50   |      | ns     |

|                    | SYNC Fall to HO Fall Delay       | $C_{LOAD} = 0$                                                   |     | 120  |      | ns     |

|                    | SYNC Rise to LO Fall Delay       | $C_{LOAD} = 0$                                                   |     | 1.20 |      | 110    |

| Symbol             | Parameter                   | Conditions  | Min | Тур | Max | Units |  |

|--------------------|-----------------------------|-------------|-----|-----|-----|-------|--|

| THER MALS          | 章nermMt5sl15rhowwi供应商       |             |     |     |     |       |  |

| T <sub>SD</sub>    | Thermal Shutdown Temp.      |             | 150 | 165 |     | °C    |  |

|                    | Thermal Shutdown Hysteresis |             |     | 25  |     | °C    |  |

| THERMAL RESISTANCE |                             |             |     |     |     |       |  |

| $\theta_{JA}$      | Junction to Ambient         | MTC Package |     | 125 |     | °C/W  |  |

| $\theta_{JA}$      | Junction to Ambient         | SDA Package |     | 32  |     | °C/W  |  |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: The human body model is a 100 pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin.

Note 3: Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate National's Average Outgoing Quality Level (AOQL).

Note 4: Device thermal limitations may limit usable range.

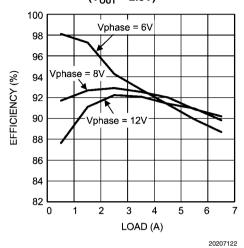

#### **Typical Performance Characteristics**

查询"LM5115AMT"供应商

# Efficiency vs. Load Current and Vphase (V<sub>OUT</sub> = 2.5V)

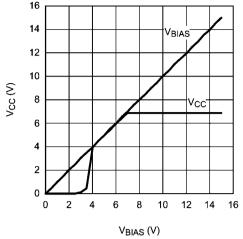

# $V_{CC}$ Regulator Start-up Characteristics, $V_{CC}$ vs. $V_{BIAS}$

20207104

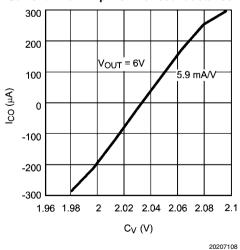

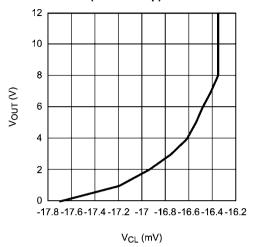

#### Current Value (CV) vs. Current Limit (V<sub>CL</sub>)

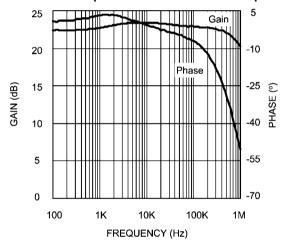

**Current Sense Amplifier Gain and Phase vs. Frequency**

20207107

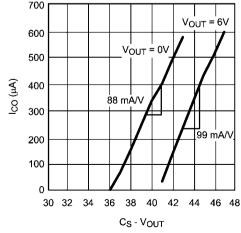

#### **Current Error Amplifier Transconductance**

Overall Current Amplifier Transconductance

20207109

7

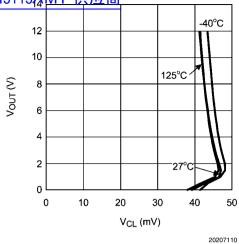

# Common Mode Output Voltage vs. Positive Current Limit Common Mode Output Voltage vs. Negative Current Limit (Room Temp)

20207111

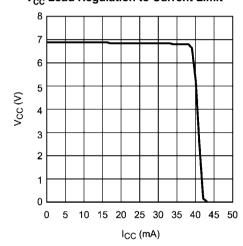

${\rm V}_{\rm CC}$  Load Regulation to Current Limit

20207105

8

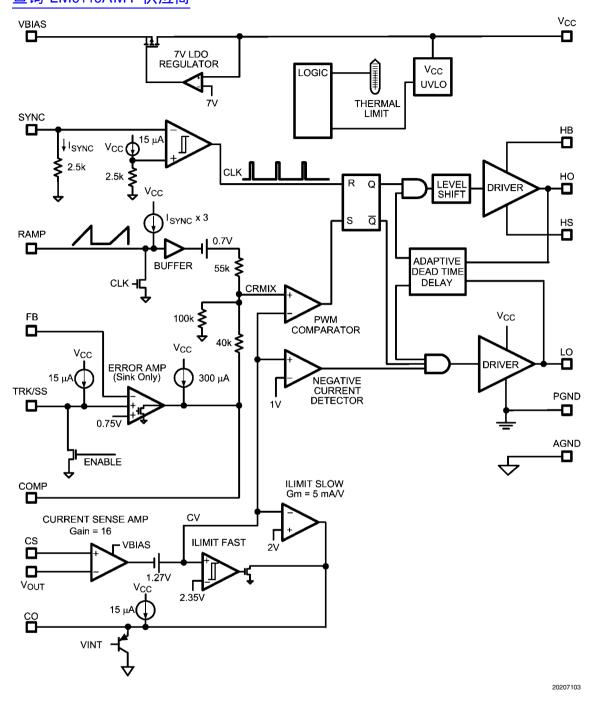

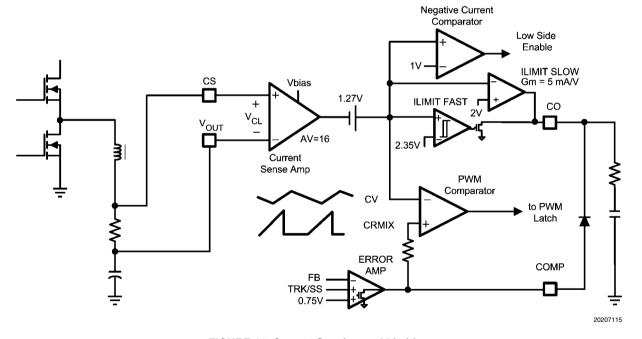

#### Block Diagram 查询"LM5115AMT"供应商

9

### Detailed Operating Description

LM5115AMT"供应商 TM5115A controller contains all of the features necessary to implement multiple output power converters utilizing the Secondary Side Post Regulation (SSPR) technique. The SSPR technique develops a highly efficient and well regulated auxiliary output from the secondary side switching waveform of an isolated power converter. Regulation of the auxiliary output voltage is achieved by leading edge pulse width modulation (PWM) of the main channel duty cycle. Leading edge modulation is compatible with either current mode or voltage mode control of the main output. The LM5115A drives external high-side and low-side NMOS power switches configured as a synchronous buck regulator. A current sense amplifier provides overload protection and operates over a wide common mode input range from 0V to 13.5V. Additional features include a low dropout (LDO) bias regulator, error amplifier, precision reference, adaptive dead time control of the gate driver signals and thermal shutdown.

#### Low Drop-Out Bias Regulator (VCC)

The LM5115A contains an internal LDO regulator that operates over an input supply range from 4.5V to 30V. The output of the regulator at the VCC pin is nominally regulated at 7V and is internally current limited to 40mA. VCC is the main supply to the internal logic, PWM controller, and gate driver circuits. When power is applied to the VBIAS pin, the regulator is enabled and sources current into an external capacitor connected to the VCC pin. The recommended output capacitor range for the VCC regulator is 0.1uF to 100uF. When the voltage at the VCC pin reaches the VCC under-voltage lockout threshold of 4.25V, the controller is enabled. The controller is disabled if VCC falls below 4.0V (250mV hysteresis). In applications where an appropriate regulated dc bias supply is available, the LM5115A controller can be powered directly through the VCC pin instead of the VBIAS pin. In this configuration, it is recommended that the VCC and the VBIAS pins be connected together such that the external bias voltage is applied to both pins. The allowable VCC range when biased from an external supply is 4.5V to 7V.

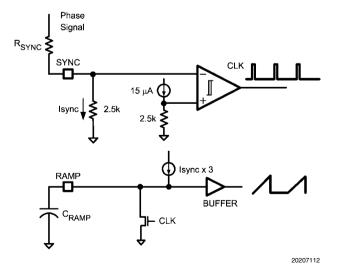

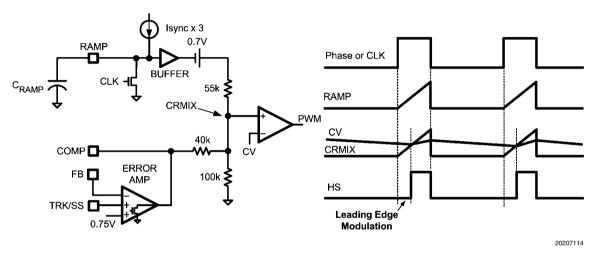

#### Synchronization (SYNC) and Feed-Forward (RAMP)

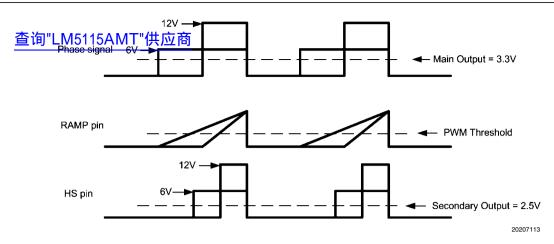

The pulsing "phase signal" from the main converter synchronizes the PWM ramp and gate drive outputs of the LM5115A. The phase signal is the square wave output from the transformer secondary winding before rectification (Figure 1). A resistor connected from the phase signal to the low impedance SYNC pin produces a square wave current (ISYNC) as shown in Figure 2. A current comparator at the SYNC input monitors I<sub>SYNC</sub> relative to an internal 15µA reference. When  $I_{\mbox{\scriptsize SYNC}}$  exceeds 15  $\mu\mbox{\scriptsize A},$  the internal clock signal (CLK) is reset and the capacitor connected to the RAMP begins to charge. The current source that charges the RAMP capacitor is equal to 3 times the I<sub>SYNC</sub> current. The falling edge of the phase signal sets the CLK signal and discharges the RAMP capacitor until the next rising edge of the phase signal. The RAMP capacitor is discharged to ground by a low impedance (100 $\Omega$ ) n-channel MOSFET. The input impedance at SYNC pin is  $2.5k\Omega$  which is normally much smaller than the external SYNC pin resistance.

The RAMP and SYNC functions illustrated in Figure 2 provide line voltage feed-forward to improve the regulation of the auxiliary output when the input voltage of the main converter changes. Varying the input voltage to the main converter produces proportional variations in amplitude of the phase signal. The main channel PWM controller adjusts the pulse width of the phase signal to maintain constant volt\*seconds and a regulated main output as shown in Figure 3. The variation of the phase signal amplitude and duration are reflected in the slope and duty cycle of the RAMP signal of the LM5115A  $(I_{SYNC} \alpha \text{ phase signal amplitude})$ . As a result, the duty cycle of the LM5115A is automatically adjusted to regulate the auxiliary output voltage with virtually no change in the PWM threshold voltage. Transient line regulation is improved because the PWM duty cycle of the auxiliary converter is immediately corrected, independent of the delays of the voltage regulation loop.

FIGURE 2. Line Feed-Forward Diagram

FIGURE 3. Line Feed-Forward Waveforms

The recommended SYNC input current range is  $50\mu A$  to  $150\mu A$ . The SYNC pin resistor ( $R_{SYNC}$ ) should be selected to set the SYNC current ( $I_{SYNC}$ ) to  $150\mu A$  with the maximum phase signal amplitude,  $V_{PHASE(max)}$ . This will guarantee that  $I_{SYNC}$  stays within the recommended range over a 3:1 change in phase signal amplitude. The SYNC pin resistor is therefore:

$$R_{SYNC} = (V_{PHASE(max)} / 150\mu A) - 2.5k\Omega$$

Once  $I_{SYNC}$  has been established by selecting  $R_{SYNC}$ , the RAMP signal slope/amplitude may be programmed by selecting the proper RAMP pin capacitor value. The RAMP signal slope should be selected to provide adequate slope compensation for the Valley current mode control scheme (Please refer to the Valley current mode section). The recommended peak amplitude of the ramp waveform is 1.75V.

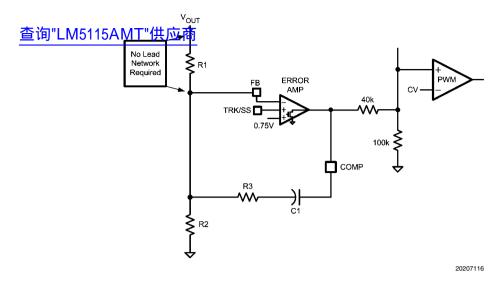

# Error Amplifier and Soft-Start (FB, CO, COMP & TRK/SS)

An internal wide bandwidth error amplifier is provided within the LM5115A for voltage feedback to the PWM controller. The amplifier's inverting input is connected to the FB pin. The output of the auxiliary converter is regulated by connecting a voltage setting resistor divider between the output and the FB pin. Loop compensation networks are connected between the FB pin and the error amplifier output (COMP). The amplifier has two non-inverting inputs. The first non-inverting input connects to a 0.75V bandgap reference while The second non-inverting input connects to the TRK/SS pin and it has 15 μA pull-up current source. The TRK/SS pin can be tied to an external resistor divider from the master output for tracking, or it can be tied to a capacitor for soft-start . TRK/SS is the reference input to the amplifier when the voltage applied to the pin is < 0.75V. For higher inputs, the internal reference controls the amplifier. When the VCC voltage is below the UVLO threshold, the TRK/SS pin is discharged to ground. When VCC rises and exceeds the positive going UVLO threshold (4.25V), the TRK/SS pin is released and allowed to rise. If an external capacitor is connected to the TRK/SS pin, it will be charged by the internal 15uA pull-up current source to gradually increase the non-inverting input of the error amplifier to 0.75V. During start-up, the output of the LM5115A converter will follow the following equation:

$$VOUT(t) = VOUT(final) \times 15 \mu A \times t / (.75 Vx Css)$$

Where

Css = external Soft-Start capacitor

VOUT(final) = regulator output set point

Pull-up current for the error amplifier output is provided by an internal 300µA current source. The PWM threshold signal at the COMP pin can be controlled by either the open drain error amplifier or the open drain current amplifier connected through the CO pin to COMP. Since the internal error amplifier is configured as an open drain output it can be disabled by connecting FB to ground. The current sense amplifier and current limiting function will be described in a later section.

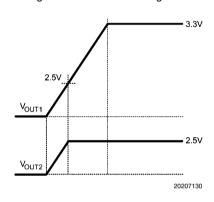

#### Power-up/Power-downTracking

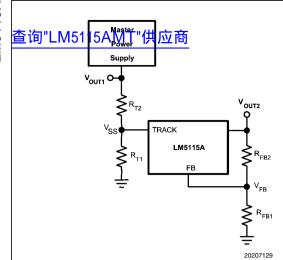

The LM5115A can track the output of a master power supply during soft start by connecting a resistor divider to the TRACK pin (Figure 4). Therefore, the output voltage slew rate of the LM5115A will be controlled by the master supply for loads that require precise sequencing. In order to track properly the output voltage of the LM5115A must be lower than the output voltage of the master supply.

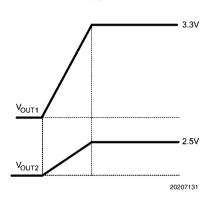

One way to use the tracking feature is to design the tracking resistor divider so that the master supply output voltage (VOUT1) and the LM5115A output voltage (VOUT2) both rise together and reach their target values at the same time. For this case, the equation governing the values of the tracking divider resistors RT1 and RT2 is:

$$R_{T1} = \frac{0.8 \times R_{T2}}{V_{OUT1} - 0.8}$$

A value of 10k $\Omega$  (1%) is recommended for RT2 as a good compromise between high precision and low quiescent current through the divider. If the master supply voltage was 3.3V and the LM5115A output voltage was 2.5 V, then the value of RT1 needed to give the two supplies identical soft start times would be 2.94 k $\Omega$  (1%). The timing diagram and waveforms for the equal soft start time configuration are shown in Figure 5 and Figure 6.

FIGURE 4.

FIGURE 5.

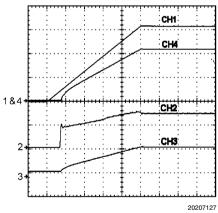

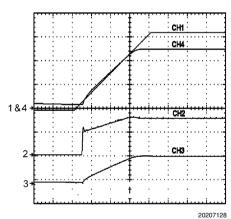

Vphase = 10V

CH1 = Master output, 1V/Div

CH2 = COMP, 5/Div

CH3 = lout, 1A/Div

CH4 = SSPR Output (Slave), 1V/Div

Horizontal Resolution= 200 µs/Div

FIGURE 6. Tracking with Equal Soft Start Time

Alternatively, the tracking feature can be used to create equal slew rates between the output voltages of the master supply and the LM5115A. This method ensures that the output voltage of the LM5115A always reaches regulation before the output voltage of the master supply. In this case, the tracking resistors can be determined based on the following equation:

$$R_{T1} = \frac{0.8 \times R_{T2}}{V_{OUT2} - 0.8}$$

Again, a value of  $10k\Omega$  1% is recommended for RT2. For the case of VOUT1 = 3.3V and VOUT2 = 2.5V, RT1 should be 4.32 k $\Omega$  1%. The timing diagram and the waveforms for equal slew rates configuration are shown in Figure 7 and Figure 8.

FIGURE 7.

Vphase = 10V

CH1 = Master output, 1V/Div

CH2 = COMP, 5/Div

CH3 = lout, 1A/Div

CH4 = SSPR Output (Slave), 1V/Div

Horizontal Resolution= 200 µs/Div

FIGURE 8. Tracking with Equal Slew Rate

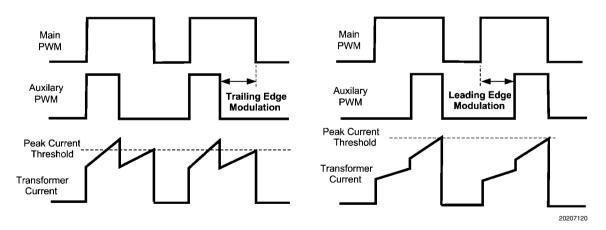

### Leading Edge Pulse Width Modulation

Unlike conventional voltage mode controllers, the LM5115A implements leading edge pulse width modulation. A current source equal to 3 times the I<sub>SYNC</sub> current is used to charge the capacitor connected to the RAMP pin as shown in *Figure 9*. The ramp signal and the output of the error amplifier (COMP) are combined through a resistor network to produce a voltage ramp with variable dc offset (CRMIX in *Figure 9*). The high-side MOSFET which drives the HS pin is held in the off state at the beginning of the phase signal. When the voltage of CRMIX exceeds the internal threshold voltage CV, the PWM comparator turns on the high-side MOSFET. The HS pin rises and the MOSFET delivers current from the main converter phase signal to the output of the auxiliary regulator. The PWM cycle ends when the phase signal falls and power is no longer supplied to the drain of the high-side MOSFET.

Leading edge modulation of the auxiliary PWM controller is required if the main converter uses peak current mode control. If trailing edge modulation were used, the additional load on the transformer secondary from the auxiliary channel would be drawn only during the first portion of the phase signal pulse. Referring to *Figure 10*, the turn-off of the high-side MOSFET of the auxiliary regulator would create a non-monotonic negative step in the transformer current. This negative current step would produce instability in a peak current mode controller. With leading edge modulation, the additional load presented by the auxiliary regulator on the transformer secondary will be present during the latter portion of the phase signal. This positive step in the phase signal current can be accommodated by a peak current mode controller without instability.

FIGURE 9. Synchronization and Leading Edge Modulation

FIGURE 10. Leading versus Trailing Edge Modulation

#### Valley Current Mode Control

有"LM5115AMT"供应商 National Section of the second of the sec benefits of valley current mode control in conjunction with leading edge modulation to correct changes in output voltage due to line and load transients. Contrary to peak current mode control, valley current mode control turns on the high-side MOSFET when the Inductor valley current reaches a programmable threshold. This programmable threshold (CRMIX) is the sum of the output of voltage error amplifier and the RAMP signal generated at the RAMP pin. Valley current mode control experiences sub-harmonic oscillation when the duty ratio, D, is less than or equal to 50%. Therefore, adequate slope compensation is needed for the proper operation across the full range of the duty ratio. The RAMP signal is proportional to the input voltage and it provides the required slope compensation for the valley current mode scheme. The desired RAMP pin capacitance can be calculated from the following equation:

$$C_{RAMP} = (0.05 \text{ x L}) / (R_{SYNC} \text{ x } R_{SENSE})$$

Where L is the power inductor,  $R_{\rm SYNC}$  is the SYNC pin resistor and  $R_{\rm SENSE}$  is the current sense resistor.

The current sense amplifier shown in *Figure 11* monitors the inductor current as it flows through a sense resistor connected between CS and VOUT. The voltage gain of the sense amplifier is nominally equal to 16. The current sense output signal is shifted by 1.27V to produce the internal CV reference signal. The CV signal is applied to the negative input of the PWM comparator and compared to CRMIX as illustrated in *Figure 11*. Therefore when CRMIX exceeds the PWM thresh-

old (CV), the PWM comparator turns on the high-side MOS-FET. Insure that the Vbias voltage is at least 3V above the regulated output voltage (VOUT) to provide enough headroom for the current sense amplifier.

Valley current mode control improves the control loop stability and bandwidth. It also eliminates the R-C lead network in the feedback path that is normally required with voltage mode control (*Figure 12*). Eliminating the lead network not only simplifies the compensation, but also reduces sensitivity to output noise that could pass through the lead network to the error amplifier.

The design of the voltage feedback path through the error amp begins with the selection of R1 and R2 in *Figure 12* to set the regulated output voltage. The steady state output voltage after soft-start is determined by the following equation:

$$VOUT(final) = 0.75V \times (1+R1/R2)$$

The parallel impedance of the R1, R2 resistor divider should be approximately  $2k\Omega$  (between  $0.5k\Omega$  and  $5k\Omega$ ). Lower resistance values may not be properly driven by the error amplifier output and higher feedback resistances can introduce noise sensitivity. The next step in the design process is selection of R3, which sets the ac gain of the error amplifier.

The capacitor C1 is connected in series with R3 to increase the dc gain of the voltage regulation loop and improve output voltage accuracy. The corner frequency set by R3 x C1 should be less than 1/10th of the cross-over frequency of the overall converter such that capacitor C1 does not add phase lag at the crossover frequency.

FIGURE 11. Current Sensing and Limiting

FIGURE 12. Voltage Sensing and Feedback

#### **Current Limiting (CS, CO and VOUT)**

Current limiting is implemented through the current sense amplifier as illustrated in Figure 11. The current sense amplifier monitors the inductor current that flows through a sense resistor connected between CS and VOUT. The voltage gain of the current sense amplifier is nominally equal to 16. The output of current sense signal is shifted by 1.27V to produce the internal CV reference signal. The CV signal drives two current limit amplifiers. Both of the current limit amplifiers have open drain (sink only) output stages which are connected to the CO pin. The CO pin is typically connected to the COMP pin through a diode (the cathode is connected to the CO pin and the anode is connected to the COMP pin). The slow current limit amplifier has a nominal transconductance of 5 mA/V and provides constant current mode operation at the desired current limit set point. The fast current limit amplifier has nominal current pull-down capability of 100mA and provides protection against fast over-current conditions. During normal operation, the voltage error amplifier controls the COMP pin voltage which adjusts the PWM duty cycle by varying the internal CRMIX level. However when the current sense input voltage,  $V_{CL}$ , exceeds 45mV, the slow current limit amplifier gradually pulls down on COMP through the CO pin. Pulling COMP low reduces the CRMIX signal and thereby reducing the operating duty cycle. By controlling the operating duty cycle, the slow current limit amplifier will force a constant current mode of operation at the desired current limit set point (Figure 13). A resistor in series with a capacitor are connected from the CO Pin to ground to provide adequate control loop compensation for the slow current limit (Figure 11). The desired current limit set point, ILimit, can be programmed by selecting the proper current sense resistor, R<sub>SENSE</sub>, using the following equation:

#### $R_{SENSE} = 0.045 \text{ V/ ILimit}$

In the event that the current sense input voltage,  $V_{CL}$ , exceeds 60mV, the fast current limit amplifier will pull down hard on COMP through the CO pin. This will reduce the CRMIX signal to a voltage below the CV signal level. Therefore, the PWM

comparator will inhibit output pulses. Once the fault condition is removed, the fast current limit amplifier will release COMP. Therefore, the CRMIX signal will increase to a normal operating threshold and the switching will resume (*Figure 14*). A current limit fold-back feature is provided by the LM5115A to reduce the peak output current delivered to a shorted load. When the common mode input voltage to the current sense amplifier (CS and VOUT pins) falls below 2V, the current limit threshold is reduced from the normal level. At common mode voltages > 2V, the current limit threshold is nominally 45mV. When VOUT is reduced to 0 V the current limit threshold drops to 39mV to reduce stress on the inductor and power MOSFETs.

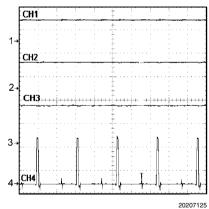

#### Vphase=10V

CH1 = CO, 5V/Div

CH2 = COMP, 5/Div

CH3 = lout, 5A/Div

CH4 = SSPR Switch Signal, 5V/Div

Horizontal Resolution= 2 µs/Div

FIGURE 13. SSPR Steady State Current Limit (Output Shorted)

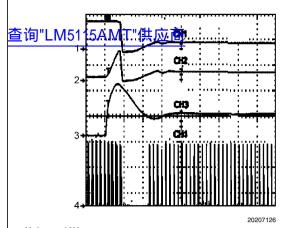

#### Vphase=10V

CH1 = CO, 5V/Div

CH2 = COMP, 5/Div

CH3 = lout, 10A/Div

CH4 = SSPR Switch Signal, 4V/Div

Horizontal Resolution= 20 µs/Div

FIGURE 14. SSPR Short Circuit Transient (No-Load to Short-Circuit)

#### **Negative Current Limit**

Under certain conditions synchronous buck regulators are capable of sinking current from the output capacitors. This energy is stored in the inductor and returned to the input source. The LM5115A detects this current reversal by detecting a negative voltage being developed across the current sense resistor. The intent of this negative current comparator is to protect the low-side MOSFET from excessive currents. Excessive negative current can also lead to a large positive voltage spike on the HS pin at the turn-off of the low-side MOSFET. This voltage spike may damage the chip if its magnitude exceeds the maximum voltage rating of the part. The negative current comparator threshold is sufficiently negative to allow inductor current to reverse at no load or light load conditions. It is not intended to support discontinuous conduction mode with diode emulation by the low-side MOSFET. The negative current comparator shown in Figure 11 monitors the CV signal and compares this signal to a fixed 1V threshold. This corresponds to a negative V<sub>CL</sub> voltage between CS and VOUT of -17mV. The negative current limit comparator turns off the low-side MOSFET for the remainder of the cycle when the  $V_{CL}$  input falls below this threshold.

#### **Gate Driver Outputs (HO & LO)**

The LM5115A provides two gate driver outputs, the floating high-side gate driver HO and the synchronous rectifier low-side driver LO. The low-side driver is powered directly by the VCC regulator. The high-side gate driver is powered from a bootstrap capacitor connected between HB and HS. An external diode connected between VCC and HB charges the bootstrap capacitor when the HS is low. When the high-side MOSFET is turned on, HB rises with HS to a peak voltage equal to VCC +  $\rm V_{HS}$  -  $\rm V_{D}$  where  $\rm V_{D}$  is the forward drop of the external bootstrap diode. Both output drivers have adaptive

dead-time control to avoid shoot through currents. The adaptive dead-time control circuit monitors the state of each driver to ensure that one MOSFET is turned off before the other is turned on. The HB and VCC capacitors should be placed close to the pins of the LM5115A to minimize voltage transients due to parasitic inductances and the high peak output currents of the drivers. The recommended range of the HB capacitor is  $0.047\mu F$  to  $0.22\mu F$ .

Both drivers are controlled by the PWM logic signal from the PWM latch. When the phase signal is low, the outputs are held in the reset state with the low-side MOSFET on and the high-side MOSFET off. When the phase signal switches to the high state, the PWM latch reset signal is de-asserted. The high-side MOSFET remains off until the PWM latch is set by the PWM comparator (CRMIX > CV as shown in *Figure 9*). When the PWM latch is set, the LO driver turns off the low-side MOSFET and the HO driver turns on the high-side MOSFET. The high-side pulse is terminated when the phase signal falls and SYNC input comparator resets the PWM latch.

#### **Thermal Protection**

Internal thermal shutdown circuitry is provided to protect the integrated circuit in the event the maximum junction temperature limit is exceeded. When activated, typically at 165 degrees Celsius, the controller is forced into a low power standby state with the output drivers and the bias regulator disabled. The device will restart when the junction temperature falls below the thermal shutdown hysteresis, which is typically 25 degrees. The thermal protection feature is provided to prevent catastrophic failures from accidental device overheating.

# Standalone DC/DC Synchronous Buck Mode

The LM5115A can be configured as a standalone DC/DC synchronous buck controller. In this mode the LM5115A uses leading edge modulation in conjunction with valley current mode control to control the synchronous buck power stage. The internal oscillator within the LM5115A sets the clock frequency for the high and low-side drivers of the external synchronous buck power MOSFETs. The clock frequency in the synchronous buck mode is programmed by the SYNC pin resistor and RAMP pin capacitor. Connecting a resistor between a dc bias supply and the SYNC pin produces a current, I<sub>SVNC</sub>, which sets the charging current of the RAMP pin capacitor. The RAMP capacitor is charged until its voltage reaches the peak ramp threshold of 2.25V. The RAMP capacitor is then discharged for 300ns before beginning a new PWM cycle. The 300ns reset time of the RAMP pin sets the minimum off-time of the PWM controller in this mode. The internal clock frequency in the synchronous buck mode is set by I<sub>SYNC</sub>, the ramp capacitor, the peak ramp threshold, and the 300ns deadtime.

$$F_{CLK} \approx 1 / ((C_{RAMP} \times 2.25V) / (I_{SYNC} \times 3) + 300ns)$$

See the LM5115 dc evaluation board application note (AN-1367) for more details on the synchronous buck mode. Please note that LM5115A is similar to LM5115 except for the tracking feature.

# App<u>tication</u>。Circuit"供应商

FIGURE 15. LM5115A Secondary Side Post Regulator (Inputs from LM5025 Forward Active Clamp Converter, 36V to 78V)

# Physical Dimensions inches (millimeters) unless otherwise noted 查询"LM5115AMT"供应商

TSSOP-16 Outline Drawing NS Package Number MTC16

| 查询"LM5115AMT"供应商 | Notes |

|------------------|-------|

|                  |       |

|                  |       |

|                  |       |

|                  |       |

|                  |       |

|                  |       |

|                  |       |

|                  |       |

|                  |       |

|                  |       |

|                  |       |

|                  |       |

|                  |       |

|                  |       |

≦询"LM5115AMT"供应商

**Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959

**National Semiconductor Europe** Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com

National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560