# SCX microCMOS Gate Array Family Application Guide

#### **TABLE OF CONTENTS**

| 1.0   | General Description                                                                                                                                                                 | ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0   | Product Features                                                                                                                                                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.0.1 | Enhanced Product Features                                                                                                                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.1   | microCMOS Process and Circuit Personalization 3                                                                                                                                     | }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.2   | Gate Array Basic Cell 3                                                                                                                                                             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.3   | Power Dissipation 3                                                                                                                                                                 | }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.4   | Absolute Maximum Ratings                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.5   | Recommended Operating Conditions                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.6   | DC Electrical Characteristics                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.7   | AC Electrical Characteristics                                                                                                                                                       | į                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.0   | Topology and Routing Resource Distribution 5                                                                                                                                        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | SCX6206 (600)                                                                                                                                                                       | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | SCX6212 (1.2k)                                                                                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | SCX6218 (1.8k)                                                                                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | SCX6225 (2.5k)                                                                                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | SCX6232 (3.2k) 6                                                                                                                                                                    | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

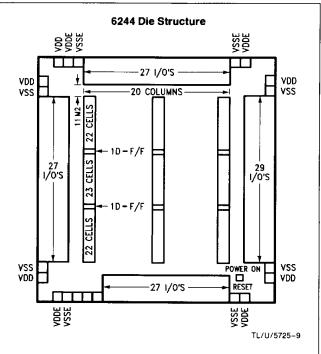

|       | SCX6244 (4.4k)                                                                                                                                                                      | ŝ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.0   | On-Chip Test Circuitry                                                                                                                                                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.0   | Macros 6                                                                                                                                                                            | ŝ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.1   | Hardware Macros                                                                                                                                                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.2   | Peripheral Macros 8                                                                                                                                                                 | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.0   | Software Macros                                                                                                                                                                     | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.1   | Software Macros (User Generated)                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.0   | Packaging                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8.0   | Propagation Delays                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9.0   | Design Automation System13                                                                                                                                                          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9.5   | Workstation Support14                                                                                                                                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10.0  |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | ·                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12.0  | Training and Technical Services                                                                                                                                                     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13.0  | Technology Centers2                                                                                                                                                                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | 2.0<br>2.0.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>3.0<br>4.0<br>5.0<br>5.1<br>5.2<br>6.0<br>6.1<br>7.0<br>8.0<br>9.0<br>9.5<br>10.0<br>10.1<br>10.2<br>10.3<br>10.4<br>11.0 | 2.0       Product Features       2         2.0       1       Enhanced Product Features       2         2.1       microCMOS Process and Circuit Personalization       3         2.2       Gate Array Basic Cell       3         2.3       Power Dissipation       4         2.4       Absolute Maximum Ratings       4         2.5       Recommended Operating Conditions       4         2.6       DC Electrical Characteristics       4         3.0       Topology and Routing Resource Distribution       5         SCX6206 (600)       5         SCX6212 (1.2k)       5         SCX6218 (1.8k)       5         SCX6225 (2.5k)       6         SCX6232 (3.2k)       6         SCX6232 (3.2k)       6         SCX6244 (4.4k)       6         4.0       On-Chip Test Circuitry       6         5.0       Macros       6         6.1       Software Macros       6         6.2       Peripheral Macros       6         6.1       Software Macros (User Generated)       7         7.0       Packaging       10         8.0       Propagation Delays       1         9.0       Design Exam |

61

006363

# 14 General Description

National Semiconductor's CMOS gate array Family utilizes a dual layer metal technology (microCMOS) to achieve operating speeds similar to Schottky-TTL with the inherent lower power consumption of standard CMOS integrated circuits. The SCX6200-Series Family is available in 2-micron drawn geometry with a 1.4 micron effective channel length. The range of complexity is currently from 600 to 6000 gates. The gates are arranged in cells. Each cell has the equivalent of three 2-input NAND or NOR gates. All outputs have the ability to drive 10 LSTTL loads. All inputs have high noise immunity and are protected from static discharge.

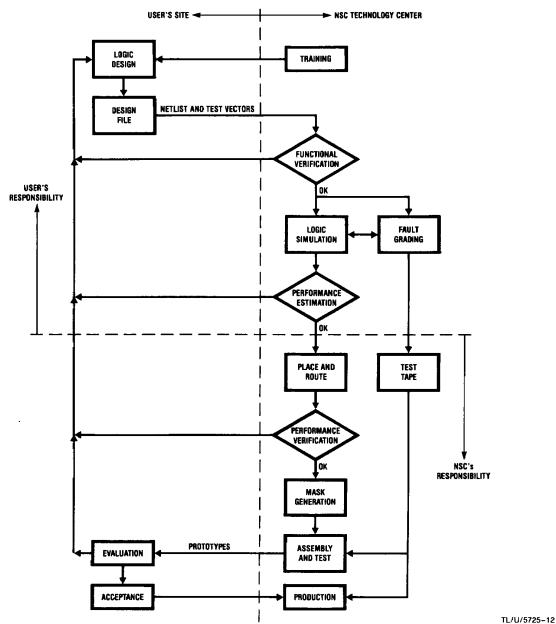

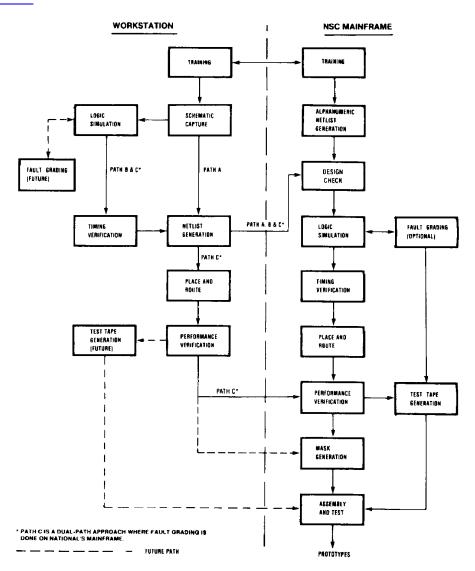

National Semiconductor supports gate array designs with a variety of user/vendor interfaces. This ranges from producing arrays from the user's schematic to accepting databases for mask generation. A large dedicated staff of gate array professionals is available to help the user determine the most efficient and cost effective way to interface on any given design.

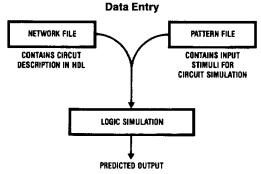

The design automation tools include workstation or text file entry (for schematic capture), logic and timing verifiers to substantiate the actual design, fault grading analysis to gauge testability and a large selection of macros (hardware and software) to speed and simplify the design.

#### 2.0 Product Features

- Latch-up proof, state-of-the-art 2-micron (drawn) dualmetal silicon-gate microCMOS technology

- Ultra-high performance—1 ns typical gate delays

- Available from 600 gates to 6000 gates

- CMOS power dissipation

- All inputs and I/Os protected from over-voltage and latchup

- Full design automation support

- Schematic capture

- Logic simulator with timing information

- Fault grading

- Multiple power rail pin connections

- Multiple packaging options in ceramic, plastic, leaded and leadless

- Pin counts to 172

- Military performance

- Alternately sourced

996

■ Complete hardware/software macrocell libraries

- On-chip self-test capability (6.0K only)

- 100% auto-place-and-route at 90% utilization

- Design automation system supported on mainframe and workstations

#### 2.0.1 Enhanced Product Features

The SCX6200-series gate array family is available in seven device increments from 600 to 6000 gates. The initial members of the 2-micron family consist of SCX6212, 6225 and 6260. Today it has been enhanced and expanded to include the 6244, 6232, 6218 and 6206. These enhanced devices contain several new features as follows:

- Flexible I/O Structure The I/O buffer has been enhanced to handle multiple functions including:

- Low-drive inputs compatible with TTL, CMOS or Schmitt Trigger

- High-drive (Clock Driver) inputs compatible with TTL, CMOS or Schmitt Trigger

- Output compatible with TTL and CMOS and configurable as TRI-STATE®, non TRI-STATE or Open Drain

- Outputs selectable for 1, 2 or 4 mA drive

- -- Bidirectional inputs/outputs

- Oscillator macros to drive 1, 2 or 4 mA

- Separate power supply traces for output drivers improve noise immunity

The input capacitance loading of the output drivers has also been reduced to enhance the overall circuit performance.

- Selectable Output Drive Capability The enhanced I/O structure now makes it possible to offer a variety of output drives for any given I/O location. Through implementation of I/O macro options, users can select their output drives in 1, 2 or 4 mA for each output buffer.

- Parallel I/O Buffers for High Drives By means of special I/O macros, output drive current in excess of 4 mA can be achieved by paralleling I/O buffers without losing the input functions. For example, to achieve 24 mA, six 4 mA I/O buffers need to be paralleled up; through use of the special macros, one pin is needed to implement the output which can be bidirectional while 5 pins can still be used as inputs.

- Dedicated Multiplexed D-Flip/Flops Incorporated into the internal array core is a number of dedicated multiplexed D-flip/flops. These flip/flops have been designed to achieve significant system speed improvement over a logically eqivalent macro function while minimizing silicon space to implement. They are ideal for scan path design techniques as well as registers and counters.

| Array<br>Name    | Equivalent<br>2-Input Gates (Note 1) | Input Cells | I/O<br>Cells | Signal<br>Pins | Test<br>Pin | V <sub>DD</sub><br>Pins | V <sub>SS</sub><br>Pins |

|------------------|--------------------------------------|-------------|--------------|----------------|-------------|-------------------------|-------------------------|

| SCX6206          | 600                                  | 8           | 40           | 48             | 1           | 4                       | 4                       |

| SCX6212          | 1260                                 | 17          | 42           | 59             | 1           | 4                       | 4                       |

| SCX6218          | 1806                                 | 3           | 70           | 73             | 1           | 8                       | B                       |

| SCX6225          | 2430                                 | 12          | 76           | 88             | 1           | 6                       |                         |

| SCX6232          | 3162                                 | 3           | 101          | 104            | 1           | 8                       | 8                       |

| SCX6244          | 4380                                 | 3           | 110          | 113            | 1           | В                       | <u>R</u>                |

| SCX6260 (Note 2) | 6090                                 | 66          | 88           | 154            | 6           | 8                       | 9                       |

Note 1: Input and I/O cells are not considered part of the internal cell count.

Note 2: Advanced Architecture with additional 2500 gates for on-chip self-test capability.

FIGURE 1. Cell

#### 2.1 microCMOS PROCESS AND CIRCUIT **PERSONALIZATION**

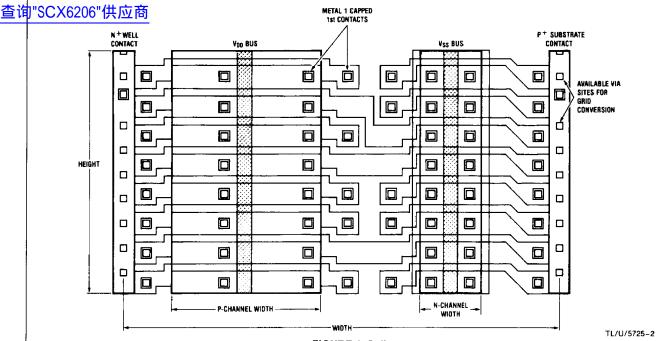

The microCMOS process developed by National is based on P-type starting material, N-well technology and oxide isolation. After the basic transistors are formed (in their respective cells), two separate layers of metalization (M1 and M2) are placed on the wafers.

The processing steps and tooling requirements for all the wafers up to the metal layers are common and fixed. Circuit patterns-called "options"-are defined by the two metal layers and the VIAs. In this way, the user's design (or circuit personality) is imposed on the wafer.

All SCX gate arrays in the family use the same basic internal cell. There are eight pairs of N and P-type MOS transistors in each cell (see Figure 1). The power and ground lines (VDD and VSS buses, respectively) run up and down the cell. This cell is repeated in all four directions to form columns and rows in the core of the array. The structure of the internal core is optimized to the size of each family member.

National Semiconductor maintains an inventory of gate array wafers fabricated up to but before metalization. As the customer's options are designed and the last three patterns finalized, wafers are taken out of inventory and the fabrication process completed for the metal layers.

In this way, National Semiconductor can provide gate array users with quick turn-around cost effective designs while maintaining the quality, reliability and production control of an in-house (4 and 6-inch) wafer fab line.

#### 2.2 GATE ARRAY BASIC CELL

Figure 1 shows the basic internal cell. The geometries are not drawn to scale and the exact topology has been modified for illustration purposes.

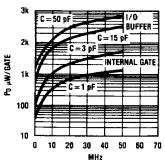

#### 2.3 POWER DISSIPATION

An outstanding feature of microCMOS circuits is their low power dissipation. CMOS circuits draw electrical current for basically two reasons:

- (1) During transition from a logic "0" to a logic "1" or vice versa, there exists a finite time when the P-channel and Nchannel devices associated with the logic element are both conducting. The CMOS circuit consumes power during this transition.

- (2) When signals change state, the distributed capacitance in the circuit (and its load) need to be either charged or discharged. The electrical current required for this purpose increases power consumption.

Thus, power dissipation is dependent on operating voltage, nodal capacitance and the frequency of circuit operation. Mathematically speaking:

$$P_O = CV^2F$$

For estimation purposes, the value of:

25 μW/gate/MHz per gate equivalent can be used for elements within the array.

700  $\mu$ W/MHz/output buffer at 15 pF load or 1500  $\mu$ W/ MHz/output at 50 pF load, can be used for the output buff-

Power dissipation in a CMOS array is typically dominated by output buffers driving large capacitive loads.

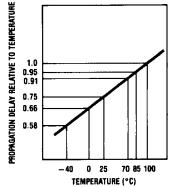

Figure 2 will help in estimating power consumption in a particular design.

FIGURE 2. Power Consumption vs Frequency

2.4 ABSOLUTE MAXIMUM RATINGS Exceeding the following absolute maximum ratings may result in permanent damage to the device.

Supply Voltage

$-0.5\mbox{V}$  to  $7\mbox{V}$

Input or Output Voltage Storage Temperature

-0.5V to  $V_{DD} + 0.5$ V -65°C to 150°C

Power Dissipation (Package Dependent) Lead Temp. (Soldering, 10 seconds)

1W 300°C

#### 2.5 RECOMMENDED OPERATING CONDITIONS Min Max Units V<sub>DD</sub>, Supply Voltage 2 6 ٧ V<sub>I</sub>, V<sub>O</sub>, Input or Output Voltage $V_{SS}$ $V_{DD}$ ٧ Io, High or Low Level Output Current 0 ± 25 mΑ I<sub>DD</sub>, V<sub>DD</sub> or V<sub>SS</sub> Current per Pad 0 ± 50 mΑ T<sub>A</sub>, Ambient Operating Temperature -40 + 85°C

#### 2.6 DC ELECTRICAL CHARACTERISTICS

$V_{DD} = 5V \pm 10\%$ , min/max limits apply over recommended operating temperature range unless otherwise specified.

| Symbol              | Parameter                                              | Conditions                                                | Min                   | Max                 | Units |

|---------------------|--------------------------------------------------------|-----------------------------------------------------------|-----------------------|---------------------|-------|

| V <sub>IH</sub>     | High Level Input Voltage                               | $V_{O} = 0.5V \text{ or } V_{DD} - 1V, I_{O} = 1 \mu A$   | 0.7 V <sub>DD</sub>   |                     | V     |

| V <sub>IL</sub>     | Low Level Input Voltage                                | $V_{O} = 0.5 V \text{ or } V_{DD} - 1 V, I_{O} = 1 \mu A$ |                       | 0.3 V <sub>DD</sub> | V     |

| V <sub>OH</sub>     | High Level Output Voltage                              | $V_I = V_{DD}$ or GND, $I_O = 1 \mu A$                    | V <sub>DD</sub> -0.05 |                     | V     |

| V <sub>OL</sub>     | Low Level Output Voltage                               | $V_I = V_{DD}$ or GND, $I_O = 1 \mu A$                    | <u></u> '             | 0.05                | V     |

| <b>І</b> он         | High Level Output Current                              | $V_I = V_{DD}$ or GND, $V_O = V_{DD} - 0.8V$              | - 4                   |                     | mA    |

| loL                 | Low Level Output Current                               | $V_I = V_{DD}$ or GND, $V_O = 0.4V$                       | 4                     |                     | mA    |

| V <sub>IH</sub> TTL | Min. High Level TTL I/P Voltage (for TTL Input Option) | $V_{O} = 0.5V \text{ or } V_{DD} - 1V, I_{O} = 1 \mu A$   | 2                     |                     | ٧     |

| V <sub>IL</sub> TTL | Max. Low Level TTL I/P Voltage (for TTL Input Option)  | $V_{O} = 0.5V \text{ or } V_{DD} - 1V, I_{O} = 1 \mu A$   |                       | 0.8                 | ٧     |

| I <sub>I</sub>      | Input Current (Without Pull-Up Resistor)               | $V_{I} = V_{DD}$ or GND                                   |                       | ± 1                 | μΑ    |

| lcc                 | Supply Current                                         | $V_I = V_{DD}$ or GND, $T_A = 25$ °C                      | <u>-</u> -            | 100                 | μΑ    |

# 2.7 AC ELECTRICAL CHARACTERISTICS $V_{DD}=5V,\,T_{A}=25^{\circ}C,\,2\mu$ process.

| Symbol                               | Parameter                                                                                                                                                          | Min                        | Max                          | Units          |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------|----------------|

| tplH                                 | Output Buffer (Non-Inverting, non-TRI-STATE) $t_r = t_f = 5 \text{ ns, } 0V-5V$ $C_L = 15 \text{ pF}$                                                              | 1.1                        | 3.5                          | ns             |

| tpHL                                 |                                                                                                                                                                    | 1.2                        | 4.2                          | ns             |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Input Buffer<br>(TTL Type, Non-Inverting)<br>at t <sub>r</sub> = t <sub>f</sub> = 5 ns, 0V-3V<br>C <sub>L</sub> = 1 pF                                             | 0.75<br>1.10               | 2.95<br>3.2                  | ns<br>ns       |

| t <sub>РLН</sub>                     | Input Buffer (CMOS Type, Inverting) at $t_r = t_f = 5$ ns, $0V-5V$ $C_L = 1$ pF                                                                                    | 0.55                       | 1.75                         | ns             |

| t <sub>РНL</sub>                     |                                                                                                                                                                    | 0.50                       | 1.40                         | ns             |

| tPLH                                 | Output TRI-STATE (Non-Inverting) at $t_r = t_f = 5$ ns $0V-5V$ $C_L = 50$ pF $R_L = 1$ k $\Omega$ Delays Measured at $50\%$ Point Between Start and Target Voltage | 1.9                        | 6.0                          | ns             |

| tPHL                                 |                                                                                                                                                                    | 2.5                        | 6.8                          | ns             |

| tPZL                                 |                                                                                                                                                                    | 2.8                        | 7.8                          | ns             |

| tPZH                                 |                                                                                                                                                                    | 1.9                        | 6.0                          | ns             |

| tPLZ                                 |                                                                                                                                                                    | 7.2                        | 8.3                          | ns             |

| tPHZ                                 |                                                                                                                                                                    | 7.0                        | 8.2                          | ns             |

| tpLH<br>tpHL<br>tpHL<br>tpLH         | Internal 2-Input NAND at $t_r=t_f=5$ ns, 0V~5V Load Equivalent to Fan-Out of 3 and 100 mils of Interconnect As Above with $C_L=0$ pF                               | 0.4<br>0.8<br>0.20<br>0.15 | 1.55<br>2.30<br>0.75<br>0.55 | ns<br>ns<br>ns |

# 查询"\$9.10年的中央的

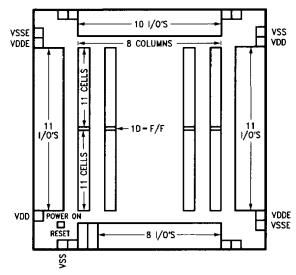

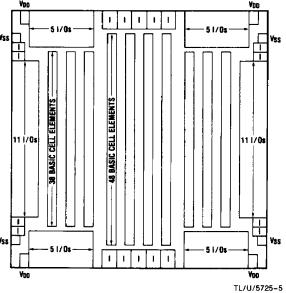

### **Resource Distribution**

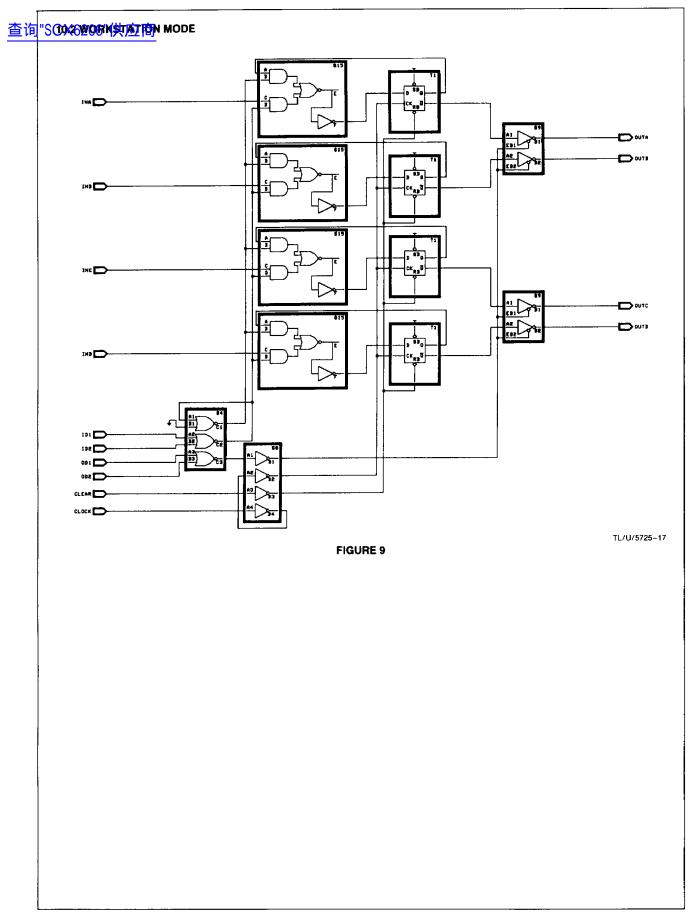

The specific topology and routing resource distribution have been tailored for each family member. Architectural considerations include the ratio of inputs and I/Os to total cell count, power consumption and package inductance to power pins (for simultaneous switching outputs) and routing resources consistant with automatic place and route software. Internal cell utilizations of greater than 85% can be expected. Individual topologies and a family summary follow.

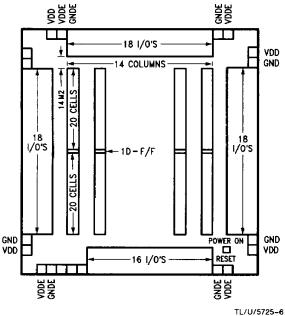

#### 6206 Die Structure

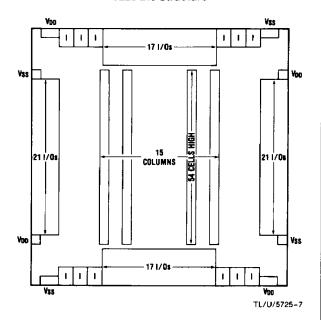

6212 Die Structure

TL/U/5725-4

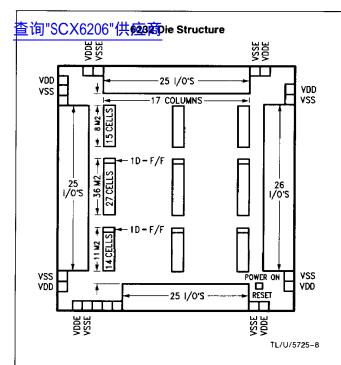

#### 6218 Die Structure

# 6225 Die Structure

# 4.0 On-Chip Test Circuitry

Each of the SCX gate arrays is provided with dedicated onchip test circuitry. This circuitry forces all the outputs to specific states to facilitate output parametric testing. These parametric tests include leakage and current sourcing/sinking measurements on all output pins.

The on-chip test circuitry is enabled by a dedicated test mode control (TMC) pin. This pin is set aside for testing and cannot be used for any other purpose on the 6212 and 6225. However, for the enhanced devices (6244, 6232, 6218 and 6206), the extra TMC pin can be avoided by means of an internal TMC decoding circuit of the user's design. In addition, an optional internal control signal derived from the TMC pin is now available. This can be used, for example, as a set or reset control signal to the internal logic.

The self-test capability has been further expanded and enhanced on the 6k-gate 6260. It has an additional 2,500 gates dedicated to provide an on-chip maintenance system that includes chip self-test, system interconnect-test, logic analyzer, and system check-sum modes. This self-test feature on the 6260 is unique from the rest of the SCX family as well as in the industry. A low at this input will activate the on-chip test circuitry. When the on-chip test circuitry is activated, the states of all outputs are determined by two other inputs; these are TRI-STATE test control (TSTC) and data test (DT). The TSTC and DT can share input pins with the user's design. They are only active when the TMC is enabled. The TSTC input has precedence over the DT input. The TMC input is active for the following discussion.

When the TSTC input is active, all the output buffers are put into a high impedance mode. When TSTC is not active, the states of the output buffers are determined by the DT input. These two inputs can be assigned to any of the input pins.

**On-Chip Test Circuitry Truth Table**

| TMC | DT         | TSTC       | Output    |

|-----|------------|------------|-----------|

| 0   | X          | Active     | TRI-STATE |

| 0   | Non-Active | Non-Active | 1         |

| 0   | Active     | Non-Active | 0         |

**Definition of Test Input States**

|            | Non-Inverting<br>Macros | Inverting<br>Macros |

|------------|-------------------------|---------------------|

| Non-Active | 0                       | 1                   |

| Active     | 1                       | 0                   |

#### 5.0 Macros

Three types of macros are available for designers to use: hardware macros, software macros (National Semiconductor standard library), and user generated software macros.

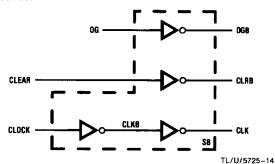

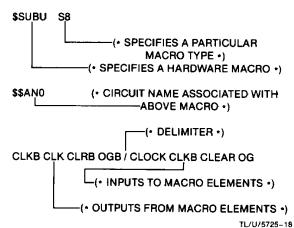

#### **5.1 HARDWARE MACROS**

The SCX family of gate arrays offers an extensive library of hardware macros (Table I). Each macro has been fully characterized and functionally proven. The designer can select those macros that most efficiently implement the design. The electrical performance of the macros is characterized at two sets of conditions: best and worst-case. Under each set of conditions, the output loading is specified at 0 pF and 1.0 pF. The 1.0 pF load is equivalent to a fan-out of 3 and includes 100 mils length of metal interconnect. A single input load is equivalent to 0.13 pF and is defined as a load factor of 1.

National Semiconductor has very tight wafer fabrication guidelines. However, process parameters still do vary from wafer-to-wafer, lot-to-lot. The electrical specifications of the macros take into account such variations.

查询"SCX6206"供应商 TABLE I. Table of Macros

| <u>(X62U6"拱/V图</u>                       | · · · · · · · · · · · · · · · · · · · |

|------------------------------------------|---------------------------------------|

| Function                                 | Macro Name                            |

| GATES                                    | T                                     |

| Triple 2-Input NAND                      | C001 (S1)                             |

| Dual 3-Input NAND                        | C002 (S2)                             |

| Dual 2-Input NAND/AND                    | C003 (S3)                             |

| Triple 2-Input NOR                       | C004 (S4)                             |

| Dual 3-Input NOR                         | C005 (S5)                             |

| Dual 2-Input NOR/OR                      | C006 (S6)                             |

| Single 2-Input Exclusive-OR              | C053 (S53)                            |

| 2-Input 2-Wide OR-NAND with Complement   | C014 (S14)                            |

| 2-Input 2-Wide AND-NOR with Complement   | C015 (S15)                            |

| Triple 4-Input NAND                      | C017 (D1)                             |

| Single 5-Input NAND (2X)                 | C018 (D2)                             |

| Triple 3-Input NAND with Complement      | C019 (D3)                             |

| Triple 4-Input NOR                       | C020 (D4)                             |

| Single 5-Input NOR (2X)                  | C021 (D5)                             |

| Triple 3-Input NOR with Complement       | C022 (D6)                             |

| 4-Input Exclusive-OR                     | C046 (T2)                             |

| 3-Input Exclusive-OR                     | C047 (D10)                            |

| Single 2-Input Exclusive-NOR             | C048 (S21)                            |

| 5-Input NAND-AND                         | C057 (D57)                            |

| 5-Input NOR-OR                           | C058 (D58)                            |

| 3-Input Exclusive-NOR                    | C800 (D800)                           |

| 8-Input AND/NAND                         | C830 (D830)                           |

| 8-Input OR/NOR                           | C878 (D878)                           |

| BUFFERS                                  |                                       |

| Triple 2X Buffer                         | C007 (S7)                             |

| Quad Inverter                            | C008 (S8)                             |

| Dual TRI-STATE Inverting Buffer          | C009 (S9)                             |

| Single Non-Inverting TRI-STATE Buffer    | C010 (S10)                            |

| Schmitt Trigger                          | C025 (S24)                            |

| Quad Inverter Buffer                     | C043 (S20)                            |

| Dual Triple Inverter Buffer              | C044 (S19)                            |

| 1-3 Buffer                               | C045 (S22)                            |

| 3-1 Buffer                               | C061 (S23)                            |

| 2-2 Buffer                               | C049 (S18)                            |

| 4-Input Exclusive-OR Buffer (2X)         | C801 (T801)                           |

| Quad Pulldown with Common Enable         | C808 (S808)                           |

| Quad Pulldown with 6-Input Enable Decode | C811 (D811)                           |

| Quad Pullup with 6-Input Enable Decode   | C812 (D812)                           |

| Quad Pullup with Common Enable           | C832 (S832)                           |

| <u> </u>                                 | · · · · · · · · · · · · · · · · · · · |

| Function                                                   | Macro Name  |

|------------------------------------------------------------|-------------|

| LATCHES                                                    |             |

| NAND R/S Latch with 2-Input NAND                           | C012 (S12)  |

| NOR R/S Latch with 2-Input NOR                             | C013 (S13)  |

| D-Latch with Set/Reset                                     | C062 (D11)  |

| 1-Bit Transparent D-Latch with<br>Reset and Enable         | C026 (D12)  |

| Triple R/S NAND Latch                                      | C027 (D7)   |

| Triple R/S NOR Latch                                       | C031 (D8)   |

| FLIP-FLOP                                                  |             |

| D Flip-Flop                                                | C023 (D9)   |

| D Flip-Flop with Set and Reset                             | C024 (T1)   |

| D Flip-Flop with Reset and Parallel Load                   | C034 (Q4)   |

| D Flip-Flop with Set/Reset Master Slave                    | C051 (T3)   |

| D Flip-Flop with Set/Reset Buffered                        | C060 (T60)  |

| D Flip-Flop with Reset (Q Output Only)                     | C064 (D64)  |

| Multiplexed D Flip-Flop with Reset                         | C035 (Q35)  |

| J-K Flip-Flop with Reset and Set                           | C037 (F37)  |

| J-K Flip-Flop with Set/Reset Master Slave                  | C052 (Q2)   |

| T Flip-Flop with Inverter Reset                            | C036 (Q6)   |

| T Flip-Flop with Reset                                     | C861 (Q861) |

| REGISTERS AND COUNTERS                                     |             |

| 2-Bit Serial In/Out and Parallel<br>Out Shift Register     | C039 (F1)   |

| 2-Bit Serial/Parallel Shift Register                       | C042 (H4)   |

| Universal Shift Register State                             | C194 (F194) |

| Up-Down Counter Stage with Parallel Load                   | C038 (F2)   |

| 4-Bit Binary Counter Control Logic                         | C871 (Q871) |

| MULTIPLEXER & DEMULTIPLEXER                                |             |

| 2-to-1 Multiplexer with<br>Single Control Input            | C056 (S56)  |

| 4-to-1 TRI-STATE Multiplexer with Enable Low               | C028 (T4)   |

| 4-to-1 Multiplexer with<br>Complement Output               | C029 (T5)   |

| 1-to-4 Decoder with Active Low<br>Outputs and Enable Input | C033 (Q3)   |

| 3-to-8 Decoder                                             | C138 (H138) |

| 8-Channel Digital Multiplexer                              | C151 (H151) |

| Quad 2-Input Multiplexer                                   | C158 (Q158) |

| Quad 2-Channel TRI-STATE<br>Multiplexer                    | C257 (Q257) |

#### \$询"SCX6206"供应商

#### TABLE I. Table of Macros (Continued)

| *************************************** |

|-----------------------------------------|

| Macro Name                              |

|                                         |

| C030 (T6)                               |

| C032 (T7)                               |

| C040 (H2)                               |

| C041 (H3)                               |

|                                         |

| Function              | Macro Name          |

|-----------------------|---------------------|

| INPUTS AND OUTPUTS    |                     |

| Inputs Only (36)      | See I/O Macro Table |

| Outputs Only (9)      | See I/O Macro Table |

| Bidirectional (72)    | See I/O Macro Table |

| Oscillator Macros (3) | See I/O Macro Table |

#### Notes on Macro Name

Note 1: Cell Count S = 1 cell (3 gates)

Q = 4 cells (12 gates)

D = 2 cells (6 gates)

F = 5 cells (15 gates)

T = 3 cells (9 gates)

H = 6 cells (18 gates)

Note 2: The 'C000' designator is a common reference used between National Semiconductor and its alternate source for the purpose of consistency with users.

#### TABLE II. I/O Macro Table

| I/O Macro Type        | Input Macro | Output Macro | Input Drive |    | Output Drive |      |      | Each Capable of    |   |             |     |

|-----------------------|-------------|--------------|-------------|----|--------------|------|------|--------------------|---|-------------|-----|

|                       | Input Macro | Output macro | 1X          | 7X | 15X          | 1 mA | 2 mA | 4 mA               | V | D           | N   |

| Input Only            | TTL         | •            | Х           | Х  | Х            |      |      |                    | Х | ×           | X   |

| (36 Macros)           | CMOS (INV)  |              | Х           | Х  | х            |      |      |                    | X | X           | X   |

|                       | CMOS (NINV) |              | Х           | х  | Х            |      |      |                    | X | l $\hat{x}$ | X   |

|                       | Schmitt     |              | Х           | Х  | Х            | :    |      |                    | Х | X           | X   |

| Output Only           |             | NINV         |             |    | _            | Х    | х    | Х                  |   | <u> </u>    |     |

| (9 Macros)            |             | INV          |             |    |              | Х    | Х    | x                  |   | ł           |     |

|                       | ĺ           | Open Drain   |             |    |              | Х    | х    | Х                  |   |             |     |

| Bidirectional         | TTL         | NINV         | Х           |    |              | Х    | Х    | X                  | Х | х           | X   |

| (72 Macros)           | CMOS (INV)  | NINV         | х           |    |              | X    | X    | X                  | x | Î           | x   |

|                       | CMOS (NINV) | NINV         | х           |    |              | X    | X    | X                  | x | Î           | Ϊ́χ |

|                       | Schmitt     | NINV         | Х           |    |              | X    | X    | X                  | X | Î           | x   |

|                       | TTL         | INV          | Х           |    |              | Х    | X    | X                  | X | x           | X   |

|                       | CMOS (INV)  | INV          | Х           |    |              | х    | X    | X                  | X | x           | X   |

|                       | CMOS (NINV) | INV          | Х           |    |              | Х    | X    | $\hat{\mathbf{x}}$ | X | Î           | x   |

|                       | Schmitt     | INV          | Х           | ĺ  |              | X    | Х    | x                  | x | x           | x   |

| Oscillator (3 Macros) |             |              |             |    |              | ×    | Х    | Х                  |   |             |     |

V = Pull-Up; D = Pull-Down; N = Neither Pull-Up nor Pull-Down

#### **5.2 PERIPHERAL MACROS**

Interfacing to the SCX gate arrays is done through the peripheral buffers. There are two types of peripheral cells; input only and bi-directional I/O cells (Table II). The peripheral macros are not included in the count of internally available cells.

The buffers are located around the periphery of the die and the exact configuration is dependent on the particular family member under consideration. Reference section 3 for specific locations of input and I/O cells.

#### 6.0 Software Macros

In addition to the pre-designed hardware macros, National Semiconductor offers a library of software macros. These software macros emulate the functions of the popular 7400 and 4000 logic families. From the designer's vantage point, these software macros are utilized as though they were hardware macros. The actual implementation of these higher order functions is handled by the design automation tools in a process that virtually expands the software macro into its hardware macro primitives.

Since the software macros reside in the design automation system, a designer may copy a software macro into his design, modify it to meet some special consideration, rename it, then reference it as a special or new software macro. This procedure is coordinated with National's Technology Centers.