www.ti.com

# 1A, Single-Input, Single Cell Li-Ion Battery Charger

Check for Samples: bq24090, bq24091, bq24092, bq24093

#### **FEATURES**

#### CHARGING

- 1% Charge Voltage Accuracy

- 10% Charge Current Accuracy

- Pin Selectable USB 100mA and 500mA Maximum Input Current Limit

- Programmable Termination and Precharge Threshold

#### PROTECTION

- 6.6V Over-Voltage Protection

- Input Voltage Dynamic Power Management

- 125°C Thermal Regulation; 150°C Thermal Shutdown Protection

- OUT Short-Circuit Protection and ISET Short Detection

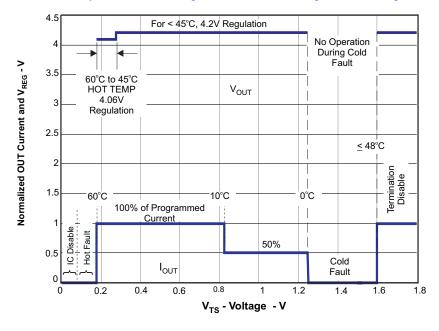

- Operation Over JEITA Range via Battery NTC – ½ Fast-Charge-Current at Cold, 4.06V at Hot, bq24092/3

- Fixed 10 Hour Safety Timer

#### SYSTEM

- Automatic Termination and Timer Disable Mode (TTDM) for Absent Battery Pack With Thermistor

- Status Indication Charging/Done

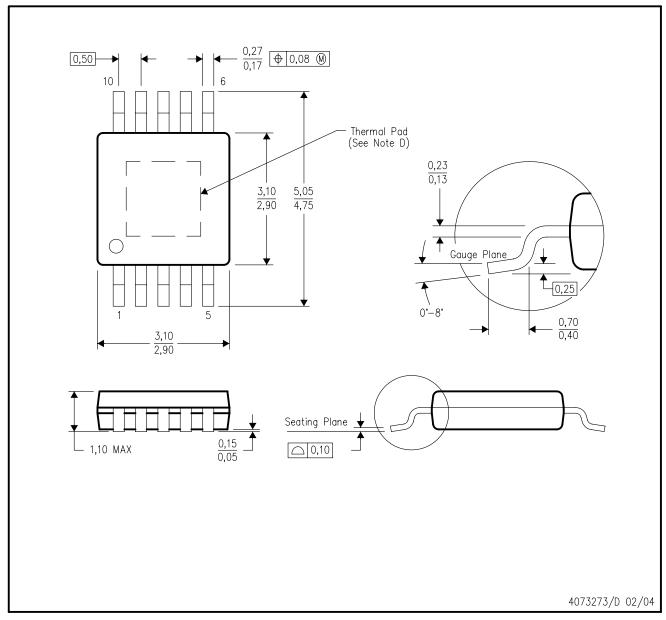

- Available in Small 10-Pin MSOP Package

#### **APPLICATIONS**

- Smart Phones

- PDAs

- MP3 Players

- Low-Power Handheld Devices

#### DESCRIPTION

The bq2409x series of devices are highly integrated Li-ion linear chargers devices targeted at space-limited portable applications. The devices operate from either a USB port or AC adapter. The high input voltage range with input overvoltage protection supports low-cost unregulated adapters.

The bq2409x has a single power output that charges the battery. A system load can be placed in parallel with the battery as long as the average system load does not keep the battery from charging fully during the 10 hour safety timer.

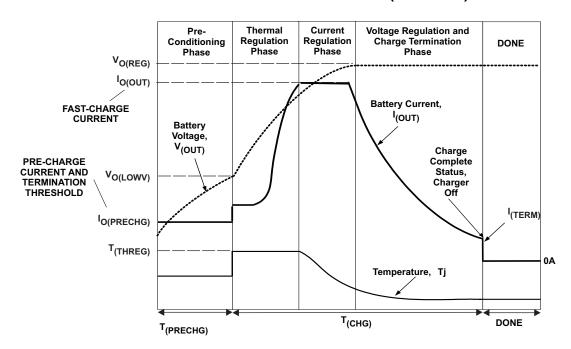

The battery is charged in three phases: conditioning, constant current and constant voltage. In all charge phases, an internal control loop monitors the IC junction temperature and reduces the charge current if an internal temperature threshold is exceeded.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **DESCRIPTION CONTINUED**

The charger power stage and charge current sense functions are fully integrated. The charger function has high accuracy current and voltage regulation loops, charge status display, and charge termination. The pre-charge current and termination current threshold are programmed via an external resistor. The fast charge current value is also programmable via an external resistor.

#### ORDERING INFORMATION

| PART #  | V <sub>O(REG)</sub> | V <sub>OVP</sub> | JEITA | TS/CE     | PG  | PACKAGE                   | Marking |

|---------|---------------------|------------------|-------|-----------|-----|---------------------------|---------|

| bq24090 | 4.20 V              | 6.6 V            | No    | 10kΩ NTC  | Yes | 10 PIN 5x3mm <sup>2</sup> | bq24090 |

| bq24091 | 4.20 V              | 6.6 V            | No    | 100kΩ NTC | Yes | 10 PIN 5x3mm <sup>2</sup> | bq24091 |

| bq24092 | 4.20 V              | 6.6 V            | Yes   | 10kΩ NTC  | Yes | 10 PIN 5x3mm <sup>2</sup> | bq24092 |

| bq24093 | 4.20 V              | 6.6 V            | Yes   | 100kΩ NTC | Yes | 10 PIN 5x3mm <sup>2</sup> | bq24093 |

#### ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                  |                             |                                                                    | VALUE      | UNIT |

|------------------|-----------------------------|--------------------------------------------------------------------|------------|------|

|                  |                             | IN (with respect to VSS)                                           | -0.3 to 7  | V    |

| lr               | Input Voltage               | OUT (with respect to VSS)                                          | -0.3 to 7  | V    |

|                  | mpat voltage                | PRE-TERM, ISET, ISET2, TS, CHG, PG, ASI, ASO (with respect to VSS) | -0.3 to 7  | V    |

|                  | Input Current               | IN                                                                 | 1.25       | Α    |

|                  | Output Current (Continuous) | OUT                                                                | 1.25       | Α    |

|                  | Output Sink Current         | CHG                                                                | 15         | mA   |

| $T_{J}$          | Junction temperature        |                                                                    | -40 to 150 | °C   |

| T <sub>STG</sub> | Storage temperature         |                                                                    | -65 to 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

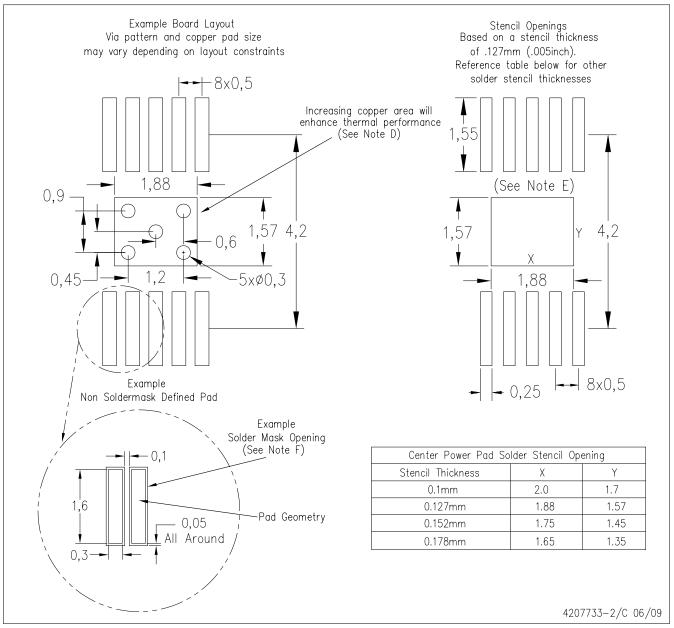

### PACKAGE DISSIPATION RATINGS(1) (2)

| PACKAGE    | $R_{	heta JA}$ | $R_{	heta JC}$ | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>T <sub>A</sub> > 25°C |

|------------|----------------|----------------|---------------------------------------|------------------------------------------|

| 5x3mm MSOP | 52°C/W         | 48°C/W         | 1.92 W                                | 19.2 mW/°C                               |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

Submit Documentation Feedback

<sup>(2)</sup> This data is based on using the JEDEC High-K board and the exposed die pad is connected to a copper pad on the board. This is connected to the ground plane by a 2x3 via matrix

<u>₩營特學Q24090"供应商</u>

### RECOMMENDED OPERATING CONDITIONS(1)

|                       |                                                                                 | MIN   | MAX  | UNIT |

|-----------------------|---------------------------------------------------------------------------------|-------|------|------|

| V                     | IN voltage range                                                                | 3.5   | 7    | V    |

| V <sub>IN</sub>       | IN operating voltage range, Restricted by V <sub>DPM</sub> and V <sub>OVP</sub> | 4.45  | 6.45 | V    |

| I <sub>IN</sub>       | Input current, IN pin                                                           |       | 1.0  | Α    |

| l <sub>out</sub>      | Current, OUT pin                                                                |       | 1.0  | Α    |

| TJ                    | Junction temperature                                                            | 0     | 125  | °C   |

| R <sub>PRE-TERM</sub> | Programs precharge and termination current thresholds                           | 1     | 10   | kΩ   |

| R <sub>ISET</sub>     | Fast-charge current programming resistor                                        | 0.675 | 49.9 | kΩ   |

| R <sub>TS</sub>       | 10k NTC thermistor range without entering BAT_EN or TTDM                        | 1.66  | 258  | kΩ   |

<sup>(1)</sup> Operation with  $V_{\text{IN}}$  less than 4.5V or in drop-out may result in reduced performance.

### **ELECTRICAL CHARACTERISTICS**

Over junction temperature range 0°C ≤ T<sub>1</sub> ≤ 125°C and recommended supply voltage (unless otherwise noted)

|                           | PARAMETER                                                                  | TEST CONDITIONS                                                                                                                                                                         | MIN  | TYP     | MAX  | UNIT     |  |

|---------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|----------|--|

| INPUT                     |                                                                            |                                                                                                                                                                                         |      |         |      |          |  |

| UVLO                      | Undervoltage lock-out Exit                                                 | $V_{IN}$ : 0V $\rightarrow$ 4V Update based on sim/char                                                                                                                                 | 3.15 | 3.3     | 3.45 | V        |  |

| V <sub>HYS_UVLO</sub>     | Hysteresis on V <sub>UVLO_RISE</sub> falling                               | V <sub>IN</sub> : 4V→0V,<br>V <sub>UVLO_FALL</sub> = V <sub>UVLO_RISE</sub> -V <sub>HYS-UVLO</sub>                                                                                      | 175  | 227     | 280  | mV       |  |

| V <sub>IN-DT</sub>        | Input power good detection threshold is $V_{OUT} + V_{IN-DT}$              | (Input power good if $V_{IN} > V_{OUT} + V_{IN-DT}$ );<br>$V_{OUT} = 3.6V$ , $V_{IN}$ : $3.5V \rightarrow 4V$                                                                           | 30   | 80      | 145  | mV       |  |

| V <sub>HYS-INDT</sub>     | Hysteresis on V <sub>IN-DT</sub> falling                                   | $V_{OUT} = 3.6V, V_{IN}: 4V \rightarrow 3.5V$                                                                                                                                           |      | 31      |      | mV       |  |

| t <sub>DGL(PG_PWR)</sub>  | Deglitch time on exiting sleep.                                            | Time measured from V <sub>IN</sub> : 0V $\rightarrow$ 5V 1 $\mu s$ rise-time to $\overline{PG}$ = low, V <sub>OUT</sub> = 3.6V                                                          |      | 45      |      | μS       |  |

| t <sub>DGL(PG_NO-</sub>   | Deglitch time on V <sub>HYS-INDT</sub> power down. Same as entering sleep. | Time measured from V <sub>IN</sub> : 5V $\rightarrow$ 3.2V 1µs fall-time to $\overline{PG}$ = OC, V <sub>OUT</sub> = 3.6V                                                               |      | 29      |      | ms       |  |

| V <sub>OVP</sub>          | Input over-voltage protection threshold                                    | $V_{IN}$ : $5V \rightarrow 7V$                                                                                                                                                          | 6.5  | 6.65    | 6.8  | V        |  |

| t <sub>DGL(OVP-SET)</sub> | Input over-voltage blanking time                                           | $V_{IN}$ : $5V \rightarrow 7V$                                                                                                                                                          |      | 113     |      | μS       |  |

| V <sub>HYS-OVP</sub>      | Hysteresis on OVP                                                          | $V_{IN}$ : $7V \rightarrow 5V$                                                                                                                                                          |      | 95      |      | mV       |  |

| t <sub>DGL(OVP-REC)</sub> | Deglitch time exiting OVP                                                  | Time measured from V <sub>IN</sub> : 7V $\rightarrow$ 5V 1 $\mu$ s fall-time to $\overline{PG}$ = LO                                                                                    |      | 30      |      | μS       |  |

|                           | USB/Adaptor low input voltage                                              | Feature active in USB mode; Limit Input Source Current to 50mA; $V_{OUT} = 3.5V$ ; $R_{ISET} = 825\Omega$                                                                               | 4.34 | 4.4     | 4.46 | V        |  |

| V <sub>IN-DPM</sub>       | protection. Restricts lout at V <sub>IN-DPM</sub>                          | Feature active in Adaptor mode; Limit Input Source Current to 50mA; $V_{OUT} = 3.5V$ ; $R_{ISET} = 825\Omega$                                                                           | 4.24 | 4.3     | 4.36 | <b>v</b> |  |

|                           | USB input I-Limit 100mA                                                    | ISET2 = Float; $R_{ISET} = 825\Omega$                                                                                                                                                   | 85   | 92      | 100  |          |  |

| I <sub>IN-USB-CL</sub>    | USB input I-Limit 500mA                                                    | ISET2 = High; $R_{ISET} = 825\Omega$                                                                                                                                                    | 430  | 462 500 |      | mA       |  |

| ISET SHORT                | CIRCUIT TEST                                                               |                                                                                                                                                                                         |      |         |      |          |  |

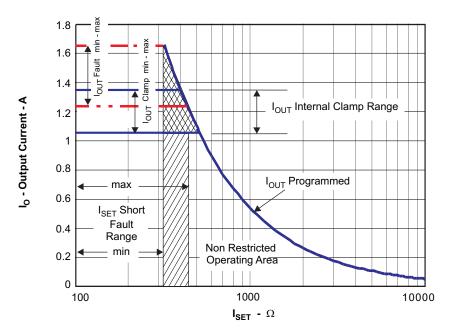

| R <sub>ISET_SHORT</sub>   | Highest Resistor value considered a fault (short). Monitored for lout>90mA | Riset: $600\Omega \rightarrow 250\Omega$ , $I_{OUT}$ latches off. Cycle power to Reset.                                                                                                 | 280  |         | 500  | Ω        |  |

| t <sub>DGL_SHORT</sub>    | Deglitch time transition from ISET short to lout disable                   | Clear fault by cycling IN or TS/BAT_EN                                                                                                                                                  |      | 1       |      | ms       |  |

| I <sub>OUT_CL</sub>       | Maximum OUT current limit Regulation (Clamp)                               | $V_{\text{IN}}$ = 5V, $V_{\text{OUT}}$ = 3.6V, $V_{\text{ISET2}}$ = Low, $R_{\text{ISET}}$ :<br>600 $\Omega$ $\rightarrow$ 250 $\Omega$ , lout latches off after $t_{\text{DGL-SHORT}}$ | 1.05 |         | 1.4  | А        |  |

| BATTERY SH                | IORT PROTECTION                                                            |                                                                                                                                                                                         |      |         |      |          |  |

| V <sub>OUT(SC)</sub>      | OUT pin short-circuit detection threshold/ precharge threshold             | $V_{OUT}$ :3V $\rightarrow$ 0.5V, no deglitch                                                                                                                                           | 0.75 | 0.8     | 0.85 | V        |  |

| V <sub>OUT(SC-HYS)</sub>  | OUT pin Short hysteresis                                                   | Recovery ≥ V <sub>OUT(SC)</sub> + V <sub>OUT(SC-HYS)</sub> ; Rising, no Deglitch                                                                                                        |      | 77      |      | mV       |  |

| I <sub>OUT(SC)</sub>      | Source current to OUT pin during short-circuit detection                   |                                                                                                                                                                                         | 10   | 15      | 20   | mA       |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

Over junction temperature range  $0^{\circ}C \le T_{J} \le 125^{\circ}C$  and recommended supply voltage (unless otherwise noted)

|                         | PARAMETER                                                                                                             | TEST CONDITIONS                                                                                                                                                                                                                                                                                 | MIN                                       | TYP                                  | MAX  | UNIT                      |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------|------|---------------------------|

| QUIESCENT               | CURRENT                                                                                                               |                                                                                                                                                                                                                                                                                                 |                                           |                                      |      | -                         |

| I <sub>OUT(PDWN)</sub>  | Battery current into OUT pin                                                                                          | $V_{IN} = 0V$                                                                                                                                                                                                                                                                                   |                                           |                                      | 1    | μА                        |

| I <sub>OUT(DONE)</sub>  | OUT pin current, charging terminated                                                                                  | $V_{IN} = 6V, V_{OUT} > V_{OUT(REG)}$                                                                                                                                                                                                                                                           |                                           |                                      | 6    | μΛ                        |

| I <sub>IN(STDBY)</sub>  | Standby current into IN pin                                                                                           | TS = LO, V <sub>IN</sub> ≤ 6V                                                                                                                                                                                                                                                                   |                                           |                                      | 125  | μΑ                        |

| I <sub>CC</sub>         | Active supply current, IN pin                                                                                         | $\begin{split} TS &= \text{open, V}_{\text{IN}} = 6\text{V, TTDM} - \text{no load on OUT pin,} \\ V_{\text{OUT}} &> V_{\text{OUT(REG)}}, \text{ IC enabled} \end{split}$                                                                                                                        |                                           | 0.8                                  | 1.0  | mA                        |

| BATTERY CH              | IARGER FAST-CHARGE                                                                                                    |                                                                                                                                                                                                                                                                                                 |                                           |                                      |      |                           |

| $V_{OUT(REG)}$          | Battery regulation voltage                                                                                            | $V_{IN} = 5.5V, I_{OUT} = 25mA, (V_{TS-45^{\circ}C} \le V_{TS} \le V_{TS-0^{\circ}C})$                                                                                                                                                                                                          | 4.16                                      | 4.2                                  | 4.23 | V                         |

| $V_{O\_HT(REG)}$        | Battery hot regulation Voltage,<br>bq24092/3                                                                          | $V_{IN} = 5.5V$ , $I_{OUT} = 25mA$ , $V_{TS-60^{\circ}C} \le V_{TS} \le V_{TS-45^{\circ}C}$                                                                                                                                                                                                     | 4.02                                      | 4.06                                 | 4.1  | V                         |

| I <sub>OUT(RANGE)</sub> | Programmed Output "fast charge" current range                                                                         | $V_{OUT(REG)} > V_{OUT} > V_{LOWV}$ ; $V_{IN} = 5V$ , ISET2=Lo, $R_{ISET} = 675$ to $10.8k\Omega$                                                                                                                                                                                               | 10                                        |                                      | 1000 | mA                        |

| $V_{\text{DO(IN-OUT)}}$ | Drop-Out, VIN – VOUT                                                                                                  | Adjust VIN down until $I_{OUT}$ = 0.5A, $V_{OUT}$ = 4.15V, $R_{ISET}$ = 675 , ISET2=Lo (adaptor mode); $T_J \le 100^{\circ}C$                                                                                                                                                                   |                                           | 325                                  | 520  | mV                        |

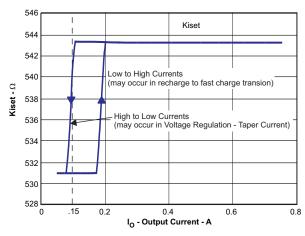

| I <sub>OUT</sub>        | Output "fast charge" formula                                                                                          | $V_{OUT(REG)} > V_{OUT} > V_{LOWV}$ ; $V_{IN} = 5V$ , ISET2 = Lo                                                                                                                                                                                                                                |                                           | K <sub>ISET</sub> /R <sub>ISET</sub> |      | Α                         |

|                         |                                                                                                                       | $R_{ISET} = K_{ISET} / I_{OUT}$ ; 50 < $I_{OUT}$ < 800 mA                                                                                                                                                                                                                                       | 510                                       | 540                                  | 565  |                           |

| $K_{ISET}$              | Fast charge current factor                                                                                            | $R_{ISET} = K_{ISET} / I_{OUT}$ ; 25 < $I_{OUT}$ < 50 mA                                                                                                                                                                                                                                        | 480                                       | 527                                  | 580  | ΑΩ                        |

|                         |                                                                                                                       | $R_{ISET} = K_{ISET} / I_{OUT}$ ; 10 < $I_{OUT}$ < 25 mA                                                                                                                                                                                                                                        | 350                                       | 520                                  | 680  |                           |

| PRECHARGE               | - SET BY PRETERM PIN                                                                                                  |                                                                                                                                                                                                                                                                                                 |                                           |                                      |      |                           |

| $V_{LOWV}$              | Pre-charge to fast-charge transition threshold                                                                        |                                                                                                                                                                                                                                                                                                 | 2.4                                       | 2.5                                  | 2.6  | V                         |

| t <sub>DGL1(LOWV)</sub> | Deglitch time on pre-charge to fast-charge transition                                                                 |                                                                                                                                                                                                                                                                                                 |                                           | 70                                   |      | μS                        |

| t <sub>DGL2(LOWV)</sub> | Deglitch time on fast-charge to pre-charge transition                                                                 |                                                                                                                                                                                                                                                                                                 |                                           | 32                                   |      | ms                        |

| I <sub>PRE-TERM</sub>   | Refer to the Termination Section                                                                                      |                                                                                                                                                                                                                                                                                                 |                                           |                                      |      |                           |

| %PRECHG                 | Pre-charge current, default setting                                                                                   | $V_{OUT} < V_{LOWV}; R_{ISET} = 1080\Omega;$<br>$R_{PRE-TERM} = High Z$                                                                                                                                                                                                                         | 18                                        | 20                                   | 22   | %l <sub>OUT-</sub><br>cc  |

|                         | Pre-charge current formula                                                                                            | $R_{PRE-TERM} = K_{PRE-CHG} (\Omega/\%) \times \%_{PRE-CHG} (\%)$                                                                                                                                                                                                                               | R <sub>PRE</sub>                          | -TERM/K <sub>PRE-CHG%</sub>          |      |                           |

| V                       | 9/ Dro pharas Factor                                                                                                  | $\begin{split} &V_{OUT} < V_{LOWV},  V_{IN} = 5V,  R_{PRE\text{-}TERM} = 2k \text{ to } 10k\Omega; \\ &R_{ISET} = 1080\Omega  ,  R_{PRE\text{-}TERM} = K_{PRE\text{-}CHG} \times \% I_{FAST\text{-}CHG}, \\ &\text{where } \% I_{FAST\text{-}CHG} \text{ is } 20 \text{ to } 100\% \end{split}$ | 90                                        | 100                                  | 110  | Ω/%                       |

| K <sub>PRE-CHG</sub>    | % Pre-charge Factor                                                                                                   | $\begin{split} &V_{OUT} < V_{LOWV},  V_{IN} = 5V,  R_{PRE-TERM} = 1k  \text{to}  2k\Omega; \\ &R_{ISET} = 1080\Omega,  R_{PRE-TERM} = K_{PRE-CHG} \times  \%I_{FAST-CHG}, \\ &\text{where}   \%I_{FAST-CHG}  \text{is}  10\%  \text{to}  20\% \end{split}$                                      | 84                                        | 100                                  | 117  | Ω/%                       |

| TERMINATIO              | N – SET BY PRE-TERM PIN                                                                                               |                                                                                                                                                                                                                                                                                                 |                                           |                                      |      |                           |

| 0/                      | Termination Threshold Current, default setting                                                                        | V <sub>OUT</sub> > V <sub>RCH</sub> ; R <sub>ISET</sub> = 1k;<br>R <sub>PRE-TERM</sub> = High Z                                                                                                                                                                                                 | 9                                         | 10                                   | 11   | %l <sub>OUT</sub> .<br>cc |

| % <sub>TERM</sub>       | Termination Current Threshold Formula                                                                                 | $R_{PRE-TERM} = K_{TERM} (\Omega/\%) \times \%TERM (\%)$                                                                                                                                                                                                                                        | R <sub>PRE-TERM</sub> / K <sub>TERM</sub> |                                      |      |                           |

| K <sub>TERM</sub>       | % Term Factor                                                                                                         | $\begin{array}{l} V_{OUT} > V_{RCH}, \ V_{IN} = 5V, \ R_{PRE\text{-}TERM} = 2k \ to \ 10k\Omega \ ; \\ R_{ISET} = 750\Omega \ K_{TERM} \times \% I_{FAST\text{-}CHG}, \ where \ \% I_{FAST\text{-}CHG} \\ is \ 10 \ to \ 50\% \end{array}$                                                      | 182                                       | 200                                  | 216  | Ω/%                       |

| TERW                    |                                                                                                                       | $V_{OUT}$ > $V_{RCH}$ , $V_{IN}$ = 5V, $R_{PRE-TERM}$ = 1k to 2kΩ; $R_{ISET}$ = 750Ω $K_{TERM}$ × %lset, where %lset is 5 to 10%                                                                                                                                                                | 174                                       | 199                                  | 224  |                           |

| I <sub>PRE-TERM</sub>   | Current for programming the term. and pre-chg with resistor. I <sub>Term-Start</sub> is the initial PRE-TERM current. | R <sub>PRE-TERM</sub> = 2k, V <sub>OUT</sub> = 4.15V                                                                                                                                                                                                                                            | 71                                        | 75                                   | 81   | μΑ                        |

| %TERM                   | Termination current formula                                                                                           |                                                                                                                                                                                                                                                                                                 | R                                         | TERM/ KTERM                          |      | %                         |

| t <sub>DGL(TERM)</sub>  | Deglitch time, termination detected                                                                                   |                                                                                                                                                                                                                                                                                                 |                                           | 29                                   |      | ms                        |

| I <sub>Term-Start</sub> | Elevated PRE-TERM current for, t <sub>Term-Start</sub> , during start of charge to prevent recharge of full battery,  |                                                                                                                                                                                                                                                                                                 | 80                                        | 85                                   | 92   | μА                        |

| t <sub>Term-Start</sub> | Elevated termination threshold initially active for t <sub>Term-Start</sub>                                           |                                                                                                                                                                                                                                                                                                 |                                           | 1.25                                 |      | min                       |

**"≝特®Q24090"供应商**

### **ELECTRICAL CHARACTERISTICS (continued)**

Over junction temperature range 0°C ≤ T<sub>J</sub> ≤ 125°C and recommended supply voltage (unless otherwise noted)

|                             | PARAMETER                                                                                          | TEST CONDITIONS                                                                                                                                                                                                          | MIN                           | TYP                        | MAX                            | UNIT |

|-----------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------|--------------------------------|------|

| RECHARGE O                  | R REFRESH                                                                                          |                                                                                                                                                                                                                          |                               |                            |                                |      |

|                             | Recharge detection threshold –<br>Normal Temp                                                      | $V_{IN}$ = 5V, $V_{TS}$ = 0.5V, $V_{OUT}$ : 4.25V $\rightarrow$ $V_{RCH}$                                                                                                                                                | V <sub>O(REG)</sub><br>-0.120 | V <sub>O(REG)</sub> -0.095 | V <sub>O(REG)</sub> -<br>0.070 | V    |

| V <sub>RCH</sub>            | Recharge detection threshold – Hot Temp                                                            | $V_{IN}$ = 5V, $V_{TS}$ = 0.2V, $V_{OUT}$ : 4.15V $\rightarrow$ $V_{RCH}$                                                                                                                                                | V <sub>O(REG)</sub><br>-0.130 | V <sub>O(REG)</sub> -0.105 | V <sub>O(REG)</sub> -<br>0.080 | V    |

| t <sub>DGL1(RCH)</sub>      | Deglitch time, recharge threshold detected                                                         | $\begin{array}{c} V_{\text{IN}} = 5\text{V, V}_{\text{TS}} = 0.5\text{V, V}_{\text{OUT}}\text{: } 4.25\text{V} \rightarrow 3.5\text{V in 1}\mu\text{s;} \\ t_{\text{DGL(RCH)}} \text{ is time to ISET ramp} \end{array}$ |                               | 29                         |                                | ms   |

| t <sub>DGL2(RCH)</sub>      | Deglitch time, recharge threshold detected in OUT-Detect Mode                                      | $V_{\text{IN}}$ = 5V, $V_{\text{TS}}$ = 0.5V, $V_{\text{OUT}}$ = 3.5V inserted; $t_{\text{DGL(RCH)}}$ is time to ISET ramp                                                                                               |                               | 3.6                        |                                | ms   |

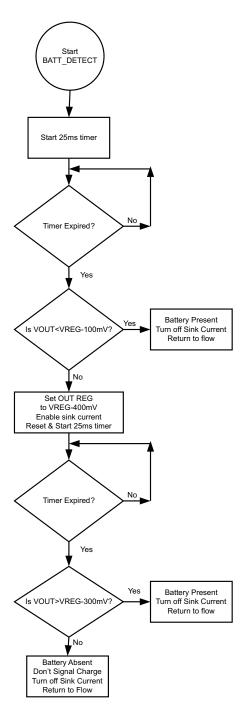

| BATTERY DE                  | TECT ROUTINE                                                                                       |                                                                                                                                                                                                                          |                               |                            |                                |      |

| $V_{REG-BD}$                | VOUT Reduced regulation during battery detect                                                      |                                                                                                                                                                                                                          | V <sub>O(REG)</sub><br>-0.450 | V <sub>O(REG)</sub> -0.400 | V <sub>O(REG)</sub> -<br>350   | ٧    |

| I <sub>BD-SINK</sub>        | Sink current during V <sub>REG-BD</sub>                                                            | V <sub>IN</sub> = 5V, V <sub>TS</sub> = 0.5V, Battery Absent                                                                                                                                                             | 7                             |                            | 10                             | mA   |

| t <sub>DGL(HI/LOW</sub>     | Regulation time at V <sub>REG</sub> or V <sub>REG-BD</sub>                                         |                                                                                                                                                                                                                          |                               | 25                         |                                | ms   |

| V <sub>BD-HI</sub>          | High battery detection threshold                                                                   | V <sub>IN</sub> = 5V, V <sub>TS</sub> = 0.5V, Battery Absent                                                                                                                                                             | V <sub>O(REG)</sub><br>-0.150 | V <sub>O(REG)</sub> -0.100 | V <sub>O(REG)</sub> -<br>0.050 | V    |

| V <sub>BD-LO</sub>          | Low battery detection threshold                                                                    | V <sub>IN</sub> = 5V, V <sub>TS</sub> = 0.5V, Battery Absent                                                                                                                                                             | V <sub>REG-BD</sub><br>+0.50  | V <sub>REG-BD</sub> +0.1   | V <sub>REG-BD</sub><br>+0.15   | V    |

| BATTERY CH                  | ARGING TIMERS AND FAULT TIMERS                                                                     |                                                                                                                                                                                                                          | *                             |                            |                                |      |

| t <sub>PRECHG</sub>         | Pre-charge safety timer value                                                                      | Restarts when entering Pre-charge; Always enabled when in pre-charge.                                                                                                                                                    | 1700                          | 1940                       | 2250                           | s    |

| t <sub>MAXCH</sub>          | Charge safety timer value                                                                          | Clears fault or resets at UVLO, TS/BAT_EN disable, OUT Short, exiting LOWV and Refresh                                                                                                                                   | 34000                         | 38800                      | 45000                          | s    |

| BATTERY-PAG                 | CK NTC MONITOR (Note 1); TS pin: 10                                                                | k and 100k NTC                                                                                                                                                                                                           |                               |                            |                                |      |

| I <sub>NTC-10k</sub>        | NTC bias current, bq24090/2                                                                        | V <sub>TS</sub> = 0.3V                                                                                                                                                                                                   | 48                            | 50                         | 52                             | μА   |

| I <sub>NTC-100k</sub>       | NTC bias current, bq24091/3                                                                        | V <sub>TS</sub> = 0.3V                                                                                                                                                                                                   | 4.8                           | 5.0                        | 5.2                            | μΑ   |

| I <sub>NTC-DIS-10k</sub>    | 10k NTC bias current when Charging is disabled, bq24090/2                                          | V <sub>TS</sub> = 0V                                                                                                                                                                                                     | 27                            | 30                         | 34                             | μΑ   |

| I <sub>NTC-DIS-100k</sub>   | 10k NTC bias current when Charging is disabled, bq24091/3                                          | V <sub>TS</sub> = 0V                                                                                                                                                                                                     | 4.4                           | 5.0                        | 5.8                            | μΑ   |

| I <sub>NTC-FLDBK-10k</sub>  | INTC is reduced prior to entering<br>TTDM to keep cold thermistor from<br>entering TTDM, bq24090/2 | V <sub>TS</sub> : Set to 1.525V                                                                                                                                                                                          | 4                             | 5                          | 6.5                            | μΑ   |

| I <sub>NTC-FLDBK-100k</sub> | INTC is reduced prior to entering TTDM to keep cold thermistor from entering TTDM, bq24091/3       | V <sub>TS</sub> : Set to 1.525V                                                                                                                                                                                          | 1.1                           | 1.5                        | 1.9                            | μΑ   |

| $V_{TTDM(TS)}$              | Termination and timer disable mode<br>Threshold – Enter                                            | $V_{TS}$ : 0.5V $\rightarrow$ 1.7V; Timer Held in Reset                                                                                                                                                                  | 1550                          | 1600                       | 1650                           | mV   |

| V <sub>HYS-TTDM(TS)</sub>   | Hysteresis exiting TTDM                                                                            | $V_{TS}$ : 1.7V $\rightarrow$ 0.5V; Timer Enabled                                                                                                                                                                        |                               | 100                        |                                | mV   |

| V <sub>CLAMP(TS)</sub>      | TS maximum voltage clamp                                                                           | V <sub>TS</sub> = Open (Float)                                                                                                                                                                                           | 1800                          | 1950                       | 2000                           | mV   |

| t                           | Deglitch exit TTDM between states                                                                  |                                                                                                                                                                                                                          |                               | 57                         |                                | ms   |

| t <sub>DGL(TTDM)</sub>      | Deglitch enter TTDM between states                                                                 |                                                                                                                                                                                                                          |                               | 8                          |                                | μS   |

| $V_{TS\_I\text{-}FLDBK}$    | TS voltage where INTC is reduce to keep thermistor from entering TTDM                              | INTC adjustment (90 to 10%; 45 to 6.6uS) takes place near this spec threshold. V <sub>TS</sub> : 1.425V → 1.525V                                                                                                         |                               | 1475                       |                                | mV   |

| C <sub>TS</sub>             | Optional Capacitance – ESD                                                                         |                                                                                                                                                                                                                          |                               | 0.22                       |                                | μF   |

| V <sub>TS-0°C</sub>         | Low temperature CHG Pending                                                                        | Low Temp Charging to Pending;<br>V <sub>TS</sub> : 1.0V → 1.5V                                                                                                                                                           | 1205                          | 1230                       | 1255                           | mV   |

| V <sub>HYS-0°C</sub>        | Hysteresis at 0°C                                                                                  | Charge pending to low temp charging;<br>V <sub>TS</sub> : 1.5V → 1V                                                                                                                                                      |                               | 86                         |                                | mV   |

| V <sub>TS-10°C</sub>        | Low temperature, half charge, bq24092/3                                                            | Normal charging to low temp charging;<br>$V_{TS}$ : 0.5V $\rightarrow$ 1V                                                                                                                                                | 765                           | 790                        | 815                            | mV   |

| V <sub>HYS-10°C</sub>       | Hysteresis at 10°C, bq24092/3                                                                      | Low temp charging to normal CHG; $V_{TS}$ : 1.0V $\rightarrow$ 0.5V                                                                                                                                                      |                               | 35                         |                                | mV   |

| V <sub>TS-45°C</sub>        | High temperature at 4.1V                                                                           | Normal charging to high temp CHG; $V_{TS}$ : 0.5V $\rightarrow$ 0.2V                                                                                                                                                     | 263                           | 278                        | 293                            | mV   |

| V <sub>HYS-45°C</sub>       | Hysteresis at 45°C                                                                                 | High temp charging to normal CHG; $V_{TS}$ : 0.2V $\rightarrow$ 0.5V                                                                                                                                                     |                               | 10.7                       |                                | mV   |

### **ELECTRICAL CHARACTERISTICS (continued)**

Over junction temperature range  $0^{\circ}C \le T_{J} \le 125^{\circ}C$  and recommended supply voltage (unless otherwise noted)

|                             | PARAMETER                                               | TEST CONDITIONS                                                     | MIN | TYP  | MAX  | UNIT |

|-----------------------------|---------------------------------------------------------|---------------------------------------------------------------------|-----|------|------|------|

| V <sub>TS-60°C</sub>        | High temperature Disable, bq24092/3                     | High temp charge to pending; $V_{TS}$ : 0.2V $\rightarrow$ 0.1V     | 170 | 178  | 186  | mV   |

| V <sub>HYS-60°C</sub>       | Hysteresis at 60°C, bq24092/3                           | Charge pending to high temp CHG; $V_{TS}$ : 0.1V $\rightarrow$ 0.2V |     | 11.5 |      | mV   |

|                             | Deglitch for TS thresholds: 10C,                        | Normal to Cold Operation; $V_{TS}$ : 0.6V $\rightarrow$ 1V          |     | 50   |      |      |

| t <sub>DGL(TS_10C)</sub>    | bq24092/3                                               | Cold to Normal Operation; $V_{TS}$ : $1V \rightarrow 0.6V$          |     | 12   |      | ms   |

| t <sub>DGL(TS)</sub>        | Deglitch for TS thresholds: 0/45/60C.                   | Battery charging                                                    |     | 30   |      | ms   |

| V <sub>TS-EN-10k</sub>      | Charge Enable Threshold, (10k NTC)                      | $V_{TS}$ : 0V $\rightarrow$ 0.175V;                                 | 80  | 88   | 96   | mV   |

| V <sub>TS-DIS_HYS-10k</sub> | HYS below V <sub>TS-EN-10k</sub> to Disable, (10k NTC)  | $V_{TS}$ : 0.125V $\rightarrow$ 0V;                                 |     | 12   |      | mV   |

| V <sub>TS-EN-100k</sub>     | Charge Enable Threshold, bq24090/2                      | V <sub>TS</sub> : 0V → 0.175V;                                      | 140 | 150  | 160  | mV   |

| V <sub>TS-DIS_HYS-</sub>    | HYS below V <sub>TS-EN-100k</sub> to Disable, bq24091/3 | $V_{TS}$ : 0.125V $\rightarrow$ 0V;                                 |     | 50   |      | mV   |

| THERMAL RE                  | GULATION                                                |                                                                     |     |      |      |      |

| $T_{J(REG)}$                | Temperature regulation limit                            |                                                                     |     | 125  |      | °C   |

| $T_{J(OFF)}$                | Thermal shutdown temperature                            |                                                                     |     | 155  |      | °C   |

| T <sub>J(OFF-HYS)</sub>     | Thermal shutdown hysteresis                             |                                                                     |     | 20   |      | °C   |

| LOGIC LEVEL                 | S ON ISET2                                              |                                                                     |     |      |      |      |

| V <sub>IL</sub>             | Logic LOW input voltage                                 | Sink 8 μA                                                           |     |      | 0.4  | V    |

| V <sub>IH</sub>             | Logic HIGH input voltage                                | Source 8 µA                                                         | 1.4 |      |      | V    |

| I <sub>IL</sub>             | Sink current required for LO                            | V <sub>ISET2</sub> = 0.4V                                           | 2   |      | 9    | μА   |

| I <sub>IH</sub>             | Source current required for HI                          | V <sub>ISET2</sub> = 1.4V                                           | 1.1 |      | 8    | μА   |

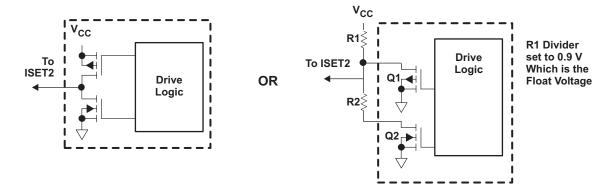

| V <sub>FLT</sub>            | ISET2 Float Voltage                                     |                                                                     | 575 | 900  | 1225 | mV   |

| LOGIC LEVEL                 | S ON CHG AND PG                                         |                                                                     |     |      |      |      |

| V <sub>OL</sub>             | Output LOW voltage                                      | I <sub>SINK</sub> = 5 mA                                            |     |      | 0.4  | V    |

| I <sub>LEAK</sub>           | Leakage current into IC                                 | $V_{\overline{CHG}} = 5V, V_{\overline{PG}} = 5V$                   |     |      | 1    | μА   |

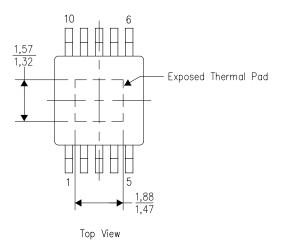

### **PIN CONFIGURATION**

### **PIN FUNCTIONS**

| NAME                    | PIN                       | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|---------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN                      | 1                         | I   | Input power, connected to external DC supply (AC adapter or USB port). Expected range of bypass capacitors $1\mu F$ to $10\mu F$ , connect from IN to $V_{SS}$ .                                                                                                                                                                                                                                                                                                                                                            |

| OUT                     | 10                        | 0   | Battery Connection. System Load may be connected. Average load should not be excessive, allowing battery to charge within the 10 hour safety timer window. Expected range of bypass capacitors $1\mu F$ to $10\mu F$ .                                                                                                                                                                                                                                                                                                      |

| PRE-TERM                | 4                         | I   | Programs the Current Termination Threshold (5 to 50% of lout which is set by ISET) and Sets the Pre-Charge Current to twice the Termination Current Level.                                                                                                                                                                                                                                                                                                                                                                  |

|                         |                           |     | Expected range of programming resistor is 1k to 10kΩ (2k: lpgm/10 for term; lpgm/5 for precharge)                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ISET                    | 2                         | I   | Programs the Fast-charge current setting. External resistor from ISET to VSS defines fast charge current value. Range is 10.8k (50mA) to 675 $\Omega$ (800mA).                                                                                                                                                                                                                                                                                                                                                              |

| ISET2                   | 7                         | I   | Programming the Input/Output Current Limit for the USB or Adaptor source: High = 500mAmax, Low = ISET, FLOAT = 100mAmax.                                                                                                                                                                                                                                                                                                                                                                                                    |

| TS                      | 9                         | I   | Temperature sense pin connected to bq24090/2 -10k at 25°C NTC thermistor & bq24091/3 -100k at 25°C NTC thermistor, in the battery pack. Floating TS Pin or pulling High puts part in TTDM "Charger" Mode and disable TS monitoring, Timers and Termination. Pulling pin Low disables the IC. If NTC sensing is not needed, connect this pin to VSS through an external 10 k $\Omega$ /100k $\Omega$ resistor. A 250k $\Omega$ from TS to ground will prevent IC entering TTDM mode when battery with thermistor is removed. |

| VSS                     | 3                         | _   | Ground terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CHG                     | 8                         | 0   | Low (FET on) indicates charging and Open Drain (FET off) indicates no Charging or Charge complete.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PG                      | 5                         | 0   | Low (FET on) indicates the input voltage is above UVLO and the OUT (battery) voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| NC                      | 6                         | NA  | Do not make a connection to this pin (for internal use) – Do not route through this pin                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Thermal PAD and Package | Pad<br>5x3mm <sup>2</sup> | _   | There is an internal electrical connection between the exposed thermal pad and the VSS pin of the device. The thermal pad must be connected to the same potential as the VSS pin on the printed circuit board. Do not use the thermal pad as the primary ground input for the device. VSS pin must be connected to ground at all times                                                                                                                                                                                      |

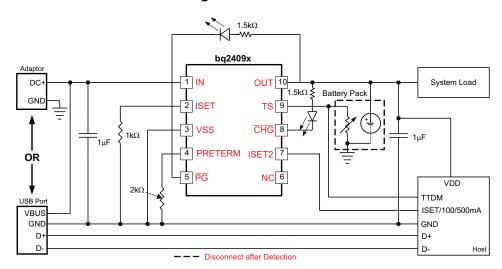

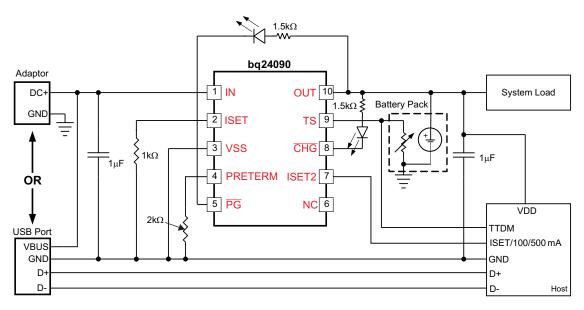

# Typical Application Circuit: bq2409x

$I_{OUT\_FAST\_CHG} = 540 \text{mA}$ ;  $I_{OUT\_PRE\_CHG} = 108 \text{mA}$ ;  $I_{OUT\_TERM} = 54 \text{mA}$

# <u>₩豐特學Q24090"供应商</u>

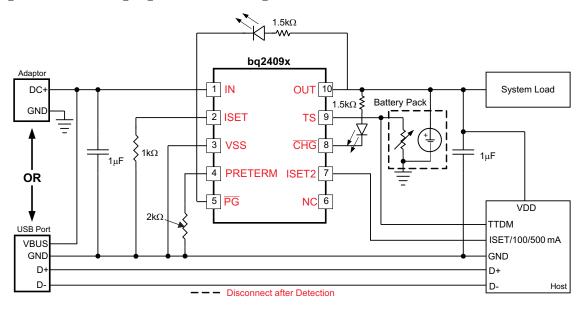

### **FUNCTIONAL BLOCK DIAGRAM**

#### TYPICAL OPERATIONAL CHARACTERISTICS

SETUP: bq2409x typical applications schematic;  $V_{IN} = 5V$ ,  $V_{BAT} = 3.6V$  (unless otherwise indicated)

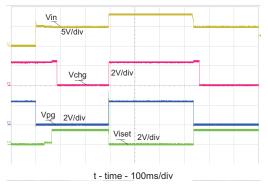

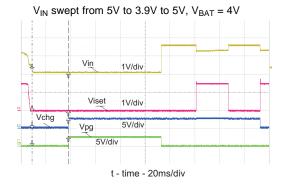

#### POWER UP, DOWN, OVP, DISABLE AND ENABLE WAVEFORMS

Figure 1. OVP 8V Adaptor - Hot Plug

Figure 2. OVP from Normal Power-up Operation –  $V_{IN}$  0V  $\rightarrow$  5V  $\rightarrow$  6.8V  $\rightarrow$ 5V

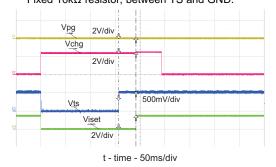

10kΩ resistor from TS to GND. 10kΩ is shorted to disable the IC. Fixed 10kΩ resistor, between TS and GND.

Figure 3. TS Enable and Disable

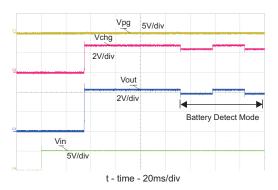

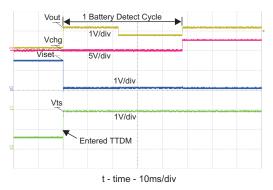

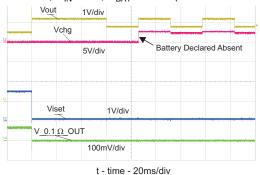

Figure 4. Hot Plug Source w/No Battery – Battery Detection

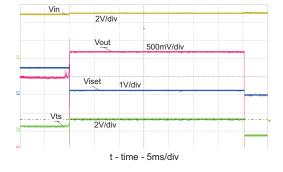

Figure 5. Battery Removal – GND Removed 1st, 42  $\Omega$  Load

Figure 6. Battery Removal with OUT and TS Disconnect 1st, With 100  $\Omega$  Load

Continuous battery detection when not in TTDM.

### TYPICAL OPERATIONAL CHARACTERISTICS (continued)

SETUP: bq2409x typical applications schematic;  $V_{IN} = 5V$ ,  $V_{BAT} = 3.6V$  (unless otherwise indicated)

Figure 7. Battery Removal with fixed TS = 0.5V

#### PROTECTION CIRCUITS WAVEFORMS

CH4: lout (1A/Div)

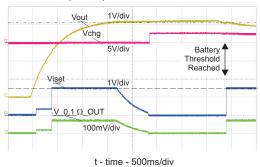

Battery voltage swept from 0V to 4.25V to 3.9V.

CH4: lout (1A/Div)

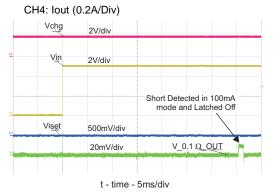

CH4: lout (0.2A/Div)

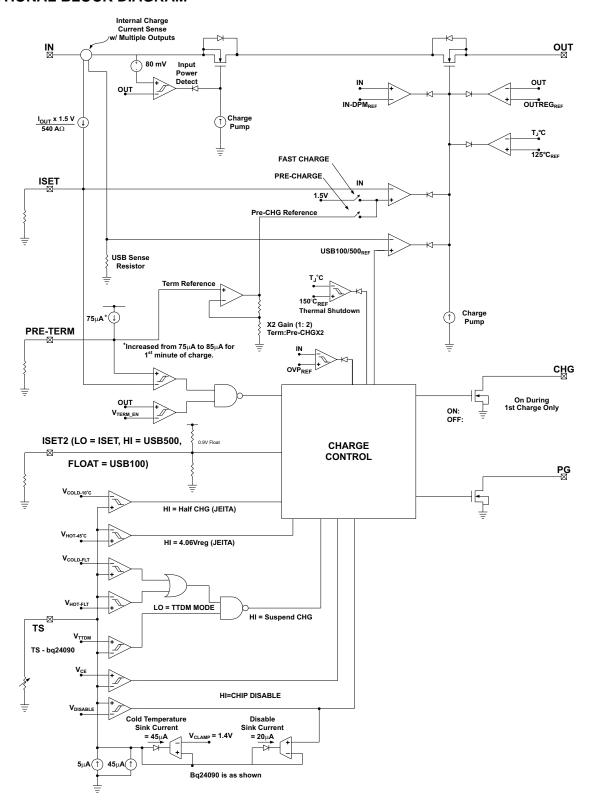

Figure 8. Battery Charge Profile

Figure 9. ISET Shorted During Normal Operation

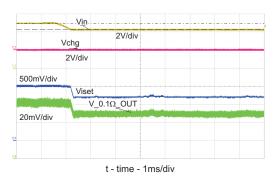

Figure 10. ISET Shorted Prior to USB Power-up

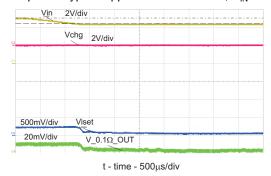

Figure 11. DPM - Adaptor Current Limits - Vin Regulated

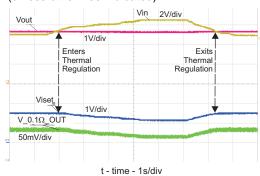

The IC temperature rises to 125°C and enters thermal regulation. Charge current is reduced to regulate the IC at 125°C. VIN is reduced, the IC temperature drops, the charge current returns to the programmed value.

### TYPICAL OPERATIONAL CHARACTERISTICS (continued)

SETUP: bq2409x typical applications schematic;  $V_{IN} = 5V$ ,  $V_{BAT} = 3.6V$  (unless otherwise indicated)

Figure 12. DPM – USB Current Limits – Vin Regulated to 4 4V

Figure 13. Thermal Reg. – Vin increases PWR/lout Reduced

Figure 14. Entering and Exiting Sleep Mode

Figure 15. K<sub>ISET</sub> for Low and High Currents

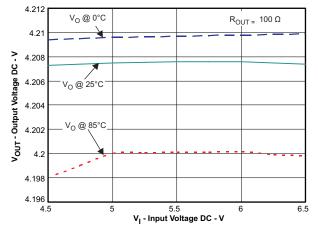

Figure 16. Line Regulation

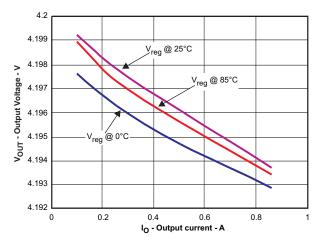

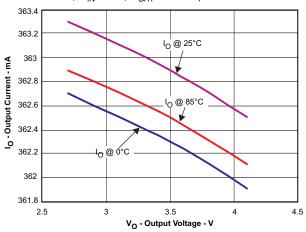

Figure 17. Load Regulation Over Temperature

<u>₩豐博型Q24090"供应商</u>

### TYPICAL OPERATIONAL CHARACTERISTICS (continued)

SETUP: bq2409x typical applications schematic; V<sub>IN</sub> = 5V, V<sub>BAT</sub> = 3.6V (unless otherwise indicated)

Figure 18. Current Regulation Over Temperature

#### **FUNCTIONAL GENERAL DESCRIPTION**

The bq2409x is a highly integrated family of 5x3mm² single cell Li-Ion chargers. The charger can be used to charge a battery, power a system or both. The charger has three phases of charging: Pre-charge to recover a fully discharged battery, fast-charge constant current to supply the buck charge safely and voltage regulation to safely reach full capacity. The charger is very flexible, allowing programming of the fast-charge current and Pre-charge/Termination Current. This charger is designed to work with a USB connection or Adaptor (DC out). The charger also checks to see if a battery is present.

The charger also comes with a full set of safety features: JEITA Temperature Standard, Over-Voltage Protection, DPM-IN, Safety Timers, and ISET short protection. All of these features and more are described in detail below.

The charger is designed for a single power path from the input to the output to charge a single cell Li-lon battery pack. Upon application of a 5VDC power source the ISET and OUT short checks are performed to assure a proper charge cycle.

If the battery voltage is below the LOWV threshold, the battery is considered discharged and a preconditioning cycle begins. The amount of precharge current can be programmed using the PRE-TERM pin which programs a percent of fast charge current (10 to 100%) as the precharge current. This feature is useful when the system load is connected across the battery "stealing" the battery current. The precharge current can be set higher to account for the system loading while allowing the battery to be properly conditioned. The PRE-TERM pin is a dual function pin which sets the precharge current level and the termination threshold level. The termination "current threshold" is always half of the precharge programmed current level.

Once the battery voltage has charged to the  $V_{LOWV}$  threshold, fast charge is initiated and the fast charge current is applied. The fast charge constant current is programmed using the ISET pin. The constant current provides the bulk of the charge. Power dissipation in the IC is greatest in fast charge with a lower battery voltage. If the IC reaches 125°C the IC enters thermal regulation, slows the timer clock by half and reduce the charge current as needed to keep the temperature from rising any further. Figure 19 shows the charging profile with thermal regulation. Typically under normal operating conditions, the IC's junction temperature is less than 125°C and thermal regulation is not entered.

Once the cell has charged to the regulation voltage the voltage loop takes control and holds the battery at the regulation voltage until the current tapers to the termination threshold. The termination can be disabled if desired. The CHG pin is low (LED on) during the first charge cycle only and turns off once the termination threshold is reached, regardless if termination, for charge current, is enabled or disabled.

Further details are mentioned in the Operating Modes section.

### **FUNCTIONAL GENERAL DESCRIPTION (continued)**

Figure 19. Charging Profile With Thermal Regulation

<u>₩豐精學Q24090"供应商</u>

#### DETAILED FUNCTIONAL DESCRIPTION

#### Power-Down or Undervoltage Lockout (UVLO)

The bq2409x family is in power down mode if the IN pin voltage is less than UVLO. The part is considered "dead" and all the pins are high impedance. Once the IN voltage rises above the UVLO threshold the IC will enter Sleep Mode or Active mode depending on the OUT pin (battery) voltage.

### **Under Voltage Lockout (UVLO):**

The bq2409x family is in power down mode if the IN pin voltage is less than V<sub>UVLO</sub>. The part is considered "dead" and all the pins are high impedance.

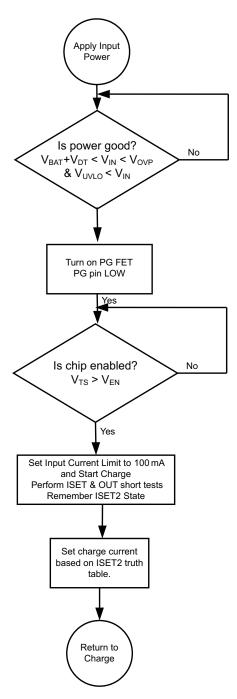

### Power-up

The IC is alive after the IN voltage ramps above UVLO (see sleep mode), resets all logic and timers, and starts to perform many of the continuous monitoring routines. Typically the input voltage quickly rises through the UVLO and sleep states where the IC declares power good, starts the qualification charge at 100mA, sets the input current limit threshold base on the ISET2 pin, starts the safety timer and enables the CHG pin. See Figure 20.

### Sleep Mode

If the IN pin voltage is between than  $V_{OUT}+V_{DT}$  and UVLO, the charge current is disabled, the safety timer counting stops (not reset) and the  $\overline{PG}$  and  $\overline{CHG}$  pins are high impedance. As the input voltage rises and the charger exits sleep mode, the  $\overline{PG}$  pin goes low, the safety timer continues to count, charge is enabled and the  $\overline{CHG}$  pin returns to its previous state. See Figure 21

### **New Charge Cycle**

A new charge cycle is started when a good power source is applied, performing a chip disable/enable (TS pin), exiting Termination and Timer Disable Mode (TTDM), detecting a battery insertion or the OUT voltage dropping below the  $V_{RCH}$  threshold. The CHG pin is active low only during the first charge cycle, therefore exiting TTDM or a dropping below  $V_{RCH}$  will not turn on the CHG pin FET, if the CHG pin is already high impedance.

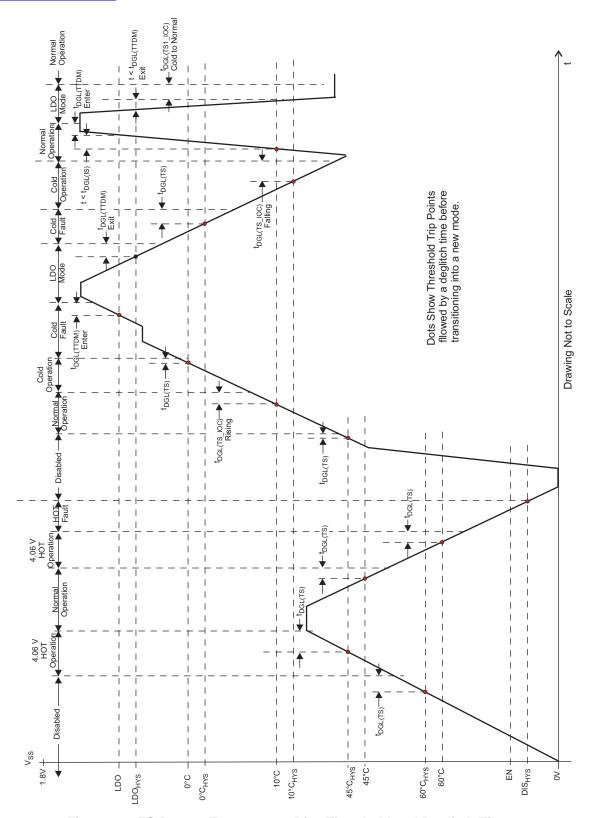

Figure 20. TS Battery Temperature Bias Threshold and Deglitch Timers

Figure 21. bq2409x Power-Up Flow Diagram

# Overvoltage-Protection (OVP) - Continuously Monitored

If the input source applies an overvoltage, the pass FET, if previously on, turns off after a deglitch,  $t_{BLK(OVP)}$ . The timer ends and the CHG and PG pin goes to a high impedance state. Once the overvoltage returns to a normal voltage, the PG pin goes low, timer continues, charge continues and the CHG pin goes low after a 25ms deglitch. PG pin is optional on some packages

### Power Good Indication (PG)

After application of a 5V source, the input voltage rises above the UVLO and sleep thresholds ( $V_{IN}>V_{BAT}+V_{DT}$ ), but is less than OVP ( $V_{IN}<V_{OVP}$ ,), then the PG FET turns on and provides a low impedance path to ground. See Figure 1, Figure 2, and Figure 14.

#### **CHG** Pin Indication

The charge pin has an internal open drain FET which is on (pulls down to  $V_{SS}$ ) during the first charge only (independent of TTDM) and is turned off once the battery reaches voltage regulation and the charge current tapers to the termination threshold set by the PRE-TERM resistor.

The charge pin is high impedance in sleep mode and OVP (if  $\overline{PG}$  is high impedance) and return to its previous state once the condition is removed.

Cycling input power, pulling the TS pin low and releasing or entering pre-charge mode causes the  $\overline{\text{CHG}}$  pin to go reset (go low if power is good and a discharged battery is attached) and is considered the start of a first charge.

### CHG and PG LED Pull-up Source

For host monitoring, a pull-up resistor is used between the "STATUS" pin and the V<sub>CC</sub> of the host and for a visual indication a resistor in series with an LED is connected between the "STATUS" pin and a power source. If the CHG or PG source is capable of exceeding 7V, a 6.2V Zener should be used to clamp the voltage. If the source is the OUT pin, note that as the battery changes voltage, the brightness of the LEDs vary.

| Charging State | CHG FET/LED       |

|----------------|-------------------|

| 1st Charge     | ON                |

| Refresh Charge |                   |

| OVP            | OFF               |

| SLEEP          |                   |

| TEMP FAULT     | ON for 1st Charge |

| V <sub>IN</sub> Power Good State                     | PG FET/LED |  |  |  |

|------------------------------------------------------|------------|--|--|--|

| UVLO                                                 |            |  |  |  |

| SLEEP Mode                                           | OFF        |  |  |  |

| OVP Mode                                             |            |  |  |  |

| Normal Input $(V_{OUT} + V_{DT} < V_{IN} < V_{OUP})$ | ON         |  |  |  |

| PG is independent of chip disable                    |            |  |  |  |

### IN-DPM (V<sub>IN-DPM</sub> or IN-DPM)

The IN-DPM feature is used to detect an input source voltage that is folding back (voltage dropping), reaching its current limit due to excessive load. When the input voltage drops to the  $V_{\text{IN-DPM}}$  threshold the internal pass FET starts to reduce the current until there is no further drop in voltage at the input. This would prevent a source with voltage less than  $V_{\text{IN-DPM}}$  to power the out pin. This works well with current limited adaptors and USB ports as long as the nominal voltage is above 4.3V and 4.4V respectively. This is an added safety feature that helps protect the source from excessive loads.

#### OUT

The Charger's OUT pin provides current to the battery and to the system, if present. This IC can be used to charge the battery plus power the system, charge just the battery or just power the system (TTDM) assuming the loads do not exceed the available current. The OUT pin is a current limited source and is inherently protected against shorts. If the system load ever exceeds the output programmed current threshold, the output will be discharged unless there is sufficient capacitance or a charged battery present to supplement the excessive load.

<u>₩豐铈學Q24090"供应商</u>

#### **ISET**

An external resistor is used to Program the Output Current (50 to 800mA) and can be used as a current monitor.

$$R_{ISET} = K_{ISET} \div I_{OUT} \tag{1}$$

Where:

I<sub>OUT</sub> is the desired fast charge current;

K<sub>ISET</sub> is a gain factor found in the electrical specification

For greater accuracy at lower currents, part of the sense FET is disabled to give better resolution. Figure 15 shows the transition from low current to higher current. Going from higher currents to low currents, there is hysteresis and the transition occurs around 0.15A.

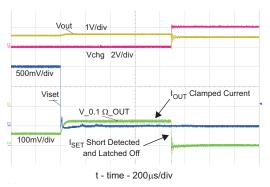

The ISET resistor is short protected and will detect a resistance lower than ≉340Ω. The detection requires at least 80mA of output current. If a "short" is detected, then the IC will latch off and can only be reset by cycling the power. The OUT current is internally clamped to a maximum current between 1.1A and 1.35A and is independent of the ISET short detection circuitry, as shown in Figure 23. Also, see Figure 9 and Figure 10.

Figure 22. Operation Over TS Bias Voltage

Figure 23. Programmed/Clamped Out Current

### PRE TERM - Pre-Charge and Termination Programmable Threshold

Pre-Term is used to program both the pre-charge current and the termination current threshold. The pre-charge current level is a factor of two higher than the termination current level. The termination can be set between 5% and 50% of the programmed output current level set by ISET. If left floating the termination and pre-charge are set internally at 10/20% respectively. The pre-charge-to-fast-charge,  $V_{lowv}$  threshold is set to 2.5V.