# CV110-1A elfular-b端中南gh Linearity Downconverter

- High dynamic range downconverter with integrated LO, IF, & RF amps

- RF: 800 915 MHz

- IF: 65 120 MHz

- +37 dBm Output IP3

- +20 dBm Output P1dB

- 5 dB Noise Figure

- +5V Single supply operation

- Pb-free 6mm 28-pin QFN package

- Low-side LO configuration

- Common footprint with other PCS/UMTS versions

# Specifications (1)

### **Product Description**

The CV110-1A is a high linearity downconverter designed to meet the demanding issues for performance, functionality, and cost goals of current and next generation mobile infrastructure. It provides high dynamic range performance in a low profile surfacemount leadless package that measures  $6 \times 6$  mm square.

Functionality includes RF amplification, frequency conversion and IF amplification, while an integrated LO driver amplifier powers the passive mixer. The MCM is implemented with reliable and mature GaAs MESFET and InGaP HBT technology.

Typical applications include frequency downconversion used in CDMA/GSM/TDMA, CDMA2000, W-CDMA, and EDGE 2.5G and 3G mobile base transceiver stations for cellular frequency bands.

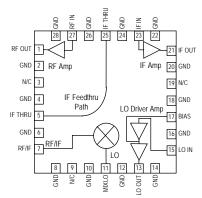

# **Functional Diagram**

**Product Information**

| Parameters                             | Units            | Min  | Тур       | Max  | Comments                        |

|----------------------------------------|------------------|------|-----------|------|---------------------------------|

| RF Frequency Range                     | MHz              |      | 800 - 915 |      |                                 |

| LO Frequency Range                     | MHz              |      | 680 - 850 |      |                                 |

| IF Center Frequency Range              | MHz              |      | 65 - 120  |      | See note 2                      |

| % Bandwidth around IF center frequency | %                |      | ±7.5      |      | See note 3                      |

| IF Test Frequency                      | MHz              |      | 75        |      |                                 |

| SSB Conversion Gain                    | dB               |      | 22        |      | $Temp = 25 \ ^{\circ}C$         |

| Gain Drift over Temp (-40 to 85 °C)    | dB               |      | ±1.5      |      | Referenced to +25 °C            |

| Output IP3                             | dBm              |      | +37       |      | See note 4                      |

| Output IP2                             | dBm              |      | +45       |      | See note 4                      |

| Output 1dB Compression Point           | dBm              |      | +20       |      |                                 |

| Noise Figure                           | dB               |      | 5         |      | See note 5                      |

| LO Input Drive Level                   | dBm              | -2.5 | 0         | +2.5 |                                 |

| LO-RF Isolation                        | dB               |      | 60        |      | $P_{LO} = 0 \text{ dBm}$        |

| LO-IF Isolation                        | dB               |      | 40        |      | $P_{LO} = 0 \text{ dBm}$        |

| Return Loss: RF Port                   | dB               |      | 15        |      |                                 |

| Return Loss: LO Port                   | dB               |      | 10        |      |                                 |

| Return Loss: IF Port                   | dB               |      | 15        |      |                                 |

| Operating Supply Voltage               | V                | +4.9 | +5        | +5.1 |                                 |

| Supply Current                         | mA               | 290  | 360       | 480  |                                 |

| FIT Rating                             | failures/1E9 hrs |      |           | 72.1 | @ 70° C ambient, 90% confidence |

| Junction Temperature                   | °C               |      |           | 160  | See note 6                      |

Specifications when using the application specific circuit (shown on page 3) with a low side LO = 0 dBm in a downconverting application over the operating case temperature range.

IF matching components affect the center IF frequency. Proper component values for other IF center frequencies than shown can be provided by emailing to applications.engineering@wj.com.

The IF bandwidth of the converter is defined as 15% around any center frequency in its operating IF frequency range. The bandwidth is determined with external components. Specifications are valid around

the total +7.5% bandwidth, i.e. with a center frequency of 240 MHz, the specifications are valid from  $80 \pm 6$  MHz. Assumes the supply voltage = +5 V. OIP3 is measured with  $\Delta f = 1$  MHz with IF<sub>out</sub> = 5 dBm / tone. Assumes LO injection noise is filtered at the thermal noise floor, -174 dBm/Hz, at the RF, IF, and Image frequencies.

6. The maximum junction temperature ensures a minimum MTTF rating of 1 million hours of usage

# **Absolute Maximum Rating**

| Parameter                  | Rating         | Ordering In   | formation                                    |

|----------------------------|----------------|---------------|----------------------------------------------|

| Operating Case Temperature | -40 to +85 °C  | e. de lig     |                                              |

| Storage Temperature        | -55 to +125 °C | Part No.      | Description                                  |

| DC Voltage                 | +6 V           |               | Cellular-band High Linearity Downconverter   |

| Junction Temperature       | +220 °C        | CV110-1AF     | (lead-free/RoHS-compliant 6x6mm QFN package) |

| RF Input (continuous)      | +2 dBm         | CV110-1APCB75 | Fully Assembled Eval. Board, IF = 75MHz      |

Operation of this device above any of these parameters may cause permanent damage.

#### Specifications and information are subject to change without notice

#### The Communications Edge TM

**Product Information**

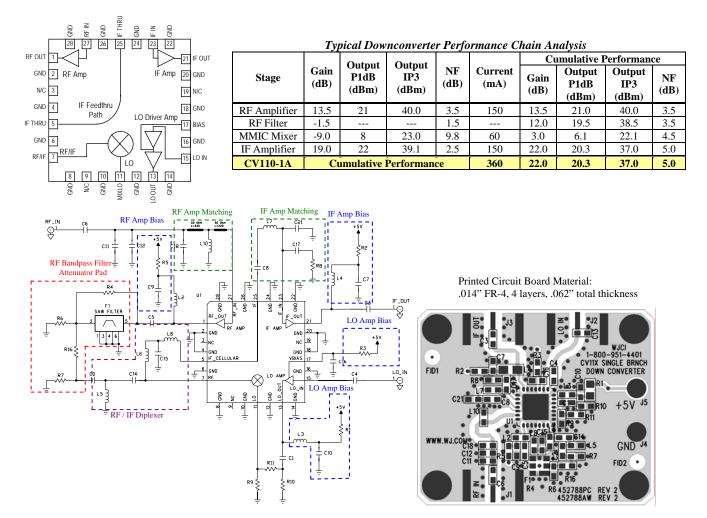

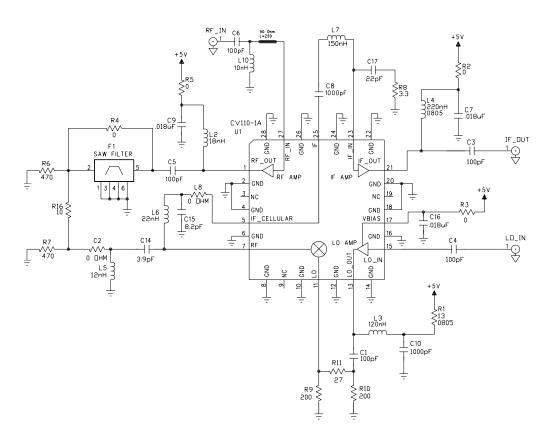

## **Device Architecture / Application Circuit Information**

**CV110-1A**: The application circuit can be broken up into four main functions as denoted in the colored dotted areas above: RF/IF diplexing (purple), amplifier matching (green), filtering (red), and dc biasing (blue). There are various placeholders for chip components in the circuit schematic so that a common PCB can be used for all WJ single-branch converters. Additional placeholders for other optional functions such as filtering are also included.

**RF** / **IF Amplifier Matching:** The RF amplifier requires a shunt matching element for optimal gain and input return loss performance. The IF amplifier requires matching elements to optimize the performance of the amplifier to the desired IF center frequency. Since IF bandwidths are typically on the order of 5 to 10%, a simple two element matching network, in the form of either a high-pass or low-pass filter structure, is sufficient to match the MMIC IF amplifier over these narrow bandwidths. Proper component values for other IF center frequencies can be provided by emailing to applications.engineering@wj.com.

**RF Bandpass Filtering:** Bandpass filtering is recommended to reject the image frequencies and achieve the best noise figure performance with the downconverter. The bandpass filter,

implemented with a SAW filter on the application circuit, allows for the suppression of noise from the image frequency. It is permissible to not use a filter and use a 2 dB pad with R6, R7, and R16 instead with slightly degraded noise figure performance. Standard WJ evaluation boards will have the 2 dB pad in place.

**External Diplexer:** In a downconversion application, the incoming RF signal impinges on the switching elements of the mixer; the interaction with these switches produces a signal at the IF frequency. The two signals (RF and IF) are directed to the appropriate ports by the external diplexer. A four-element diplexer is used in the circuit implementation (L8 and C2 are not used). Pin 5 contains the IF signal and allows the signal to be transferred to pin 25 for the convenience of PCB layouts.

**DC biasing:** DC bias must be provided for the RF, LO and IF amplifiers in the converter. R1 sets the operating current for the last stage of the LO amplifier and is chosen to optimize the mixer LO drive level. Proper RF chokes and bypass capacitors are chosen for proper amplifier biasing at the intended frequency of operation. The "+5 V" dc bias should be supplied directly from a voltage regulator.

**Product Information**

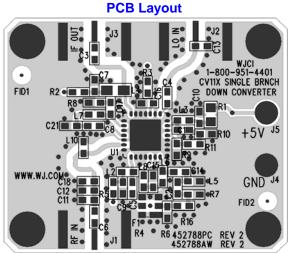

### Downconverting Application Circuit: CV110-1APCB75 RF = 800 – 915 MHz, IF = 75 MHz

Circuit Board Material: .014" FR-4, 4 layers, .062" total thickness

| <b>Bill of Materials</b> |                                      |  |  |

|--------------------------|--------------------------------------|--|--|

| Ref. Desig.              | Component                            |  |  |

| R1                       | 13 $\Omega$ chip resistor, size 0805 |  |  |

| R2, R3, R4, R5, C2, L8   | $0 \Omega$ chip resistor             |  |  |

| R6, R7                   | 470 Ω chip resistor                  |  |  |

| R8                       | 3.3 $\Omega$ chip resistor           |  |  |

| R9, R10                  | $200 \Omega$ chip resistor           |  |  |

| R11                      | 27 $\Omega$ chip resistor            |  |  |

| R16                      | $10 \Omega$ chip resistor            |  |  |

| C1, C3, C4, C5, C6       | 100 pF chip capacitor                |  |  |

| C7, C9, C16              | 0.018 µF chip capacitor              |  |  |

| C8, C10                  | 1000 pF chip capacitor               |  |  |

| C11, C12, C13,           | Shown in silkscreen, but not         |  |  |

| C18, C21, F1             | used in actual circuit.              |  |  |

| C14                      | 3.9 pF chip capacitor                |  |  |

| C15                      | 8.2 pF chip capacitor                |  |  |

| C17                      | 22 pF chip capacitor                 |  |  |

| L2                       | 18 nH chip inductor                  |  |  |

| L3                       | 120 nH chip inductor                 |  |  |

| L4                       | 220 nH chip inductor, size 0805      |  |  |

| L5                       | 12 nH chip inductor                  |  |  |

| L6                       | 22 nH chip inductor                  |  |  |

| L7                       | 150 nH chip inductor                 |  |  |

| L10                      | 10 nH chip inductor                  |  |  |

| U1                       | CV110-1A WJ Converter                |  |  |

|                          |                                      |  |  |

All components are of size 0603 unless otherwise specified.

The Communications Edge TM

**Product Information**

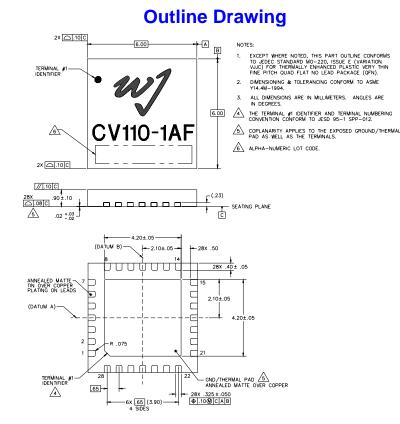

### **CV110-1AF Mechanical Information**

This package is lead-free/RoHS-compliant. It is compatible with both lead-free (maximum 260°C reflow temperature) and leaded (maximum 245°C reflow temperature) soldering processes. The plating material on the pins is annealed matte tin over copper.

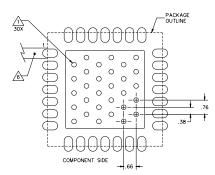

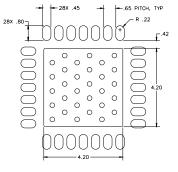

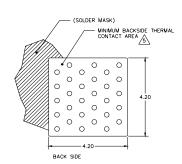

# **Mounting Configuration / Land Pattern**

#### NOTES:

- GROUND/THERMAL VIAS ARE CRITICAL FOR THE PROPER PERFORMANCE OF THIS DEVICE. VIAS SHOULD USE A .35mm (#80/.0135") DIAMETER DRILL AND HAVE A FINAL, PLATED THRU DIAMETER OF .25mm (.010").

- ADD AS MUCH COPPER AS POSSIBLE TO INNER AND OUTER LAYERS NEAR THE PART TO ENSURE OPTIMAL THERMAL PERFORMANCE.

- 3. TO ENSURE RELIABLE OPERATION, DEVICE GROUND PADDLE-TO-GROUND PAD SOLDER JOINT IS CRITICAL.

- 4. ADD MOUNTING SCREWS NEAR THE PART TO FASTEN THE BOARD TO A HEATSINK. ENSURE THAT THE GROUND/THERMAL VIA REGION CONTACTS THE HEATSINK

- DO NOT PUT SOLDER MASK ON THE BACK SIDE OF THE PC BOARD IN THE REGION WHERE THE BOARD CONTACTS THE HEATSINK.

- AND CONSTRUCTION.

- 7. USE 1 OZ. COPPER MINIMUM.

- 8. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

# **Product Marking**

The component will be lasermarked with a "CV110-1AF" product label with an alphanumeric lot code on the top surface of the package.

Tape and reel specifications for this part will be located on the website in the "Application Notes" section.

# **ESD / MSL Information**

Caution! ESD sensitive device.

| ESD Rating:<br>Value: | Class 1B<br>Passes ≥ 500V to <1000V |

|-----------------------|-------------------------------------|

| Test:                 | Human Body Model (HBM)              |

| Standard:             | JEDEC Standard JESD22-A114          |

#### ESD Rating: Class III

| Value:    | Passes $\geq$ 500V to <1000V |

|-----------|------------------------------|

| Test:     | Charged Device Model (CDM)   |

| Standard: | JEDEC Standard JESD22-C101   |

|           |                              |

MSL Rating: Level 2 at +260°C convection reflow Standard: JEDEC Standard J-STD-020

## **Functional Pin Layout**

| Pin | FUNCTION         | Pin | FUNCTION         |

|-----|------------------|-----|------------------|

| 1   | RF Amp Output    | 15  | LO Amp Input     |

| 2   | GND              | 16  | GND              |

| 3   | N/C              | 17  | LO Amp Bias      |

| 4   | GND              | 18  | GND              |

| 5   | IF Feedthru Port | 19  | N/C or GND       |

| 6   | GND              | 20  | GND              |

| 7   | Mixer RF /       | 21  | IF Amp           |

| /   | IF Port 2        | 21  | Output/Bias      |

| 8   | GND              | 22  | GND              |

| 9   | N/C or GND       | 23  | IF Amp Input     |

| 10  | GND              | 24  | GND              |

| 11  | Mixer LO Input   | 25  | IF Feedthru Port |

| 12  | GND              | 26  | GND              |

| 13  | LO Amp Output    | 27  | RF Amp Input     |

| 14  | GND              | 28  | GND              |

Specifications and information are subject to change without notice