# SEMI 4801 450NSEC, STATIC, TTL IN/OUT 4096x1 N-MOS RAM

#### **FEATURES**

- Single +5V Power Supply

- 4Kx1 Organization

- Replaces 4 1024x1 Static RAMs

- Completely Static—No Clocks or Refresh

- 18 Pin Package

- Access/Cycle Times As Low As 400 nsec max

- 250 mw Typical Operating Power

- Separate Data In and Data Out

- TTL Compatible I/O

- Three State Outputs

- Data Bus Compatible I/O Function

# GENERAL DESCRIPTION

Part Number 4801 is a 4K semiconductor random access memory

organized as 4096 1-bit words. It is fully static and needs no clock or refresh pulses. It requires a single  $\pm 5$  volt power supply and is fully TTL compatible on input and output lines. The 4801 is packaged in a convenient 18 pin dual-in-line package.

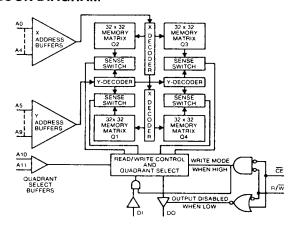

# **BLOCK DIAGRAM**

# LOGIC SYMBOL

# **TRUTH TABLE**

|    |               | _             |           |          |            |

|----|---------------|---------------|-----------|----------|------------|

| CE | R/W           | DI            | DO        | STATUS   | MODE       |

| Н  | Don't<br>Care | Don't<br>Care | High<br>Z | Deselect | Standby    |

| L  | Н             | Don't<br>Care | Data      | Selected | READ       |

| L  | L             | L.            | High<br>Z | Selected | Write<br>0 |

| L  | L             | Н             | High<br>Z | Selected | Write<br>1 |

#### PIN CONFIGURATION

|          |                  | A5 🗖 1          | 18 🗖 VCC |

|----------|------------------|-----------------|----------|

| Αи       | Address Inputs   | A4 🗖 2          | 17 🗖 A6  |

| DI       | Data Input       | DI 🗖 3          | 16 🔲 A7  |

| DO       | Data Output      | CE 🗖 4          | 15 🗖 A3  |

| CE       | Chip Enable      | ₽0 🗖 5          | 14 🗖 A2  |

| R/W      | Read/Write       | A10 🗖 6         | 13 🗖 A9  |

| $v_{ss}$ | Ground           | R/ <b>₩</b> 🗖 7 | 12 🗖 A8  |

| Vcc      | +5V Power Supply | A11 🗖 8         | 11 🗖 AO  |

|          | , ,,,,           | Vss 🗖 9         | 10 🗀 A1  |

|          |                  |                 |          |

EIIIII SEMI

30. 100 to 3. Helectrolite Memories & Magnetics Corporation 3 888 s North 28th Avenue, Phoenix, Arzon (150) 7 (6) 2) 288 5/26

# EMM SEMI 4801:450NSEC STATIC, TTL IN/OUT 4096x1:N-MOS RAM

# 章询"4801ACC"供应商 RECOMMENDED OPERATING CONDITIONS AMB = 0°C to ±70°C

| PARAMETER        | SYMBOL | MIN         | NOM | MAX  | UNIT |

|------------------|--------|-------------|-----|------|------|

| Supply Voltage   | Vcc    | 4.75        | 5.0 | 5.25 | Vdc  |

| Input High Level | Viн    | 2.4         |     | Vcc  | Vdc  |

| Input Low Level  | VIL    | <b>-0.5</b> |     | 0.8  | Vdc  |

# DC ELECTRICAL CHARACTERISTICS (Full Operating Voltage & Temperature Range Unless Otherwise Noted)

| CHARACTERISTICS        | SYMBOL | MIN | TYP | MAX | UNIT | CONDITIONS                      |

|------------------------|--------|-----|-----|-----|------|---------------------------------|

| Input Leakage Current  | ILI    | 10  |     | +10 | μA   | $V_{IN} = 0.5V \text{ or } +5V$ |

| Output Leakage Current | ILO    | -10 |     | +10 | μA   | Vout = 2.4V                     |

| Output Voltage High    | Vон    | 2.4 |     | Vcc | Vdc  | Іон = -200 да                   |

| Output Voltage Low     | VoL    |     |     | 0.4 | Vdc  | IoL = 2.0ma                     |

| Power Supply Current   | Icc    |     | 45  | 75  | ma   | Vcc = 5V; 25°C                  |

|                        | Icc    |     | 65  | 100 | ma   | $Vcc = 5V; 70^{\circ}C$         |

# **READ CYCLE—AC CHARACTERISTICS**

| PARAMETER                                   | SYMBOL  | 48  | 301 | 48  | 01A | 48  | 01B | CONDITIONS           |  |

|---------------------------------------------|---------|-----|-----|-----|-----|-----|-----|----------------------|--|

| TATAMETER                                   | STWIDGE | MIN | MAX | MIN | MAX | MIN | MAX | CONDITIONS           |  |

| Read Cycle Time                             | TRC     | 600 |     | 450 |     | 400 |     |                      |  |

| Access Time                                 | TA      |     | 600 |     | 450 |     | 400 | Full                 |  |

| Chip Enable to<br>Output Enable             | Тсо     |     | 200 |     | 150 |     | 140 | Operating<br>Voltage |  |

| Data Valid After Address                    | Тон1    | 150 |     | 100 |     | 85  |     | and<br>Temperature   |  |

| Previous Data Valid After<br>Chip De-Select | Тон2    | 25  |     | 25  |     | 25  |     | Range                |  |

# WRITE CYCLE—AC CHARACTERISTICS

| PARAMETER                                | SYMBOL  | 48  | 301 | 480 | 01A | 480 | 01B | CONDITIONS  |

|------------------------------------------|---------|-----|-----|-----|-----|-----|-----|-------------|

| FADAMETED                                | STWIDGE | MIN | MAX | MIN | MAX | MIN | MAX | CONDITIONS  |

| Write Cycle Time                         | Twc     | 600 | 1   | 450 | T   | 400 |     |             |

| Address To Write Time                    | Taw     | 100 | -   | 75  | 1   | 65  |     | Full        |

| Write Pulse Switch                       | Twp     | 500 |     | 375 |     | 330 |     | Operating   |

| Write Recovery Time                      | Twr     | 0   |     | 0   |     | 0   |     | Voltage     |

| Data Set Up Time                         | Tow     | 350 |     | 250 |     | 225 |     | and         |

| Data Hold Time                           | Тон     | 0   |     | 0   |     | 0   |     | Temperature |

| Output Disable From Write or Chip Enable | Тотw    |     | 150 |     | 125 |     | 110 | Range       |

# **CAPACITANCE**

| PARAMETER          | SYMBOL | MIN | TYP | MAX | UNIT | CONDITIONS             |

|--------------------|--------|-----|-----|-----|------|------------------------|

| Input Capacitance  | С      |     |     | 5   | pF   | V <sub>IN</sub> = 2.4V |

| Output Capacitance | С      |     |     | 10  | pF   |                        |

EIIIII SEMI

A subsidiary of Electronic Memories & Magnetics disporation 28883 North 28th Avenue, Progress, Arzona 35017 2 (602) 263-020

# EMM/SEMI 4801,450NSEC, STATIC, TTL:IN/OUT/4096x1;N-MOS/RAM

# ABSOLUTE MAXIMUM, BATINGS

(See Note 1) (Referenced to Gnd)

| RATING                                    | VALUE        | UNIT |

|-------------------------------------------|--------------|------|

| Voltage On Any Pin With<br>Respect To GND | −0.5 to +7   | VDC  |

| Power Dissipation                         | 1.6 (Note 2) | W    |

| Operating Ambient<br>Temperature Range    | 0 to +70     | °C   |

| Storage Temperature                       | -65 to +150  | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages.

NOTE 1: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended or maximum voltages for extended periods of time could affect device reliability.

NOTE 2: At 25 C Ambient, Derate 13.5 mw/ C.

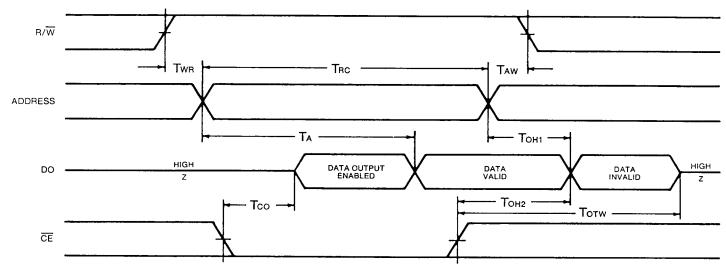

#### **READ CYCLE TIMING**

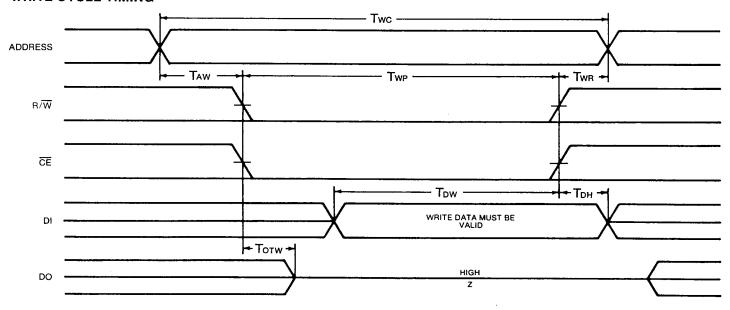

#### WRITE CYCLE TIMING

A Superdiance of the contract and described de

# 查询"4801ACC"供应商

# **FUNCTIONAL DESCRIPTION**

EMM SEMI 4801 is a 4096 bit static RAM organized as 4096 words x 1 bit. After addressing the proper word on pins  $A_0$  through  $A_{11}$ , data is read or written on separate data input/output pins (DI and DO) under the control of Read/Write (R/W) or Chip Enable ( $\overline{CE}$ ).

Data access is particularly simple since address setup time is not required. The chip is in a read mode whenever  $R/\overline{W}$  is high. If  $\overline{CE}$  is held low, the array may be read by toggling addresses. Valid output data will be available within time  $T_A$  of stable address. If  $\overline{CE}$  is used to control the read mode, data access time must always be equal to or greater than  $T_A$ , but can not occur earlier than  $T_{CO}$  from  $\overline{CE}$  going low.

The write mode occurs when both  $\overline{CE}$  and  $R/\overline{W}$  are low. Data storage, therefore, is unaffected by change in state on pins  $A_N$ , DI, DO,  $\overline{CE}$  or  $R/\overline{W}$  as long as either  $\overline{CE}$  or  $R/\overline{W}$  are high. To write, addresses must be stable for time  $T_{AW}$  before writing plus  $T_{WP}$  while writing.

# There are three possible modes of writing.

- 1.  $\overline{CE}$  is held low. Taw and Twp are then defined by R/W going from a high state to a low state and Twn is defined by R/W going from a low state to a high state.

- 2. R/W is held low. CE going low is then used to define Taw and Twp. CE going high is used to define Twa.

- 3.  $\overline{CE}$  and R/W are both used. Timing at the beginning of the cycle is then defined by the latter of  $\overline{CE}$  or R/W going low and timing at the end of the cycle is determined by the earlier of  $\overline{CE}$  or R/W going high.

The addresses must remain stable for the entire Write cycle, but data inputs are not required to remain stable. The correct logic level will be entered as long as the input data is stable for time Tow during the write cycle.

Since Data Out is high impedance during a Write cycle, Data In and Data Out may be wire-ored for applications requiring a common data bus.

### **NOTES**

- 1. Taw is measured from the latter of  $\overline{CE}$  or  $R/\overline{W}$  going low.

- 2. Two is measured from the latter of  $\overline{CE}$  or  $R/\overline{W}$  going low to the earlier of  $\overline{CE}$  or  $R/\overline{W}$  going high.

- 3. Two is measured from the earlier of  $\overline{CE}$  or  $R/\overline{W}$  going high.

- 4. Toh and Toware measured from the earlier of  $\overline{CE}$  or  $R/\overline{W}$  going high.

- 5. Totw is measured from R/W going low or  $\overline{CE}$  going high, whichever occurs first.

- 6. Timing diagrams are based on loading to simulate the capacitive effect of five additional outputs plus the current loading effect of one TTL input.

- 7. Input pulse levels 0.8 volts logic low to 2.4 volts logic high.

- 8. Input rise and fall times 10 nsec.

- 9. Timings measured from 1.5 volt level whether pulse is going high or low.

- 10. Output is high impedance during a write mode or when  $\overline{CE}$  is high. Input always represents a high impedance.

4

# 查询"4801ACC"供应商

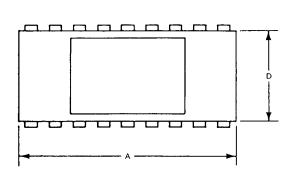

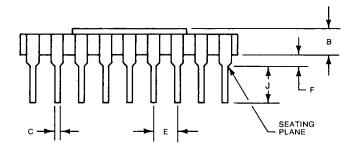

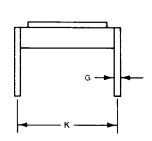

# **PACKAGING DIMENSIONS**

|     | MILLIN | METERS | INC   | HES   |

|-----|--------|--------|-------|-------|

| DIM | MIN    | MAX    | MIN   | MAX   |

| Α   | 22.6   | 23.1   | 0.890 | 0.910 |

| В   | _      | 3.18   | _     | 0.125 |

| С   | 0.38   | 0.53   | 0.015 | 0.021 |

| D   | 7.06   | 7.57   | 0.278 | 0.298 |

| E   | 2.29   | 2.79   | 0.090 | 0.110 |

| F   | 0.64   | 1.65   | 0.025 | 0.065 |

| G   | 0.20   | 0.31   | 0.008 | 0.012 |

| J   | 2.54   | 3.81   | 0.100 | 0.150 |

| K   | 7.62   | Ref    | 0.300 | Ref.  |

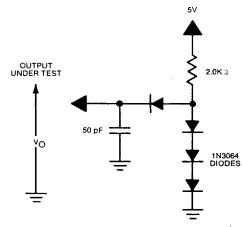

# **TEST OUTPUT LOAD**

Capacitive loading to simulate effect of five additional outputs plus one TTL input

EIIIII SEMI

ASIDELLIAN WECHANIS ALTERIA A ALTERIA SOFFICION PERMUNICATA ARTICLES AREAS ERONE AREAS ERONES ERONES

# 查询"4801ACC"供应商

#### ORDERING INFORMATION

| Speed    | Package              | Temperature Range                    |

|----------|----------------------|--------------------------------------|

| 600 nsec | Ceramic              | 0°C to +70°C                         |

| 450 nsec | Ceramic              | 0°C to +70°C                         |

| 400 nsec | Ceramic              | 0°C to +70°C                         |

|          | 600 nsec<br>450 nsec | 600 nsec Ceramic<br>450 nsec Ceramic |

EMM/SEMI reserves the right to make changes at any time in order to improve design and to supply the best product possible.

#### **WARNING:**

#### MOS CIRCUITS ARE SUBJECT TO DAMAGE FROM STATIC DISCHARGE

Internal static discharge circuits are provided to minimize part damage due to environmental static electrical charge build-ups. Industry established recommendations for handling MOS circuits include:

- Ship and store product in conductive shipping tubes or in conductive foam plastic. Never ship or store product in non-conductive plastic containers or non-conductive plastic foam material.

- 2. Handle MOS parts only at conductive work stations.

- 3. Ground all assembly and repair tools.

Represented in your area by:

A Subsidiary of Electronic Memories & Magnetics Corporation 3883 North 28th Avenue, Phoenix, Arizona 85017 Telephone (602) 263-0202 • TWX 910-951-1383

MAY O 4 1993

V R

的问题,这种"不是"。 电间记录 以此