L6376

### 0.5 A high-side driver quad intelligent power switch

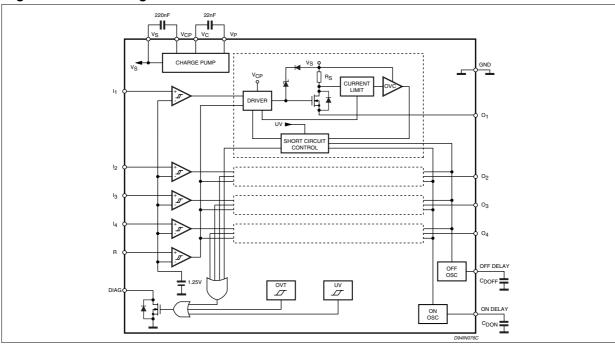

#### **Features**

- Multipower BCD technology

- 0.5 A four independent outputs

- 9.5 to 35 V supply voltage range

- Internal current limit

- Non-dissipative over-current protection

- Thermal shutdown

- Under voltage lockout with hysteresys

- Diagnostic output for under voltage, over temperature and over current

- External asynchronous reset input

- Presettable delay for overcurrent

- Diagnostic

- Open ground protection

- Immunity against burst transient (IEC 61000-4-4)

- ESD protection (human body model ± 2 kV)

#### **Description**

This device is a monolithic quad intelligent power switch in multipower BCD technology, for driving inductive, capacitive or resistive loads. Diagnostic for CPU feedback and extensive use of electrical protections make this device inherently indistructible and suitable for general purpose industrial applications.

Table 1. Device summary

| Order codes | Package    | Packaging     |

|-------------|------------|---------------|

| L6376D      | PowerSO-20 | Tube          |

| L6376D013TR | PowerSO-20 | Tape and reel |

# **Contents**

| 1  | Maximum rating                     | . 3 |

|----|------------------------------------|-----|

| 2  | Pin connections                    | . 4 |

| 3  | Thermal characteristics            | . 6 |

| 4  | Electrical characteristics         | . 7 |

| 5  | Overtemperature protection (OVT)   | 10  |

| 6  | Undervoltage protection (UV)       | 10  |

| 7  | Diagnostic logic                   | 10  |

| 8  | Short circuit operation            | 11  |

| 9  | Programmable diagnostic delay      | 12  |

| 10 | Reset input                        | 12  |

| 11 | Demagnetization of inductive loads | 13  |

| 12 | Package mechanical data            | 15  |

| 13 | Revision history                   | 17  |

# 1 Maximum rating

Table 2. Absolute maximum ratings

| Symbol                            | Pin           | Parameter                                                              | Value              | Unit |

|-----------------------------------|---------------|------------------------------------------------------------------------|--------------------|------|

| V                                 | 6             | Supply voltage ( $t_W \le 10 \text{ ms}$ )                             | 50                 | V    |

| $V_s$                             | 0             | Supply voltage (DC)                                                    | 40                 | ٧    |

| V <sub>s</sub> - V <sub>out</sub> |               | Difference between supply voltage and output voltage                   | internally limited |      |

| V <sub>id</sub>                   | 16, 17        | Externally forced voltage                                              | -0.3 to 7          | V    |

| l <sub>id</sub>                   | 10, 17        | Externally forced current                                              | ±1                 | mA   |

| l <sub>i</sub>                    | 12, 13,       | Channel input current (forced)                                         | ±2                 | mA   |

| V <sub>i</sub>                    | 14, 15,<br>18 | Channel input voltage                                                  | -0.3 to 40         | V    |

| l <sub>out</sub>                  | 2, 3, 8,      | Output current (see also I <sub>sc</sub> )                             | internally limited |      |

| V <sub>out</sub>                  | 9             | Output voltage                                                         | internally limited |      |

| E <sub>il</sub>                   |               | Energy inductive load (T <sub>J</sub> =125 °C); each channel           | 200                | mJ   |

| P <sub>tot</sub>                  |               | Power dissipation                                                      | internally limited |      |

| V <sub>diag</sub>                 | 19            | External voltage                                                       | -0.3 to Vs+0.7     | ٧    |

| I <sub>diag</sub>                 | 19            | Externally forced current                                              | -10 to 10          | mA   |

| T <sub>op</sub>                   |               | Ambient temperature, operating range                                   | -25 to 85          | °C   |

| T <sub>J</sub>                    |               | Junction temperature, operating range (see overtemperature protection) | -25 to 125         | °C   |

| T <sub>stg</sub>                  |               | Storage temperature                                                    | -55 to 150         | °C   |

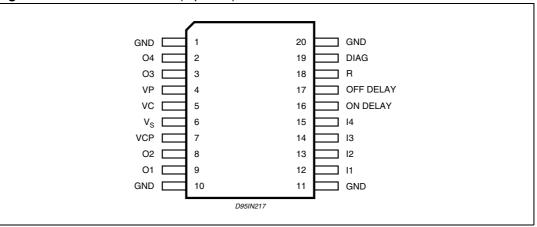

# 2 Pin connections

Figure 2. Pin connections (top view)

Table 3. Pin description

| N#               | Pin name                                                                                                                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6                | V <sub>S</sub>                                                                                                                 | Positive supply voltage. An internal circuit, monitoring the supply voltage, maintains the IC in OFF-state until $V_S$ reaches 9 V or when $V_S$ falls under 8.5 V. The diagnostic is availlable since $V_S = 5$ V.                                                                                                                                                                                                                                              |

| 7                | V <sub>CP</sub>                                                                                                                | Switch driver supply. To minimize the output drop voltage, a supply of about 10 V higher than $V_{\rm S}$ is required. In order to use the built-in charge pump, connect a filter capacitor from pin1 to pin. The suggested value assures a fast transition and a low supply ripple even in worse condition. Using the four channels contemporarily, values less than 68 nF have to be avoided.                                                                  |

| 2, 3, 8, 9       | O <sub>1</sub> , O <sub>2</sub> ,<br>O <sub>3</sub> , O <sub>4</sub>                                                           | High side outputs. Four independently controlled outputs with built-in current limitation.                                                                                                                                                                                                                                                                                                                                                                       |

| 1, 10,<br>11, 20 | GND Ground and power dissipating pins. These pins are connected to the b ground of the IC, so are useful for heat dissipation. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12,13,<br>14, 15 | I <sub>1</sub> , I <sub>2</sub> , I <sub>3</sub> , I <sub>4</sub>                                                              | Control inputs. Four independent control signals. The output is held OFF until the voltage at the corresponding input pin reaches 1.35 V and is turned OFF when the voltage at the pin goes below 1.15 V.                                                                                                                                                                                                                                                        |

| 16               | ON DELAY                                                                                                                       | Programmable ON duration in short circuit. If an output is short circuited to ground or carryng a current exceeding the limit, the output is turned OFF and the diagnostic activation are delayed. This procedure allows the driving of hard surge current loads. The delay is programmed connecting a capacitor (50 pF to 15 nF) versus ground with the internal time constant of 1.28 μs/pF. The function can be disabled short circuiting this pin to ground. |

| 17               | OFF<br>DELAY                                                                                                                   | Programmable OFF duration in short circuit. After the short circuit or overcurrent detection, the switch is held OFF before the next attempt to switch on again. The delay is programmed connecting a capacitor (50 pF to 15 nF) versus ground with the internal time constant of 1.28 µs/pF. Short circuiting this pin to ground the OFF delay is 64 times the ON delay.                                                                                        |

| 18               | R                                                                                                                              | Asyncronous reset input. This active low input (with hysteresis), switch off all the outputs independently from the input signal. By default it is biased low.                                                                                                                                                                                                                                                                                                   |

Table 3. Pin description (continued)

| N# | Pin name       | Function                                                                                                                                                                                                                                                                                                                                                                                                   |

|----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                | Diagnostic output. This open drain output reports the IC working condition. The bad condition (as undervoltage, overcurrent, overtemperature) turns the output low.                                                                                                                                                                                                                                        |

| 5  | V <sub>C</sub> | Pump oscillator voltage. At this pin is available the built-in circuitry to supply the switch driver at about 10 V higher than $V_{\rm S}$ . To use this feature, connect a capacitor across pin 4 and pin 5. The suggested value assures a fast transition and a minimum output drop voltage even in worse condition. Using the four channels contemporarily, values less than 6.8 nF have to be avoided. |

| 4  | V <sub>P</sub> | Bootstrapped voltage. At this pin is available the 11 V oscillation for the charge pump, at a typical frequency of 200 kHz.                                                                                                                                                                                                                                                                                |

# 3 Thermal characteristics

Table 4. Thermal data

| Symbol            | Parameter                                                             | Value | Unit |

|-------------------|-----------------------------------------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal resistance, junction to ambient (see thermal characteristics) | 50    | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction-case                                      | 1.5   | °C/W |

Note: Additional data on the PowerSO-20 can be found in Application note AN668

# 4 Electrical characteristics

Table 5. Electrical characteristcs ( $V_s = 24 \text{ V}$ ;  $T_J = -25 \text{ to } 125 \text{ °C}$ ; unless otherwise specified.)

| Symbol            | Pin#             | Parameter Test condition                                            |                                                                    | Min  | Тур | Max | Unit |

|-------------------|------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|------|-----|-----|------|

| DC opera          | tion             |                                                                     |                                                                    |      |     |     |      |

| V <sub>s</sub>    |                  | Supply voltage                                                      |                                                                    | 9.5  | 24  | 35  | V    |

| V <sub>sth</sub>  | 6                | UV upperthreshold                                                   |                                                                    | 8.5  | 9   | 9.5 | V    |

| V <sub>shys</sub> | 0                | UV hysteresis                                                       |                                                                    | 200  | 500 | 800 | mV   |

| I <sub>qsc</sub>  |                  | Quiescent current                                                   | Outputs ON, no load                                                |      | 3   | 5   | mA   |

| V <sub>il</sub>   |                  | Input low level                                                     |                                                                    | 0    |     | 0.8 | V    |

| V <sub>ih</sub>   |                  | Input high level                                                    |                                                                    | 2    |     | 40  | V    |

|                   | 12,13,<br>14,15, | land this a summent                                                 | $V_i = 0 V$                                                        | -5   | -1  | 0   | μА   |

| I <sub>bias</sub> | 18               | Input bias current                                                  | V <sub>i</sub> = 40 V                                              | 0    | 5   | 20  | μΑ   |

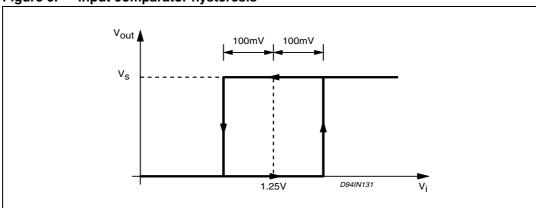

| V <sub>ihys</sub> |                  | Input comparators hysteresis                                        |                                                                    | 100  | 200 | 400 | mV   |

| Θlim              |                  | OVT upper threshold                                                 |                                                                    |      | 150 |     | °C   |

| Θн                |                  | Threshold hysteresis                                                |                                                                    |      | 20  | 30  | °C   |

|                   |                  | Short circuit current                                               | $V_s = 9.5 \text{ to } 35 \text{ V};$<br>$R_l = 2 \Omega$          | 0.65 | 0.9 | 1.2 | Α    |

| I <sub>sc</sub>   | 2, 3, 8, 9       | Outrout valta se duese                                              | I <sub>out</sub> = 500 mA;<br>T <sub>J</sub> = 25 °C               |      | 320 | 500 | mV   |

|                   |                  | Output voltage drop                                                 | I <sub>out</sub> = 500 mA;<br>T <sub>J</sub> = 125 °C              |      | 460 | 640 | mV   |

| I <sub>olk</sub>  |                  | Output leakage current                                              | $V_0 = 0 \text{ V}; V_i < 0.8 \text{ V}$                           |      |     | 100 | μА   |

| V <sub>cl</sub>   |                  | Internal voltage clamp (V <sub>s</sub> -V <sub>o</sub> each output) | $I_o = 100 \text{ mA}$<br>single pulsed<br>$T_p = 300 \mu\text{s}$ | 47   | 52  | 57  | V    |

| V <sub>ol</sub>   |                  | Low state output voltage                                            | $V_i = V_{il}; R_L = \infty$                                       |      | 0.8 | 1.5 | V    |

| I <sub>dlkg</sub> |                  | Diagnostic output leakage                                           | Diagnostic off                                                     |      |     | 25  | μА   |

| V <sub>diag</sub> | 19               | Diagnostic output voltage drop                                      | I <sub>diag</sub> = 5 mA                                           |      |     | 1.5 | V    |

| I <sub>dch</sub>  | 16, 17           | Delay capacitors charge current                                     |                                                                    |      | 40  |     | μА   |

Table 5. Electrical characteristcs (continued)  $(V_s = 24 \text{ V}; T_J = -25 \text{ to } 125 \text{ °C}; \text{ unless otherwise specified.})$

| Symbol                         | Pin#                                     | Parameter Test condition               |                                                                         | Min      | Тур      | Max     | Unit            |

|--------------------------------|------------------------------------------|----------------------------------------|-------------------------------------------------------------------------|----------|----------|---------|-----------------|

| AC opera                       | tion                                     |                                        | •                                                                       | <u>l</u> |          | L       |                 |

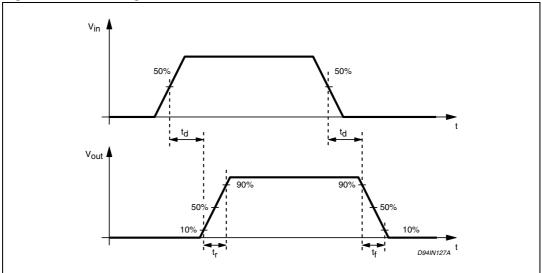

| t <sub>r</sub> -t <sub>f</sub> | 2, 3, 8,                                 | Rise or fall time                      |                                                                         |          | 3.8      |         | μS              |

| t <sub>d</sub>                 | 12 vs 9<br>13 vs 8<br>14 vs 3<br>15 vs 2 | Delay time                             | $V_s = 24 \text{ V}; R_l = 47 \Omega$ $R_l \text{ to ground}$           |          | 1        |         | μS              |

| dV/dt                          | 2, 3, 8, 9                               | Slew rate<br>(Rise and fall edge)      | $V_s = 24 \text{ V}; R_l = 47 \Omega$ $R_l \text{ to ground}$ Rise Fall |          | 5<br>7.6 | 7<br>10 | V/μs<br>V/μs    |

| t <sub>on</sub>                | 16                                       | On time during short circuit condition | 50 pF < C <sub>DON</sub> < 15 nF                                        |          | 1.28     |         | μs/pF           |

|                                | 17                                       | Off time during short                  | pin 13 grounded                                                         |          | 64       |         | t <sub>ON</sub> |

| t <sub>OFF</sub>               | 17                                       | circuit condition                      | 50 pF < C <sub>DOFF</sub> < 15 nF                                       |          | 1.28     |         | μs/pF           |

| f <sub>max</sub>               |                                          | Maximum operating frequency            |                                                                         |          | 25       |         | kHz             |

| Source d                       | rain ndm                                 | os diode                               |                                                                         |          |          |         |                 |

| V <sub>fsd</sub>               |                                          | Forward on voltage                     | I <sub>fsd</sub> = 500 mA                                               |          | 1        | 1.5     | V               |

| I <sub>fp</sub>                |                                          | Forward peak current                   | tp = 10 ms;<br>duty cycle = 20 %                                        |          |          | 1.5     | Α               |

| t <sub>rr</sub>                |                                          | Reverse recovery time                  | I <sub>fsd</sub> = 500 mA;<br>dI <sub>fsd</sub> /dt = 25 A/ms           |          | 200      |         | ns              |

| t <sub>fr</sub>                |                                          | Forward recovery time                  |                                                                         |          | 50       |         | ns              |

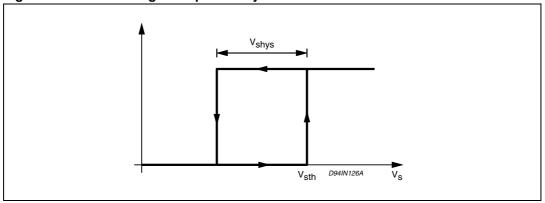

Figure 3. Undervoltage comparator hysteresis

Figure 4. Switching waveforms

#### 5 Overtemperature protection (OVT)

If the chip temperature exceeds  $\Theta$ lim (measured in a central position in the chip) the chip deactivates itself.

The following actions are taken:

- all the output stages are switched off;

- the signal DIAG is activated (active low).

Normal operation is resumed as soon as (typically after some seconds) the chip temperature monitored goes back below  $\Theta_{\text{lim}}$ - $\Theta_{\text{H}}$ .

The different thresholds with hysteretic behavior assure that no intermittent conditions can be generated.

### 6 Undervoltage protection (UV)

The supply voltage is expected to range from 9.5 V to 35 V, even if its reference value is considered to be 24 V. In this range the device operates correctly. Below 9.5 V the overall system has to be considered not reliable. Consequently the supply voltage is monitored continuously and a signal, called UV, is internally generated and used.

The signal is "on" as long as the supply voltage does not reach the upper internal threshold of the Vs comparator  $V_{sth}$ . The UV signal disappears above  $V_{sth}$ .

Once the UV signal has been removed, the supply voltage must decrease below the lower threshold (i.e.  $V_{sth}$ - $V_{shvs}$ ) before it is turned on again.

The hysteresis  $V_{shys}$  is provided to prevent intermittent operation of the device at low supply voltages that may have a superimposed ripple around the average value.

The UV signal switches off the outputs, but has no effect on the creation of the reference voltages for the internal comparators, nor on the continuous operation of the charge-pump circuits.

#### 7 Diagnostic logic

The situations that are monitored and signalled with the DIAG output pin are:

- current limit (OVC) in action; there are 4 individual current limiting circuits, one per each output; they limit the current that can be sunk from each output, to a typical value of 800 mA, equal for all of them;

- under voltage (UV);

- over temperature protection (OVT).

The diagnostic signal is transmitted via an open drain output (for ease of wired-or connection of several such signals) and a low level represents the presence of at least one of the monitored conditions, mentioned above.

#### 8 Short circuit operation

In order to allow normal operation of the other inputs when one channel is in short cirtuit, an innovative non dissipative over current protection (patent pending) is implemented in the device.

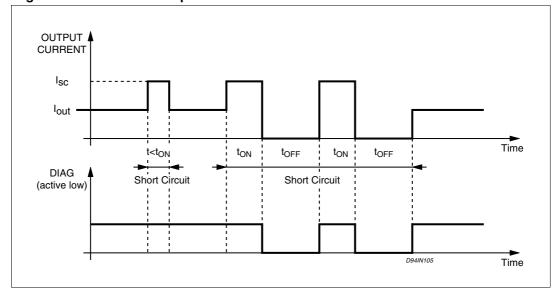

Figure 5. Short circuit operation waveforms

In this way, the temperature of the device is kept enough low to prevent the intervention of the thermal protection (in most of the cases) and so to avoid the shut down of the whole device.

If a short circuit condition is present on one output, the current limiting circuit puts that channel in linear mode — sourcing the ISC current (typically 800 mA) — for a time period  $(t_{ON})$  defined by an external capacitor  $(C_{DON})$  connected to the ON DELAY pin).

After that period, if the short circuit condition is still present the output is turned off for another time period ( $t_{OFF}$ ) defined by a second external capacitor ( $C_{DOFF}$  connected to the OFF DELAY pin).

When also this period is expired:

- if the short circuit condition is still present the output stays on for the tON period and the sequence starts again;

- if the short circuit condition is not present anymore the normal operation of the output is resumed.

The  $t_{ON}$  and  $t_{OFF}$  periods are completely independent and can be set from 64  $\mu$ s to 15  $\mu$ s, using external capacitors ranging from 50 pF to 15 nF (1.28  $\mu$ s/pF).

If the OFF DELAY pin is tied to ground (i.e. the  $C_{DOFF}$  capacitor is not used) the  $t_{OFF}$  time period is 64 times the  $t_{ON}$  period.

The diagnostic output (DIAG) is active when the output is switched off, while it is not active when the output is on (i.e. during the  $t_{\text{ON}}$  period) even if in that period a short circuit condition is present.

Typical waveforms for short circuit operation are shown in *Figure 5*.

If both the ON DELAY and the OFF DELAY pins are grounded the non dissipative over current protection is inhibited and the outputs in short circuit remain on until the thermal shutdown switch OFF the whole device. In this case the short circuit condition is not signalled by the DIAG pin (that continues to signal the under voltage and over temperature conditions).

#### 9 Programmable diagnostic delay

The current limiting circuits can be requested to perform even in absence of a real fault condition, for a short period, if the load is of capacitive nature or if it is a filament lamp (that exhibits a very low resistance during the initial heating phase).

To avoid the forwarding of misleading — i.e. short diagnostic pulses in coincidence with the intervention of the current limiting circuits when operating on capacitive loads — the activation of the diagnostic can be delayed with respect to the intervention of one of the current limiting circuits.

This delay can be defined by an external capacitor  $(C_{DON})$  connected between the ON DELAY pin and ground.

#### 10 Reset input

An external reset input R (pin 18) is provided to simultaneously switch OFF all the outputs: this signal (active low) is in effect an asynchronous reset that keeps the outputs low independently from the input signals. For example, this reset input can be used by the CPU to keep the outputs low after a fault condition (signaled by the DIAG pin).

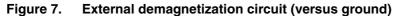

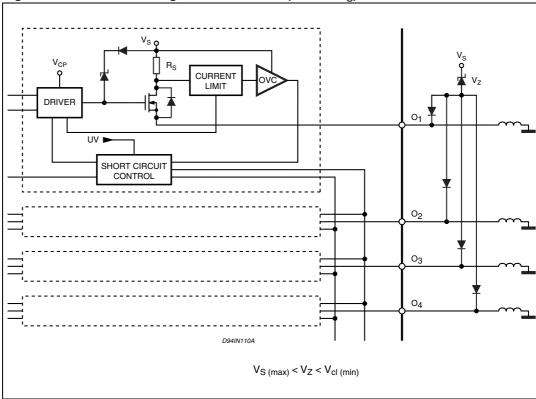

## 11 Demagnetization of inductive loads

The device has four internal clamping diodes able to demagnetize inductive loads.

The limitation is the peak power dissipation of the packages, so — if the loads are big or if there is the possibility to demagnetize more loads contemporarly — it is necessary to use external demagnetization circuits.

In Figure 7 and Figure 8 are shown two topologies for the demagnetization versus ground and versus  $V_{\rm S}$ .

The breakdown voltage of the external device  $(V_Z)$  must be chosen considering the minimum internal clamping voltage  $(V_{cl})$  and the maximum supply voltage  $(V_S)$ .

Figure 6. Input comparator hysteresis

4

Figure 8. External demagnetization circuit (versus  $V_S$ )

# 12 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com

Table 6. PowerSO-20 mechanical data

| D!     | mm   |       |      | inch  |       |       |  |

|--------|------|-------|------|-------|-------|-------|--|

| Dim.   | Min  | Тур   | Max  | Min   | Тур   | Max   |  |

| Α      |      |       | 3.6  |       |       | 0.142 |  |

| a1     | 0.1  |       | 0.3  | 0.004 |       | 0.012 |  |

| a2     |      |       | 3.3  |       |       | 0.130 |  |

| аЗ     | 0    |       | 0.1  | 0.000 |       | 0.004 |  |

| b      | 0.4  |       | 0.53 | 0.016 |       | 0.021 |  |

| С      | 0.23 |       | 0.32 | 0.009 |       | 0.013 |  |

| D (1)  | 15.8 |       | 16   | 0.622 |       | 0.630 |  |

| D1 (2) | 9.4  |       | 9.8  | 0.370 | 0.3   |       |  |

| Е      | 13.9 |       | 14.5 | 0.547 |       | 0.570 |  |

| е      |      | 1.27  |      |       | 0.050 |       |  |

| еЗ     |      | 11.43 |      |       | 0.450 |       |  |

| E1 (1) | 10.9 |       | 11.1 | 0.429 |       | 0.437 |  |

| E2     |      |       | 2.9  |       |       | 0.114 |  |

| E3     | 5.8  |       | 6.2  | 0.228 |       | 0.244 |  |

| G      | 0    |       | 0.1  | 0.000 |       | 0.004 |  |

| Н      | 15.5 |       | 15.9 | 0.610 |       | 0.626 |  |

| h      |      |       | 1.1  |       |       | 0.043 |  |

| L      | 0.8  |       | 1.1  | 0.031 |       | 0.043 |  |

| N      |      | •     | 8°(t | typ.) | •     |       |  |

| S      |      |       | 8°(m | nax.) |       |       |  |

| Т      |      | 10    |      |       | 0.394 |       |  |

a2 DETAIL B DÉTAIL A Е еЗ DETAIL A Н lead D DETAIL B 11 - C -SEATING PLANE

G C

(COPLANARITY) s BOTTOM VIEW E2 E1 ЕЗ D1 0056635 I

Figure 9. Package dimensions

# 13 Revision history

Table 7. Document revision history

| Date           | Revision | Changes                                   |

|----------------|----------|-------------------------------------------|

| September 2003 | 5        | First issue in EDOCS dms.                 |

| 03-Mar-2008    | 6        | Modified: Removed obsolete package DIP-20 |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com