# Magacka Falf P供应商

### SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

REJ03B0082-0131 Rev.1.31 Apr 18, 2005

### **DESCRIPTION**

The M306V8FJFP are single-chip microcomputers using the high-performance silicon gate CMOS process using a M16C/60 Series CPU core and are packaged in a 116-pin plastic molded QFP. These single-chip microcomputers operate using sophisticated instructions featuring a high level of instruction efficiency. With 1M bytes of address space, they are capable of executing instructions at high speed. They also feature a built-in OSD display function and data slicer, making them ideal for closed caption and ID1 for TV control.

# **Applications**

TV

# -----Table of Contents-----

| DESCRIPTION1                   |  |

|--------------------------------|--|

| Central Processing Unit (CPU)9 |  |

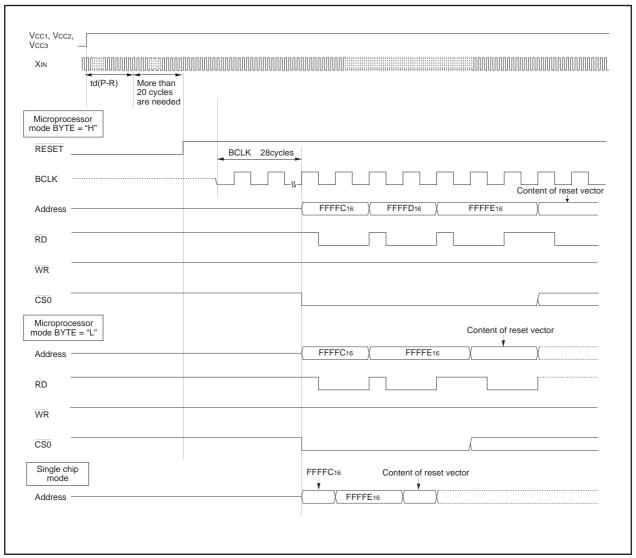

| Reset                          |  |

| Processor Mode                 |  |

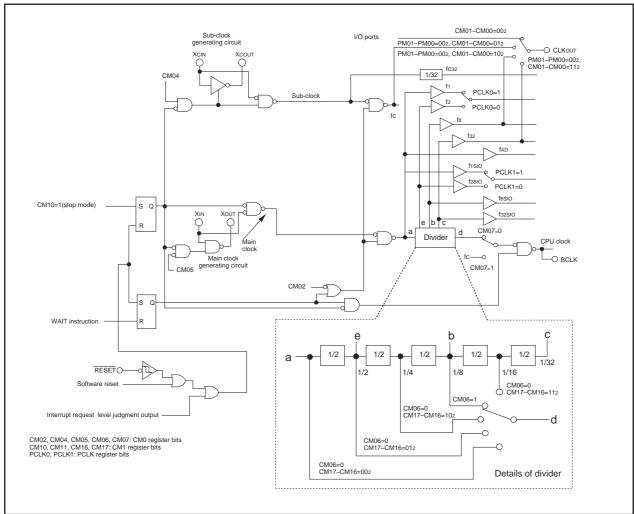

| Clock Generating Circuit50     |  |

| Protection67                   |  |

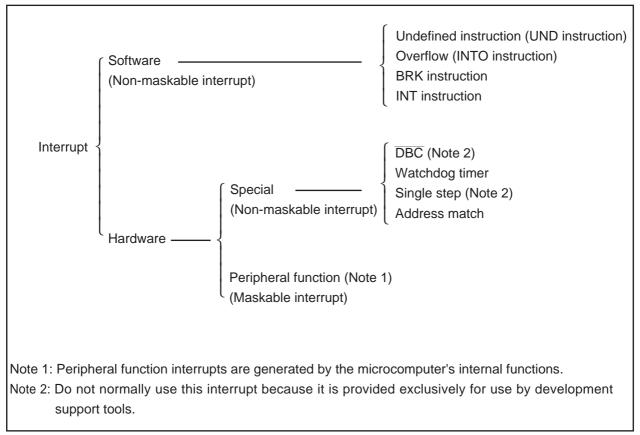

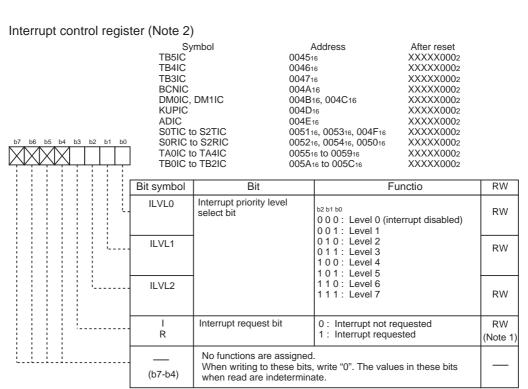

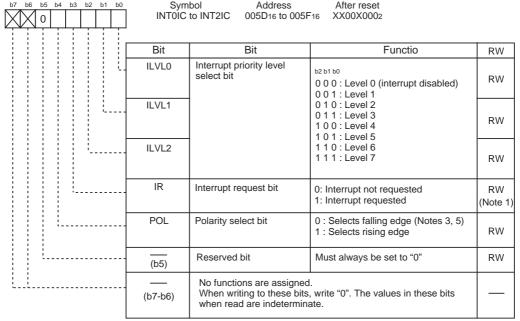

| Interrupts68                   |  |

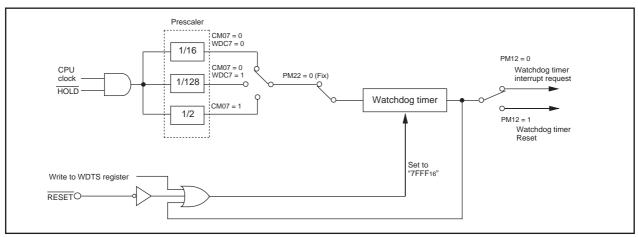

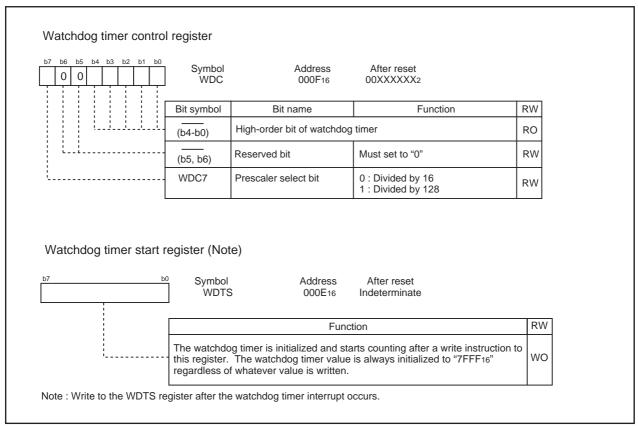

| Watchdog Timer89               |  |

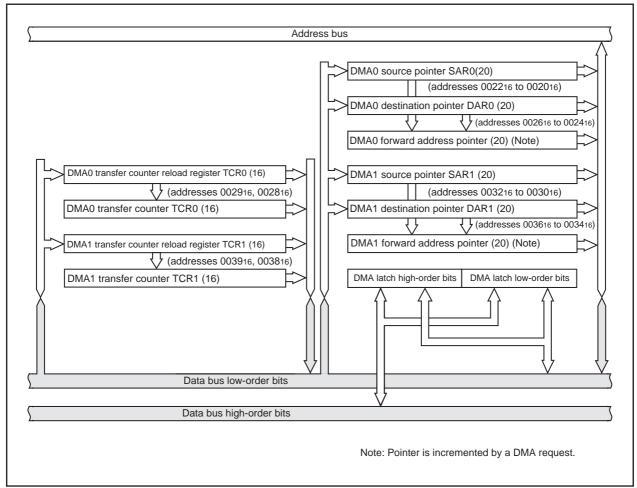

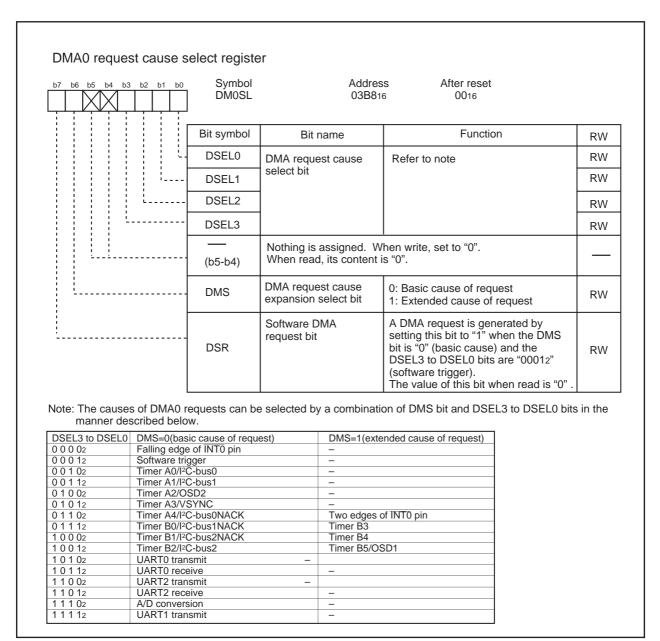

| DMAC91                         |  |

| Timer 101                      |  |

| Serial I/O123                  |  |

| A/D Converter1                               | 56  |

|----------------------------------------------|-----|

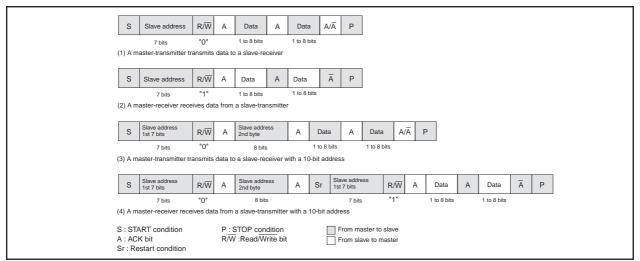

| Multi-master I <sup>2</sup> C-BUS Interface1 | 70  |

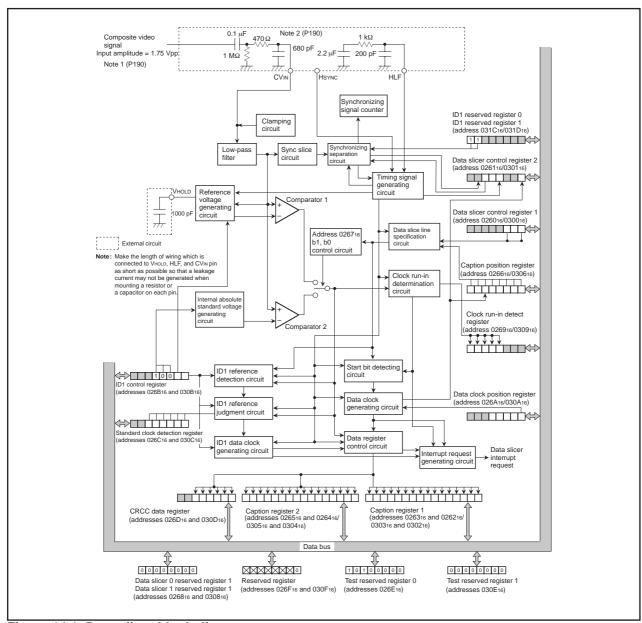

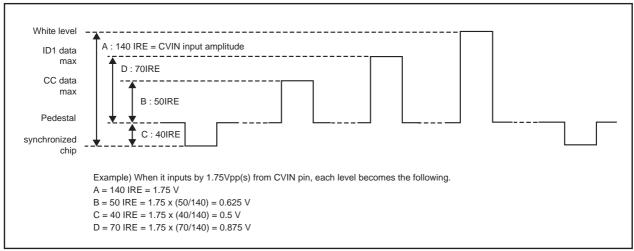

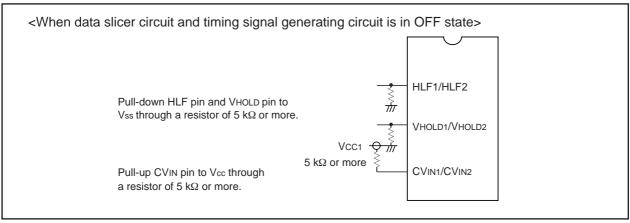

| Data Slicer1                                 | 90  |

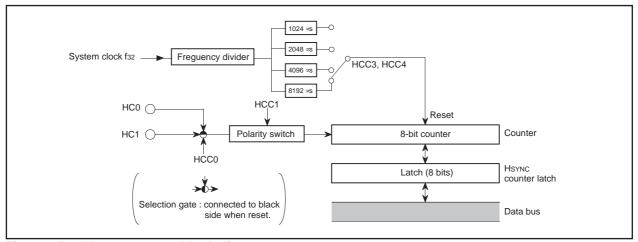

| HSYNC Counter                                | .03 |

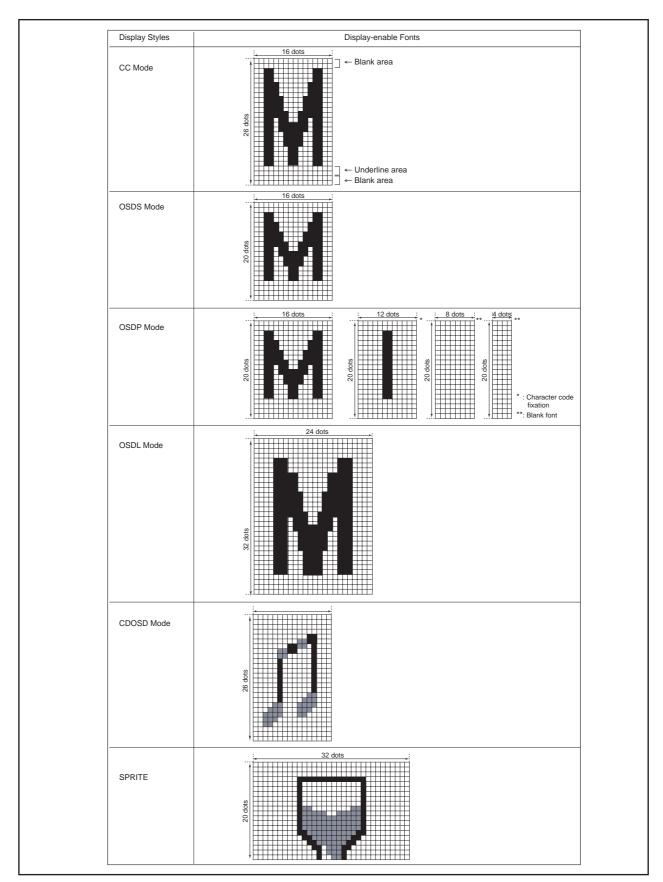

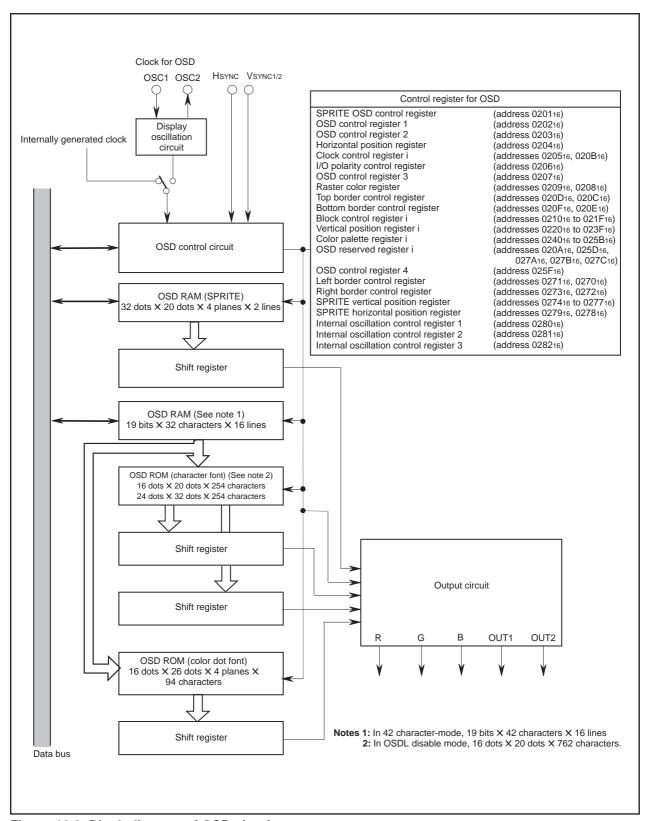

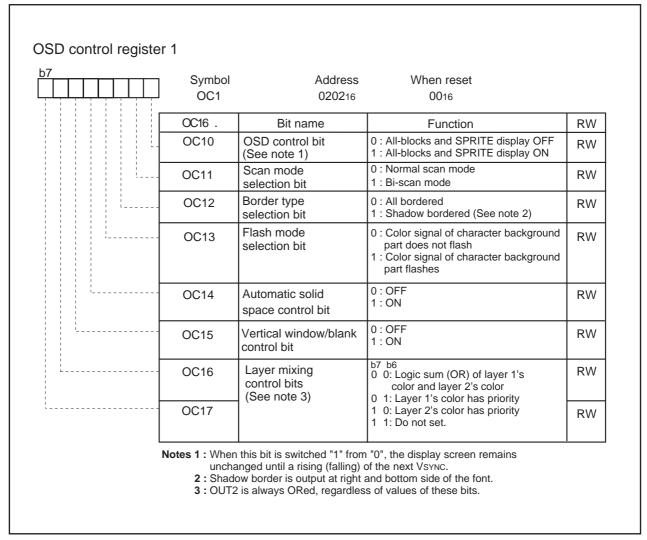

| OSD Functions                                | 04  |

| Programmable I/O Ports20                     | 60  |

| ELECTRICAL CHARACTERISTICS29                 | 95  |

| Flash Memory Version3                        | 16  |

| Usage Precaution3                            | 48  |

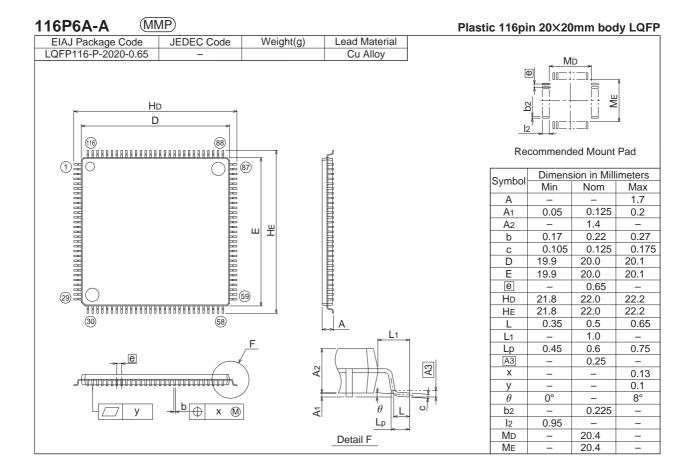

| PACKAGE OUTLINE3                             | 63  |

### **Performance Outline**

Table 1.1. Performance outline of M306V8FJFP

| Item                          |                                      | Performance                                                      |  |  |

|-------------------------------|--------------------------------------|------------------------------------------------------------------|--|--|

| Number of basic instructions  |                                      | 91 instructions                                                  |  |  |

| Shortest instr                | uction execution time                | 62.5 ns (f(BCLK)= 16MHz                                          |  |  |

| Memory                        | ROM                                  | (See the product list)                                           |  |  |

| capacity                      | RAM                                  | (See the product list)                                           |  |  |

| I/O port                      | P0 to P10                            | 75                                                               |  |  |

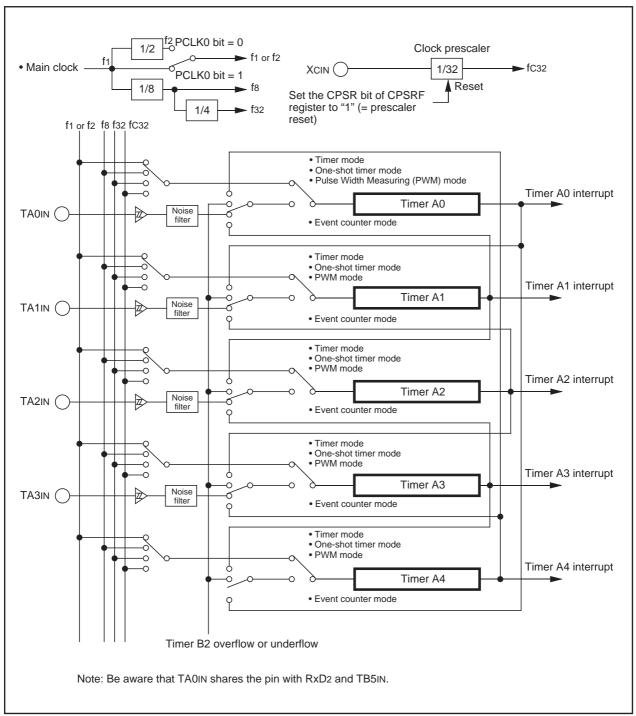

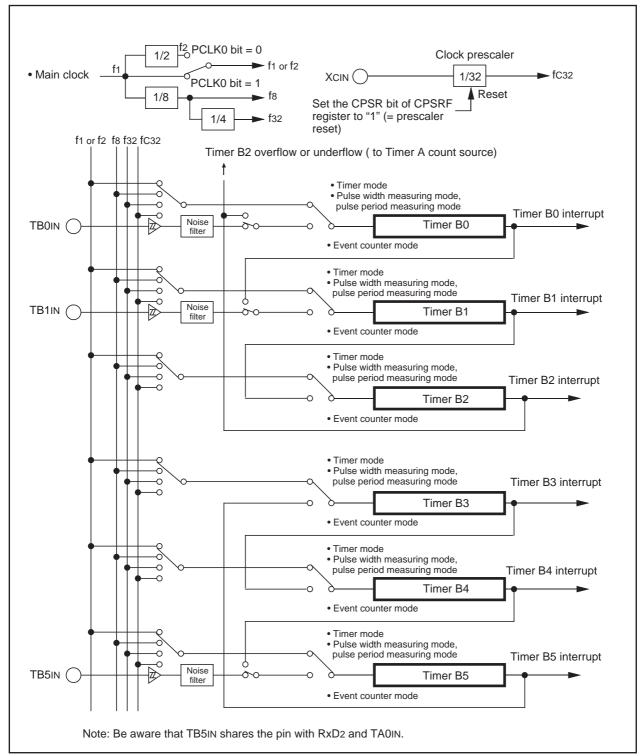

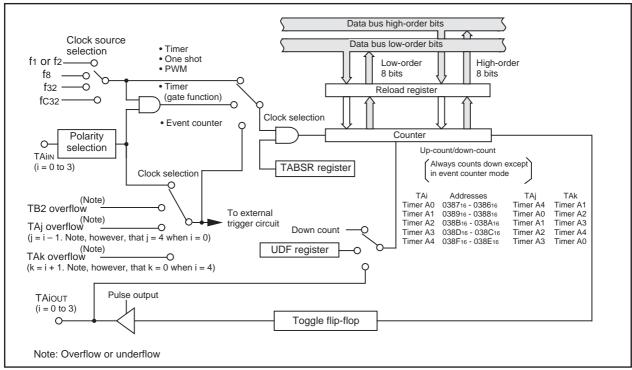

| Multifunction                 | TA0, TA1, TA2, TA3, TA4              | 16 bits output x 5 channels                                      |  |  |

| timer                         | TB0, TB1, TB2, TB3, TB4,<br>TB5      | 16 bits input x 6 channels                                       |  |  |

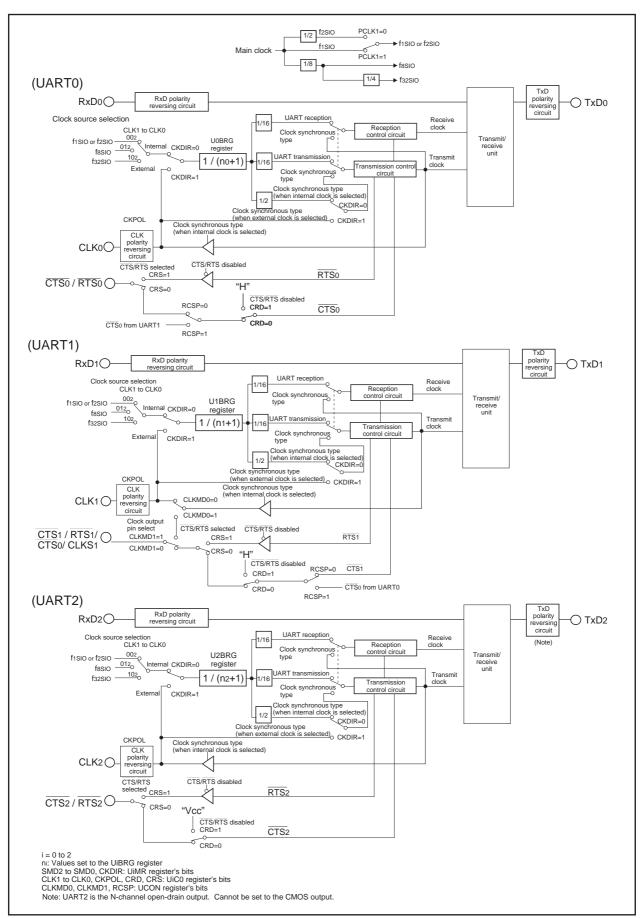

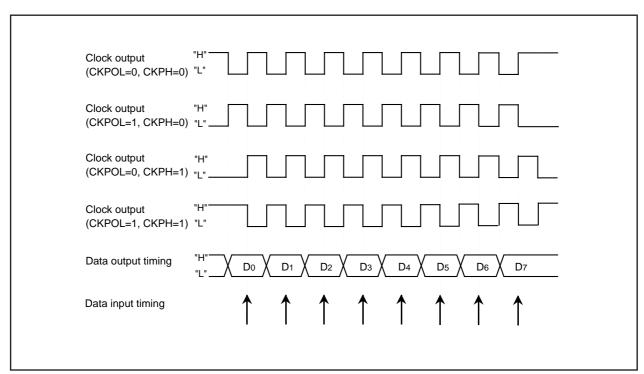

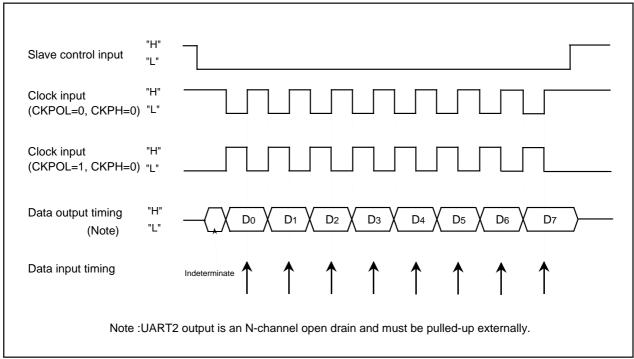

| Serial I/O                    | UART0, UART1, UART2                  | (UART, clock sync. serial I/O, IEBus (Note 2)) x 3               |  |  |

| A/D converter                 | •                                    | 8 bits x 13 channels                                             |  |  |

| Data slicer                   |                                      | 2 circuits                                                       |  |  |

| Hsync counte                  | r                                    | 1 circuit 2 lines                                                |  |  |

| OSD function                  |                                      | 1 circuit                                                        |  |  |

| Multi-master I                | <sup>2</sup> Cbus interface (Note 1) | 3 circuits 4 lines                                               |  |  |

| DMAC                          |                                      | 2 channels (trigger: 29 sources)                                 |  |  |

| Watchdog tim                  | er                                   | 15 bits x 1 (with prescaler)                                     |  |  |

| Interrupt                     |                                      | 31 internal and 5 external sources, 4 software sources, 7 levels |  |  |

| Clock general                 | tion circuit                         | 3 circuits                                                       |  |  |

|                               |                                      | Main clock                                                       |  |  |

|                               |                                      | Sub-clock (These circuits contain a built-in feedback)           |  |  |

|                               |                                      | OSD clock                                                        |  |  |

| Power supply v                | roltage                              | 3.15 to 3.45V                                                    |  |  |

| Flash memory                  | · ·                                  | 3.15 to 3.45V                                                    |  |  |

|                               | Number of program/erase              | 100 times                                                        |  |  |

| Power consur                  | mption                               | 500mW                                                            |  |  |

| I/O                           | I/O withstand voltage                | 3.3V                                                             |  |  |

| characteristics               | Output current                       | 5mA                                                              |  |  |

| Memory expansion              |                                      | Available (to 4M bytes)                                          |  |  |

| Operating ambient temperature |                                      | -20 to 70°C                                                      |  |  |

| Device configuration          |                                      | CMOS high performance silicon gate                               |  |  |

| Package                       |                                      | 116-pin plastic mold QFP                                         |  |  |

| Notes:                        | <u> </u>                             |                                                                  |  |  |

<sup>1.</sup> I<sup>2</sup>C bus is a registered trademark of Koninklijke Philips Electronics N. V.

<sup>2.</sup> IEBus is a trademark of NEC Electronics Corporation. When you use option function, please specify that.

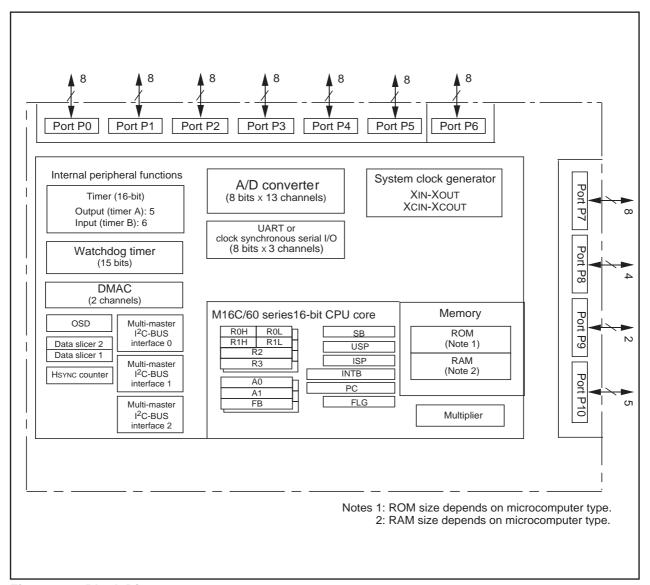

# **Block Diagram**

Figure 1.1 is a block diagram of the M306V8FJFP.

Figure 1.1. Block Diagram

### **Product List**

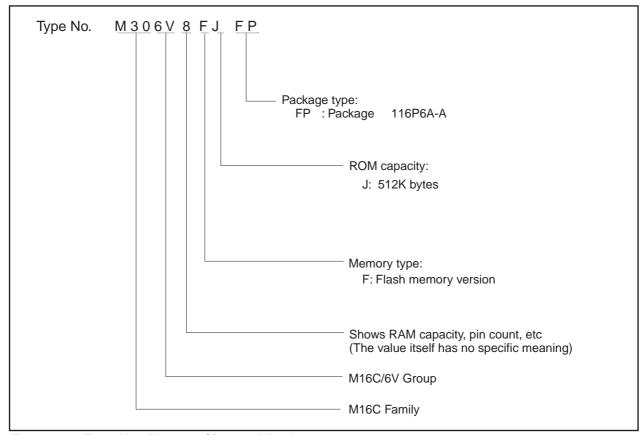

Product list is show in Table 1.2 type No., memory size and package type are show in Figure 1.2.

Table 1.2. Product List

| Type No.   | ROM capacity | RAM capacity | Package type | Remarks              |

|------------|--------------|--------------|--------------|----------------------|

| M306V8FJFP | 512K bytes   | 16K bytes    | 116P6A-A     | Flash memory version |

Figure 1.2. Type No., Memory Size, and Package

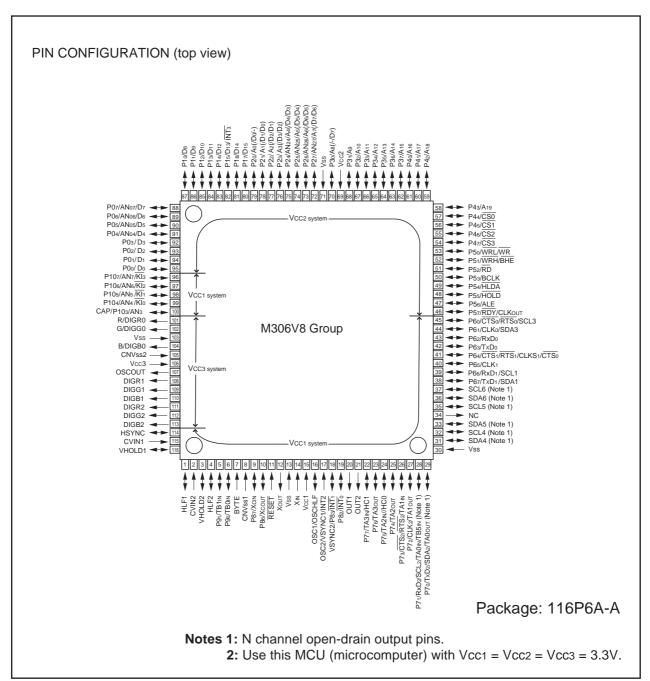

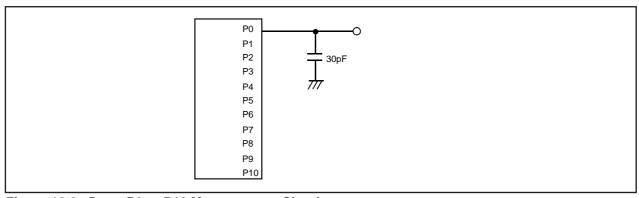

### **Pin Configuration**

Figures 1.3 show the pin configuration.

Figure 1.3. Pin Configuration (Top View)

# **Pin Description**

Table 1.3. Pin Description (1)

| Pin name                  | Signal name                                | I/O type         | Power supply | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------|--------------------------------------------|------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

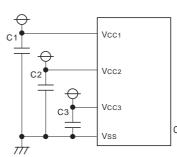

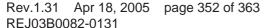

| VCC1, VCC2,<br>VCC3, VSS  | Power supply input                         |                  |              | Apply 3.3 V to the Vcc1, Vcc2 and Vcc3 pins and 0 V to the Vsspin. (Note 1) Insert a bypass capacitor between power supply and GND. (Note 2)                                                                                                                                                                                                                                                                                                                            |

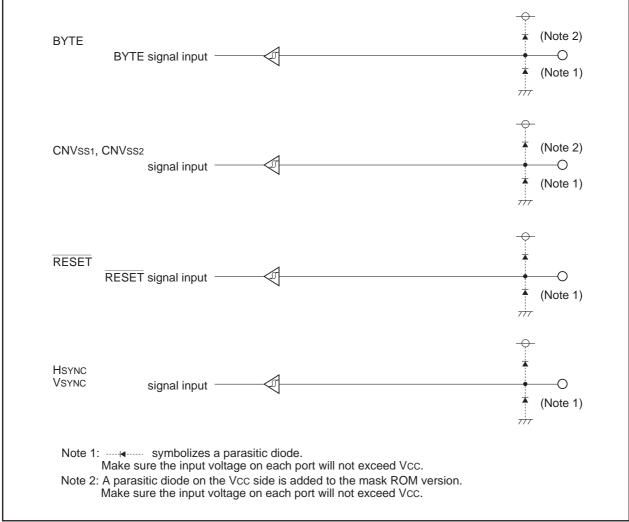

| CNVSS1,<br>CNVSS2         | CNVss1/<br>CNVss2                          | Input            | Vcc          | CNVss1 pin switches between processor modes. Connect this pin to Vss pin when after a reset you want to start operation in single-chip mode (memory expansion mode) or the Vcc1 pin when starting operation in microprocessor mode. Always connect CNVss2 pin to Vss.                                                                                                                                                                                                   |

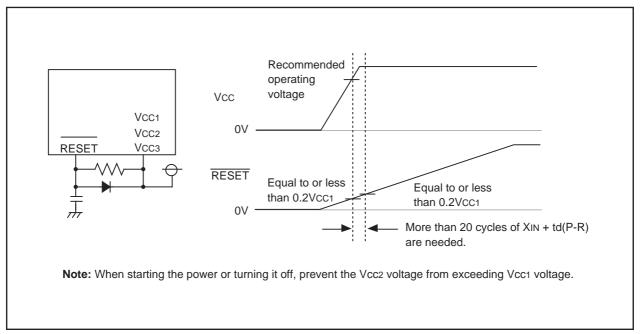

| RESET                     | Reset input                                | Input            | Vcc          | "L" on this input resets the microcomputer.                                                                                                                                                                                                                                                                                                                                                                                                                             |

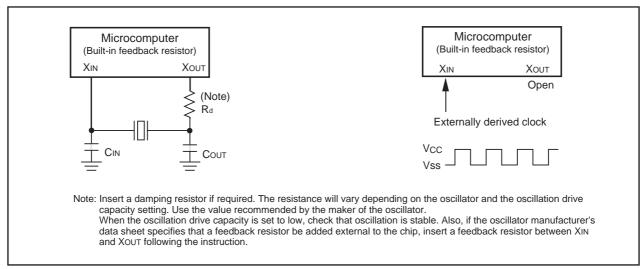

| XIN<br>XOUT               | Clock input<br>Clock output                | Input<br>Output  | Vcc          | These pins are provided for the main clock generating circuit input/output. Connect a ceramic resonator or crystal between the XIN and the XOUT pins. To use an externally derived clock, input it to the XIN pin and leave the XOUT pin open.                                                                                                                                                                                                                          |

| BYTE                      | External data<br>bus width<br>select input | Input            | Vcc          | This pin selects the width of an external data bus. A 16-bit width is selected when this input is "L"; an 8-bit width is selected when this input is "H". This input must be fixed to either "H" or "L". Connect this pin to the Vss pin when operating in single-chip mode.                                                                                                                                                                                            |

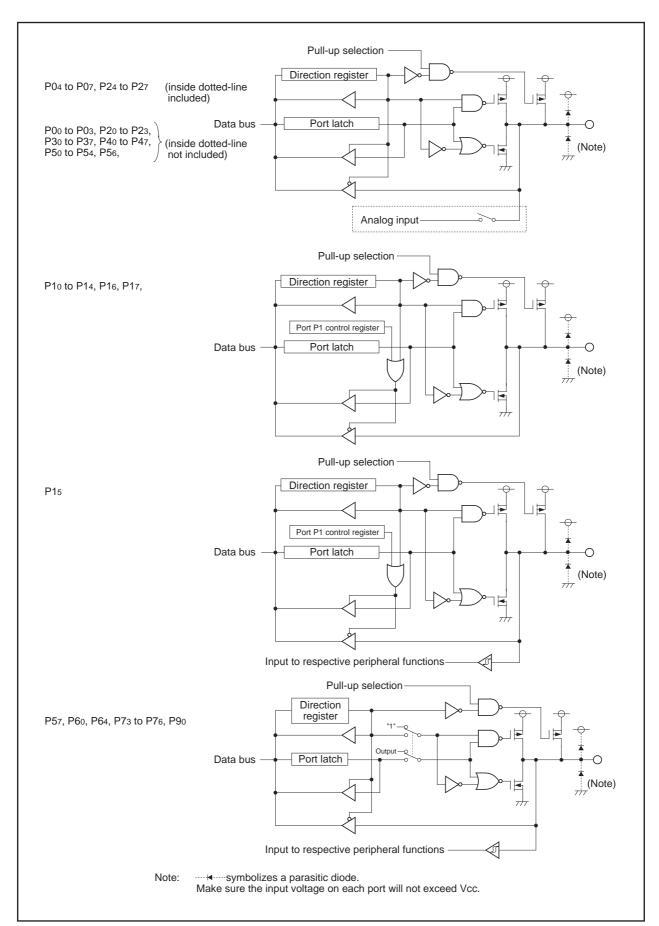

| P00 to P07                | I/O port P0                                | I/O              | Vcc          | This is an 8-bit CMOS I/O port. This port has an I/O select direction register, allowing each pin in that port to be directed for input or output individually. If any port is set for input, selection can be made for it in a program whether or not to have a pull-up resistor in 4 bit units. This selection is unavailable in memory extension and microprocessor modes. This port can function as input pins for the A/D converter when so selected in a program. |

| Do to D7                  |                                            | I/O              |              | When set as a separate bus, these pins input and output data (Do -D7).                                                                                                                                                                                                                                                                                                                                                                                                  |

| P10 to P17                | I/O port P1                                | I/O              | Vcc          | This is an 8-bit I/O port equivalent to P0. P15 also function as INT interrupt input pins as selected by a program.                                                                                                                                                                                                                                                                                                                                                     |

| D8 to D15                 |                                            | I/O              |              | When set as a separate bus, these pins input and output data (D <sub>8</sub> –D <sub>15</sub> ).                                                                                                                                                                                                                                                                                                                                                                        |

| P20 to P27                | I/O port P2                                | I/O              | Vcc          | This is an 8-bit I/O port equivalent to P0. This port can function as input pins for the A/D converter when so selected in a program.                                                                                                                                                                                                                                                                                                                                   |

| Ao to A7                  |                                            | Output           |              | These pins output 8 low-order address bits (A <sub>0</sub> to A <sub>7</sub> ).                                                                                                                                                                                                                                                                                                                                                                                         |

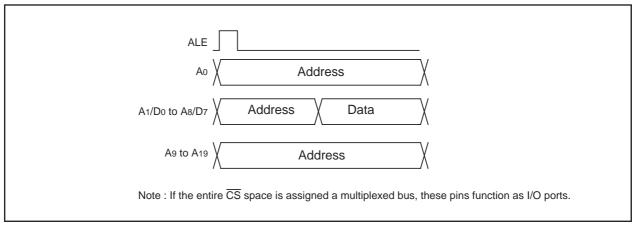

| A0/D0 to<br>A7/D7         |                                            | I/O              |              | If the external bus is set as an 8-bit wide multiplexed bus, these pins input and output data (Do to D7) and output 8 low-order address bits (Ao to A7) separated in time by multiplexing.                                                                                                                                                                                                                                                                              |

| A0<br>A1/D0 to<br>A7/D6   |                                            | Output<br>I/O    |              | If the external bus is set as a 16-bit wide multiplexed bus, these pins input and output data (Do to D6) and output address (A1 to A7) separated in time by multiplexing. They also output address (A0).                                                                                                                                                                                                                                                                |

| P30 to P37                | I/O port P3                                | I/O              | Vcc          | This is an 8-bit I/O port equivalent to P0.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A8 to A15                 | _                                          | Output           | -            | These pins output 8 middle-order address bits (A8 to A15).                                                                                                                                                                                                                                                                                                                                                                                                              |

| A8/D7,<br>A9 to A15       |                                            | I/O<br>Output    |              | If the external bus is set as a 16-bit wide multiplexed bus, these pins input and output data (D7) and output address (A8) separated in time by multiplexing. They also output address (A 9 to A15).                                                                                                                                                                                                                                                                    |

| P40 to P47                | I/O port P4                                | I/O              | Vcc          | This is an 8-bit I/O port equivalent to P0.                                                                                                                                                                                                                                                                                                                                                                                                                             |

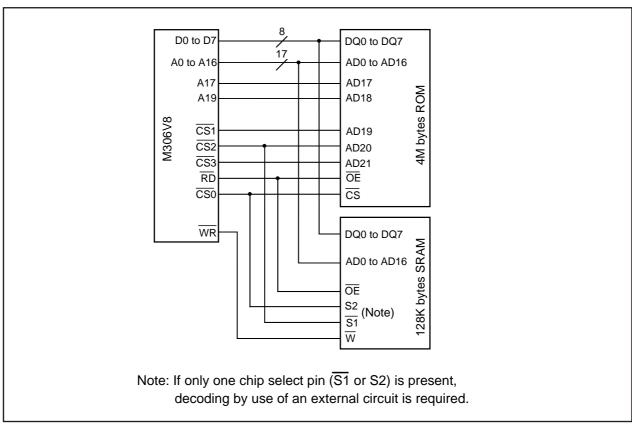

| A16 to A19,<br>CS0 to CS3 |                                            | Output<br>Output |              | These pins output A16 to A19 and CS0 to CS3 signals. A16 to A19 are 4 high- order address bits. CS0 to CS3 are chip select signals used to specify an access space.                                                                                                                                                                                                                                                                                                     |

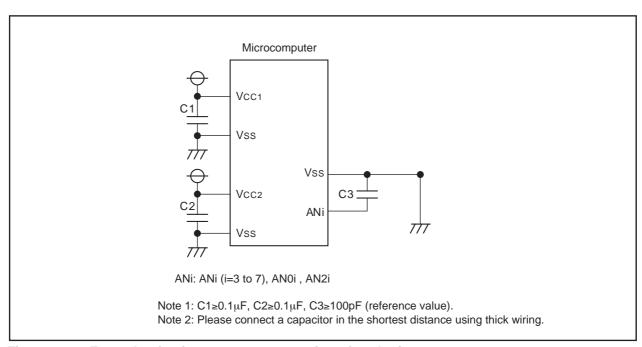

- Notes 1: In this manual, hereafter, VCC refers to VCC1 unless otherwise noted

- 2: Insert capacitors between each power supply pin and GND to prevent errors or latch-up by noise.

- Also, use thick and shortest possible wiring to connect capacitors.

RENESAS

$C1 \ge 0.1 \times F, \ C2 \ \ge 0.1 \times F, \ C3 \ \ge 0.1 \times F \ (reference \ value)$

Table 1.4. Pin Description (2)

| Pin name                                                                                                                 | Signal name                                 | I/O type                                                    | Power supply | unction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P50 to P57                                                                                                               | I/O port P5                                 | I/O                                                         | Vcc          | This is an 8-bit I/O port equivalent to P0. In single-chip mode, P57 in this port outputs a divide-by-8 or divide-by-32 clock of XIN or a clock of the same frequency as XCIN as selected by program.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

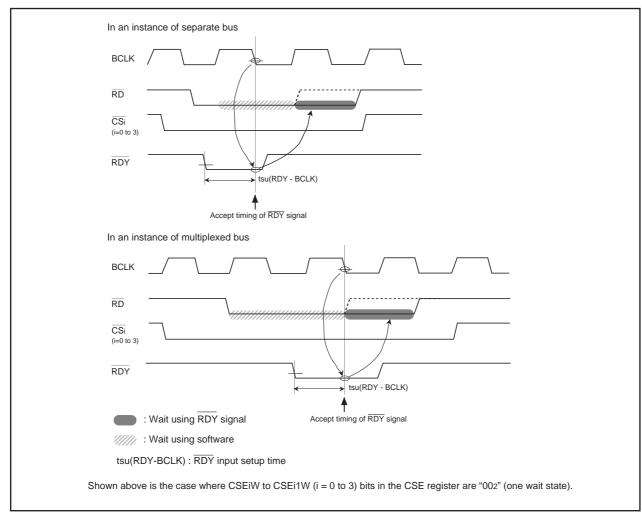

| WRL / WR,<br>WRH / BHE,<br>RD,<br>BCLK,<br>HLDA,<br>HOLD,<br>ALE,<br>RDY                                                 |                                             | Output Output Output Output Output Input Output Input Input |              | Output WRL/WRH, (BHE/WR), RD, BCLK, HLDA, and ALE signals WRL/WRH and BHE/WR are switch able in a program. Note that WRL and WRH are always used as a pair, so as WR and BHE.  WRL, WRH, and RD selected  If the external data bus is 16 bits wide, data are written to even addresses when the WRH signal is low, and written to odd addresses when the WRH signal is low. Data are read out when the RD signal is low.  WR, BHE, and RD selected  Data are written when the WR signal is low, or read out when the RD signal is low. Odd addresses are accessed when the BHE signal is low. Use this mode when the external data bus is 8 bits wide.  The microcomputer goes to a hold state when input to the HOLD pin is held low. While in the hold state, HLDA outputs a low level. ALE is used to latch the address. While the input level of the |  |

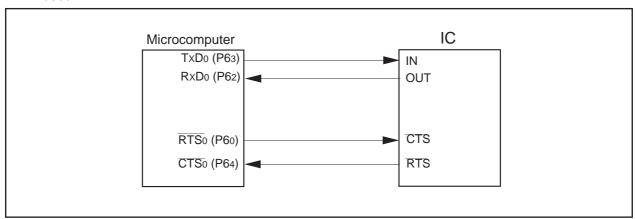

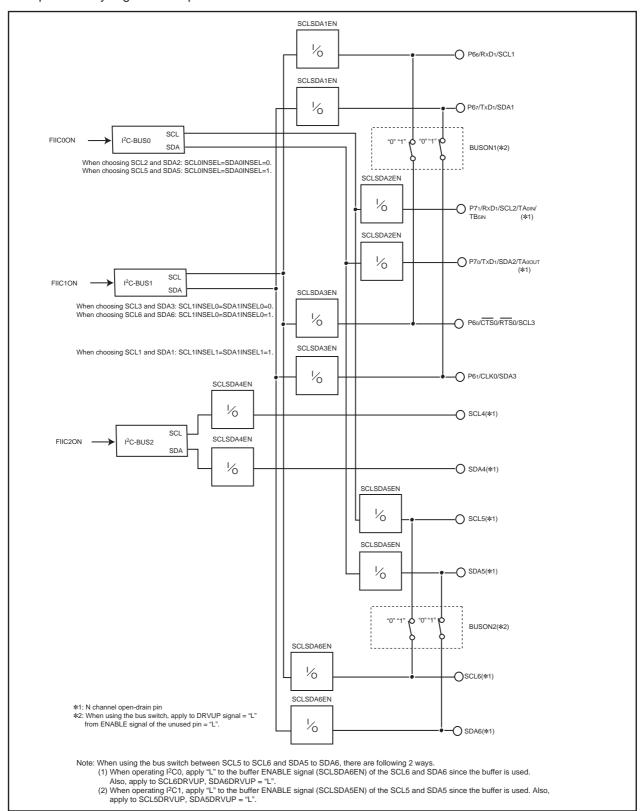

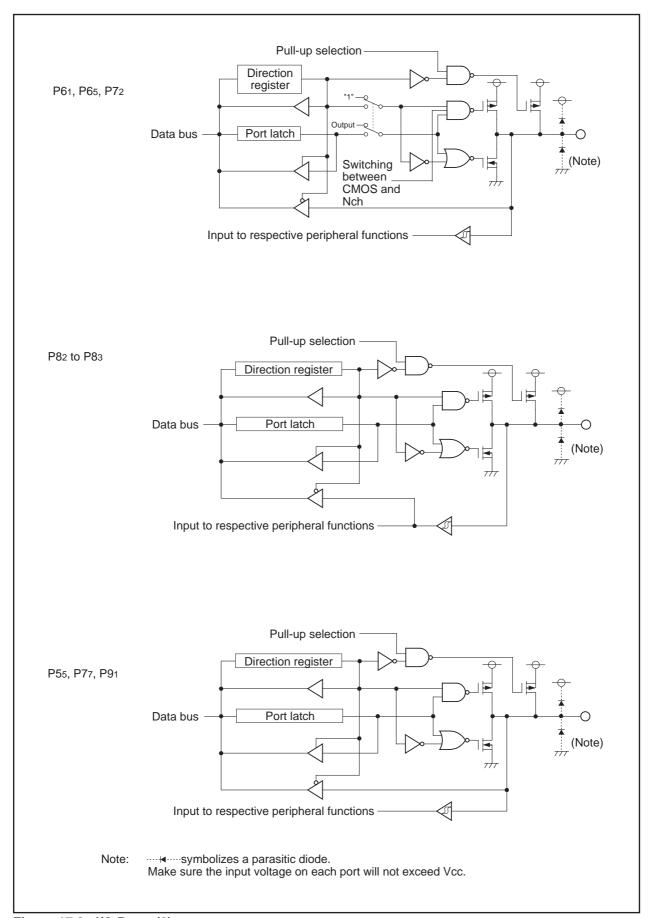

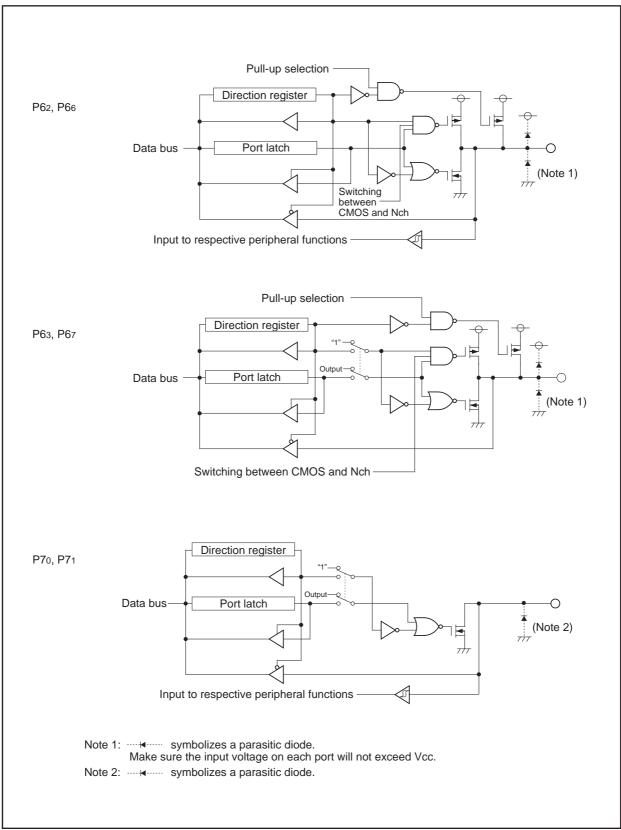

| P60 to P67                                                                                                               | I/O port P6                                 | I/O                                                         | Vcc          | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as UART0, UART1 and multi-master I <sup>2</sup> C bus I/O pins as selected by program.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

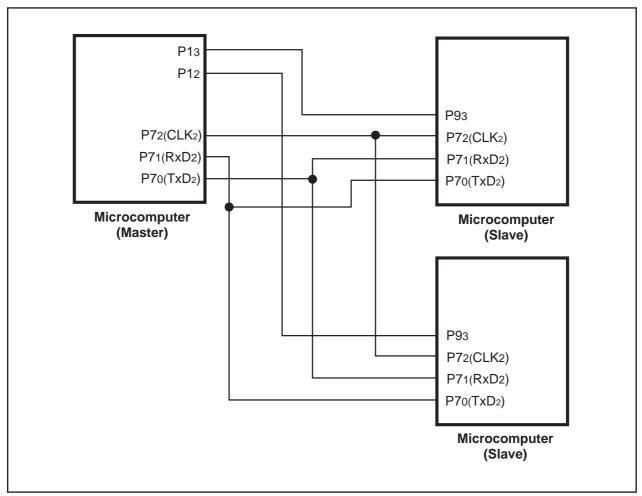

| P70 to P77                                                                                                               | I/O port P7                                 | I/O                                                         | Vcc          | This is an 8-bit I/O port equivalent to P0. (However, P70 and P71 are the pins of N-channel opendrain output) This port can function as I/O pins for timers A0 to A3 and B5 by selecting in a program. And, UART2, I <sup>2</sup> C bus I/O pin, P75 and P77 can also function as input pin for Hsync conter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

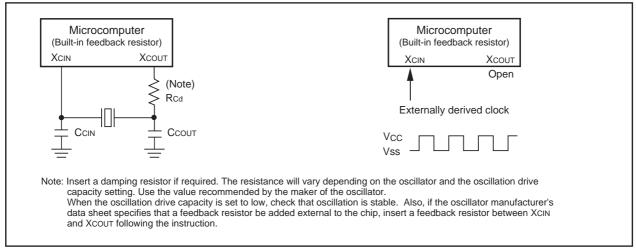

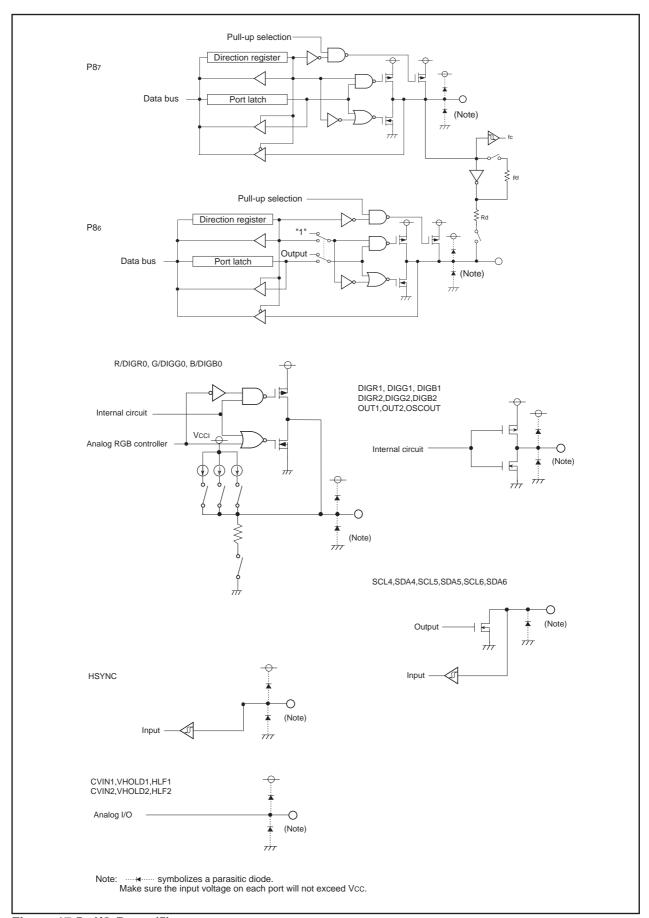

| P82, P84,<br>P86,<br>P87,                                                                                                | I/O port P8                                 | I/O                                                         | Vcc          | They are I/O ports with the same functions as P0. When so selected in a program, they can function as I/O pins for INT interrupt, Vsync input pins and the sub clock oscillator circuit. In that case, connect a crystal resonator between P86 (XCOUT pin) and P87 (XCIN pin).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| P90, P91                                                                                                                 | I/O port P9                                 | I/O                                                         | Vcc          | This is an 8-bit I/O port equivalent to P0. Pins in this port also function as timer B0 and B1 input pins as selected by program.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

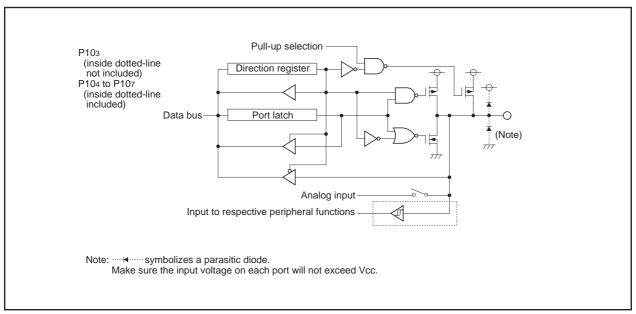

| P103 to<br>P107                                                                                                          | I/O port P10                                | I/O                                                         | Vcc          | This is an I/O port equivalent to P0. Pins in this port also function as A/D converter input pins and the capacitor connection pin for analog RGB operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| SCL4 to 6,<br>SDA4 to 6                                                                                                  | Multi-master I <sup>2</sup> C-bus interface | I/O                                                         |              | These are exclusive pins for multi-master I <sup>2</sup> C-bus interface (N-channel open drain output.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Hsync                                                                                                                    | Hsync input                                 | Input                                                       | Vcc          | OSD function Hsync input pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| R/DIGR0,<br>B/DIGB0,<br>G/DIGG0,<br>OUT1,<br>OUT2,<br>DIGR1,<br>DIGB1,<br>DIGG2,<br>DIGR2,<br>DIGG2,<br>DIGB2,<br>OSCOUT | OSD<br>function<br>output pin               | Output                                                      | Vcc          | These are exclusive pins for OSD functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| CVin1,<br>VHOLD1,<br>HLF1,<br>CVin2,<br>VHOLD2,<br>HLF2                                                                  | Data slicer<br>function I/O<br>pin          | I/O                                                         | Vcc          | These are exclusive pins for data slicer function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

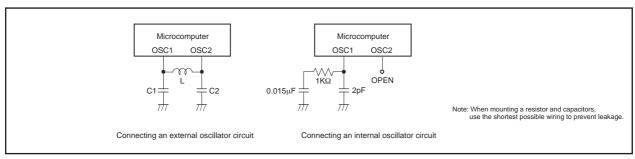

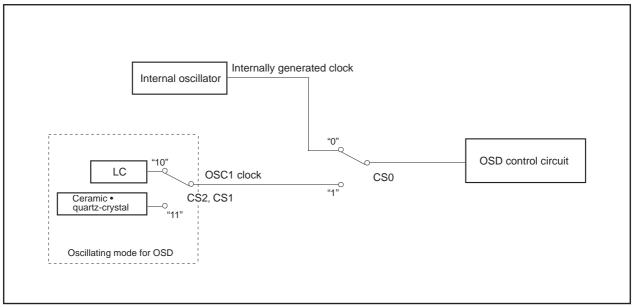

| OSC1/<br>OSDHLF,<br>OSC2                                                                                                 | Oscillation pin for OSD function            | I/O                                                         | Vcc          | These are oscillation pins for OSD function. Using the same pins as external interrupt and Vsync input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

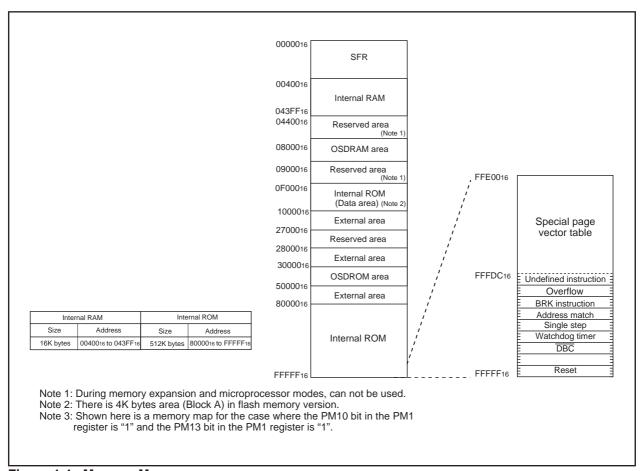

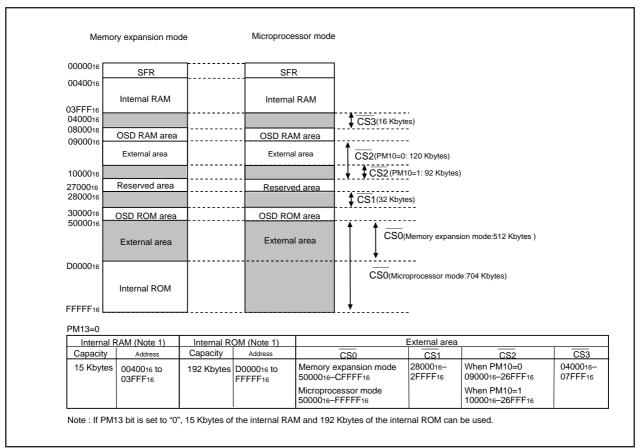

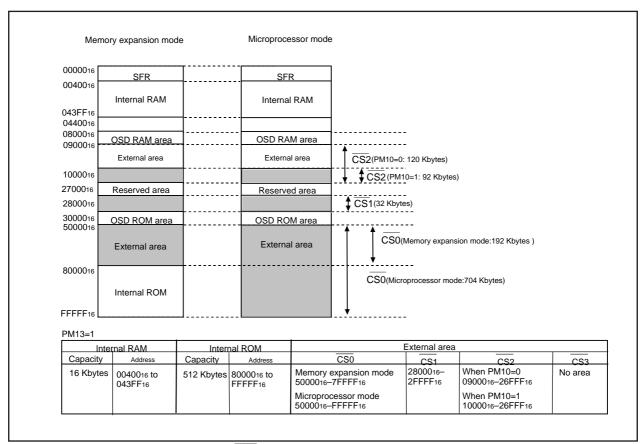

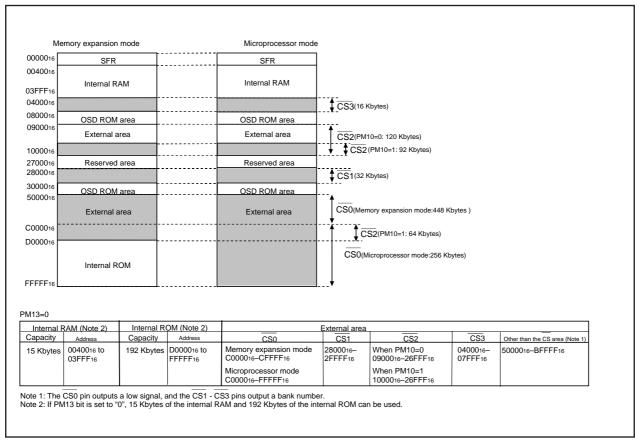

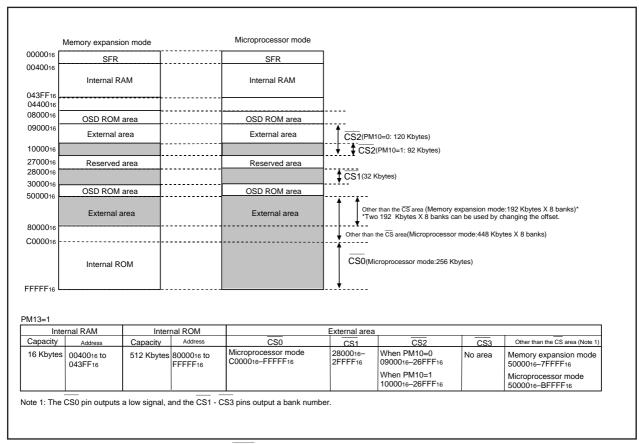

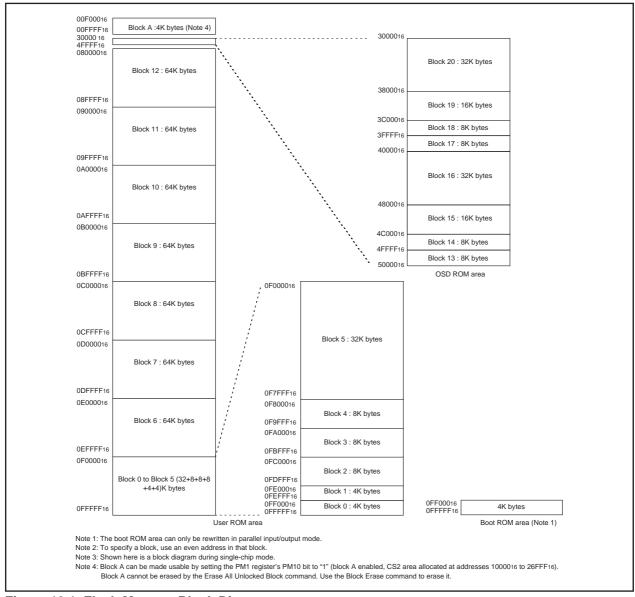

### **Memory**

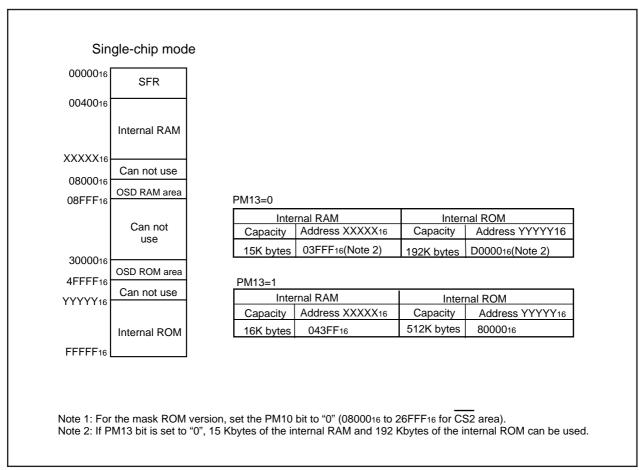

Figure 1.4 is a memory map of the M306V8FJFP. The address space extends the 1M bytes from address 0000016 to FFFFF16.

The internal ROM is allocated in a lower address direction beginning with address FFFFF16. For example, a 64 Kbytes internal ROM is allocated to the addresses from F000016 to FFFFF16.

The fixed interrupt vector table is allocated to the addresses from FFFDC16 to FFFFF16. Therefore, store the start address of each interrupt routine here.

The internal RAM is allocated in an upper address direction beginning with address 0040016. For example, a 10 Kbytes internal RAM is allocated to the addresses from 0040016 to 02BFF16. In addition to storing data, the internal RAM also stores the stack used when calling subroutines and when interrupts are generated.

The SRF is allocated to the addresses from 0000016 to 003FF16. Peripheral function control registers are located here. Of the SFR, any area which has no functions allocated is reserved for future use and cannot be used by users.

The special page vector table is allocated to the addresses from FFE0016 to FFFDB16. This vector is used by the JMPS or JSRS instruction. For details, refer to the "M16C/60 and M16C/20 Series Software Manual." In memory expansion and microprocessor modes, some areas are reserved for future use and cannot be used by users.

Figure 1.4. Memory Map

### **Central Processing Unit (CPU)**

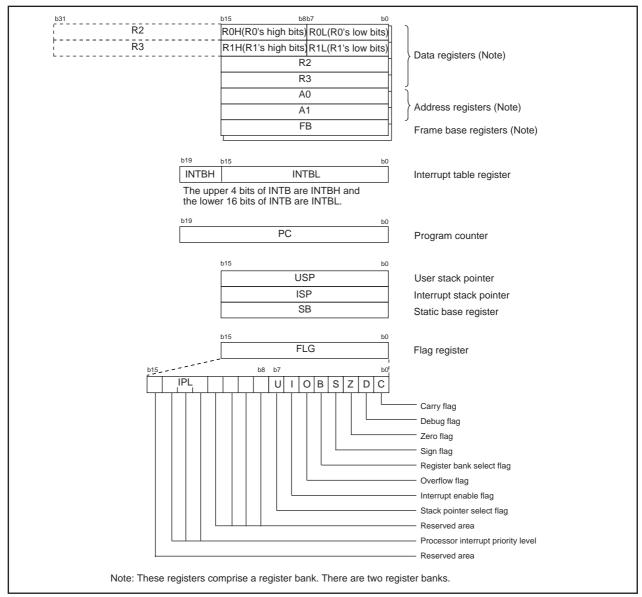

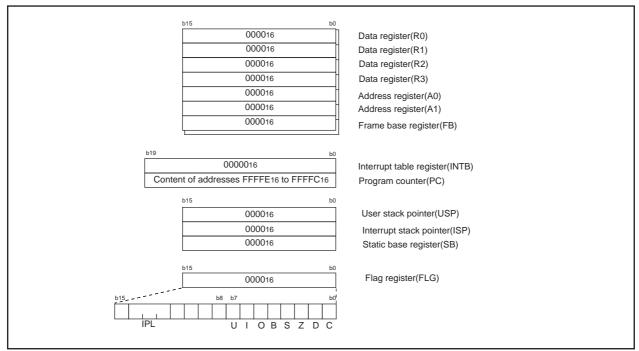

Figure 2.1 shows the CPU registers. The CPU has 13 registers. Of these, R0, R1, R2, R3, A0, A1 and FB comprise a register bank. There are two register banks.

Figure 2.1. CPU registers

### (1) Data Registers (R0, R1, R2 and R3)

The R0 register consists of 16 bits, and is used mainly for transfers and arithmetic/logic operations. R1 to R3 are the same as R0.

The R0 register can be separated between high (R0H) and low (R0L) for use as two 8-bit data registers. R1H and R1L are the same as R0H and R0L. Conversely, R2 and R0 can be combined for use as a 32-bit data register (R2R0). R3R1 is the same as R2R0.

### (2) Address Registers (A0 and A1)

The register A0 consists of 16 bits, and is used for address register indirect addressing and address register relative addressing. They also are used for transfers and logic/logic operations. A1 is the same as A0.

In some instructions, registers A1 and A0 can be combined for use as a 32-bit address register (A1A0).

### (3) Frame Base Register (FB)

FB is configured with 16 bits, and is used for FB relative addressing.

### (4) Interrupt Table Register (INTB)

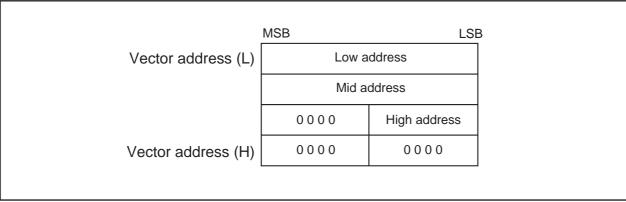

INTB is configured with 20 bits, indicating the start address of an interrupt vector table.

# (5) Program Counter (PC)

PC is configured with 20 bits, indicating the address of an instruction to be executed.

### (6) User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

Stack pointer (SP) comes in two types: USP and ISP, each configured with 16 bits. Your desired type of stack pointer (USP or ISP) can be selected by the U flag of FLG.

### (7) Static Base Register (SB)

SB is configured with 16 bits, and is used for SB relative addressing.

### (8) Flag Register (FLG)

FLG consists of 11 bits, indicating the CPU status.

### Carry Flag (C Flag)

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

### • Debug Flag (D Flag)

The D flag is used exclusively for debugging purpose. During normal use, it must be set to "0".

### · Zero Flag (Z Flag)

This flag is set to "1" when an arithmetic operation resulted in 0; otherwise, it is "0".

### • Sign Flag (S Flag)

This flag is set to "1" when an arithmetic operation resulted in a negative value; otherwise, it is "0".

### Register Bank Select Flag (B Flag)

Register bank 0 is selected when this flag is "0"; register bank 1 is selected when this flag is "1".

### Overflow Flag (O Flag)

This flag is set to "1" when the operation resulted in an overflow; otherwise, it is "0".

#### Interrupt Enable Flag (I Flag)

This flag enables a maskable interrupt.

Maskable interrupts are disabled when the I flag is "0", and are enabled when the I flag is "1". The I flag is cleared to "0" when the interrupt request is accepted.

#### Stack Pointer Select Flag (U Flag)

ISP is selected when the U flag is "0"; USP is selected when the U flag is "1".

The U flag is cleared to "0" when a hardware interrupt request is accepted or an INT instruction for software interrupt Nos. 0 to 31 is executed.

#### Processor Interrupt Priority Level (IPL)

IPL is configured with three bits, for specification of up to eight processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than IPL, the interrupt is enabled.

#### Reserved Area

When write to this bit, write "0". When read, its content is indeterminate.

### **SFR**

| Address            | Register                                 |         | Symbol     | After reset                  |

|--------------------|------------------------------------------|---------|------------|------------------------------|

| 000016             |                                          |         |            |                              |

| 000116             |                                          |         |            |                              |

| 000216             |                                          |         |            |                              |

| 000316             |                                          |         |            |                              |

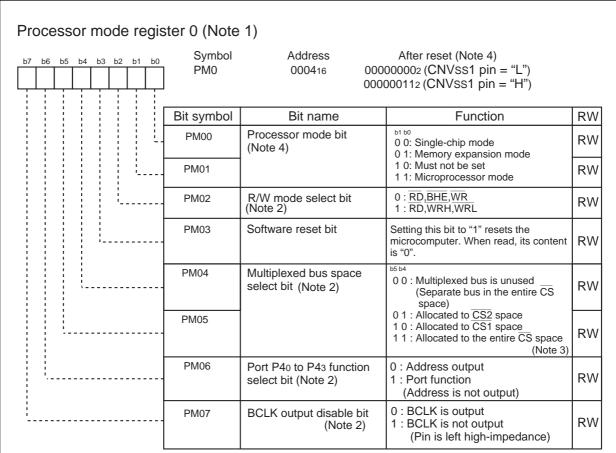

| 000316             | Processor mode register 0 (              | Note 2) | PM0        | 000000002(CNVss1 pin is "L") |

| 000416             | riocessoi illoue register o              | NOIE Z) | FIVIO      |                              |

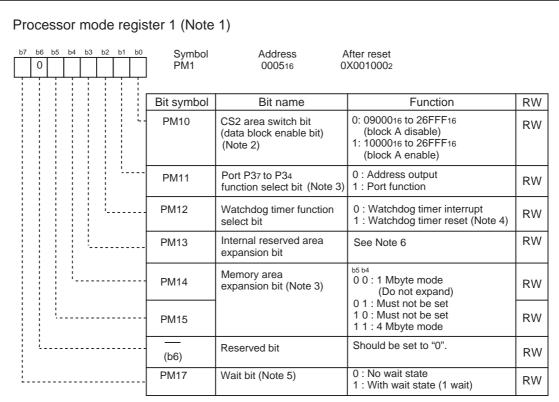

| 2005               | Dropper made register 1                  |         | PM1        | 00000112(CNVss1 pin is "H")  |

| 000516             | Processor mode register 1                |         |            | 000010002                    |

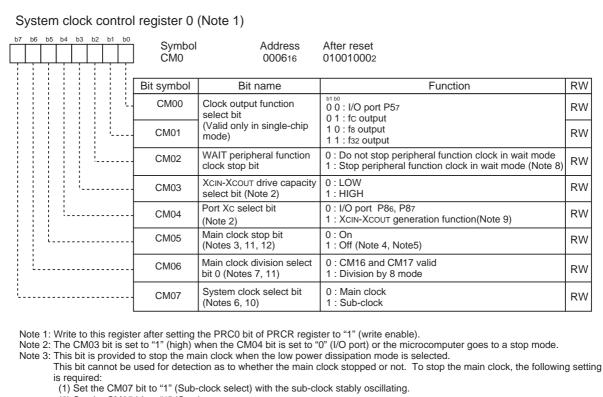

| 000616             | System clock control register 0          |         | CM0        | 010010002                    |

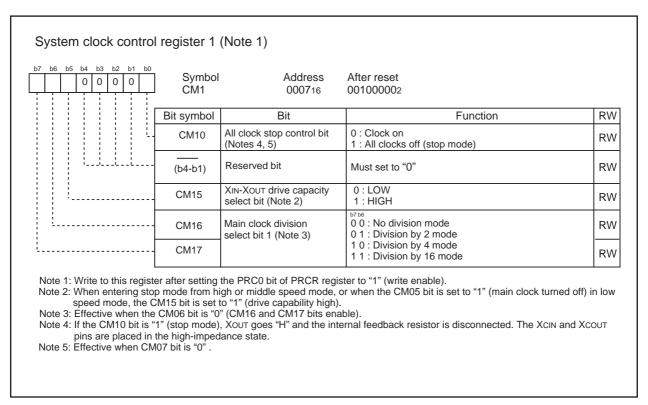

| 000716             | System clock control register 1          |         | CM1        | 001000002                    |

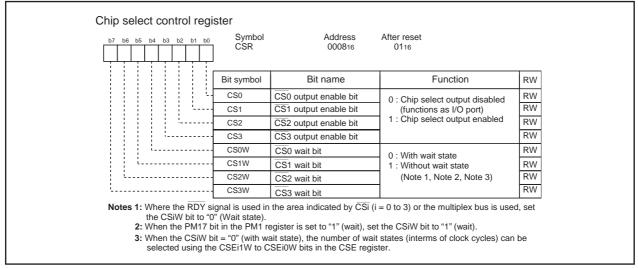

| 000816             | Chip select control register             |         | CSR        | 00000012                     |

| 000916             | Address match interrupt enable register  |         | AIER       | XXXXXX002                    |

| 000A16             | Protect register                         |         | PRCR       | XX0000002                    |

| 000B16             | Data bank register                       |         | DBR        | 0016                         |

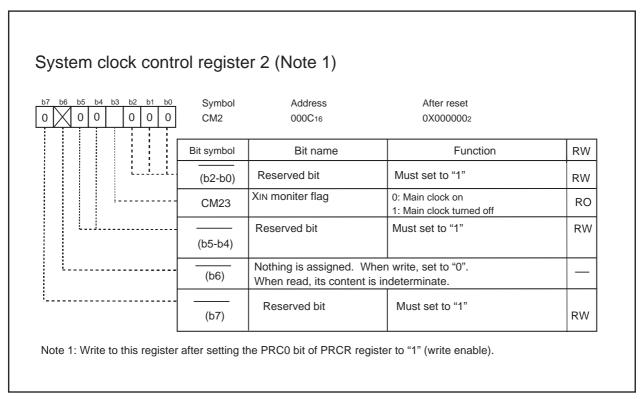

| 000C16             | System clock control register 2          |         | CM2        | 0000X0002                    |

| 000D16             | Joseph Glock Golden agreed 2             |         |            | 0000,10002                   |

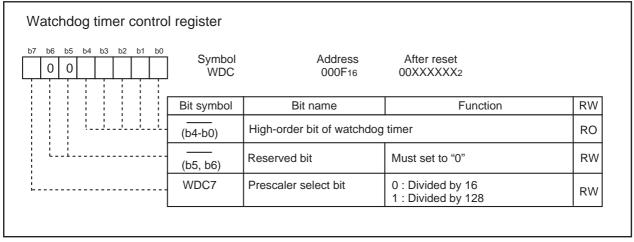

| 000E16             | Watchdog timer start register            |         | WDTS       | ??16                         |

| 000E16             | Watchdog timer control register          |         | WDC        | 00??????2                    |

| 001016             |                                          |         |            |                              |

|                    | Address match interrupt register 0       |         | RMAD0      | 0016                         |

| 001116             |                                          |         |            | 0016                         |

| 001216             |                                          |         |            | X016                         |

| 001316             |                                          |         |            |                              |

| 001416             | Address match interrupt register 1       |         | RMAD1      | 0016                         |

| 001516             | · •                                      |         |            | 0016                         |

| 001616             |                                          |         |            | X016                         |

| 001716             |                                          |         |            | 7.0.0                        |

| 001716             |                                          |         |            |                              |

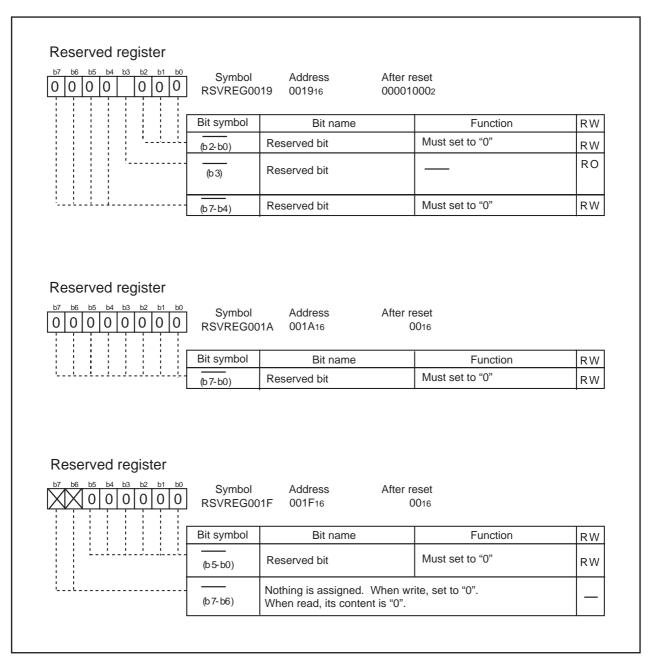

| 001916             | Reserved register                        |         | RSVREG0019 | 000010002                    |

|                    | Reserved register                        |         | RSVREG0019 | 00010002                     |

| 001A <sub>16</sub> |                                          |         |            |                              |

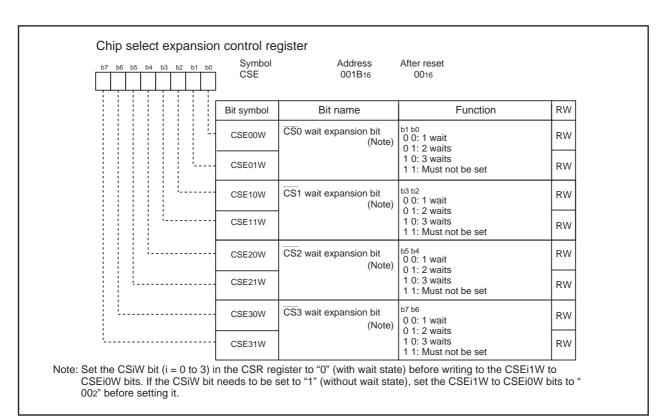

| 001B <sub>16</sub> | Chip select expansion control register 2 |         | CSE        | 0016                         |

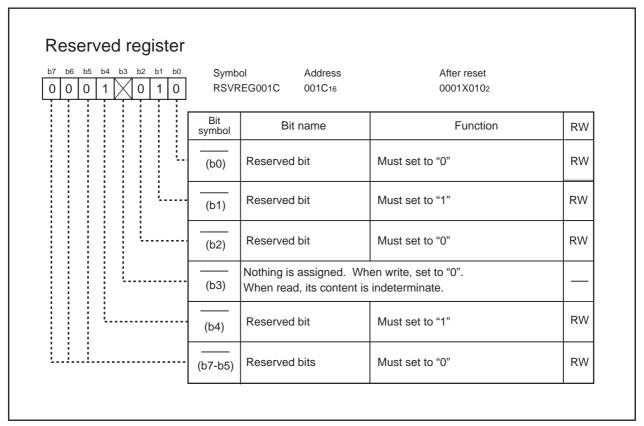

| 001C <sub>16</sub> | Reserved register                        |         | RSVREG001C | 0001X0102                    |

| 001D <sub>16</sub> |                                          |         |            |                              |

| 001E <sub>16</sub> | Reserved register                        |         | RSVREG001E | XXX000002                    |

| 001F16             | Reserved register                        |         | RSVREG001F | 0016                         |

| 002016             | DMA0 source pointer                      |         | SAR0       | ??16                         |

| 002116             | ·                                        |         |            | ??16                         |

| 002216             |                                          |         |            | X?16                         |

| 002316             |                                          |         |            | 71.10                        |

| 002416             | DMA0 destination pointer                 |         | DAR0       | ??16                         |

| 002516             | DiviAo destination pointei               |         | DANO       | -                            |

|                    |                                          |         |            | ??16                         |

| 002616             |                                          |         |            | X?16                         |

| 002716             |                                          |         |            |                              |

| 002816             | DMA0 transfer counter                    |         | TCR0       | ??16                         |

| 002916             |                                          |         |            | ??16                         |

| 002A16             |                                          |         |            |                              |

| 002B16             |                                          |         |            |                              |

| 002C16             | DMA0 control register                    |         | DM0CON     | 00000?002                    |

| 002D16             |                                          |         |            |                              |

| 002E16             |                                          |         |            |                              |

| 002E16             |                                          |         |            |                              |

|                    |                                          |         |            |                              |

| 003016             | DMA1 source pointer                      |         | SAR1       | ??16                         |

| 003116             |                                          |         |            | ??16                         |

| 003216             |                                          |         |            | X?16                         |

| 003316             |                                          |         |            |                              |

| 003416             | DMA1 destination pointer                 |         | DAR1       | ??16                         |

| 003516             | •                                        |         |            | ??16                         |

| 003616             |                                          |         |            | X?16                         |

| 003716             |                                          |         |            |                              |

| 003816             | DMA1 transfer counter                    |         | TCD4       | 2246                         |

| 003916             | DMA1 transfer counter                    |         | TCR1       | ??16                         |

|                    |                                          |         |            | ??16                         |

| 003A16             |                                          |         |            |                              |

| 003B16             |                                          |         |            |                              |

| 003C <sub>16</sub> | DMA1 control register                    |         | DM1CON     | 00000?002                    |

| 003D16             |                                          |         |            |                              |

| 003E16             |                                          |         |            |                              |

| 003F16             |                                          |         |            |                              |

|                    |                                          |         |            |                              |

Note 1: The blank areas are reserved and cannot be accessed by users.

<sup>? :</sup> This bit is indeterminate.

Note 2: The PM00 and PM01 bits do not change at software reset, watchdog timer reset and oscillation stop detection reset.

X : Nothing is mapped to this bit

| 0.00459                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Address | Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Symbol   | After reset |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|

| MATS   Interrupt control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 004016  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |             |

| MATS   Interrupt control register   INT 3   Interrupt control register   TBSIC   XXXX70002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |             |

| MT3 interrupt control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | IN TO SEE A | IN ITOLO | 1/1/000000- |

| Timer B4 interrupt control register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |             |